# รายงานวิจัยฉบับสมบรูณ์

โครงการ เทคนิคที่มีประสิทธิภาพสำหรับการสังเคราะห์ระดับสถาปัตยกรรมสำหรับระบบเรียลไทม์ VLSI

โดย นางสาวจันทนา จันทราพรซัย และคณะ

30 มิถุนายน พ.ศ. 2548

# รายงานวิจัยฉบับสมบรูณ์

โครงการ เทคนิคที่มีประสิทธิภาพสำหรับการสังเคราะห์ระดับสถาปัตยกรรมสำหรับระบบเรียลไทม์ VLSI

โดย นางสาวจันทนา จันทราพรซัย และคณะ

30 มิถุนายน พ.ศ. 2548

# รายงานวิจัยฉบับสมบรูณ์

โครงการ เทคนิคที่มีประสิทธิภาพสำหรับการสังเคราะห์ระดับสถาปัตยกรรมสำหรับระบบเรียลไทม์ **VLS**I

นางสาวจันทนา จันทราพรชัย มหาวิทยาลัยศิลปากร

ศ. ดร. วัลลภ สุระกำพลธร สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

สนับสนุนโดยทบวงมหาวิทยาลัย และสำนักงานกองทุนสนับสนุนการวิจัย (ความเห็นในรายงานนี้เป็นของผู้วิจัย ทบวงฯ และ สกว. ไม่จำเป็นต้องเห็นด้วยเสมอไป)

### บทคัดย่อ

ในงานวิจัยนี้ได้นำเสนอ Framework สำหรับวิธีการสำรวจการออกแบบที่เหมาะสมซึ่ง พิจารณาปัจจัยความไม่แน่นอน (Impreciseness) ในข้อกำหนดของการออกแบบ ในการ สังเคราะห์วงจรระดับสถาปัดยกรรมนั้น มักจะมีความไม่แน่นอนเกี่ยวกับข้อมูลของข้อกำหนด ในงานวิจัยนี้ ผู้วิจัยได้พิจารณาประเภทของความไม่แน่นอนของประเภท ได้แก่ ความไม่แน่ นอนในด้านข้อกำหนดของหน่วยคำนวณ และความไม่แน่นอนในข้อกำหนดด้านเงื่อนไขด้าน เวลาและเงื่อนไขด้านจำนวนรีจิสเตอร์ ใน Framework นี้ จะอ้างอิงรูปแบบ iterative และอ้างอิง กับวิธีการจัดลำดับอันได้แก่ Register-Constrained Inclusion Scheduling ในบทความนี้ได้นำ เสนอตัวอย่างถึงวิธีการทำงานของการจัดลำดับแบบนี้ และได้ทดลองการใช้ Framework การ ออกแบบนี้กับตัวอย่าง benchmark อันได้แก่ Discrete Cosine Transform และ Voltera Filter แนวทางการออกแบบที่เลือกสำหรับการออกแบบทั้งสองนี้ได้เหมาะสมกับระดับการยอมรับได้ (Acceptability Criteria) และประหยัดจำนวนรีจีสเตอร์ทั้งหมดโดยประมาณด้วย

คำสำคัญ การสำรวจการออกแบบโดยอาศัยความไม่แน่นอน การจัดลำดับ คุณ ลักษณะการออกแบบหลายปัจจัย ข้อมูลความไม่แน่นอน เงื่อนไขด้านเวลา และ Inclusion Scheduling

<u>Keywords</u> Imprecise Design Exploration, Scheduling/Allocation, Multiple Design Attribute, Imprecise Information, Register Constraint, Inclusion Scheduling

#### **Abstract**

We propose a design exploration framework which consider impreciseness in design specipication. In high-level synthesis, imprecise information is often encountered. We consider two types of imprecesness: impreciseness underlying on functional unit specipications and on contraints: latency and register. The framework is iterative and based on a core scheduling called, *Register-Constrained Inclusion Scheduling*. An example how the scheduling algorithm work is shown. We demonstrate the effectiveness of our framework for imprecise specipication by exploring a design solution for a well-known benchmark, *Discrete Cosine Transform*, and *Voltera Filter*. The selected solution meets the acceptability criteria while minimizing the total number of registers.

### สัญญาเลขที่ MRG4680115

# โครงการ เทคนิคที่มีประสิทธิภาพสำหรับการสังเคราะห์ระดับสถาปัตยกรรมสำหรับระบบเรียลไทม์ VLSI แบบฟอร์มรายงานโครงการวิจัยประจำปี

| <b>ชื่อโครงการ</b> เทคนิคที่มีประสิทธิภ             | าพสำหรับ | บการสังเคราะห์ระดับสถาปัตยกรรมสำหรับระบบเรียลไทม์ VLSI |

|-----------------------------------------------------|----------|--------------------------------------------------------|

| <b>ระยะเวลาโครงการ 1</b> กรกฎาคม :                  | 2546- 30 | มิถุนายน 2548                                          |

| ชื่อหัวหน้าโครงการผู้ได้รับทุน น                    | างสาวจัน | ทนา จันทราพรชัย                                        |

| ชื่อห <b>ักวิจัยที่ปรึกษา</b> ศ. ดร. วัลลภ          | สุระกำพ  | តេចប                                                   |

| รายงานช่วงวันที่ 1 มกราคม 2548                      |          |                                                        |

| <ol> <li>สำหรับหัวหน้าโครงการผู้ได้รับทุ</li> </ol> |          | ,                                                      |

|                                                     |          | ได้ดำเนินการตามแผนที่วางไว้                            |

|                                                     |          | ได้ดำเนินการง่าซ้ากว่าแผนที่วางไว้                     |

|                                                     |          | ได้เปลี่ยนแผนงานที่วางไว้ดังนี้                        |

|                                                     |          |                                                        |

- 1.2 รายละเอียดผลการดำเนินงานของโครงการ

- 1. สรุปย่อ (Summary)

### วัตถุประสงค์

- 1. เพื่อเป็นการสร้างนักวิจัยที่มีความรู้ความสามารถในทางเทคนิคการออกแบบวงจร VLSI

- 2. เพื่อเป็นการพัฒนาความรู้ที่เป็นพื้นฐานในการพัฒนาชอฟต์แวร์สำหรับการสังเคราะห์วงจร VLSI แบบ อัตโนมัติ

- 3. เพื่อเป็นการศึกษาเทคนิคที่อยู่ในปัจจุบันในการออกแบบวงจร VLSI และวิเคราะห์ข้อดีเสีย

- 4. เพื่อเป็นการพัฒนาเทคนิคใหม่เพื่อช่วยในการออกแบบวงจร VLSI ที่พิจารณาคุณลักษณะของวงจรหลาย อย่างพร้อมๆกัน และปัจจัยความไม่แน่นอน

- 5. เพื่อเป็นการนำเทคนิคไปใช้ในการสังเคราะห์วงจร VLSI แบบอัตโนมัติ ในการสังเคราะห์วงจรสำหรับ อุปกรณ์ทางอิเล็กทรอนิกส์ต่างๆ

#### การดำเนินงานวิจัย

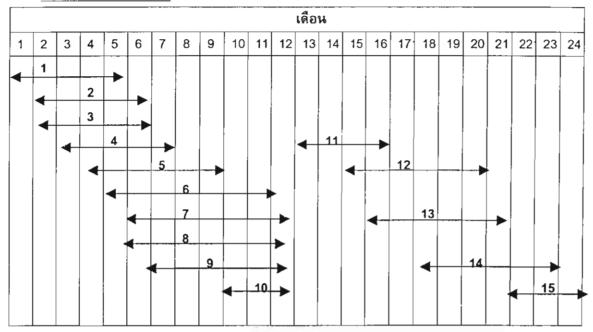

### กิจกรรมที่ได้วางแผนไว้

- 1. ศึกษาเทคนิคอัตโนมัติในการสังเคราะห์วงจร ในด้าน scheduling, allocation, module selection ที่ได้ถูกพัฒนา ขึ้นมาก่อน และวิเคราะห์ข้อดีเสียของเทคนิคเหล่านี้

- 2. ศึกษาปัจจัยความไม่แน่นอนในการสังเคราะห์วงจรชั้นตัน

- 3. ศึกษาปัจจัยคุณลักษณะของวงจรผลลัพธ์ ในแง่ของเวลา ขนาด การใช้พลังงาน รวมถึงความสัมพันธ์ระหว่างกันและ กัน

- 4. ปรับปรุง model สำหรับการวิเคราะห์คุณลักษณะของวงจรผลลัพธ์ที่มีความไม่แน่นอนรวมอยู่ด้วย

- 5. พัฒนา หรือปรับปรุงเทคนิคในการสังเคราะห์วงจร VLSI ตามแบบ model ที่วางไว้ ที่พิจารณา scheduling, allocation พร้อมกันก่อน สำหรับ Functional และ Register allocation

- 6. พัฒนา ชอฟต์แวร์เพื่อจำลองการทำงานของเทคนิคดังกล่าว

- 7. เลือก Benchmark หรือตัวอย่าง Application ที่ใช้อยู่ทั่วไป เพื่อการทดลองเปรียบเทียบการทำงานของเทคนิคใหม่ ที่พัฒนาขึ้นและเทคนิคเก่า

- 8. ทดลองประสิทธิผลของเทคนิคที่คิดคันขึ้นจากโปรแกรมจำลองที่พัฒนาขึ้น

- 9. วิเคราะห์ผลการทดลองและศึกษาแนวทางการนำเทคนิคไปใช้ในการออกแบบจริง

- 10. เขียนรายงานสรุปผลการวิจัย เพื่อนำเสนอผลงานในวารสารทางวิชาการในสาขาที่เกี่ยวข้อง

- 11. ศึกษาวิธีการ Design Exploration ที่มีอยู่

- 12. นำเทคนิดข้อ 5 มาเป็นสร้างเป็น Design Framework ใหม่ที่มีปัจจัยความไม่แน่นอนมากเกี่ยวข้อง โดยอาศัยความ รู้ข้อ 11

- 13. แก้ไข และพัฒนาแบบจำลองการทำงานเพื่อหา Design Solution ที่ได้จากวีธิใหม่นี้

- 14. วัดประสิทธิผลของเทคนิคที่มีอยู่ และ เทคนิคใหม่ เปรียบเทียบกัน

- 15. เขียนรายงานสรุปผลการวิจัยทั้งหมด เพื่อประกอบการนำเสนอในการประชุมทางวิชาการ หรือตีพิมพ์ในวารสารทาง วิชาการ

### <u>กิจกรรมที่ได้ทำจริง</u>

ได้ดำเนินการกิจกรรมที่ 15 เสร็จสิ้นแล้ว

### สรุปการดำเนินงาน

- 1. ได้ทำการศึกษาค้นคว้างานวิจัยที่เกี่ยวข้องกับวิธีการทำ Register Allocation ที่ใกล้เคียงกัน และทบทวน วิธีการ Inclusion Scheduling ที่จะใช้สำหรับทำ Resource binding และ Allocation เมื่อพิจารณาปัจจัย ความไม่แน่นอนมาเกี่ยวข้องด้วยการใช้ Fuzzy Set โดยละเอียด และพิจารณาข้อเด่นของการนำ Register constraint ระหว่างการทำ Scheduling/Allocation เมื่อมีปัจจัยความไม่แน่นอน

- 2. วิเคราะห์ปัญหาที่เกิดขึ้นและนิยามปัญหาเมื่อต้องการพิจารณาปัจจัย Register constraint ในสภาวะที่มี ความไม่แน่นอน ด้วยฟัชชีเซท

- 3. ได้ทำการปรับปรุงเทคนิคเพื่อรองรับปัจจัยของความไม่แน่นอนในส่วนของริจีสเตอร์แล้ว

- 4. ได้ปรับปรุงและพัฒนาชอฟต์แวร์ตามข้อ 3 เรียบร้อยแล้ว

- 5. ได้ทำการทดลองกับ Benchmark เบื้องล้นแล้ว และได้ผลดีกว่าแบบดั้งเดิมที่ไม่ได้พิจารณาปัจจัย register ถึง 35%

- 6. ได้ปรับปรุงและพัฒนา Design Exploration Framework แบบ iterative ซึ่งนำปัจจัยความไม่แน่นอนด้าน Register Constraint มาเกี่ยวข้อง

- 7. ได้ทำการทดลองกับ Benchmark และเก็บข้อมูลเพิ่มเติมสำหรับ Design Exploration

- 8. ได้เขียนสรุปรายงาน และส่ง manuscript ไปยัง IEEE Transactions on Computer-Aided Design (Impact Factor 0.782) เมื่อวันที่ 30 เมษายน 2548

#### 3. ผลงานวิจัยที่ตีพิมพ์ในวารสารวิชาการระดับนานาชาติ

- ได้ตีพิมพ์เรื่อง Efficient Scheduling for Design Exploration with Imprecise Latency and Register Constraints ใน Lecture Notes in Computer Science (LNCS 3207) ปี 2004 หน้า 259-**270 impact** factor **0.413**

- ได้ดีพิมพ์เรื่อง Design Exploration Framdwork under Impreciseness based on Inclusion Scheduling ใน Lecture Notes in Computer Science (LNCS 3321) ปี 2004 หน้า 78-93 impact factor 0.413

### 4. กิจกรรมอื่นๆที่เกี่ยวข้อง

- ได้นำเสนอผลงานทางวิชาการเรื่อง Efficient Scheduling for Design Exploration with Imprecise Latency and Register Constraints ในการประชุมวิชาการ The 2004 International Conference on Embedded And Ubiquitous Computing (EUC04) ที่ University of Aizu ประเทศญี่ปุ่น ในวันที่ 25-27 สิงหาคม 2547

- ได้นำเสนอผลงานทางวิชาการเรื่อง Register-Constrained Inclusion Scheduling for Imprecise Specification ในงานประชุม IEEE Analog and Digital Techniques in Electrical Engineering ปี 2004 ณ โรงแรมโลตัสปางสวนแก้ว เชียงใหม่ วันที่ 20-24 พฤศจิกายน 2547 และลงตีพิมพ์ใน Proceeding ของงานประชุม หน้า 160-163

- ได้นำเสนอผลงานทางวิชาการเรื่อง Design Exploration Framdwork under Impreciseness based on Inclusion Scheduling ในงานประชุมวิชาการ 9<sup>th</sup> ASIAN Computing Science Conference ณ มหาวิทยาลัย เชียงใหม่ ในวันที่ 10-12 ธันวาคม 2548

#### ปัญหาและอุปสรรค

MRG4680115 30 มิถุนายน 2548

| ความเห็นและข้อเสนอแนะ                               |

|-----------------------------------------------------|

| <del>-</del>                                        |

|                                                     |

| งานที่จะทำในปีต่อไป<br>-                            |

| รับนักวิจัยที่ปรึกษา<br>จะส่งแบบประเมินตามมาภายหลัง |

| ลงนวม                                               |

|                                                     |

(หัวหน้าโครงการผู้ได้รับทุน)

2.

### บทคัดย่อ

ในงานวิจัยนี้ได้นำเสนอ Framework สำหรับวิธีการสำรวจการออกแบบที่เหมาะสมซึ่ง พิจารณาปัจจัยความไม่แน่นอน (Impreciseness) ในข้อกำหนดของการออกแบบ ในการ สังเคราะห์วงจรระดับสถาปัตยกรรมนั้น มักจะมีความไม่แน่นอนเกี่ยวกับข้อมูลของข้อกำหนด ในงานวิจัยนี้ ผู้วิจัยได้พิจารณาประเภทของความไม่แน่นอนของประเภท ได้แก่ ความไม่แน่ นอนในด้านข้อกำหนดของหน่วยคำนวณ และความไม่แน่นอนในข้อกำหนดด้านเงื่อนไขด้าน เวลาและเงื่อนไขด้านจำนวนรีจิสเตอร์ ใน Framework นี้ จะอ้างอิงรูปแบบ iterative และอ้างอิง กับวิธีการจัดลำดับอันได้แก่ Register-Constrained Inclusion Scheduling ในบทความนี้ได้นำ เสนอตัวอย่างถึงวิธีการทำงานของการจัดลำดับแบบนี้ และได้ทดลองการใช้ Framework การ ออกแบบนี้กับตัวอย่าง benchmark อันได้แก่ Discrete Cosine Transform และ Voltera Filter แนวทางการออกแบบที่เลือกสำหรับการออกแบบทั้งสองนี้ได้เหมาะสมกับระดับการยอมรับได้ (Acceptability Criteria) และประหยัดจำนวนรีจีสเตอร์ทั้งหมดโดยประมาณด้วย

คำสำคัญ การสำรวจการออกแบบโดยอาศัยความไม่แน่นอน การจัดลำดับ คุณ ลักษณะการออกแบบหลายปัจจัย ข้อมูลความไม่แน่นอน เงื่อนไขด้านเวลา และ Inclusion Scheduling

<u>Keywords</u> Imprecise Design Exploration, Scheduling/Allocation, Multiple Design Attribute, Imprecise Information, Register Constraint, Inclusion Scheduling

# สารบัญ

| บทคัดย่อ                                                              | 1  |

|-----------------------------------------------------------------------|----|

| บทที่ 1 บทนำ                                                          | 4  |

| บทที่ 2 งานวิจัยที่เกี่ยวข้อง                                         | 6  |

| บทที่ 3 Model และความรู้เกี่ยวกับทฤษฎีพัชซี่เชด                       | 8  |

| 3.1 การ model ระบบและคุณลักษณะของระบบ                                 | 8  |

| 3.2 ทฤษฎีฟัชชี่เชต                                                    | 11 |

| บทที่ 4 Iterative Design Framework                                    | 13 |

| บทที่ 5 Register-Constrained Inclusion Scheduling                     | 14 |

| 5.1 Latency-based Inclusion Scheduling                                | 14 |

| 5.2 อัลกอริทีม Register-Constrained Inclusion Scheduling              | 16 |

| 5.2.1 Imprecise Timing Attribute                                      | 16 |

| 5.2.2 การคำนวณการใช้งานรีจิสเตอร์                                     | 18 |

| 5.2.3 อัลกอริทึม                                                      | 19 |

| บทที่ 6 ตัวอย่างการทำงานของ Register-Constrained Inclusion Scheduling | 22 |

| บทที่ 7 ผลการทดลอง                                                    | 26 |

| 7.1 Discrete Cosine Transform                                         | 26 |

| บทที่ 8 สรุปผล                                                        | 30 |

| เอกสารอ้างอิง                                                         | 31 |

# สารบัญรูปและตาราง

| รูปที่ 3.1 โค้ดและตัวอย่าง DFG                                                               | 8    |

|----------------------------------------------------------------------------------------------|------|

| รูปที่ 3.2 การพล็อดของฟังก์ชัน Rai.azi - 1.249689aı - 2azi - 0.001242                        | g    |

| รูปที่ 3.3 Projection ของรูป 3.2                                                             | 10   |

| รูปที่ 3.4 (a) Z-Shaped acceptability function (b) projection                                | 10   |

| รูปที่ 3.5 การบวกตัวเลขฟัชชี่ A+B                                                            | 11   |

| รูปที่ 4.1 การหา design solution แบบ iterative                                               | 13   |

| รูปที่ 5.1 ค่า FST(u) และ FFT(u) สองกรณี                                                     | 17   |

| รูปที่ 5.2 ความสัมพันธ์ระหว่างโหนดที่ถูกจัดลำดับแล้วและ life time                            | 19   |

| รูปที่ 6.1 กราฟตัวอย่าง                                                                      | 22   |

| -<br>ตารางที่ 6.1 แสดงคุณลักษณะของหน่วยคำนวณ                                                 | 22   |

| รูปที่ 6.2 System Specification สำหรับกราฟตัวอย่าง                                           |      |

| -<br>รูปที่ 6.3  (a) ตารางจัดลำดับที่ได้จาก RCIS (b) ตารางจัดลำดับที่ได้ indusion scheduling | 23   |

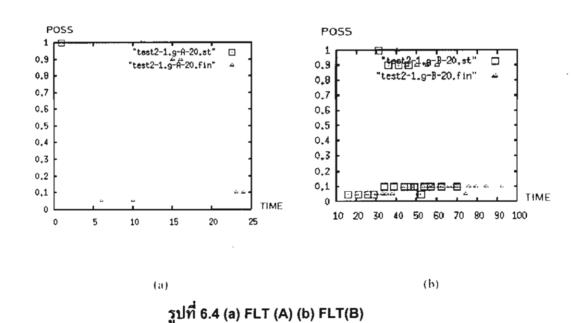

| รูปที่ 6.4 (a) FLT (A) (b) FLT(B)                                                            | 23   |

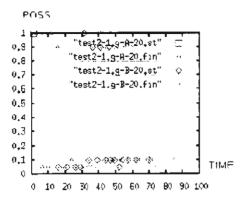

| รูปที่ 6.5 FLT (A) และ FLT(B)                                                                | 24   |

| รูปที่ 6.6 FLT สำหรับทุกโหนดในกราฟ (a) FST (b) MFFT                                          | 24   |

| รูปที่ 6.7 Register count และค่าความเป็นไปได้ ณ เวลาต่างๆ                                    | 25   |

| รูปที่ 6.8 กราฟใหม่เมื่อเดิมโหนดเข้าไป                                                       | 25   |

| ตารางที่ 7.1 ลักษณะของ adder และ multiplier                                                  | 26   |

| ิตารางที่ 72 ผลการทดลองของ DCT เปรียบเทียบ RCIS และ IS สำหรับจำนวนหน่วยคำนวณต่าง ๆ กัน       | 27   |

| รูปที่ 7.1 system specification ของ DCT                                                      | 27   |

| ดารางที่ 7.3 ค่าความเป็นไปได้สำหรับการใช้งานจำนวนรีจิสเตอร์ต่างๆ กัน สำหรับ กรณี             |      |

| adder 7ตัว และ multiplier 5 ตัว ของ RCIS                                                     | 27   |

| ตารางที่ 7.4 ค่าความเป็นไปใัด้สำหรับการใช้งานจำนวนรีจิสเตอร์ต่างๆ กัน สำหรับ กรณี            |      |

| adder 7ตัว และ multiplier 5 ตัว ของ IS                                                       | 27   |

| รูปที่ 7.2 System Specification ของ Voltera filter                                           | 28   |

| -<br>ตารางที่ 7.5 ผลการทดลองของ Voltera filter  เปรียบเทียบ RC!S และ IS สำหรับจำนวนห         | น่วย |

| คำนวณต่างๆ กัน                                                                               | 29   |

| รูปที่ 7.3 ค่า acceptability degree ของแต่จะการออกแบบ                                        | 29   |

# บทที่ 1 บทนำ

ในการสังเคราะห์วงจรระดับสถาปัตยกรรม มักมีความไม่แน่นอนในข้อมูลต่างๆ ได้แก่ ในแง่ของการ implement การเลือกองค์ประกอบ (component) ของวงจรสำหรับการออกแบบ อาจจะยังไม่สามารถกำหนดได้เนื่องจากหลายสาเหตุ อาจจะเป็นเพราะมีหลาย ประเภทขององค์ประกอบให้เลือก เช่น มี module ที่ทำหน้าที่เป็น ตัวคูณ (multiplier) หลาย ประเภท หรืออาจจะเป็นเพราะ module บาง module ยังไม่ได้ถูกออกแบบในระดับ physical ทำ ให้คุณลักษณะบางอย่างของ module นั้นยังไม่แน่นอน หรือแม้ว่า module นั้นได้ถูกออกแบบ เรียบร้อยแล้ว คุณลักษณะบางอย่างอาจจะมีการเปลี่ยนแปลงเนื่องจากขั้นตอนการ fabricate ก็ ได้ อีกประเภทหนึ่งของความไม่แน่นอนได้แก่ ความไม่แน่นอนหรือความกำกวมในด้านระดับ การยอมรับได้ (acceptability level) หรือระดับความพึงพอใจของการออกแบบที่ได้ในระดับ สถาปัตยกรรม เช่นถ้ามีความพึงพอใจกับการออกแบบที่สามารถทำงานได้ภายในเวลา cycle และถ้าการออกแบบที่ได้ทำงานได้ในเวลา 51 cycle จะยังสามารถยอมรับได้หรือไม่ โดย เฉพาะอย่างยิ่งเมื่อมีปัจจัยการออกแบบหลายปัจจัยมาเกี่ยวข้องซึ่งปัจจัยเหล่านั้นอาจจะขัดแย้ง กันอยู่ในดัวเอง เช่นในแง่ประสิทธิภาพและการใช้พลังงาน ประสิทธิภาพความเร็วสูงอาจจะไม่ ประหยัดพลังงาน หรือ ในแง่ของจำนวนรีจิสเตอร์ที่ใช้กับเวลาในการทำงานของการออกแบบที่ ได้ ถ้าวงจรทำงานเร็วอาจจะใช้จำนวนรีจิสเตอร์มากขึ้น จะยอมรับได้หรือไม่ ถ้าวงจรนั้นทำงาน ช้าลง 1 หรือ 2 clock cycle แต่ประหยัดรีจิสเตอร์ได้ 1 ตัว หรือ ถ้าใช้เวลามากขึ้นกว่าเดิม 10 clock cycle จะยังยอมรับได้หรือไม่ มากน้อยเท่าไร ดังนั้นการพิจารณาปัจจัยความไม่แน่นอน อย่างเหมาะสมในการสังเคราะห์วงจรรวมระดับสถาปัตยกรรมจะมีผลต่อการออกแบบที่ได้ด้วย

ในงานวิจัยนี้ ได้มีการนำเสนอ framework สำหรับการสำรวจการออกแบบที่เหมาะสม ซึ่งพิจารณาปัจจัยความไม่แน่นอนทั้งในด้านข้อกำหนดของระบบผลลัพธ์และเงื่อนไข (requirement) ด้านเวลา (latency) และการใช้งานรีจิสเตอร์ อย่างไรก็ดีวิธีการดังกล่าวสามารถ ขยายต่อไปเพื่อพิจารณาความไม่แน่นอนในเงื่อนไขหลายๆ ด้านในการออกแบบด้วย ลักษณะ ข้อกำหนดของระบบถูก model อ้างอิงกับทฤษฎีพัชซี่เชต ในงานวิจัยนี้จะพิจารณาจำนวนรีจิส เตอร์ที่ใช้เป็นอีกมิติหนึ่งของเงื่อนไขของระบบงาน ผู้วิจัยได้คิดคันวิธีการจัดลำดับ (scheduling) เมื่อพิจารณาปัจจัยด้านเวลา[3,7] เพื่อใช้เป็นอัลกอริทึมหลักใน iterative design framework นี้ ตารางจัดลำดับที่ได้จะพยายามลดการใช้งานในแง่ของจำนวนริจิสเตอร์ ถ้าดารางจัดลำดับนั้น ยอมรับได้ ก็จะได้ผลลัพธ์การออกแบบ ถ้าไม่เช่นนั้น จะมีการปรับจำนวนทรัพยาการ หรือ หน่วยคำนวณและทดลองจัดลำดับด้วยวิธีดังกล่าวใหม่ จนกว่าได้ผลลัพธ์การออกแบบที่ยอมรับ ได้ ข้อมูลเข้าของ framework นี้ได้แก่ data flow graph ซึ่งประกอบด้วยพารามิเตอร์ด้านเวลาที่ มีความไม่แน่นอนอยู่ งานประยุกด์ของระบบประเภทดังกล่าวได้แก่ ระบบ digital signal processing หรือ communication switch และ งานประเภท real-time multimedia rendering เป็นตัน ข้อกำหนดที่ไม่แน่นอนทั้งในด้านพารามิเตอร์และเงื่อนไขนั้นจะมีผลอย่างมากต่อการจัด

สรรทรัพยาการ (resource allocation) และการจัดลำดับสำหรับการออกแบบงานประยุกด์เหล่า นี้ ดังนั้น การพัฒนาเทคนิคการสังเคราะห์และเทคนิคการ optimize วงจรรวม ซึ่งพิจารณาปัจจัย ความไม่แน่นอนเหล่านี้จึงมีความสำคัญอย่างยิ่ง

ในการสังเคราะห์วงจรและเครื่องมือต่างๆ ที่มีอยู่โดยทั่วไปจะไม่พิจารณาปัจจัยความไม่ แน่นอนในข้อกำหนดดังกล่าว ส่วนมากจะสมมติว่าข้อมูลต่างๆ ที่ได้จะได้จากพิจารณากรณี worst case หรือกรณีทั่วไป (typical case) แล้ว เช่นพิจารณาเวลาในการทำงานของ module ที่ ใช้ในแบบ worst case เงื่อนไขด้านเวลามักจะกำหนดมาในรูบ่แบบของค่าคงที่ (fixed value) ซึ่งแม้ว่าในความเป็นจริงอาจจะยืดหยุ่นได้บ้างเนื่องจากระดับความพึงพอใจของนักออกแบบแต่ ละคนมักจะแตกต่างกัน การตั้งสมมติฐานแบบดังกล่าวอาจจะเป็นแหล่งกำเนิดทำให้การต้องมี การปรับการออกแบบหลายครั้งกว่าจะได้ผลลัพธ์ หรืออาจจะนำมาซึ่งผลลัพธ์ของการออกแบบที่ ใช้ทรัพยากรต่างๆ มากเกินความจำเป็น การพิจารณาปัจจัยความไม่แน่อย่างเหมาะสมตั้งแต่ขั้น แรกๆ ของการออกแบบจะทำให้ได้การออกแบบเริ่มต้นที่ดี และทำให้การปรับการออกแบบทำ ได้เร็วกว่า

การใช้ตัวแปรสุ่มและความน่าจะเป็นเป็นอีกแนวทางหนึ่งซึ่งใช้ model ความไม่แน่นอน อย่างไรก็ดี การเก็บข้อมูลเกี่ยวกับความน่าจะเป็น บางครั้งก็ยากลำบากและใช้เวลาในการเก็บ ข้อมูล นอกจากนี้ความไม่แน่นอนบางอย่างเช่นระดับความพึงพอใจของการออกแบบที่ได้ก็ไม่ สามารถ model ได้ด้วยความน่าจะเป็น

ในงานวิจัยนี้ ผู้วิจัยได้พิจารณาทั้งปัจจัยความไม่แน่นอนด้านเวลาและการใช้งานรีจิส เตอร์ ผู้วิจัยได้พัฒนา framework สำหรับการสำรวจการออกแบบที่พิจารณาความไม่แน่นอนใน ข้อกำหนดคุณลักษณะของระบบผลลัพธ์และเงื่อนไข framework ดังกล่าวเป็นแบบ iterative ซึ่ง อาศัยวิธีการจัดลำดับที่ได้พัฒนาขึ้น ที่เรียกว่า RCIS (Register-Constrained Inclusion Scheduling) ซึ่งพิจารณาข้อมูลที่มีความไม่แน่นอน จากการทดลองพบว่าผู้วิจัยสามารถหาคำ ตอบสำหรับการออกแบบที่ลดจำนวนรีจิสเตอร์ได้

ในรายงานนี้ได้แบ่งออกเป็นบทต่างๆ ดังนี้

- -บทที่ 2 นำเสนองานวิจัยที่เกี่ยวข้อง

- -บทที่ 3 อธิบายถึง model ที่ใช้ในงานวิจัยทั้ง data flow graph และ model คุณ ลักษณะที่ไม่แน่นอน และนำเสนอความรู้พื้นฐานต่างๆเกี่ยวกับทฤษฎีฟัชซี่ที่จำเป็น

- -บทที่ 4 อธิบายถึง iterative design framework ที่ได้พัฒนาขึ้น

- -บทที่ 5 นำเสนอวิธีการจัดลำดับแบบ RCIS ซึ่งใช้ในบทที่ 3 โดยละเอียด และ นำเสนอ นอกจากนี้ได้นำเสนอประเด็นต่างๆ ที่เกี่ยวข้องเมื่อพิจารณาการใช้งานรีจิสเตอร์ และการ คำนวณจำนวนรีจิสเตอร์ที่ใช้ระหว่างการจัดลำดับเมื่อมีปัจจัยความไม่แน่นอน

- -บทที่ 6 นำเสนอตัวอย่างการทำงานของอัลกอริทึมดังกล่าวในบทที่ 4

- -บทที่ 7 นำเสนอผลการทดลองเมื่อใช้ framework ดังกล่าวกับตัวอย่าง benchmark

- -บทที่ 8 สรุปงานวิจัยและนำเสนอแนวทางการวิจัยต่อไปในอนาคต

# บุทที่ 2 งานวิจัยที่เกี่ยวข้อง

ได้มีนักวิจัยหลายๆ ท่านได้ใช้ตรรกะแบบพัชซี่เพื่อแก้ปัญญาการจัดลำดับในงาน ประยุกต์ต่างๆ กัน เช่น ฟิลด์ compiler optimization ได้มีการใช้ทฤษฎีพัชซี่เซตในการพิจารณา real-time event และ ความไม่แน่นอนเกี่ยวกับตัวแปร (variable) [18] Lee et. al ใช้การอนุมาน แบบพัชซีมาช่วยหาตารางจัดลำดับที่เป็นไปได้สำหรับระบบ real-time โดยให้แต่ละ task ทำได้ งานตาม deadline ภายใต้เงื่อนไขการใช้ทรัพยาการที่กำหนด [23] ในงานด้าน production management ได้มีการใช้กฎพัชซี่เพื่อทำการจัดลำดับสำหรับ job shop และ floor shop [27,33] Kaviani และ Vranesic ใช้กฎพัชซี่เพื่อตัดสินหาจำนวนโพรเชสเชอร์ที่เหมาะสมสำหรับ เชตของ task และ deadline ที่กำหนดให้สำหรับระบบ real-time [22] Soma et.al พิจารณาการทำ schedule optimization โดยใช้การอนุมานแบบพัชซี่ [32] งานวิจัยเหล่านี้ ไม่ได้พิจารณากรณีที่ว่าข้อกำหนดด้านเวลาของแต่ละ task อาจจะไม่ใช่คำแน่นอน หรือไม่ได้พิจารณาคุณ ลักษณะอื่นๆ นอกจากด้านเวลาของตารางการจัดลำดับ

งานวิจัยอื่นๆ เกี่ยวกับการสำรวจการออกแบบวงจร (design exploration) ได้แก่ [1,9,15,26] งานเหล่านี้แตกต่างกันในด้านเทคนิคที่ใช้ในการหาผลลัพธ์การออกแบบและการตัด สินใจเลือกผลลัพธ์การออกแบบ อย่างไรก็ดึงานเหล่านี้ไม่ได้พิจารณาปัจจัยความไม่แน่นอนใน คุณลักษณะของระบบเช่น เงื่อนไขด้านเวลา และความไม่แน่นอนเกี่ยวกับเวลาที่ใช้ในการรัน งานในหน่วยคำนวณ Karkowski และ Otten ได้เสนอ model ที่ใช้ในการจัดการความไม่แน่นอน ด้านเวลาของหน่วยคำนวณโดยใช้ทฤษฏีพัชชี่เชด วิธีการที่นำเสนอได้อ้างอิงวิธีการ possibilistic programming โดยอาศัย integer linear programming (ILP) เพื่อหาดารางจัด ลำดับและการจัดสรรทรัพยากรหน่วยคำนวณโดยภายใต้เงื่อนไขต้านเวลาและพื้นที่ โดยเงื่อนไข ก็ได้ใช้ฟัชซี่เซต model เช่นกัน อย่างไรก็ดีการใช้ ILP กับ fuzzy constraint และ fuzzy coefficient นั้น ใช้เวลาในการประมวลผลมาก นอกจากนี้งานวิจัยนี้ไม่ได้พิจารณาถึงระดับความ พึงพอใจที่เกิดขึ้นสำหรับผลลัพธ์การออกแบบที่ได้ ได้มีงานวิจัยหลายงานเกี่ยวกับการประมาณ การการใช้ทรัพยากร (resource estimation) [10,28,31] ซึ่งงานเหล่านี้ก็ไม่ได้พิจารณาคุณ ลักษณะของการแบบหลายปัจจัย หรือไม่ได้พิจารณาถึงความไม่แน่นอนในคุณลักษณะของ ระบบผลลัพธ์

งานวิจัยเกี่ยวกับการจัดลำดับและการจัดสรรการใช้รีจิสเตอร์มีอีกมากมายใน area ของ การสังเคราะห์วงจรระดับสถาปัตยกรรม และ compiler optimization สำหรับสถาปัตยกรรมของ VLIW เช่น Varatkar et. al. ได้นำเสนออัลกอริทึมการจัดลำดับสำหรับระบบมัลติโพรเซสเซอร์ ซึ่งพิจารณาการประหยัดพลังงานทั้งหมด [34] Shao et. al. ได้นำเสนอการจัดลำดับสำหรับ ระดับคำสั่ง (instruction level scheduling) สำหรับงานประยุกต์ที่มีลูปและพิจารณาประหยัด

พลังงานโดยการลด switching activity [30] Chen et. al. ได้เสนอการจัดลำดับสำหรับงาน ประยุกต์ที่มีลูปสำหรับการ optimize ระบบในด้านเวลาและจำนวน memory operation ภายใต้ เงื่อนไขข้อจำกัดด้านจำนวนรีจิสเตอร์ [16] เทคนิคดังกล่าวใช้เทคนิคของ multidimensional retiming Eichenerger et. al. เสนอวิธีการจัดสรรทรัพยากรรีจิสเดอร์สำหรับสถาปัดยกรรมแบบ VLIW และ superscalar โดยใช้ stage scheduling [13,14] Akturan และ Jacome นำเสนออัลก อริทึมการจัดลำดับที่พิจารณาการใช้จำนวนรีจิสเตอร์อย่างประหยัดโดยอาศัยเทคนิค pipelining [2] อัลกอริทึมนี้ใช้เทคนิค retiming และ force directed scheduling มาช่วย และ พิจารณาข้อดีข้อเสียระหว่างขนาดของโค้ดผลลัพธ์ ประสิทธิภาพการทำงานของโค้ดผลลัพธ์ และ การใช้รีจิสเตอร์ของโค้ดนั้นๆ Wong et. al. ได้พัฒนาวิธีการแทรก objective function เข้า ไประหว่างการจัดลำดับและการจัดสรรการใช้ทรัพยากร [35] อัลกอริทึมดังกล่าวชื่อย่อว่า FLOF จะพยายามลดจำนวนการใช้งานรีจิสเตอร์ภายใต้เงื่อนไขด้านเวลาและจำนวนทรัพยากรที่ กำหนดให้ Dani et. al. ได้นำเสนอ heuristic ในการใช้ stage scheduling เพื่อลดจำนวนรีจิส เตอร์ ซึ่งงานนี้ก็มุ่งไปยังการจัดลำดับสำหรับระดับคำสั่งเช่นกัน [11] Zalamea et. al. ได้นำ เสนอวิธีการทางด้านฮาร์ดแวร์และซอฟต์แวร์เพื่อลดการใช้งานรีจิสเตอร์โดยเน้นไปยัง สถาปัตยกรรมแบบ VLIW [24,25,38] ในส่วนของซอฟต์แวร์ งานวิจัยนี้ได้ทำการปรับปรุง modulo scheduling ให้พิจารณาเงื่อนไขด้านจำนวนรีจิสเตอร์ และ register spilling อย่างไรก็ดี งานวิจัยนี้เน้นไปยังการจัดลำดับสำหรับงานประยุกด์ที่มีลูปในโค้ดและไม่ได้พิจารณาปัจจัยความ ไม่แน่นอนในคุณลักษณะของระบบหรือข้อกำหนดของระบบผลลัพธ์

ในงานวิจัย [3] ได้มีการพัฒนา inclusion scheduling ซึ่งพิจารณาปัจจัยความไม่แน่ นอนคุณลักษณะของระบบขึ้น อัลกอริทึมนี้ได้ถูกปรับปรุงและนำมาใช้ในการสำรวจการออกแบบ ภายใต้เงื่อนไขความไม่แน่นอนต่างๆ ด้าน และใช้ในการประมาณขอบเขตในแง่ของจำนวน ทรัพยากร [5,6,8] อย่างไรก็ดีงานวิจัยดังกล่าวก็ไม่ได้พิจารณาปัจจัยของการใช้ทรัพยากรรีจิส เตอร์ในการจัดลำดับ

# บทที่ 3 Model และความรู้เกี่ยวกับทฤษฎีฟัชซี่เซต

ในบทนี้จะได้อธิบายถึง model ที่สำคัญๆ ที่ใช้ในการ model ระบบและคุณลักษณะ รวม ทั้งการ model ปัจจัยความไม่แน่นด้วยทฤษฎีฟัชชี่เซต และ operation ต่างๆ ของฟัชซี่เซตที่ เกี่ยวข้อง

### 3.1 การ model ระบบและคุณลักษณะของระบบ

ในการ model ระบบและคุณลักษณะของระบบส่วนใหญ่นั้น ในระดับสถาปัตยกรรมได้ อ้างอิงการใช้กราฟนั่นคือการใช้ data flow graph (DFG)  $G = (V, \mathcal{E}, \beta)$  ซึ่งในที่นี้จะพิจารณาเป็น แบบ directed acyclic graph ใน data flow graph นั้น จะประกอบด้วยโหนด V, edge  $\mathcal{E}$  และ weight function  $\beta$ บนตัวโหนด  $V \in V$

operation ในโค้ดจะหมายถึงโหนดในกราฟ และความสัมพันธ์ระหว่าง operation จะ หมายถึงการใหลของข้อมูลจาก operation หนึ่งไปยังอีก operation หนึ่งซึ่งจะหมายถึง directed edge ในกราฟ และ weight function จะ map จากเซตของโหนดในกราฟไปยังค่าคุณ ลักษณะของ operation ที่สัมพันธ์กับโหนดนั้น อันได้แก่ ประเภทของ operation ดังตัวอย่างใน รูป 3.1

A: R1 = R2+R3

B: R4 = R5+R6

C: R7 = R8 \* R9

D: R10= R11 \*R12

E: R13 = R1+R4+R7+R10

### รูปที่ 3.1 โค้ดและตัวอย่าง DFG

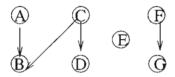

ในรูปที่ 3.1 แสดงโค้ดด้วอย่างที่ประกอบด้วย operation และ DFG ที่สัมพันธ์กัน ในกราฟ นี้ประกอบด้วย 5 โหนด โหนด A,B,E เป็น operation การบวกและ โหนด C,D เป็น operation การคูณ กล่าวคือ  $V = \{A,B,C,D,E\}, \mathcal{E} = \{A \rightarrow E,B \rightarrow E,C \rightarrow E,D \rightarrow E\}$ . และ  $\beta(A) = \beta(B) = \beta(E) = \text{add}$  และ  $\beta(C) = \beta(D) = \text{multiply}$

operation ใน DFG จะสามารถถูกคำนวณในหน่วยคำนวณต่างๆ รูปแบบกันได้ ดังนั้นจะ หมายถึงว่าผู้ออกแบบสามารถเลือกหน่วยคำนวณได้หลายรูปแบบสำหรับ operation หนึ่งๆ ซึ่ง จะหมายถึงว่าในการออกแบบนั้นจะมีความไม่แน่นอนของการเลือกหน่วยคำนวณมาใช้ด้วยนั่น เอง

สำหรับเงื่อนไขสำหรับผลลัพธ์การออกแบบนั้น อาจจะได้แก่ข้อจำกัดด้านการใช้พลังงาน และข้อจำกัดด้านต้นทุนการผลิต ข้อกำหนดทั้งหลายนี้จะถูก model ได้ด้วย tuple  $S = (\mathcal{F}, A, \mathcal{M}, \mathcal{Q})$  โดย  $\mathcal{F}$  หมายถึง เซดของประเภทของหน่วยคำนวณที่มีอยู่ในระบบทั้งหมด เช่นอาจจะหมายถึงเซ็ตของ ด้วบวกและด้วคูณ $\mathcal{F} = \{add. mul\}$  และ A หมายถึง  $\{A_\ell: \forall \ell \in \mathcal{F}\}$

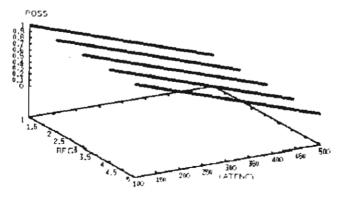

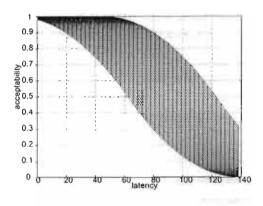

การใช้ฟังก์ชัน Q ในการนิยามระดับการยอมรับได้ (acceptability level) ของระบบนั้นมี ประโยชน์หลายอย่าง เช่น สามารถแสดงถึงขอบเขดเงื่อนไขของระบบผลลัพธ์ และสามารถ แสดงถึง design goal ที่มีครอบคลุมถึงปัจจัยความต้องการหลายด้าน ตัวอย่างเช่น ผู้ออกแบบ อาจจะสนใจระบบผลลัพธ์ที่มีทำงานได้ในเวลาไม่เกิน 500 หน่วยเวลาและจำนวนรีจิสเตอร์ที่ใช้ ไม่เกิน 6 และถ้าใช้เวลาในการทำงานและจำนวนรีจิสเตอร์ยิ่งน้อยก็จะพึงพอใจมากขึ้น ระบบที่ ดีที่สุด (ideal system) อาจจะมีเวลาในการทำงานน้อยกว่า 100 หน่วยเวลา และใช้จำนวนรีจิส เตอร์เท่ากับ 1 ความต้องการดังกล่าว model ได้ด้วยฟังก์ชัน 🗵 🗓 ๑ังนี้

$$Q(a_1, a_2) = \begin{cases} 0 & \text{if } a_1 > 500 \text{ or } a_2 > 6\\ 1 & \text{if } a_1 \le 100 \text{ and } a_2 \le 1\\ F(a_1, a_2) & \text{otherwise.} \end{cases}$$

(2.1)

โดยที่ F เป็น linear function และหมายถึง R[a1, az] = 1.249689(a1 + 2az) - 0.001242 ซึ่ง จะให้ค่าระดับการยอมรับได้ระหว่าง [0..1]

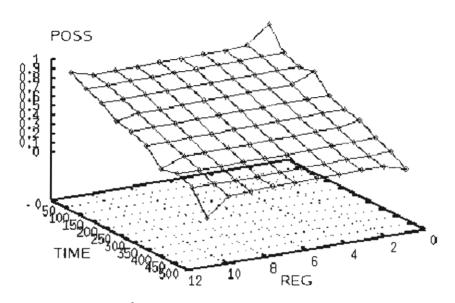

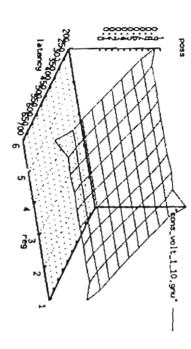

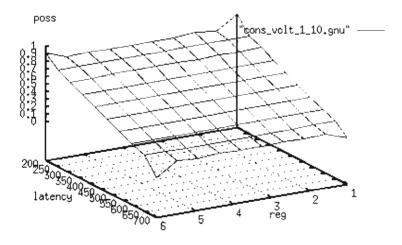

รูปที่ 3.2 แสดงการพลอตของฟังก์ชัน Q ข้างดัน ซึ่งแสดงถึง weighted sum ของคุณ ลักษณะทั้งสองโดยให้ความสำคัญในการลดจำนวนรีจิสเตอร์มากกว่าการลดเวลาในการทำงาน เป็น 2 เท่า (register count: latency = 1:2) อีกนัยหนึ่งคือสามารถยินยอมให้เพิ่มเวลาในการ ทำงาน 2 หน่วยเวลาถ้าสามารถลดจำนวนรีจิสเตอร์ได้ 1 ตัว รูปที่ 2.3 แสดง projection ของรูป 2.2 ในการ possibility และ latency (ในที่นี้บางครั้งเรียกว่า tradeoff)

รูปที่ 3.2 การพล็อตของฟังก์ชัน กิลเ.ฉะ) - 1.24%8%(a<sub>1</sub> + 2a<sub>2</sub>) - 0.001242

รูปที่ 3.3 Projection ของรูป 3.2

ในกรณีทั่วไปจะได้ดังสมการนี้

$$Q(a_{1}, a_{2}, ..., a_{n}) = \begin{cases} 0 & \text{if } a_{1} > p_{1}_{n, a_{n}} = \text{or } a_{n} > p_{n}_{n, a_{n}} \\ 1 & \text{if } a_{1} \leq p_{1}_{n, a_{n}} = \text{and } a_{n} \leq p_{n}_{n, a_{n}} \end{cases}$$

$$F(w_{1}a_{1} + w_{2}a_{2} + ...w_{n}a_{n}) & \text{otherwise.}$$

(2.2)

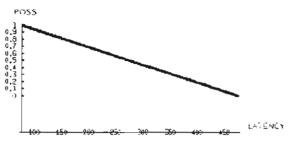

โดยที่ผู้ออกแบบอาจจะสามารถแทนที่แกน register count ด้วยปัจจัยอื่นๆ เช่น การใช้ พลังงาน (power) รูป 3.4 (a) แสดงตัวอย่างของข้อกำหนด Q เมื่อพิจารณา tradeoff ทั้งสอง ปัจจัยเป็น พา - 4 พ = 1 โดย F หมายถึงฟังก์ชัน curve รูปร่าง Z-shaped ในรูป 3.4 (b) แสดง projection ของรูป 3.4 (a) โดยแต่ละ Z-curve จะหมายถึงแต่ละ projection ของแต่ละ ฟังก์ชัน Q ในระนาบ acceptability และ possibility Curve ด้านในสุดจะหมายถึงเวลาในการ ทำงานที่น้อยที่สุดและจะมีค่าการใช้พลังงานสูงสุด ดังนั้นถ้าการออกแบบที่มีค่าระดับการยอมรับ ได้มากจะหมายถึงการออกแบบที่ optimize ตามเป้าหมายของการออกแบบมากนั่นเอง

รูปที่ 3.4 (a) Z-Shaped acceptability function (b) projection

จาก model ข้างต้น ในงานวิจัยนี้ได้พิจารณาปัญหาการจัดลำดับและการจัดสรรทรัพยากร ดังต่อไปนี้

กำหนดข้อกำหนด S = (F,A,M,Q) และกราฟ G = (V,E,B) และ α ระดับการยอมรับได้ αหาตารางการจัดลำดับภายใต้จำนวนหน่วยคำนวณและจำนวนรีจิสเตอร์ที่กำหนด สำหรับแต่ ละ f ใน F ซึ่งมีระดับการยอมรับได้มากกว่าหรือเท่ากับ α ภายใต้ Q

### 3.2 ทฤษฎีพืชชี่เชต

พืชชี่เซตกำเนิดโดย Zadeh เป็นเซตที่มีขอบเขตไม่แน่นอน (imprecise boundary) [36,37] เซตตามความหมายดั้งเดิมนั้น องค์ประกอบ (element) หนึ่งๆ จะสามารถเป็นหรือไม่ เป็นสมาชิกของเซตได้เท่านั้น อีกนัยหนึ่งจะหมายความว่าจะมีค่าฟังก์ชันสมาชิก หรือ membership degree เป็น 0 (ไม่เป็นสมาชิก) หรือเป็น 1 (เป็นสมาชิก) เท่านั้น สำหรับฟัชชี่ เซตนั้นจะสามารถให้ค่าฟังก์ชันสมาชิกสำหรับแต่ละ element ภายใต้ universe เป็นค่าที่อยู่ ระหว่าง [0..1] ซึ่งจะบอกถึง degree การเป็นสมาชิกของ element นั้นๆ ดังนั้นค่า degree ของการเป็นสมาชิก (membership value) นั้น น่เเ่: เเ่ → [0,1]

พืชซี่เชตจะเรียกว่าเป็น normal set ถ้าภายในเซตนั้นมีสมาชิกอย่างน้อยหนึ่งตัวที่มีค่า เป็น membership degree เป็น 1 ส่วน convex พืชซี่เชตจะหมายถึงพัชซี่เชตที่มี element x,y,z ใดๆ ซึ่ง × < y < z กล่าวคือ μ∆(y) ≥ min(μ∆(x),μ∆(z)) ตัวเลขพัชซี่ (fuzzy number) จะเป็น convex, normal พืชซี่เชต กำหนดให้ A, B เป็นตัวเลขพัชซี่ และมีพังก์ชัน สมาชิก μ∆(x) และ μв(y) ตามลำดับ กำหนดให้ \* เป็นการกระทำแบบ binary ซึ่งอาจจะเป็น หนึ่งใน operation ดังนี้ {+, -, ×, ÷, min, max} การกระทำทางคณิตศาสตร์ของตัวเลขพัชซี่ สองตัวเลข A,B ได้เป็นเซตใหม่และมีพังก์ชันสมาชิก A \* B คำนวณดังนี้ โดย extended principle [17]

$$\mu_{A*B}(z) = \bigvee_{z=x*y} (\mu_A(x) \wedge \mu_B(y))$$

โดยที่ V และ ^คือ operation max และ min ตามลำดับ

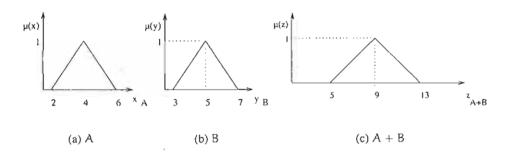

รูปที่ 3.5(a) แสดงตัวเลขฟัชชี่ A ซึ่งเป็นเซต normal และรูปแบบ triangular พิจารณาใน ช่วง universe (2..6) ๋จะเห็นค่าที่เป็นไปได้มากที่สุดของ A คือค่า 4 เนื่องจากมี ระดับความเชื่อ มั่น 1 (presumption level) และรูปที่ 3.5(b) แสดงตัวเลขฟัชชี่อีกตัว B ซึ่งมี universe อยู่ในช่วง (3,7) และรูปที่ 2.5(c) แสดงผลของการกระทำ A+B ด้วยสมการข้างต้น

รูปที่ 3.5 การบวกตัวเลขพัชซี่ A+B

ในการเปรียบเทียบตัวเลขพัชริงองร้ามีหลายวิธีที่สามารถทำได้ วิธีการด่างๆ เหล่านี้ ต่างกันที่การเลือกตัวแทนของเซตมาเบรียบเรียบ [21] วิธีการอันหนึ่งในการเลือกตัวแทนของ เซตนั้นเช่น การใช้ removal ซึ่งสัมพัทธ์กับ k จะหมายถึงระยะห่างจากค่า k คำนวณได้จาก RIA.k] = \frac{1}{2} [R\_1[A,k] + R\_r[A,k]] (สำหรับตัวเลขพัชซี่ A) โดยที่ k เป็นระยะห่างบนแกน x และ R, เป็นพื้นที่ด้านซ้ายของ curve membership function กับเส้นตรง x=k และ R, เป็นพื้นที่ ทางด้านขวาของ curve membership function กับเส้นตรง x=k อีกตัวอย่างได้แก่การใช้ mode ซึ่งจะเป็นการเลือกค่า x โดยที่ \muxi = \max t(\muxi U \text{X} t) สำหรับทุก x, และอีกตัวอย่างได้แก่การใช้ divergence ซึ่งหมายถึงความกว้างของเซตคำนวณโดย \frac{\text{X}\_{max}}{\text{X}\_max} = \frac{\text{X}\_max}{\text{min}} = \text{unarnsh} defuzzied value เป็นตัวแทนของเซตก็สามารถทำได้เช่นเดียวกัน ซึ่งวิธีการ defuzzified ได้มีหลายวิธีใน เอกสารต่างๆ [29]

จากฟัชชี่เชตดังกล่าว ในงานวิจัยนี้ได้แสดงความสัมพันธ์ระหว่างหน่วยคำนวณและค่า ความเป็นไปได้ของการที่หน่วยคำนวณนั้นจะมีคุณลักษณะหนึ่งๆ ด้วยฟัชชี่เซตของคุณลักษณะ (fuzzy set of characteristics) A, โดยกำหนดให้  $\mu_f[\mathfrak{a}] \in [0,1]$ .  $\forall \mathfrak{a} \in A_f$  หมายถึง degree ความเป็นไปได้ในการมีคุณลักษณะ a ของหน่วยคำนวณ f ซึ่งในบทความนี้จะใช้ด้วอย่างของ คุณลักษณะอันได้แก่เวลา (timing attribute) เช่น fuzzy timing attribute สำหรับหน่วย คำนวณ f ได้แก่  $\{\frac{10}{2}, \frac{20}{11}, \frac{35}{11}, \frac{70}{11}, \frac{3}{11}\}$  หมายถึงว่า f สามารถใช้เวลา 10,20,35, หรือ 70 หน่วย เวลาในการประมวลผลด้วยความเป็นไปได้  $\mu_f(10) = .2, \mu_f(20) = .4, \mu_f(35) = 1, \mu_f(70) = .7$  เป็นต้น

### บทที่ 4 Iterative Design Framework

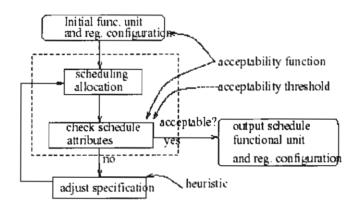

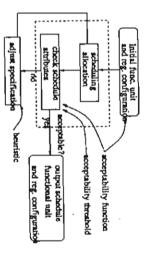

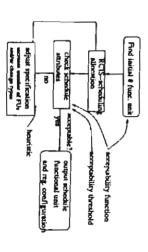

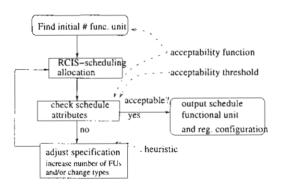

รูปที่ 4.1 แสดงภาพรวมของขั้นตอนการออกแบบแบบ iterative สำหรับการหาการออก แบบที่ใช้เลือกการออกแบบที่เป็นคำตอบที่ต้องการ นักออกแบบอาจจะเลือกตัวแบบเริ่มต้น ที่(initial design configuration) จาก heuristic เช่นจากการจัดลำดับแบบ ALAP (as late as possible) หรือ ASAP (as soon as possible) [8] ในงานวิจัยนี้อัลกอริทึม RCIS ถูกใช้ในขั้น ตอน scheduling และ allocation ในรูปนี้ ซึ่งเป็นอัลกอริทึมที่ให้ค่าคุณลักษณะแบบ imprecise ซึ่งใช้ในการตัดสินต่อไปว่าการออกแบบที่ได้เป็นที่พึงพอใจหรือไม่

รูปที่ 4.1 การหา design solution แบบ iterative

RCIS เป็นอัลกอริทึมการจัดลำดับที่ได้ใช้ข้อมูลความไม่แน่นอนเกี่ยวกับหน่วยคำนวณ มาช่วยในการจัดลำดับ โดยการป้อนอินพุตที่เป็นรูปแบบกราฟแบบ direct acyclic และป้อน จำนวนหน่วยคำนวณที่ต้องการทดลองจัดลำดับลงไป จากนั้นอัลกอริทึมจะให้ตารางการจัด ลำดับเป็นคำตอบ ซึ่งตารางนี้จะแสดงถึงลำดับการทำงานของแต่ละ operation ในกราฟใน หน่วยคำนวณที่กำหนด และคำนวณคุณลักษณะของตารางผลลัพธ์ที่ได้ด้วย จากนั้นคุณลักษณะ ดังกล่าวจะถูกนำไปตรวจสอบกับคำระดับความพอใจที่ได้เซตไว้ (acceptability threshold) หาก น้อยกว่าผู้ออกแบบจะได้ทำการปรับจำนวนและประเภทของหน่วยคำนวณที่มีอยู่และทดลองรัน อัลกอริทึมอีกครั้งต่อไป อนึ่งในการปรับจำนวนและประเภทของหน่วยคำนวณนั้นขึ้นกับลักษณะ ของงานประยุกต์หรือกราฟที่ใช้ด้วย

### บทที่ 5 Register-Constrained Inclusion Scheduling

ในบทนี้จะใต้กล่าวถึงอัลกอริทึม Register-Constraint Inclusion Scheduling (RCIS) ซึ่งอาศัย core อัลกอริทึม inclusion scheduling ตาม Algorithm 5.1 อัลกอริทึมนี้จะทำการ ตรวจสอบคุณลักษณะของตารางจัดลำดับที่ได้โดยพิจารณาถึงปัจจัยการใช้งานรีจิสเตอร์ด้วย

### 5.1 Latency-based Inclusion Scheduling

ใน inclusion scheduling นั้น จะพิจารณาคุณลักษณะแบบพัชชี่ซึ่งได้พิจารณาค่าคุณ ลักษณะด้านเวลาของแต่ละหน่วยคำนวณ สำหรับตารางจัดลำดับผลลัพธ์ที่ได้นั้นจะมีคุณ ลักษณะแบบพัชชี่ด้วย อีกนัยหนึ่งในอัลกอริทึม inclusion scheduling จะใช้การคำนวณทาง คณิตศาสตร์แบบพัชชี่มาช่วยเนื่องจากเวลาของหน่วยคำนวณแต่ละตัวเป็นตัวเลขพัชชี่ ในการบ คำเวลาสะสมแต่ละขั้นตอนจึงต้องใช้การคำนวณทางคณิตศาสตร์แบบพัชชี่นั่นเอง ผลของตัว เลขพัชชี่ที่ได้แสดงถึงคำเวลาที่เป็นไปได้ทั้งของตารางจัดลำดับผลลัพธ์ จุดเด่นของอัลกอริทึมนี้ คือการเลือกที่จะจัดสรร operation ไปยังหน่วยคำนวณหนึ่งๆ ซึ่งจะอาศัย heuristic แบบที่ ทดลองจัดสรรลงไปก่อนและคำนวณคุณลักษณะของตารางผลลัพธ์ที่ได้ และเปรียบเทียบกับการ ทดลองจัดสรรไปยังหน่วยคำนวณอื่นๆที่เหลือ และเลือกตารางผลลัพธ์ที่มีคุณลักษณะที่"ดีที่สุด" จากหลักการง่ายๆ ดังกล่าวนี้ทำให้ได้คุณลักษณะของตารางจัดลำดับผลลัพธ์ที่ละเอียดและใช้ เป็นข้อมูลในการตัดสินใจต่างๆ ได้ เช่นการเลือกใช้ module [4]

```

Algorithm 5.1 Inclusion Scheduling Input: G = (V, \mathcal{E}, \beta). Spec = (F, \mathcal{A}, \mathcal{M}, Q), and N = \#FUs Output: A schedule S, with imprecise latency

```

```

1 Q = vertices in G with no incoming edges

finding root nodes

2 while Q \neq \underline{empty do}

Q = prioritized(Q)

u = dequeue(Q); mark u scheduled

gcod_S = NULL:

<u>foreach</u> f \in \{f_i : \text{ where } f_i \text{ is able to perform } \beta(u), 1 \leq j \leq N\} \underline{do}

temp_S = assign\_heuristic(S, u, f)

assign u at FU f

if Eval_Schedule[good_S, temp_S, G, Spec]

then good_S = temp_S \underline{\mathbf{fi}} od

S = good\_S

keep good schedule

10

for each v:(u,v) \in E do

11

12

indegree(v) = indegree(v) - 1

13

if indegree (v) = 0 then enqueue (Q, v) fined

14 od

15 <u>return</u>[$]

```

อัลกอรีทึม 5.1 นี้ การคำนวณทางฟัชซี่เกิดขึ้นในฟังก์ชัน Eval\_Schedule บรรทัดที่ 8 ซึ่งจะทำการประเมินค่าคุณลักษณะของตารางหลังจากได้จัดสรร operation ให้หน่วยคำนวณ แล้ว และจะทำการเปรียบเทียบว่าดารางที่ได้มีคุณลักษณะดีกว่าดารางอื่น ๆที่ได้ทดลองมาหรือ ไม่ และจดจำตารางที่ดีที่สุดที่พบมาไว้

### Algorithm 5.2 Eval\_Schedule

```

Input: schedules S_{1*}S_{2*}, G = [\mathcal{V}_*\mathcal{E}_*\beta], and Spec = [F_*\mathcal{A}_*\mathcal{M}_*\mathcal{Q}]. Output: 1 if S_1 is better than S_2, 0 otherwise.

```

```

1 // construct a modified graph

2 G_0 = (V_0, \mathcal{E}_0, \beta) where V_0 = V—{unscheduled nodes}, \mathcal{E}_0 = \emptyset

3 foreach schedule S_1 = S_1 \text{ to } S_2 \text{ do}

\mathcal{E}_0 = \{ \{u, v\} : u, v \in \mathcal{V}_0 \} \text{ if } u, v \text{ in same f.u. in } S_1 \}

and v is immediately after u}

Sort graph G according to the topological order

n

foreach level i of graph G in topological order do

\#\gamma(u) returns the functional unit binding for u

u.aur = fuzzyadd\_time[u.attr_attr[\gamma(u)]]

9

for each u: v \to u, \forall v \in V_i, do

10

11

u.attr = hzzvmax\_time[v.attr_u.attr]

<u>od</u>

12

13

od

Let W is a set of leaves in Go.

// merge all values in quality[$4]

15

quality[S_1] = fuzzymax\_time[W]

17 od

18 # comparing the overall attributes of both schedules

19 return(compare[quality[S1], quality[S2])]

```

อัลกอริทึม 5.2 เป็นอัลกอริทึม Eval\_Schedule ซึ่งจะทำการเดิม edge ลงไปในกราฟ กลายเป็นกราฟแสดงการจัดลำดับ ถ้าโหนดสองโหนดถูกนำมาจัดลำดับต่อกันและโหนดทั้งสอง ไม่มีความสัมพันธ์กันมาก่อนในกราฟ ดังบรรทัดที่ 4 ดังนั้นตารางจัดลำดับที่ได้จะเป็นอยู่ในรูป ของกราฟอันใหม่นี้ ซึ่งแสดงลำดับการทำงานของแต่ละโหนด สมมดิให้ค่าเวลาของแต่ละหน่วย คำนวณเป็นแบบ discrete การคำนวณในบรรทัดที่ 9 จะอาศัยการกระทำแบบฟัชซี่ตามที่ได้ กล่าวในบทที่ 3 ซึ่งหมายถึงการบวก และบรรทัดที่ 11 หมายถึงการคำนวณ max

เช่นถ้ากำหนดให้ DFG โดยที่  $\mathcal{V}=\{A,B,C\}$ .  $\mathcal{E}=\{A\to C\}$  และ  $\beta(A)=\beta(B)=\beta(C)=$  add. และมีหน่วยคำนวณ  $\mathcal{F}=\{FU_1,FU_2\}$  โดยที่  $FU_1$  มีค่า ลักษณะทางด้านเวลาเป็น  $\{(5,0.05),(10,0.7),(20,0.8),(30,1)\}$  และ  $FU_2$  มีค่าลักษณะทาง ด้านเวลาเป็น  $\{(5,0.05),(15,0.5),(22,0.9),(35,11)\}$  หลังจากทำการจัดลำดับแล้วได้ ว่า A ถูก จัดสรรให้  $FU_1$  และ B ถูกจัดสรรให้  $FU_2$  เพราะถ้าจัดสรร B ให้  $FU_1$  จะได้ตารางที่มีคุณ ลักษณะไม่ดีเท่า และจัดสรร C ให้  $FU_1$  ทำให้ได้ตารางผลลัพธ์ที่มี weight latency 47.9 แต่ ถ้าจัดสรร C ให้  $FU_2$  จะได้ตารางผลลัพธ์ที่มี weight latency 52.5 ดังนั้นดารางนี้จึงเป็นตารางที่ดีกว่า สังเกตว่านี้เป็นเพียงตัวอย่างซึ่งพิจารณาแต่คุณลักษณะทางด้านเวลาเท่านั้น

### 5.2 อัลกอริทิม Register-Constrained Inclusion Scheduling

อัลกอริทึม Register-Constrained Inclusion Scheduling ดังแสดงดังอัลกอริทึม 5.3 จะ แดกต่างจากอัลกอริทึมในรูป 5.1 ในบรรทัดที่ 8 ซึ่งเป็น routine ที่ใช้ประเมินว่าตารางจัดลำดับ ที่ได้ดีหรือไม่เมื่อพิจารณาปัจจัยรีจิสเตอร์มาเกี่ยวข้องแล้ว

```

Algorithm 5.3 Register-Constrained Inclusion Scheduling (RCIS) Input: G = [V_* \mathcal{E}_* \beta]. Spec = [F_* \mathcal{A}_* \mathcal{M}_* \mathcal{Q}], and N = \#FUs

```

Output: A schedule \$, with imprecise latency

```

I/Q = vertices in G with no incoming edges

# finding root nodes

2 while Q \neq \underline{empty do}

\mathbf{Q} = prioritized[\mathbf{Q}]

\mathbf{u} = dequeue(\mathbf{Q}): mark \mathbf{u} scheduled

good_S = NULL;

<u>foreach</u> f \in \{f_i : \text{where } f_i \text{ is able to perform } \beta(u), 1 \leq j \leq N\} \underline{do}

temp_S = assign\_heuristic(S, u, f)

# assign war LU f

if Eval_Schedule_with_Reg[good_S_temp_S_G_Spec]

then 200d_S = temp_S fi od

10

$ = good_S

# keep good schedule

foreach v: [u, v] ∈ E do

II

1)

indegree[\mathbf{v}] = indegree[\mathbf{v}] - 1

13

if indegree |v| = 0 then enqueue |Q, v| is od

14 od

15 return|S|

```

ซึ่งในการพิจารณาปัจจัยรีจิสเตอร์มาเกี่ยวข้องนั้นมีความซับซ้อนอยู่มาก เนื่องจากเวลาของ แต่ละ operation หรือโหนดเป็นรูปแบบของฟัซซี่เซตซึ่งมีค่าฟังก์ชันสมาชิกอยู่ [[4] = ] จะ หมายถึงว่าโหนดนั้นจะใช้เวลา x ด้วย possibility y ดังนั้นเวลาเริ่มต้นการทำงานของโหนดและ เวลาสิ้นสุดการทำงานของโหนดในตารางจัดลำดับนั้นจะมีค่าเป็นรูปแบบฟัซซี่เซตไปด้วย ดังนั้น ในการคำนวณหาเวลาเริ่มต้นและเวลาที่สิ้นสุดการทำงานของโหนดในรูปแบบฟัซซี่นี้ ก็จะอาศัย กราฟจัดลำดับมาช่วย ดังที่ได้อธิบายในหัวข้อที่แล้วถึงการสร้างกราฟจัดลำดับ ต่อไปนี้จะ อธิบายถึงการคำนวณการใช้งานรีจิสเตอร์ในกราฟจัดลำดับ

#### 5.2.1 Imprecise Timing Attribute

ในการคำนวณการใช้งานรีจุ๊สเตอร์แบบดั้งเดิม จำเป็นต้องพิจารณาการ life time ของ แต่ละโหนดในตารางจัดลำดับ แต่เนื่องจากในงานนี้ได้ใช้กราฟจัดลำดับแทน และโหนดแต่ละ โหนดมีเวลาเริ่มต้นและเวลาสิ้นสุดเป็นรูปแบบพัชซี่การคำนวณการใช้งานรีจิสเตอร์ต้อง พิจารณาฟังก์ชันสมาชิกด้วย ต่อนี้จะของนิยาม FST(u) และ FFT(u) ซึ่งหมายถึงพัชซี่เซตของ เวลาเริ่มต้นและฟัชซีเซตของเวลาสิ้นสดการทำงานของโหนด u ก่อน

นิยาม 5.1 กำหนดกราฟ  $G=[\mathcal{V},\mathcal{E},\beta]$  และตารางจัดลำดับ เวลาเริ่มต้นการทำงาน ของโหนด u ในกราฟ ในรูปแบบฟัชซีเซต FST(u) โดยค่าสมาชิก  $\mu_{\text{FST}}$  จะหมาย ถึงว่าโหนด u อาจจะเริ่มดัน ณ เวลา x ด้วย possibility y

สำหรับโหนดซึ่งเริ่มที่เวลา 0 ในแต่ละหน่วยคำนวณ จะให้ FST ใน = 3 ซึ่งเป็นค่า crisp

นิยาม 5.2 กำหนดกราฟ  $G=\{\mathcal{V},\mathcal{E},\beta\}$  และตารางจัดลำดับ เวลาเริ่มต้น รทำงาน ของโหนด u ในกราฟ ในรูปแบบฟัชซีเซต FFT(u) โดยค่าสมาชิก  $^{\text{ILFFT}}$  เมโ $^{\chi}$ ] =  $^{\text{IL}}$  จะหมายถึง ว่าโหนด u อาจจะสิ้นสุดการทำงาน ณ เวลา x ด้วย possibility y

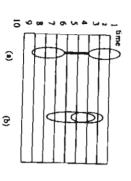

ความหมายของการใช้ตัวเลขพัชซี่เมื่อแทนค่าเวลาเริ่มต้นและเวลาสิ้นสุดเป็นดังรูป 5.1 จะเห็นว่าเวลาเริ่มต้นและเวลาสิ้นสุดเป็นเชตที่มีขอบเขตไม่แน่นอน และอาจจะทับซ้อนกันได้ใน รูป 5.1(b) ด้วย ดังนั้นเมื่อโหนดมีการใช้งานทรัพยากร ณ เวลาหนึ่งๆ จะต้องมีค่า possibility กำกับอยู่ด้วย

รูปที่ 5.1 ค่า FST(u) และ FFT(u) สองกรณี

ปกติแล้วเมื่อคำเวลาในการทำงานเป็นค่า crisp คำเวลาเริ่มดันและเวลาสิ้นสุดจะเป็นทำ ให้เกิดช่วงเวลา life time ระหว่าง [x...y] ซึ่งหมายถึงเวลาที่โหนดต้องการใช้งานรีจิสเตอร์ ระหว่างการคำนวณนั้น ในกรณีนี้เมื่อพิจารณาเป็นค่าฟัชซี่ก็จะทำให้เกิด fuzzy life time ดังนั้น จึงกำหนดให้ค่า fuzzy life time ของโหนด u ประกอบด้วยฟัชซี่เชต 2 เซตได้แก่ FST(u) และ MFFT(u) ซึ่งหมายถึงค่าเวลาเริ่มดันที่มากที่สุดที่เป็นไปได้สำหรับโหนดลูกทุกตัวของ u

สำหรับ FLT(u) กำหนดให้ min\_st เป็นค่าเวลาที่น้อยที่สุดสำหรับ FST(u) เมื่อ [ +-51 - u] > 0 และกำหนดมให้ min\_fin เป็นค่าเวลาสิ้นสุดที่น้อยที่สุดจาก MFFT(u) เมื่อ [ +-M++T - u] > 0 และ max\_fin เป็นค่าเวลาสิ้นสุดที่มากที่สุดจาก MFFT(u) เมื่อ [ +-M++T - u] > 0 สมมดิกำหนดให้ สมาชิกใน FST(u) และ MFFT(u) ถูกเรียงลำดับได้จากค่าเวลาน้อยไปมาก สร้างฟัชซี่เชตอีก

เซตได้แก่ IFST(u) ซึ่งการ map ค่าเวลาที่อยู่ในช่วง [min\_st..max\_st] ไปยังเลขจำนวนจริง [0..1] ซึ่งหมายถึงค่าความเป็นไปได้ที่โหนด u ที่กำลังรันอยู่ ณ เวลา x ที่จะใช้รีจิสเตอร์ เช่น เดียวกับ IMFFT(u) สำหรับ MFFT(u) ตามนิยาม 5.4-5.5

<u>นิยาม 5.4</u> สำหรับกราฟ G → เ≀.៩.№ และตารางจัดลำดับที่กำหนด [min\_st..max\_st] และ FLT(u)

[min\_fin..max\_fin] และ FLT(u)

จากนิยามข้างตัน สมมดิให้ ค่าเวลา a,b ∈FST(u) เมื่อ a < b ถ้าโหนด u เริ่มต้น ณ เวลา a จะได้ว่าโหนด u จะเริ่มต้นแล้ว ณ เวลา b ด้วย สำหรับ MFFT(u) เมื่อ a < b และ a,b ∈MFFT(u) ถ้าโหนด u ได้สิ้นสุดการทำงานไปแล้ว ณ เวลา a จะได้ว่าโหนด u จะก็จะสิ้นสุด การทำงาน ณ เวลา b ด้วยเช่นกัน ดังคุณลักษณะต่อไปนี้

คุณสมบัติที่ 5.1 ค่าความเป็นไปได้สำหรับ IFST(u) ถูกเรียงลำดับจากมากไปน้อย คุณสมบัติที่ 5.2 ค่าความเป็นไปได้สำหรับ IMFFT(u) ถูกเรียงลำดับจากน้อยไปมาก เมื่อได้ IFST(u) และ IMFFT(u) จากนั้นจะทำการรวมเซตทั้งสองเพื่อสร้าง fuzzy interval ด้วยนิยาม 5.6

นิยาม 5.6 สำหรับกราฟ G = (Ѵ.٤.฿) และตารางจัดลำดับที่กำหนด และ IFST(u), IMFFT(u)

คำนวณการใช้รีจีสเตอร์ได้ในแต่ละเวลา

### 5.2.2 การคำนวณการใช้งานรีจิสเตอร์

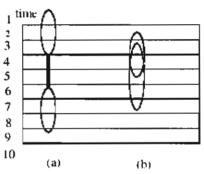

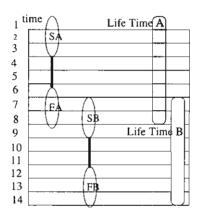

เมื่อได้ตารางจัดลำดับในรูปแบบของกราฟแล้ว จะต้องทำการคำนวณ FST(u) และ FFT(u) สำหรับ u ∈ V รูปที่ 5.2 แสดงความหมายของ fuzzy life time ตามนิยาท 4.4-4.5 โดย

SA และ FA หมายถึง FST และ FFT ของโหนะ A เซนเคียวกันสำหรับ SB และ FB หมายถึง FST และ FFT ของโหนด B และ fuzzy life time ของโหนด A และ B เป็นดังรูปด้านขวา

รูปที่ 5.2 ความสัมพันธ์ระหว่างโหนดที่ถูกจัดลำดับแล้วและ life time

ในรูปนี้ life time ของโหนด A และ B อาจจะทับซ้อนกันได้ โดยทั่วไปแล้วเมื่อค่าเวลา จะเป็นค่าคงที่ซึ่งไม่ใช่เซต การที่ช่วงเวลาทับซ้อนกันของทั้งสองโหนดหมายถึงว่าณ เวลานั้นจะ ต้องการรีจีสเตอร์ 2 ตัว จากในตัวอย่างนี้คือ ณ เวลาที่ 7 และ 8

เมื่อเวลาในการทำงานเป็นรูปแบบฟัซซี่ กล่องแต่ละกล่องในรูปจะยังคงหมายถึงว่ายัง ต้องการรีจิสเตอร์จำนวนหนึ่งตัวอยู่ แต่ว่าจะต้องมีการคำนวณค่าความเป็นไปได้ในการใช้งานรี จีสเตอร์สำหรับแต่ละช่วงเวลาด้วย ซึ่งหมายถึงว่า ณ เวลานั้นโหนดอาจจะไม่ได้รันอยู่จริงก็ได้ เช่น โหนดนั้นอาจจะเริ่มหลังจากนั้น หรืออาจจะทำงานเสร็จสิ้นไปแล้ว นั่นคือหมายถึงว่าความ เป็นไปได้ที่โหนดจะไม่ใช้รีจิสเตอร์ ณ เวลานั้น อีกนัยหนึ่งมีโอกาสเป็นไปได้ที่รีจิสเตอร์อาจจะมี การถูกใช้ร่วมกันกับโหนดอื่น พิจารณาการทับซ้อนในรูปที่ 5.2 ณ เวลาที่ 7 อาจจะมีการใช้ รีจิส เตอร์หนึ่งตัวหรือสองตัวก็ได้ ทั้งนี้ขึ้นอยู่กับว่าความสัมพันธ์  $A \to B$  เกิดขึ้นหรือไม่ ถ้า  $A \to B$  เกิดขึ้นตามกราฟ DFG หมายถึงว่าจำนวนรีจิสเตอร์ที่ใช้จะเป็นได้แค่หนึ่งเท่านั้น ซึ่งกรณีนี้เชต IFLT(A) และ IFLT(B) จะมีผลการอินเตอร์ไม่เท่ากับเซตว่าง แต่ถ้า โหนดทั้งสองไม่สัมพันธ์กัน จำนวนรีจิสเตอร์ที่ต้องการอาจจะเป็นสองตัวก็ได้แม้ว่าเซต IFLT(A) และ IFLT(B) จะมีผลการ อินเตอร์ไม่เท่ากับเซตว่าง ซึ่งทั้งสองกรณีนี้ก็ต้องถูกนำมาพิจารณาในระหว่างการคำนวณการใช้ งานรีจิสเตอร์

#### 5.2.3 อัลกอริทึม

อัลกอริทึม 5.4 อธิบายถึงการคำนวณค่าเวลาแบบ fuzzy และการคำนวณการใช้งานรี จิสเตอร์จากกราฟจัดลำดับ ซึ่งอัลกอรึทึมนี้สามารถใช้ในบรรทัดที่ 8 ของอัลกอริทึม 5.3 ได้

ในอัลกอริทึมนี้บรรทัดที่ 6 จะเรียกอัลกอริทึม 5.5 เพื่อคำนวณการ life time ของโหนด แบบฟัชซี่และหาจำนวนการใช้งานรีจิสเตอร์สูงสุดของตารางจัดลำดับนี้ ซึ่งการใช้งานรีจิสเตอร์ของตารางนั้นจะถูกเก็บไว้ใน Reg[S<sub>i</sub>] สำหรับตาราง S<sub>i</sub> และ จากนั้นจะคำนวณเวลาที่ใช้ทั้งหมด ของตารางนี้ ซึ่งหลังจากเรียกอัลกอริทึม 5.5 แล้วก็จะได้ค่าเวลาของแต่ละโหนดทั้งหมดใน

กราฟออกมา ดังนั้นเวลาที่ใช้ทั้งหมดของตารางนี้จะได้มาจากการใช้ตัวดำเริ่มการแบบฟัชซี่ สำหรับ max โดยกระทำกับเวลาสิ้นสุดของทุกโหนดในกราฟจัดลำดับที่เป็น leat ในบรรทัดที่ 9 จะทำการรวมค่าเวลาและการใช้งานรีจิสเตอร์เข้าด้วยกันโดยอาศัย heuristic function คาใหมที่ ได้จะเรียกว่าเป็นคุณภาพของกราฟจัดลำดับดังกล่าว ซึ่งก็จะถูกนำมาเปรียบเทียบสำหรับแต่ละ ตารางจัดลำดับที่ได้ในแต่ละรอบเพื่อเก็บตารางที่ดีที่สุดที่หามาได้ต่อไป

```

Algorithm 5.4 Eval Schedule with Reg

Input: schedules S_1, S_2, G = (V, \mathcal{E}, \beta), and Spec = (F, \mathcal{A}, \mathcal{M}, \mathcal{Q})

Output: 1 if S_2 is better than S_2, 0 otherwise.

I \cdot \mathsf{Go} = (\mathcal{V}_0, \mathcal{E}_{0,n}\beta) where \mathcal{V}_0 = \mathcal{V} - \{\mathsf{unscheduled nodes}\}_n \mathcal{E}_0 = \emptyset

2 foreach schedule S. = Sr to S2 do

\mathcal{E}_0 = \{(\mathbf{u}, \mathbf{v}) : \mathbf{u}, \mathbf{v} \in \mathcal{V}_0, \text{ if } \mathbf{u}, \mathbf{v} \text{ in same f.u. in } S\}

and y is immediately after u.

Calculate register usage for C_0 using Algorithm 4.3

Let W is a set of leaves in Go

latency 💆 = fuzzymax_time[W]

quality[S_{-}] = Combine([latency[S_{-}], Reg[S_{-}])

10 od

12 # comparing the overall attributes of both schedules

13 return[compare] quality[Sq], quality[Sq]]

Algorithm 5.5 Calculate Register Count

Input: Scheduled Graph G_0 for schedule S and, original DFG G = (V, \mathcal{E}, \beta) Spec = (F, A, \mathcal{M}, Q)

Output: Reg 5 contains register counts needed and its possibility

Calculate FLT(u) ∀u ∈ Go by Definition 4.3

Calculate IFLT(u) ∀u ∈ G<sub>0</sub> by Definitions 4.4–4.5

3 Let max_es be max, finished time, ∀u ∈ G<sub>0</sub>

4 for cs = \frac{1}{10} max cs do

(RegAt[cs], reg, RegAt[cs], poss) = Count[Node(IFLT[cs], G_0)] od

6 Yn FRegin = 0

7 for cs = 1 to max_cs do

FReg RegAties reg reg = RegAties reg

FReg RegAt es reg poss =

max(FReg RegAt[cs]_reg] poss, RegAt[cs] poss) od

12 Reg S - FReg

```

ในอัลกอริทึม 5.5 RegAt จะเก็บค่าจำนวนรีจิสเตอร์ที่มากที่สุดที่ต้องการ ณ แต่ละเวลา cs รวมทั้งเก็บค่าความเป็นไปได้ ค่าทั้งสองจะถูกคำนวณด้วยอัลกอริทึม 5.6 Count\_Node บรรทัด 7-10 จะคำนวณจำนวนรีจิสเตอร์ทั้งหมดที่ต้องการและค่าความเป็นไปได้

#### Algorithm 5.6. Count Node

Input: in Line es

Output: # registers needed and its possibility at @

```

I node_set == [nodes occupy reg at cs]

set Gr in topological order

Let sorted_node be node_set sorted in by sorted Go

1 pass - 0, reg - 0

5 Yi E sorted node, Lok = FALSE i.count = FALSE

o for every i ∈ sorted_node do

for j = i + 1 to last node in scrted node do

if Lok = TRUE and Leount = FALSE

reg + +: poss = max[poss, \mu_{\mathbf{E}_{a}}]

10

LCOUNT - TRUE fi

i\underline{f}\ FindPath(i_\bullet j)

13

11

then j.ok = FALSE # don't count descendant fi

15

Let j be the last node in sorted_node

16

\underline{if} j.ok = TRUE

JA

then

reg + +: poss = max(poss, \mu p : u (es)

j.count == TRUE fi

20

22 return (reg. poss)

```

ในอัลกอริทึม 5.6 จะเป็นเพียง heuristic ที่ใช้ในการพิจารณาหาโหนดที่เป็น ancestor ณ เวลาหนึ่งๆ โดยสมมติให้ ancestor นั้นทำงานเสร็จก่อนโหนดลูกก่อนที่โหนดลูกจะเริ่ม ทำงานได้ ตัว flag ok ใช้บอกว่าโหนดควรจะถูกนับไปด้วยหรือไม่ ณ เวลานั้น ถ้ามีโหนดที่เป็น ลูกหรือหลานของโหนดที่รันอยู่ ณ เวลาเดียวกัน flag จะถูกเซดเพื่อบอกว่าจะไม่นับโหนดลูก หรือหลานนั้นๆ ไปด้วย เนื่องจากดารางจัดลำดับนี้ประกอบด้วยทุกโหนดในกราฟ โหนดลูกหรือ หลานนั้นก็จะถูกนับรวมไปด้วยในที่สุด ค่า reg และ poss บอกถึงจำนวนที่นับได้ทั้งหมดและค่า ความเป็นไปได้สูงสุด บรรทัดที่ 3 โหนที่อยู่รันอยู่ ณ เวลานี้ซึ่งจะถูกเรียงลำดับตามลำดับของ topological order 1 และอัลกอริทึมจะนำโหนดออกมาจากลิสต์ที่เรียงลำดับแล้วที่ละดัวมา พิจารณาว่าโหนดโหนดนั้นมีความสัมพันธ์กับโหนดอื่นในลิสต์หรือไม่โดยฟังก์ชัน Find\_Path ใน บรรทัดที่ 13

ถ้าพิจารณาเวลาในการทำงานทั้งหมดของอัลกอริทึมนี้จะได้ว่า เวลาที่ใช้ส่วนใหญ่จะอยู่ ที่บรรทัด 6-21 ซึ่งคือ <sup>OllV]-[I][]</sup> สำหรับ DAG และฟังก์ชัน Find\_Path ใช้เวลา OllV] - [I][

ในอัลกอริทึม 5.5 การคำนวณ FLT(u) ขึ้นกับว่า FST(u) และ MFFT(u) เป็นเชตมี จำนวนสมาชิกเท่าไร ถ้าให้ N₁ เป็นจำนวนสมาชิกของ FST(u) และ MFFT(u) บรรทัดที่ 1-2 จะ ใช้เวลาในการคำนวณเท่ากับ O(N IVIEIT และการคำนวณสำหรับ IFLT(u) จะอาศัยลูปซ้อนลูป เท่านั้น ดังนั้น อัลกอริทึม 5.5 รันในเวลาฟังก์ชันโพลิโนเมียล

# บทที่ 6 ตัวอย่างการทำงานของ Register-Constrained Inclusion Scheduling

หลังจากได้รวมอัลกอริทึมทั้งหมดเข้าด้วยกัน เมื่อลา เริทึม RCIS แล้ว ต่อไปนี้จะนำเสนอตัว อย่างการคำนวณ FLT และตารางจัดลำดับ

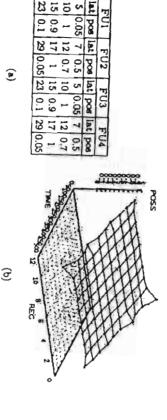

พิจารณากราฟในรูป 6.1 สมมดิว่ามีหน่วยคำนวณแบบ general purpose อยู่ 4 ตัว โดยให้ FU1, FU3 มีลักษณะเหมือนกัน และ FU2, FU4 มีลักษณะเหมือนกันเช่นกันดังดาราง 6.1 ใน รูปคอลัมน์ (lat,poss) แสดงถึงเวลาและค่าความเป็นได้ของเวลานั้นถ้าโหนดมารันในหน่วย คำนวณดังกล่าว

รูปที่ 6.1 กราฟตัวอย่าง

| FUs     | (lat.poss) |      | (lat | (lat.poss) |     | .poss) | (lat,poss) |      |

|---------|------------|------|------|------------|-----|--------|------------|------|

|         | lat        | poss | lat  | poss       | lat | poss   | lat        | poss |

| FULFU3  | 5          | 0.05 | 10   | l          | 15  | 0,9    | 23         | 0.1  |

| FU2.FU4 | 7          | 0.5  | 12   | 0.7        | 17  | 1      | 29         | 0.05 |

ตารางที่ 6.1 แสดงคุณลักษณะของหน่วยคำนวณ

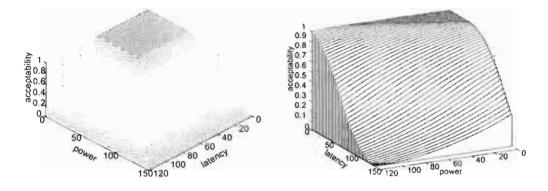

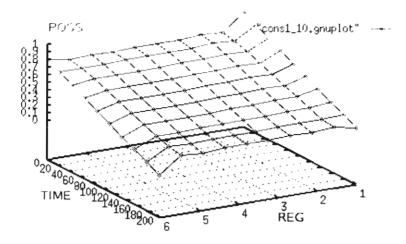

กำหนดให้ระบบที่ต้องการมีคุณลักษณะดังรูปที่ 6.2 โดยแกนรีจิสเตอร์อยู่ระหว่าง [1..7] และค่าเวลาอยู่ในช่วง [1..200] ซึ่งในรูปนี้ได้ใช้ weighted sum เช่นเดียวกับสมการ (2.1) เมื่อ กำหนดสัดส่วน (latency:register count)=1:10

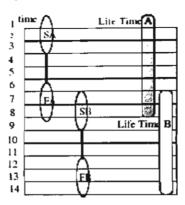

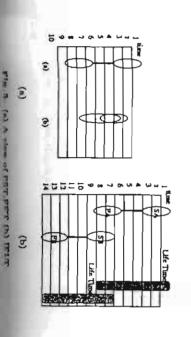

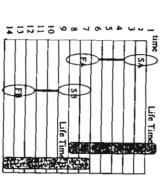

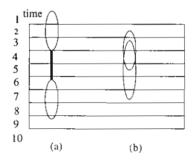

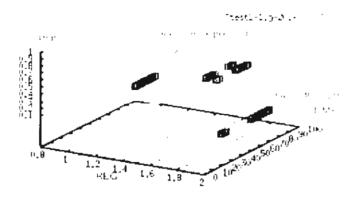

ในจากบทที่แล้วรูป 6.3 (a) แสดงตารางจัดลำดับที่ได้และสังเกตว่า FU1 และ FU3 จะ เป็นหน่วยคำนวณที่น่าใช้มากกว่า ในการคำนวณ FST(u) สมมดิให้โหนดเริ่มต้นทำงานได้เร็วที่ สุดเท่าที่จะทำได้ พิจารณาโหนด B ในดาราง รูป 6.4 (a) แสดง FLT(A) และ MFFT(A) รูป 6.5(b) แสดง FLT(B) สำหรับ FST(A) ค่าความเป็นไปได้ ณ เวลา x หมายถึงค่าความเป็นไปได้ที่โหนด A จะใช้รีจิสเตอร์หนึ่งตัว ณ เวลา x (จากรูปสี่เหลี่ยมในตาราง) เช่น กันสำหรับ MFFT(A) จะหมายถึงค่าความเป็นไปได้สำหรับโหนด A ที่จะสิ้นสุด ณ เวลา x สำหรับทั้งสอง โหนด A และ B ที่ไม่ขึ้นแก่กัน รูป 6.5 เปรียบเทียบ FLT(A) และ FLT(B) จะพบว่า FST(B) จะ ทับซ้อนกับ MFFT(A) รูป 6.6 แสดง FLT สำหรับทุกโหนด

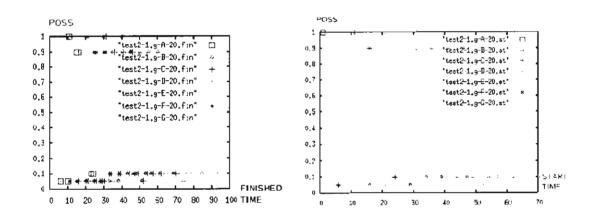

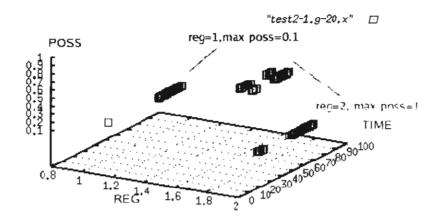

ค่า register count และค่าความเป็นไปได้ ณ เวลาต่างๆ แสดงในรูปที่ 6.7 จากรูปสรุป ได้ว่าการใช้งานรีจีสเตอร์เป็นดังนี้ (1,0.1) และ (2,1) ซึ่งหมายถึงว่าบางครั้งอาจจะมีการใช้ จำนวนรีจิสเตอร์เพียง 1 ตัวด้วยความเป็นไปได้ 0.1 และค่าเวลาสิ้นสุดที่มากที่สุดที่เป็นไปได้ จากตารางจัดลำดับนี้ได้แก่ 92 ด้วยความเป็นไปได้ 0.1 พิจารณา weighted sum ของเวลาทั้ง หมดที่ใช้และการใช้งานรีจิสเตอร์เป็น 79.53 ซึ่งค่าเฉลี่ยของเวลาอยู่ที่ 52 เปรียบเทียบเงื่อนไข

ค้านเวลาในรูป 6.2 แล้วพบว่าถ้าเวลาที่ใช้ทั้งหมดของตารางจัดลำดับเป็น 52 และใช้จำนวนรีจิส เตอร์เป็น 2 ตัวจะได้ acceptability degree เท่ากับ 0.76 ซึ่งจะเห็นว่าค่าความพึงพอใจดังกล่าว ใกล้เคียงกับที่ได้เมื่อใช้ inclusion scheduling ซึ่งได้เวลาทั้งหมดเป็น 41 ก็จะได้ acceptability degree 0.76 เช่นกัน ซึ่งในกรณีนี้จะใช้จำนวนรีจิสเตอร์เท่ากับ 3 ตัว ตารางนี้เป็นดังรูป 6.3(b)

รูปที่ 6.2 System Specification สำหรับกราฟตัวอย่าง

| FU1 | FU2 | FU3 | FU4 | Ι. |     |          |     |     |  |  |

|-----|-----|-----|-----|----|-----|----------|-----|-----|--|--|

|     | 10- |     |     | П  | FU1 | FU2      | FU3 | FU4 |  |  |

| A   | -   | E   | -   | Н  | Α   | F        | Е   | _   |  |  |

| F   | -   | C   |     | П  | _   | <b>'</b> | -   | '   |  |  |

| G   |     | D   |     | П  | G   | -        | C   |     |  |  |

| ٠   | ١.  |     |     | П  | В   |          | D   | -   |  |  |

| B   | -   | -   | -   | ľ  |     |          |     |     |  |  |

|     | (8  |     |     | •  | (b) |          |     |     |  |  |

|     | (8  | ,   |     |    |     |          |     |     |  |  |

รูปที่ 6.3 (a) ตารางจัดลำดับที่ได้จาก RCIS (b) ตารางจัดลำดับที่ได้ inclusion scheduling

รูปที่ 6.5 FLT (A) และ FLT(B)

รูปที่ 6.6 FLT สำหรับทุกโหนดในกราฟ (a) FST (b) MFFT

รูปที่ 6.7 Register count และค่าความเป็นไปได้ ณ เวลาต่าง ๆ

หากเดิมโหนดเข้าไปในกราฟอีก เป็นกราฟใหม่ดังรูป 6.8 และใช้ system specification เช่นเดิมและลักษณะทางหน่วยคำนวณเหมือนเดิม RCIS จะให้ตารางซึ่งใช้เวลาเฉลี่ยทั้งหมด 57 และจำนวนรีจิสเตอร์ที่ใช้ทั้งหมดเท่ากับ 2 ตัว ทำให้ได้ acceptability degree เท่ากับ 0.74 เทียบกับ inclusion scheduling ซึ่งให้ค่าเฉลี่ยเวลาเท่ากับ 37 และใช้จำนวนรีจิสเตอร์ทั้งหมด เท่ากับ 4 ตัวที่ให้ค่า acceptability degree เท่ากัน

รูปที่ 6.8 กราฟใหม่เมื่อเติมโหนดเข้าไป

# บทที่ 7 ผลการทดลอง

ในที่นี้พิจารณาผลการทดลอง โดยการสำรวจการออกแบบสำหรับ benchmark Discrete Cosine Transform (DCT) [12] และ Volter filter [8]

#### 7.1 Discrete Cosine Transform

ตัวอย่าง DCT นี้ประกอบด้วย 48 โหนด ซึ่งสมมติให้แต่ละหน่วยคำนวณมีลักษณะดังในตา ราง 7.1 และ system specification เป็นดังรูป 7.1 โดยให้แกนรีจิสเตอร์อยู่ในช่วง [1..12] และ แกนเวลาอยู่ในใช่วง [1..500] ตาราง 7.2 แสดงผลการทดลองโดยเปรียบเทียบกรณีต่างๆ ของ จำนวนหน่วยคำนวณที่ต่างๆ กัน คอลัมน์ RCIS และ IS แสดงการเปรียบเทียบการทำงานของ ตารางที่ได้จากอัลกอริทึม RCIS และ inclusion scheduling แถว Avg Latency แสดงถึง weighted sum ของ latency เพียงอย่างเดียว แถว Max Reg แสดงจำนวนรีจิสเตอร์สูงสุดที่ ต้องการ แถว acceptability แสดง ค่า acceptability degree ของค่า (Avg Latency,Max Reg) แถว Max Latency แสดงค่าเวลาที่มากที่สุดที่เป็นไปได้ และแถว Avg Weight แสดงค่า weighted sum ของ RCIS และ IS โดยสำหรับ RCIS  $w_1$ =1 และ  $w_2$  = 10 สำหรับ IS ค่านี้จะ เหมือนกันกับค่าในช่อง Avg Latency เนื่องจาก IS จะพิจารณาการลดค่าเวลาเป็นหลัก ตาราง 7.3-7.4 แสดงค่าความเป็นไปได้ของการใช้รีจิสเตอร์แต่ละจำนวนสำหรับ RCIS และ IS ซึ่งจะ พบว่า IS จะพยายามลดค่าเวลาที่ใช้ทั้งหมดของตารางจัดลำดับโดยไม่คำนึงถึงการใช้งานรีจิส เตอร์ ซึ่งจากตารางทั้งหมดสรุปได้ว่า RCIS จะให้ค่า acceptability degree ที่เท่าๆ กับ IS หรือ ดีกว่า โดยพิจารณาการใช้งานรีจิสเตอร์ ทำให้ใช้งานรีจิสเตอร์ไปประหยัดกว่ามากถึง 37 % ใน กรณีการออกแบบโดยใช้ adder 7 ตัว และ multiplier 5 ตัว ซึ่งจากกรณีต่างๆ ที่ทดลองทั้งหมด พบว่ากรณี การใช้ adder 5 ตัว และ multiplier 4 ตัว เป็นกรณีที่ให้ค่า acceptability degree สูง สุด ในการทดลองทั้งหมดดังกล่าว การทดลองที่ใช้เวลานานที่สุดได้แก่ กรณีที่ใช้ adder 7 ตัว และ multiplier 5 ตัว โดยใช้เวลาทั้งหมดประมาณ 1 นาที่ 50 วินาที่ บนเครื่อง Pentium IV 1.8 GHz 1GB RAM

| FU's       | (lat.poss) |      | (lat,poss) |      | (lat | ,poss) | (lat,poss) |      |

|------------|------------|------|------------|------|------|--------|------------|------|

|            | .lat       | poss | lat        | poss | lat  | poss   | lat        | poss |

| Adder      | .5         | 0.05 | 10         | 1    | 15   | 0.9    | 23         | 0.1  |

| Multiplier | 7          | 0.5  | 12         | 0.7  | 17   | 1      | 29         | 0.05 |

ตารางที่ 7.1 ลักษณะของ adder และ multiplier

|               | 5 adds | 4 muls | 6 adds 4 muls |      | 6 adds 5 muls |       | 7 adds 4 fra s |       | = idds 5 muls |       |

|---------------|--------|--------|---------------|------|---------------|-------|----------------|-------|---------------|-------|

|               | RCIS   | IS     | RCIS          | 18   | RCIS          | IS    | RCIS           | 15    | RCIN          | - 21  |

| Avg Latency   | 122    | 111    | 132           | 98   | 117           | 99    | 124            | i     |               | 1+4   |

| Max Reg       | 6      | 8      | 7             | 10   | 8             | 10    | 7              | 10    | -             | 11    |

| Acceptability | 0.719  | 0.704  | 0.69          | 0.69 | 0.694         | 0.691 | 0.699          | 0.683 | 0.691         | 0.683 |

| Max Latency   | 226    | 252    | 296           | 224  | 213           | 197   | 255            | 226   | 230           | 179   |

| Avg Weight    | 188    | 111    | 198           | 98   | 206           | 99    | 210            | 104   | 209           | 94    |

ตารางที่ 7.2 ผลการทดลองของ DCT เปรียบเทียบ RCIS และ IS สำหรับจำนวนหน่วยคำนวณต่าง ๆ กัน

รูปที่ 7.1 system specification ของ DCT

| #reg | 2 3 |   | 4   | 5   | 6 | 7 |

|------|-----|---|-----|-----|---|---|

| poss | 0.1 | 3 | 0.1 | 0.1 | 1 | 1 |

ตารางที่ 7.3 ค่าความเป็นไปได้สำหรับการใช้งานจำนวนรีจิสเตอร์ต่าง ๆ กัน สำหรับ กรณี adder 7ตัว และ multiplier 5 ตัว ของ RCIS

| #reg | 2    | 4    | 5 | 6    | 7 | 8   | 10 | 11 |

|------|------|------|---|------|---|-----|----|----|

| poss | 0.05 | 0.05 | 1 | 0.05 | 1 | 0.1 | 1  | 1  |

ตารางที่ 7.4 ค่าความเป็นไปได้สำหรับการใช้งานจำนวนรีจิสเตอร์ต่าง ๆ กัน สำหรับ กรณี adder 7ตัว และ multiplier 5 ตัว ของ IS

#### 7.2 Volter Filter

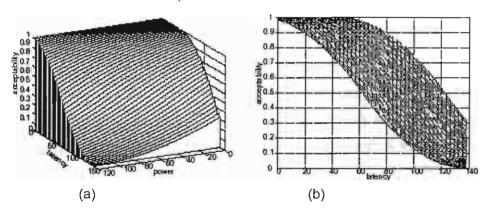

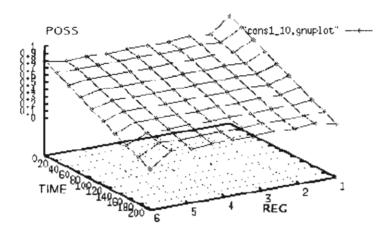

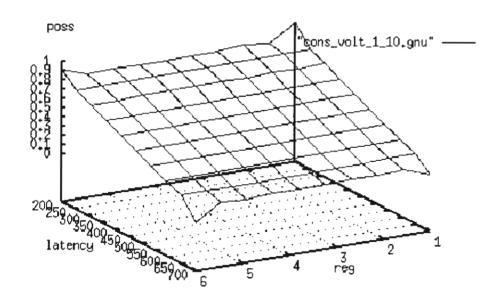

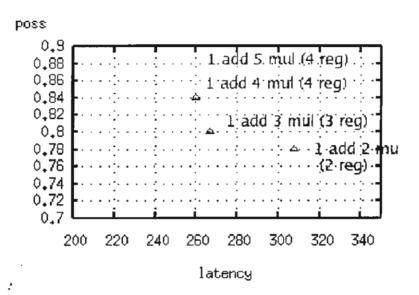

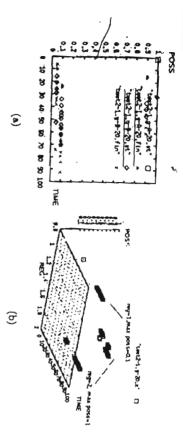

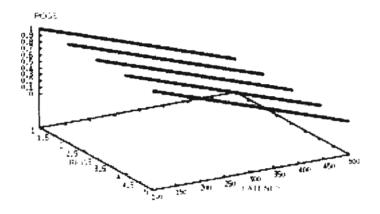

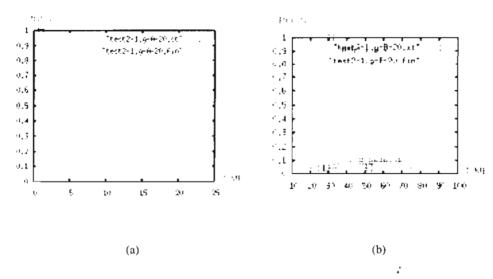

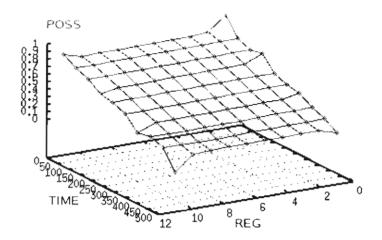

ใน benchmark นี้ประกอบด้วย 27 โหนดโดย 10 โหนดเป็นโหนดที่ต้องการหน่วย adder และ ที่เหลือต้องการ multiplier สมมดิให้ระบบประกอบด้วย adder และ multiplier ที่มี ลักษณะเช่นเดียวกับในการทดลองแรก กำหนด system specification เป็นดังรูป 7.2 โดยให้แก นรีจิสเตอร์อยู่ในช่วง [1..7] และแกนเวลาอยู่ในใช่วง [200..700] เนื่องจากลักษณะของกราฟ ประกอบด้วยโหนดที่ต้องการ multiplier มากและโหนดเหล่านี้ส่วนใหญ่ไม่ขึ้นแก่กัน จึงทำให้การ จะมีทำให้ได้ดารางจัดลำดับที่ใช้เวลาลดลง เพิ่มจำนวน สมมติให้พิจารณา multiplier acceptability threshold เท่ากับ 0.8 และ  $w_1$ =1 และ  $w_2$  = 10 โดย RCIS พยายามจะสร้างตา รางซึ่งลดค่า weighted sum ของค่าเวลาและการใช้งานรีจิสเตอร์ w<sub>1</sub>x+ w<sub>2</sub> y เมื่อ x,y เป็นค่า เวลาและจำนวนรีจิสเตอร์ของตารางที่ได้ตามลำดับ รูปที่ 7.4 แสดง acceptability degreeที่ได้ สำหรับแต่ละการออกแบบสำหรับ RCIS เมื่อได้เพิ่มจำนวนหน่วยคำนวณจะพบว่าเวลาที่ใช้ของ ตารางจัดลำดับที่ได้จะลดลงด้วย จนถึงกรณีเมื่อเพิ่ม multiplier เป็น 4 ตัวหรือมากกว่า RCIS จะให้ดารางจัดลำดับที่ให้ค่า acceptability degree 0.84 ซึ่งมากกว่า acceptability threshold 0.8 ที่ต้องการ และเมื่อตรวจสอบตารางจัดลำดับก็จะพบว่าการเพิ่ม multiplier ต่อไปจะทำให้ค่า acceptability degree ลดลงด้วยเนื่องจากจะมีการใช้งานจำนวนรีจิสเตอร์ที่มากขึ้น ซึ่งต่างจาก IS ที่จะะพยายามเพิ่มจำนวน multiplier โดยไม่คำนึงถึงจำนวนรีจิสเตอร์ที่เพิ่มขึ้นตามว่าจะมีผล กระทบกับ acceptability degree ที่ลดลงไป

จากผลการทดลอง จะพบว่า RCIS จะให้การออกแบบผลลัพธ์ที่ดีกว่าโดยใช้จำนวนรีจิส เตอร์น้อยกว่า สำหรับเวลาในการทำงาน กรณีที่ช้าที่สุดในการทดลองชุดนี้ใช้เวลา 2.8 วินาที นั่นคือกรณี adder 1 ตัว และ multiplier 5 ตัว

รูปที่ 7.2 System Specification ของ Voltera filter

|               | 1 add . | 2 muls | Ladd | Smils | 1 add | 4 muls | Ladd: | 5 muls |

|---------------|---------|--------|------|-------|-------|--------|-------|--------|

|               | RCIS    | IS     | RCIS |       | RCIS  | IS     | RCIS  | 18     |

| Avg Latency   | 308     | 3()()  | 267  | 270   | 260   | 260    | 260   | 246    |

| Max Reg       | 2       | 2      | 3    | 3     | 4     | 4      | 1     | 5      |

| Acceptability | 0.78    | 0.80   | 0.84 | 0.84  | 0.84  | 0.84   | 0.84  | 0.84   |

| Max Latency   | 561     | 561    | 474  | 477   | 445   | 445    | 445   | 416    |

## ตารางที่ 7.5 ผลการทดลองของ Voltera filter เปรียบเทียบ RCIS และ IS สำหรับจำนวน หน่วยคำนวณต่าง ๆ กัน

รูปที่ 7.3 ค่า acceptability degree ของแต่ละการออกแบบ

## บทที่ 8 สรุปผล

ในงานวิจัยนี้ได้นำเสนอ framework เพื่อสำรวจการออกแบบโดยพิจารณาถึงปัจจัย ความไม่แน่นอน โดย framework นี้ได้อ้างอิงถึงการจัดลำดับ RCIS ซึ่งได้พิจารณาความไม่แน่ นอนใน system specification และเงื่อนไข ซึ่งจะพยายามที่จะสร้างตาราจัดลำดับที่ใช้เวลาใน การทำงานน้อยที่สุดและมีการใช้งานรีจิสเตอร์น้อยที่สุด framework ดังกล่าวได้สามารถนำไปใช้ ในการสร้างการออกแบบภายใต้ปัจจัยความไม่แน่นอนด่างๆ และเลือกตัวออกแบบที่เหมาะสม ยอมรับได้ภายใต้เงื่อนไขเวลาและการใช้งานรีจิสเตอร์ ในงานวิจัยนี้ได้ทดสอบผลการออกแบบที่ เลือกโดยใช้ benchmark Discrete Cosine Transform และ Voltera filter ซึ่งพบว่าจะให้ผลการ ออกแบบที่เหมาะสมตามระดับความพึงพอใจที่ต้องการได้

## เอกสารอ้างอิง

- [1] I. Ahmad, M. K. Dhodhi, and C.Y.R. Chen. Integrated scheduling, allocation and module selection for design- space exploration in high-level synthesis. *IEEE Proc.-Comput. Digit. Tech.*, 142:65.71, January 1995.

- [2] Cagdas Akturan and Margarida F. Jacome. RS-FDRA a register sensitive software pipelining algorithm for embedded VLIW processors. *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, 12(21):1395.1415, December 2002.

- [3] C. Chantrapornchai, E. H. Sha, and X. S. Hu. Efficient scheduling for imprecise timing based on fuzzy theory. In *Proceedings of Midwest Symposium on Circuits and Systems*, pages 272.275, 1998.

- [4] C. Chantrapornchai, E. H. Sha, and X. S. Hu. Efficient algorithms for Finding highly acceptable designs based on module-utility selections. In *Proceedings of the Great Lake Symposium on VLSI*, pages 128.131, 1999.

- [5] C. Chantrapornchai, E. H-M. Sha, and X. S. Hu. Efficient module selections for Finding highly acceptable designs based on inclusion scheduling. *J. of System Architecture*, 11(4):1047.1071, 2000.

- [6] C. Chantrapornchai, E. H-M. Sha, and Xiaobo S. Hu. Efficient acceptable design exploration based on module utility selection. *IEEE Trans. on Computer Aided Design of Integrated Circuits and Systems*, 19:19.29, Jan. 2000.

- [7] C. Chantrapornchai, W. Surakumpolthorn, and E.H. Sha. Efficient scheduling for design exploration with imprecise latency and register constraints. In Lecture Notes in Computer Science! 2004 International Conference on Embedded and Ubiquitous Computing (EUC), pages 259.270, 2004.

- [8] C. Chantrapornchai and S. Tongsima. Resource estimation algorithm under impreciseness using inclusion scheduling. *Intl. J. on Foundation of Computer Science*, *Special Issue in Scheduling*, 12(5):581.598, 2001.

- [9] S. Chaudhuri, S. A. Bylthe, and R. A Walker. An exact methodology for scheduling in 3D design space. In *Proceedings of the 1995 International Symposium on System Level Synthesis*, pages 78.83, 1995.

- [10] S. Chaudhuri and R. Walker. Computing lower bounds on functional units before scheduling. In *Proceedings of the International Symposium on System Level Synthesis*, pages 36.41, 1994.

- [11] A. Dani, V. Ramanan, and R. Govindarajan Register-sensitive software pipelining. In *Proceedings, of the Merged 12th International Parallel Processing and 9th International Symposium on Parallel and Distributed Systems*, pages 194.198, April 1998.

- [12] M. K. Dhodhi, F. H. Hielscher, R. H. Storer, and J. Bhasker. Datapath synthesis using a problem-space genetic algorithm. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 14(8):934.944, August 1995.

- [13] A. Eichenberger and E. S. Davidson. Register allocation for predicated code. In *Proceeding of MICRO*, 1995. [14] Alexandre E. Eichenberger and Edward S. Davidson. Stage scheduling: A technique to reduce the register requirements of a modulo schedule. In *Proceedings of MICRO-28*, pages 338.349, 1995.

- [15] H. Esbensen and E. S. Kuh. Design space exploration using the genetic algorithm. In *Proceedings of the 1996 International Symposium on Circuits and Systems*, pages 500.503, 1996.

- [16] F.Chen, S. Tongsima, and E. H. Sha. Loop scheduling algorithm for timing and memory operation minimization with register constraint. In *Proceedings of SiP'98*, 1998.

- [17] K. Gupta. Introduction to fuzzy arithmetics. Van Nostrand, 1985.

- [18] O. Hammami. Fuzzy scheduling in compiler optimizations. In *Proceedings of the ISUMA-NAFIPS*, 1995.

- [19] I. Karkowski. Architectural synthesis with possibilistic programming. In *HICSS-28*, January 95.

- [20] I. Karkowski and R. H. J. M. Otten. Retiming synchronous circuitry with imprecise delays. In *Proceedings of the 32nd Design Automation Conference*, pages 322.326, San Francisco, CA, 1995.

- [21] A. Kaufmann and M. M. Gupta. Fuzzy mathematical models in engineering and management science. North-Holland, 1988.

- [22] A. S. Kaviani and Z. G. Vranesic. On scheduling in multiprocessor systems using fuzzy logic. In *Proceedings of the International Symposium on Multiple-valued Logic*, pages 141.147, 1994.

- [23] J. Lee, A. Tiao, and J. Yen. A fuzzy rule-based approach to real-time scheduling. In *Proceedings of Intl. Conf. FUZZ-94*, volume 2, 1994.

- [24] Josep Llosa, Eduard Ayguade, Antonio Gonzalez, Mateo Valero, and Jason Eckhardt. Lifetime-sensitive modulo scheduling in a production environment. *IEEE Transactions on Computers*, 50(3):234.249, 2001.

- [25] Josep Llosa, Mateo Valero, and Eduard Ayguade. Heuristics for register-constrained software pipelining. In *International Symposium on Microarchitecture*, pages 250.261, 1996.

- [26] C. A. Mandal, P. O. Chakrabarti, and S. Ghose. Design space exploration for data path synthesis. In *Proceedings of the10th International Conference on VLSI Design*, pages 166.170, 1996.

- [27] K. Mertins et al. Set-up scheduling by fuzzy logic. In *Proceedings of the International Conference on ComputerIntegrated Manufacturing and Automation Technology*, pages 345.350, 1994.

- [28] J. Rabaey and M. Potkonjak. Estimating implementation bounds for real time DSP application specific circuits. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 13(6), June 1994.

- [29] T. J. Ross. Fuzzy Logic with Engineering Applications. McGrawHill, 1 edition, 1995.

## ภาคผนวก ผลงานตีพิมพ์ใน LNCS 3207 และ LNCS 3321

LNCS 3207

# Embedded and Ubiquitous Computing

International Conference, EUC 2004 Aizu-Wakamatsu City, Japan, August 2004 Proceedings

:.

| Non-uniform Set-Associative Caches for Power-Aware Embedded Processors | 207 Mindes Ad Hoc Networks | n Integrated Multichannel Selection and Dynamic Power Control | rack 3: Power-Aware Computing | Nitin Auluck, Dharma P. Agrawal | or Precedence Constrained Hard<br>eneous Multiprocessors | Satoshi Yamane, Takashi Kanatani | Yookun Cho  Reductive Probabilistic Verification Methods for Embedded | Amparison of Tie-Breaking Policies for Real-Time Scheduling  n Multiprocessor                 | Virtual Reality Based System for Remote Maintenance of Rotating Machinery                         | Providing Protected Execution Environments for Embedded  Decrating Systems Using a \( \mu\)-Kernel | Sachwa Kim, Michael Buettner, Mark Hermeling,  Seongsoo Hong | Experimental Assessment of Scenario-Based Multithreading for Real-Time Object Oriental Model | A Mobile Way-Finding Application Controlling Internet-Distributed Signaling Devices via LAN Concento | Alternative CPU Core Organizations | Component Composition Tools: Process Call Scheduling According to the Priority in Connector |   |

|------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------|-------------------------------|---------------------------------|----------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------|---|

|                                                                        |                            | Elms                                                          |                               | Track 5: Mobile Computing       |                                                          |                                  | Interconnect Cores g Applications                                     | of MPEG-2 Like Real-Time Parallel Media SP SoC Cradle Architecture  K. Singh, Vipin Chaudhary | Hardware Mediators: A Portability Artifact for Component-Based Systemsfor Component-Based Systems |                                                                                                    | R ITS                                                        | Track 4: Hardware/Software Co-design and System-on-Chip                                      | ing                                                                                                  |                                    | Non-uniform Set-Associative Caches for Power-Aware  Embedded Processors                     | • |

time the actual execution of processing for a single frame was completed within essing for a single video frame at the model simulation stage was 600sec., but in real ing, when written in C++, amounts to some 15k steps. Speed of execution of the procallocated were mainly interface processing, warning processing and control process 100msec., satisfying the design objectives.

IP modules, and we were able to use RPC to perform the functional evaluations. The driving safety support system configured in SpecC quickly detected the online

controlled car was confirmed, satisfying design objectives at speeds up to 10km. design objectives to be satisfied at the simulation level, and validation with a radio-From the above, we were able to evaluate that the proposed design method enables

## S

evaluated its effectiveness. By using modeling without separating the functions into extended the validation system to apply to the ITS system for control processing, and online method of validation using RPC to access IP components in the network envitrolled with the control system being designed. Our proposed design method uses tions to HW and SW. We performed simulations by connecting the object to be conthe method of trade-offs was used to shorten development time. HW and SW, there was no need to configure the system in multiple languages. And ronment. We confirmed the validity of this approach in an application to the design of functions called for by the design specifications to HW and SW. And we proposed an these simulations, following a staged approach to detailed design in allocating the We proposed a hardware/software co-design method of the optimal allocation of funcimage processing for ITS. We configured dynamic models for the control system,

ate the degree of effectiveness In the near future, we will apply the design method to other application and evalu-

- Hiroaki Takada "Present situation and future prospects in development technologies for embedded systems," IPSJ Journal Vol. 42, No. 4, pp. 930-938 (2001) (in Japanese) Hisso Koizumi, Katsubiko Seo, Pumio Suzuki, Yohsuke Ohsuru, and Hiroto Yassura. "A

- Proposal for a Co-design Method in Control System Using Combination of Models. EICE Trans. on Information and Systems, vol. E78-D No. 3, pp. 237-247 (1955).

Thomas D.E., Adams J.K. and Schmit H., "A Method and Method for Hardware Software

Codesign", IEEE Design and Test of Computers, Vol. 10, No. 3, pp. 6-15(1993).

Takashi Naitoh, Keiichi Yamada & Shin Yamamoto: "A robust method of numberplate 545 (1998) (in Japanese) recognition at the image taking point," IEICE Transactions A. Vol. 181-A, No. 4, pp. 536.

Daniel D. Gajski et al., The SpecC specification description language and how to use it. CQ Press K.K. (2000)

Developments in traffic systems (ITS) for dedicated express motorways: http://www.llines.or.jp/veritt/j frame.html (2002)

# Efficient Scheduling for Design Exploration with Imprecise Latency and Register Constraints

Chantana Chantrapornchai<sup>1</sup>\*, Wanlop Surakumpolthorn<sup>2</sup>, and Edwin Sha<sup>3</sup>\*\*

Faculty of Science, Silpakorn University, Nakorn Pathom, Thailand Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Thailand

3 Department of Computer Science, University of Texas, Richardson, Texas, USA

off between latency and register counts and selecting a solution with constraints, this paper proposes a polynomial-time scheduling algorithm satisfactory performance and cost. The experiments show that we can The algorithm can be used in design exploration for exploring the tradewhich minimizes both functional units and registers while scheduling formation is unavoidable. Under the imprecise system characteristics and are important steps. During the early stage of the design, imprecise in-Abstract. In archiectural synthesis, scheduling and resource allocation schieve a schedule with the same acceptable degree while saving register upto 37% compared to the traditional algorithm

## Introduction

a latency by two cycles while saving one register and what about expanding 10 is considered to be acceptable at architecture level. If a design with latency of the component may have not been completely designed down to the geometry In architectural level synthesis, imprecise information is almost unavoidable. For more cycles? Effective treatment of such impreciseness in high level synthesis there are multiple conflicting design criteria, for example, is it worth to expand 50 cycles is acceptable, what about a design with 51 cycles? Especially when level. Another kind of impreciseness or vagueness arises from the way a design instance, there may be various choices of modules implementing the functions or can undoubtedly play a key role in finding optimal design solutions.

ate a schedule subject to register constraints under impreciseness. The proposed dimension of imprecise system requirement. We extend the work in [1] to cremodeled based on the fuzzy set theory. Register count is considered as another tion and use them during architectural synthesis. The system characteristics are This work was supported in part by the TEL under grant number MRG4680115 algorithm can be integrated into design exploration framework which considers In this paper, we present an approach to handle certain imprecise specifica-

the tradeoff between latency and register usage to find an acceptable solution. Such systems can be found in many digital signal processing applications, e.g., communication switches and real-time multimedia rendering systems.

Many researchers have applied the fuzzy logic approach to various kinds of scheduling problem [10,11]. These approaches, however, do not take into account the fact that an execution delay of each job can be imprecise and/or multiple attributes of a schedule. Research works related to register allocation exists in high-level synthesis and compiler optimization area for VLIW architecture. For example, Chen et. al. proposed a loop scheduling for timing and memory operation optimization under register constraint [8]. The technique is based on multi-dimensional retiming. Eichenberger et. al. presented an approach for register allocation for VLIW and superscalar code via stage scheduling [7]. Dani et. al. also presented a heuristic which uses stage scheduling to minimize register requirement. They also target at instruction level scheduling [5]. Nonetheless, these works focus on loop scheduling and do not consider handling the imprecise system characteristics or specification.

The inclusion scheduling which takes the imprecise system characteristic was proposed in [1]. The algorithm was expanded and used in design exploration under imprecise system requirement as well as the estimation of resource bounds [2,3,4]. However, it does not take register criteria in creating a schedule.