# รายงานวิจัยฉบับสมบูรณ์

การถอดรหัสแบบหลายสแตกโดยใช้มัลติโพรเซสเซอร์ Multiprocessor-based Multiple Stack Decoding

โดย

ผศ.ดร.วิระสิทธิ์ อิ่มถวิล

ภาควิชาวิศวกรรมไฟฟ้า คณะวิศวกรรมศาสตร์

มหาวิทยาลัยขอนแก่น

# รายงานวิจัยฉบับสมบูรณ์

การถอดรหัสแบบหลายสแตกโดยใช้มัลติโพรเซสเซอร์ Multiprocessor-based Multiple Stack Decoding

ผู้วิจัย

ผศ.คร.วิระสิทธิ์ อิ่มถวิล

ภาควิชาวิศวกรรมไฟฟ้า คณะวิศวกรรมศาสตร์

บหาวิทยาลัยขอนแก่น

นักวิจัยที่ปรึกษา

ศ.คร.วัลลภ สุระกำพลธร

ภาควิชาอิเล็กทรอนิกส์

สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาคกระบัง

สนับสนุนโดยสำนักงานคณะกรรมการการอุดมศึกษา และสำนักงานกองทุนสนับสนุนการวิจัย

(ความเห็นในราชงานนี้เป็นของผู้วิจัช สกอ. และ สกว. ไม่จำเป็นต้องเห็นด้วยเสมอไป)

#### **ACKNOWLEDGEMENT**

I would like to express my gratitude to my mentor, Professor Wanlop Surakampontorn, who provided me support and encouragement throughout this research project.

I would also like to thank my present and former master degree students in the Department of Electrical Engineering, Khon Kaen University, Monkol Kupimai, Pongpaiboon Boonchai, Teera Supanon, Jariya Ponsawad, and Assawanon Noisuwan for making an active research environment.

I would like to thank the Department of Electrical Engineering, Khon Kaen University, for supporting me in carrying out this research project.

I would like to acknowledge the financial support given to me by The Thailand Research Funds and The commission on Higher Education.

Last, but not least, my most sincere thanks go to my wife, Kanokwan Imtawil, my beloved son, Wuttikorn Imtawil, and my lovely daughter, Kanika Imtawil, for their patience and support.

VIRASIT IMTAWIL

รทัสโกรงการ : MRG4680124

ชื่อโกรงการ : การถอครหัสแบบหลายสแตกโคยใช้มัลติโพรเซสเซอร์

ชื่อนักวิจัยและสถาบัน: ผศ.คร. วิระสิทธิ์ อื่มถวิล ผู้วิจัย

ภาควิชาวิศวกรรมไฟฟ้า คณะวิศวกรรมศาสตร์ มหาวิทยาลัยขอนแก่น

E-mail address : virasit@kku.ac.th

ระยะเวลาโครงการ : 1 กรกฎาคม 2546 ถึง 30 มิถุนายน 2548

วิธีการถอดรหัสแบบหลายสแตกเป็นวิธีการถอดรหัสแบบซีเควนเชียล เพื่อใช้สำหรับถอดรหัส สัญญาณที่มีการเข้ารหัสแบบคอนโวลูชัน หลักการของวิธีการถอดรหัสแบบหลายสแตก คือ สแตกจะถูก แบ่งออกเป็น 2 ส่วนใหญ่ๆ คือ สแตกหลักและสแตกรอง โดยที่มีสแตกหลักเพียงสแตกเดียวซึ่งมีขนาด ใหญ่ และมีสแตกรองอีกหลายสแตกซึ่งมีขนาดเล็ก กลไกของการถอดรหัสจะเริ่มจากการทำงานบนสแตก หลักเช่นเดียวกับการถอดรหัสแบบสแตกเดียว ในสภาวะที่มีการรบกวนจากสัญญาณรบกวนมาก บางครั้ง การถอดรหัสไม่สามารถสิ้นสุดได้ที่สแตกหลัก จำเป็นต้องย้ายโหนดบางส่วนมาทำงานในสแตกรอง จน กระทั่งการถอดรหัสสิ้นสุดลงในสแตกรอง แต่การสิ้นสุดในสแตกรอง ยังไม่ถือว่าเป็นการถอดรหัสที่มี ความถูกต้องแม่นยำสูง เนื่องจากเส้นทางการถอดรหัสที่ได้อาจจะไม่ใช่เส้นทางที่ถูกต้อง ดังนั้นถ้าเวลาที่ ตั้งไว้สำหรับการถอดรหัสยังไม่ถึงก่าลิมิต การถอดรหัสก็จะกลับมาดำเนินการที่สแตกหลัก เมื่อได้เส้น ทางการถอดรหัสที่สแตกหลักก็จะนำเส้นทางนี้มาเปรียบเทียบกับเส้นทางเดิมที่ได้ และเลือกเส้นทางที่ดี กว่าเป็นเส้นทางการถอดรหัส อย่างไรก็ตามบางครั้งพบว่า การถอดรหัสมีประสิทธิภาพที่ไม่ดีนัก

งานวิจัยนี้เป็นการประยุกต์วิธีการถอดรหัสโดยใช้มัลติโพรเซสเซอร์ทำงานไปพร้อมๆกันในวิธี การถอดรหัสแบบหลายสแตก โดยการออกแบบการทำงานร่วมกันของมัลติโพรเซสเซอร์ที่เหมาะสม สามารถที่จะเลือกจำนวนของโพรเซสเซอร์ในการถอดรหัสได้ ผลการจำลองด้วยคอมพิวเตอร์ ปรากฏว่า วิธีการถอดรหัสแบบขนานโดยใช้มัลติโพรเซสเซอร์ในวิธีการถอดรหัสแบบหลายสแตก เพื่อถอดรหัส สัญญาณที่เข้ารหัสแบบคอนโวลูชันซึ่งมีค่าความยาวคอนสเตรนท์สูง ให้ค่าอัตราความผิดพลาดบิตลดลง อย่างมาก กรณีศึกษาได้ทำการทดสอบที่จำนวนโพรเซสเซอร์เป็น 4 และ 16

คำหลัก: การถอดรหัสแบบหลายสแตก การถอดรหัสแบบขนาน การเข้ารหัสแบบคอนไวลูชั้น

#### **ABSTRACT**

Project Code: MRG4680124

Project Title: Multiprocessor-based Multiple Stack Algorithm

Investigator: Assistant Professor Dr. Virasit Imtawil

Department of Electrical Engineering.

Faculty of Engineering, Khon Kaen University

E-mail Address: virasit@kku.ac.th

Project Period: 1st July 2003 to 30th June 2005

The Multiple Stack Algorithm (MSA) is an algorithm for sequential decoding for convolutional codes. The main principle of the MSA is the stacks will be separated into 2 main groups; the main or primary stack and the secondary stacks or simply called substacks. The main stack is made large and the sub-stacks are made small. The decoding starts in the main stack as the conventional single stack algorithm (SSA). Occasionally, in a very noisy case, the decoding is not done in the main stack, some top nodes will be transferred into a sub-stack. If the decoding is terminated in the sub-stack, the decoded path will be stored as a tentative decision. This tentative path may not be the correct path. If the computational limit is not reached, the decoding will be back to the main stack. The decoding then happens in the main stack again. If the decoding is terminated in the main (first) stack before the computational limit is reached, the new decoded path will be compared with the tentative path. The better one will be chosen the decoded path. However, it is often found that the decoding, in the noisy case, is terminated with the computational limit without being back to the main stack again. When this situation happens, the decoding error probability is usually very high.

In order to improve the error performance particularly in a very noisy block which requires excessive tree searches, a parallel decoding scheme for a multiple stack algorithm (MSA) is proposed in this paper. In this scheme, apart from the main decoder working on the main stack, a scalable set of multiple decoders working in parallel on their multiple stacks are incorporated. All the decoders are working almost independently with the help of the control processor, where the decoding process and the termination rules are outlined. Two cases, 4-processor MSA and 16-processor MSA, are employed as examples to investigate the performance of the proposed scheme. Comparing with the conventional MSA, extensive computer simulations show that the bit error probabilities (BER) are significantly improved.

Key words: The multiple stack algorithm, parallel decoding, convolutional codes

## OUTPUT จากโครงการวิจัยที่ได้รับทุนจาก สกอ. และ สกว.

#### 1. ผลงานตีพิมพ์ในวารสารวิชาการระดับนานาชาติ

V. Imtawil and W. Surakampontorn, "Parallel Decoding Scheme for Multiple Stack Algorithm" Accepted to be published in IEE Proceedings: Communications (impact factor = 0.298)

### 2. การนำผลงานวิจัยไปใช้ประโยชน์

- 2.1 เชิงวิชาการ ได้มีการนำเอาผลงานวิจัยไปใช้ในการเรียนการสอนวิชา Digital Communications ในระดับปริญญาตรี และ Error Control Coding ในระดับบัณฑิตศึกษา

- 2.2 มีการสร้างและพัฒนานักวิจัยใหม่ในสาขาวิชาไฟฟ้าสื่อสารของประเทศไทย

# 3. การเสนอผลงานในที่ประชุมวิชาการ

- 3.1 V. Imtawil and W. Surakampontom, "A scalable multiprocessor-based multiple stack algorithm" บทคัดย่อใน: การประชุม "นักวิจัยรุ่นใหม่...พบ...เมธีวิจัยอาวุโส สกว." ณ โรงแรม เฟลิกซ์ ริเวอร์แคว จ.กาญจนบรี มกราคม 2548

- 3.2 V. Imtawil and W. Surakampontorn, "Parallel Decoding Scheme for Multiple Stack Algorithm" โปสเตอร์นำแสดงในงาน KKU ICT'2005 ณ หอประชุมกาญจนาภิเษก มหาวิทยาลัยขอนแก่น จ.ขอนแก่น มิถุนายน 2548

# สารบัญ

|                                                                            | Page |

|----------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENT                                                            | i    |

| บทคัดย่อ                                                                   | ii   |

| ABSTRACT                                                                   | iii  |

| OUTPUT                                                                     | iv   |

| สารบัญ                                                                     | v    |

| บทที่ เบทนำ                                                                | 1    |

| 1.1 ความเป็นมาและความสำคัญของปัญหา                                         | 1    |

| 1.2 วัตถุประสงค์                                                           | 3    |

| 1.3 ขอบเขตและข้อจำกัดของงานวิจัย                                           | 3    |

| 1.4 ผลงานวิจัยที่กาคว่าจะได้รับ                                            | 3    |

| บทที่ 2 การถอครหัสแบบหลายสแคก                                              | 5    |

| 2.1 บทน้ำ                                                                  | 5    |

| 2.2 การเข้ารหัสสัญญาณแบบคอนโวลูชั้น                                        | 6    |

| 2.3 การถอครหัสสัญญาณที่เข้ารหัสแบบคอนโวลูชัน                               | 9    |

| บทที่ 3 การถอครหัสแบบหลายสแตกโดยมัลติโพรเซสเซอร์                           | 19   |

| 3.1 บทน้ำ                                                                  | 19   |

| 3.2 รูปแบบ MSA โดยมัลติโพรเชสเชอร์                                         | 19   |

| 3.3 ผลการทคสอบโครงสร้างรูปแบบ                                              | 22   |

| 3.4 การถอครหัสแบบ MSA โคยมัลติโพรเชสเชอร์                                  | 23   |

| 3.5 การประยุกศ์การถอครหัสแบบ MSA ในรหัสแบบรีเคอร์ซีพซิสเต็มเมติกคอนโวลูชัน | 26   |

| บทที่ 4 การทคสอบและผลการทดสอบ                                              | 29   |

| 4.1 บทนำ                                                                   | 29   |

| 4.2 การจำลองระบบสื่อสารและสมมุติฐานที่ใช้ในการทดสอบ                        | 29   |

| 4.3 ผลการทคสอบประสิทธิภาพการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์กับค่าพารา   |      |

| มิเตอร์ต่าง ๆ                                                              | 30   |

| 4.4 ผลการทคสอบประสิทธิภาพการถอดรหัสแบบ MSA ในรหัสแบบรีเกอร์ชีพซิสเต็มเมดิเ | n    |

| คอนโวลูชัน                                                                 | 39   |

| บทที่ 5 สรุปงานวิจัย                                                       | 41   |

| เอกสารอ้างอิง                                                              | 42   |

| ภาคผนวก                                                                    | 43   |

# บทที่ 1 บทนำ

## I.1 ความเป็นมาและความสำคัญของปัญหา

เทคนิคการเข้ารหัสเพื่อแก้ไขความผิดพลาด (forward error correction, FEC) หรือเพื่อควบคุม ความผิดพลาดเป็นเทคนิคการเข้ารหัสข้อมูลคิจิตอลเพื่อเพิ่มประสิทธิภาพในการป้องกันสัญญาณรบกวน ที่เกิดขึ้นในช่องสื่อสาร สามารถแบ่งออกได้เป็น 2 หมวดหมู่ใหญ่ๆ คือ การเข้ารหัสแบบบล็อก (block coding) และการเข้ารหัสแบบคอนโวลูชัน (convolutional coding) รหัสคอนโวลูชันเป็นการเข้ารหัสเพื่อ แก้ไขความผิดพลาดซึ่งถูกใช้แพร่หลายในระบบสื่อสารทั้งภาคพื้นดินและผ่านดาวเทียม วิธีการถอดรหัส สัญญาณข้อมูลที่เข้ารหัสแบบคอนโวลูชันมือยู่ 2 วิธีใหญ่ๆ คือ การถอครหัสแบบวิเทอบิ (Viterbi decoding) และการถอครหัสแบบซีเควนเชียล (Sequential decoding) (Forney, 1974) งานวิจัยนี้จะเกี่ยว ข้องกับการถอครหัสแบบซีเควนเซียล ซึ่งมีข้อคีเหนือการถอครหัสแบบวิเทอบิคือสามารถใช้กับรหัสคอน โวลูชันที่มีค่าความยาวคอนสเตรนท์สูงๆได้ เนื่องจากความซับซ้อนในการคำนวณไม่ขึ้นกับค่าความยาว คอนสเตรนท์ ในขณะที่การถอครหัสแบบวิเทอบิมีค่าความซับซ้อนในการคำนวณเพิ่มขึ้นแบบเล็กโพเบบ เชียลกับค่าความยาวคอนสเตรนท์ (Lin และ Costello, 1983) และ (Haccoun และ Begin, 1989) ค้วยเหตุนี้ จึงทำให้การถอครหัสแบบซีเควนเซียลสามารถให้อัตราความผิดพลาดบิตที่ต่ำมากๆได้โดยการเพิ่มค่า ความยาวคอนสเตรนท์ของตัวเข้ารหัส อย่างไรก็ตามข้อเสียของการถอดรหัสแบบซีเควนเซียลคือค่าความ แปรปรวนในการคำนวณ (Computational variability) กล่าวคือบล็อกข้อมูลที่มีสัญญาณรบกวนน้อยจะใช้ เวลาในการถอครหัสเร็ว ส่วนบล็อกข้อมูลที่มีสัญญาณรบกวนมากจะใช้เวลาในการถอครหัสช้าและบ่อย ครั้งที่การถอครหัสไม่สามารถสิ้นสุคภายในเวลาที่กำหนด ทำให้บล็อกข้อมูลถูกลบซึ่งเรียกว่า อีเรชัว (Erasure)

ในการทบทวนเอกสารที่เกี่ยวข้องกับการถอดรหัสแบบซีเควนเซียลพบว่า มีงานวิจัยออกมามาก มายเพื่อลดปัญหาของอีเรชัว และค่าความแปรปรวนในการคำนวณ เช่นการถอดรหัสแบบฟาโน (Fano algorithm, FA) (Forney และ Bower, 1971) ซึ่งเป็นอัลกอริทึมหนึ่งของการถอดรหัสแบบซีเควนเซียลพบ พบว่าทำให้สามารถลดผลของอีเรชัว และค่าความแปรปรวนในการคำนวณได้ แต่ปัญหาก็คือการลดอีเรชัว โดยวิธีการถอดรหัสแบบฟาโนส่งผลให้อัตราความผิดพลาดบิตเพิ่มขึ้นโดยเฉลี่ย เนื่องจากการตั้งค่า backsearch limit อาจทำให้ทางเดินที่ถูกต้องในแผนภูมิต้นไม้แทนรหัส (code tree) ถูกลบไปก่อนที่ขบวน การถอดรหัสจะสิ้นสุดลง ต่อมาสถาปัตยกรรมของการถอดรหัสแบบหลายคัวประมวลผล (multiprocessor decoding system architecture) (Belanger et al.,1994) โดยใช้หลักการให้ตัวประมวลผลทำงานบนหลายๆ ทางเดินในต้นไม้แทนรหัสพร้อมๆกันด้วยโครงสร้างการทำงานที่แน่นอนของการถอดรหัสแบบสแตก The Single Stack Algorithm, SSA ผลที่ได้ในงานวิจัยนี้สามารถที่จะเปลี่ยนจำนวนของตัวประมวลผล

ตามที่ต้องการได้และการเพิ่มตัวประมวลผลก็จะได้ก่ากวามแปรปรวนในการกำนวณ ที่ลดลง แต่อย่างไรก็ ตาม อีเรชัวก็ยังไม่หมดไป

อัลกอริทึมของการถอครหัสแบบซีเควนเขียลวิธีการหนึ่งซึ่งเป็น Erasure-free Sequential Decoding Algorithm โดยใช้หลักการของหลายสแตกเรียกว่า The Multiple Stack Algorithm (MSA) (Chevillat และ Costello, 1976) ในการถอครหัสแบบ MSA จะอาศัยหลักการคล้ายๆกับ The Single Stack Algorithm, SSA (Jelinek, 1969) ต่างกันตรงที่จำนวนสแตกที่ใช้ใน MSA มีมากกว่าหนึ่งสแตกและการ ทำงานของตัวถอดรหัสจะกำหนดขนาดของสแตลออกเป็น 2 ส่วนคือ สแตลหลักหรือสแตลแรกและกลุ่ม ของสแตกรองหรือสแตกอันคับสูงซึ่งจะมีหลายสแตก โดยที่ขนาคของสแตกหลักจะโตกว่าขนาคของสแต ครองมาก ในกรณีปกติของการถอครหัสที่มีสัญญาณรบกวนน้อย การทำงานของขบวนการถอครหัสมักจะ สิ้นสุดที่สแคกหลัก จะมีเพียงบางครั้งเท่านั้นที่สแคกรองจะถูกนำมาใช้ นั่นคือในกรณีที่ช่องสื่อสารมี สัญญาณรบกวนมากซึ่งมักจะทำให้เกิดอีเรชั่ว ในกรณีนี้การทำงานของ MSA จะไม่สิ้นสุดจนกว่าค่าของ การคำนวณที่ใช้ในการถอดรหัสจะถึงค่าๆหนึ่งซึ่งถูกตั้งไว้ก่อนหน้า โดยหลักการเช่นนี้ทำให้ MSA เป็น วิธีการถอครหัสแบบ ซีเควนเชียลที่สามารถถอครหัสได้สมบูรณ์ (complete decoding) โดยไม่เกิดอีเรชัว เช่นเดียวกับการถอดรหัสแบบ VA อย่างไรก็ตามข้อด้อยของ MSA ก็คือประสิทธิภาพในอัตราความผิด พลาคบิดยังมีค่าสูงกว่าการถอครหัสแบบ VA นอกจากนั้นแล้วความต้องการของหน่วยความจำใน MSA ก็ ยังมีมากในกรณีที่ต้องการประสิทธิภาพในอัตราความผิดพลาดบิตต่ำ ซึ่งต่อมาได้มีการพัฒนาวิธีการปรับ ปรุงประสิทธิภาพของ MSA ในการใช้หน่วยความจำที่มีประสิทธิภาพมากขึ้นโดยเฉพาะในกลุ่มของสแต ครองและให้ชื่ออัลกอริทึมใหม่ว่า The modified MSA (Y. Lin และ S.H. Tu, 1997) ในวิธีการนี้ใช้วิธีการ จัคสแตกรองในรูปแบบวงแหวนเสมือน (Ring-like structure) ซึ่งการจัดหน่วยความจำลักษณะนี้ทำให้ สามารถที่จะกำหนดขนาดของสแตกรองและจำนวนโนคที่ย้ายระหว่างสแตกให้มีค่าสูงได้แต่ปัญหาที่ตาม มาของงานวิจัยลักษณะนี้คือการได้ทางเคินของการถอดรหัส (Decoded path) อาจจะใช้เวลานานและส่งผล ถึงการเกิดโอเวอร์โฟล์ (Overflow) ที่บัฟเฟอร์ด้านอินพุทได้ ต่อมา Kaiping Li และ Samir Kallel, (1999) ได้เสนอรูปแบบใหม่ของการลดอัตราความผิดพลาดบิตใน MSA โดยใช้หลักการของการลอดรหัสสองทิศ ทางและให้ชื่อว่า The bi-directional MSA ซึ่งให้อัตราความผิดพลาดบิดที่น่าสนใจเมื่อเปรียบเทียบกับ VA แต่อย่างไรก็ตามก็ยังไม่พบงานวิจัยใดที่นำเอาหลักการของตัวประมวลผลแบบหลายโหนคกับ MSA และ ศึกษาโครงสร้างของสถาปัตยกรรมที่เหมาะสมสำหรับการถอครหัสแบบ MSA ในรูปแบบของ multiprocessor architecture ซึ่งน่าจะให้ประสิทธิภาพในอัตราความผิดพลาดบิตที่คีขึ้นกว่าการถอดรหัส แบบ MSA เคิม

ในงานวิจัยนี้เรานำเสนอวิธีการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์เพื่อปรับปรุงประสิทธิ ภาพในอัตราความผิดพลาดบิตของขบวนการถอดรหัสที่ใช้ MSA ผลการทดสอบประสิทธิภาพเมื่อจำลอง ระบบด้วยคอมพิวเตอร์ ปรากฏว่าอัตราความผิดบิตใน MSA มีค่าลดลงอย่างมากเมื่อใช้วิธีการถอดรหัส แบบ MSA โดยมัลติโพรเซสเซอร์ แนวกิดวิธีการประยุกต์ใช้การถอดรหัสแบบ MSA โดยมัลติ โพรเชสเซอร์ สำหรับถอดรหัสคอนโวลูชันเป็นจึงทางเลือกหนึ่งที่น่าสนใจโดยเฉพาะอย่างยิ่งในระบบที่ ต้องการทำอัตรากวามผิดพลาดบิตที่ดำๆ

### 1.2 วัตถุประสงก์ของการวิจัย

- 121 เพื่อพัฒนาประสิทธิภาพของการถอดรหัสแบบหลายสแตก (The Multiple Stack Algorithm)

- 1.2.2 เพียหาวิธีการุประยุกต์ใช้มัลติโพรเซสเซอร์ในการถอดรหัสแบบซึเทวนเซียลเพื่อลดปัญหา computational variability ซึ่งทำให้เกิด crasure ขึ้น

- 1.2.3 เพื่อศึกษาและอยุกแบบใครงสร้างของสถาปัตยกรรมมัสดีโพรเซสเซอร์ที่เหมาะสมกับการ ถอดรหิสแบบหลายสแตก

- 1.2 ง เพื่อศึกษาและออกแบบการเข้ารหิสแบบอื่นๆที่เหมาะสมกับการใช้มัลดิโพรเซสเซอร์ในการ ถอดรหิสแบบหลายสแตก

- 1.2.5 เพื่อเป็นการเผยแพร่วิชาการและองค์สวามรู้ในเชิงการวิจัยของการถอครหัสโดยใช้มัสดิ โพรเซสเซอร์

- 1.2.6 เพื่อพัฒนาศักยภาพในการทำงานวีจัยของผู้ทำวิจัยซึ่งเป็นยาจารย์ในสถาบันยุคมศึกษา

#### 1.3 ขอบเขตของงานวิจัย

- 1.3.1 งานวิจัยนี้จะเป็นการอยกแบบการประยูกด์ใช้มัลดีโพรเซสเซยร์แบบด่างๆในการถยดรหิส แบบหลายสแตกเพื่อเพิ่มประสิทธิภาพการทำงานของการถอดรหิสแบบหลายสแตกโดยวิธี การจำลองในโปรแกรมซึ่งเขียนโดยใช้ภาษซึทำงานบนระบบปฏิบัติการณ์ยูนิกส์

- 1.3.2 วิเคราะห์ประสิทธิภาพการทำงานของการถอดรูหัสแบบหลายสูแตกเมื่อใช้มัลดีโพรเซสเซอร์ เพื่อเปรียบเทียบกับการถอดรหัสแบบหลายสแตกเมื่อใช้โพรเซสเซอร์เดียวในช่องสื่อสาร แบบ AWGN

- 1.4.1 ที่กษาและออกแบบการประยุกต์ใช้การถอดรหัสแบบหลายสแดกในรหัสแบบรีเกอร์ซีพซิส เต็มเมดิกกอนใวลูชัน

# 1.4 ผลงานวิจัยที่กาดว่าจะได้รับ

- 1.4.2 ได้ผลการเปรียบเทียบประสิทธิภาพการถอดรหัสแบบหลายสแตกเมื่อใช้มัลดีโพรเซสเซอร์ กับการถอดรหัสแบบหลายสแตกที่ใช้โพรเซสเซอร์เดียว

- 1.4.3 ได้ทางเลือกใหม่ในการถอดรหัสแบบซีเควนเซียล นั่นคือการถอดรหัสแบบหลายสแตกเมื่อ ใช้มัลติโพรเซสเซอร์ ซึ่งให้ประสิทธิภาพในอัตราความผิดพลาดบิดดำกว่าการถอดรหัสแบบ หลายสแตกเมื่อใช้โพรเชสเซอร์ตัวเดียว

- 1.4.4 ได้วิธีการประยุกต์ใช้วิธีการถอดรหิสแบบหลายสแตกในรหิสแบบรีเดอร์ซีพซิสเต็มเมติก คอนโวลูชิน

- 145 ได้พัฒนาศักยภาพในการทำงานวิจัยของผู้วิจัย

# บทที่ 2 การถอดรหัสแบบหลายสแตก

#### 2.1 บทนำ

ในการส่งและรับข้อมูลคิจิตอลผ่านช่องสื่อสารหนึ่งๆปัญหาที่ไม่สามารถจะหลีกเลี่ยงได้คือการ ถูก รบกวนของสัญญาณ ซึ่งมาจากทั้งตัวอุปกรณ์ในระบบและจากภายนอก และเป็นสาเหตุที่ทำให้ สัญญาณที่รับได้มีความผิดเพี้ยนจากสัญญาณเดิม หรือทำให้สัญญาณข้อมูลมีคุณภาพต่ำลง ดังนั้นเพื่อให้ ได้สัญญาณที่มีคุณภาพดีที่สุดจึงได้มีการค้นคว้าหาวิธีเพื่อให้ได้มาซึ่งสัญญาณข้อมูลที่ถูกต้องมากที่สุด วิธี การหนึ่งที่จะเพิ่มประสิทธิภาพของระบบสื่อสารเพื่อให้ได้คุณภาพของสัญญาณที่เครื่องรับดีขึ้นคือการใช้ เทคนิคการเข้ารหัสควบคุมการ ผิดพลาด (Error Control Coding, ECC) หรือบางครั้งก็เรียกว่าการเข้า รหัสช่องสื่อสาร (Channel Coding) ในวิธีการนี้มีหลักการเบื้องต้นก็คือการเพิ่มส่วนซ้ำซ้อน (redundancy) ให้กับข้อมูลดิจิตอลที่จะส่งผ่านช่องสื่อสารซึ่งปริมาณของส่วนซ้ำซ้อนที่ใส่เข้าไปจะ สัมพันธ์กับระดับในการป้องกันสัญญาณรบกวนของสัญญาณรหัส (Coded signal)

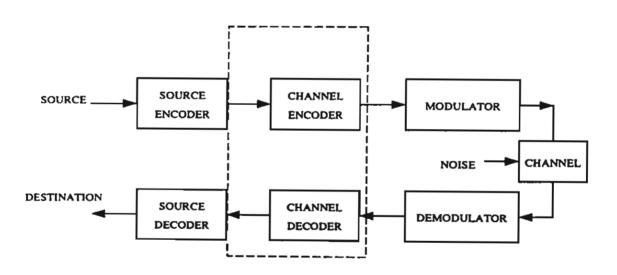

ภาพที่ 2.1 บล็อกไดอะแกรมของระบบสื่อสารเชิงดิจิตอล

ภาพที่ 2.1 เป็นบล็อกไดอะแกรมของระบบสื่อสารเชิงคิจิตอลขั้นพื้นฐานโดยทั่วไป สำหรับงาน วิจัยนี้ที่ทำการศึกษาจะเกี่ยวข้องกับตัวเข้ารหัสช่องสื่อสาร ( Channel encoder ) ซึ่งต่อไปจะเรียกสั้น ๆว่า ตัวเข้ารหัสและตัวถอดรหัสช่องสื่อสาร ( Channel decoder ) ซึ่งต่อไปจะเรียกสั้น ๆว่าตัวถอดรหัส จาก ภาพที่ 2.1 ข้อมูลคิจิตอลที่ต้องการจะส่งถูกป้อนเข้าทางด้านอินพุทของตัวเข้ารหัสซึ่งจะทำหน้าที่เข้ารหัส ข้อมูลโดยการเพิ่มส่วนซ้ำซ้อนให้กับข้อมูล เปรียบเสมือนกับเป็นการเพิ่มภูมิคุ้มกันสัญญาณรบกวนก่อน ส่งผ่านช่องสื่อสารไปยังภาครับสัญญาณ ในส่วนของภาครับก็จะทำหน้าที่รับสัญญาณและกำจัดสัญญาณที่ มีความผิดเพี้ยนเนื่องจากสัญญาณ ถูกรบกวน โดยนำสัญญาณที่รับได้มาผ่านขบวนการการถอดรหัสโดย ตัวถอดรหัส (Decoder) ซึ่งจะทำหน้าที่ดึงเฉพาะสัญญาณข้อมูลดิจิตอลออกมาโดยการแยกส่วนซ้ำซ้อน ออกเพื่อให้ได้ข้อมูลที่มีความเหมือนหรือใกล้เคียงกับข้อมูลที่ส่งมาซึ่งกระบวนการเข้ารหัสสัญญาณและ การถอดรหัสสัญญาณจะได้กล่าวถึงในหัวข้อถัดไป

## 2.2 การเข้ารหัสแบบคอนโวลูชัน

เทคนิกการเข้ารหัสข้อมูลคิจิตอลสามารถแบ่งออกได้เป็น 2 หมวดหมู่ใหญ่ๆ คือ การเข้ารหัสแบบ บล็อก (Block coding) และการเข้ารหัสแบบคอนโวลูชัน (Convolutional coding) ซึ่งการเข้ารหัสทั้งสอง แบบ ก็จะมีขบวนการการถอดรหัสที่เหมาะสมแตกต่างกัน โดยงานวิจัยนี้จะเกี่ยวข้องกับการเข้ารหัสแบบ กอนโวลูชันและการถอดรหัสแบบซีเควนเซียลโดยอัลกอริทึมแบบหลายสแตกเท่านั้น

การเข้ารหัสแบบลอนโวลูชันเป็นการเข้ารหัสที่มีการใช้หน่วยความจำสำหรับจำสถาะนะของบิด ข้อมูลซึ่งจะแตกต่างจากการเข้ารหัสแบบบล็อก นั่นหมายความว่าสัญญาณรหัส (Code word) w บิด ณ เวลาหนึ่งๆจะ ขึ้นอยู่กับสัญญาณอินพุท (message) k บิด ณ เวลานั้นกับสัญญาณอินพุท mk บิด ก่อน หน้านั้น m สัญญาณ เมื่อ m หมายถึงอันคับของหน่วยความจำของตัวเข้ารหัส ซึ่งแตกต่างจากการเข้า รหัสแบบบล็อกคือ ในการเข้ารหัสแบบบล็อก สัญญาณรหัส m บิดจะขึ้นอยู่กับสัญญาณอินพุท k บิด ณ เวลานั้นเท่านั้น

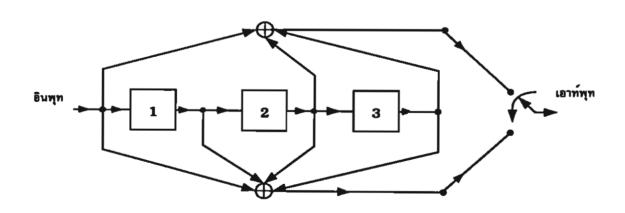

ภาพที่ 2.2 ดัวเข้ารหัสแบบคอนโวลูชัน มี R=1/2 , m=3

ภาพที่ 2.2 แสดงการเข้ารหัสแบบคอนโวถูชันโดยมีอัตราการเข้ารหัสเท่ากับ 1/2 และมีจำนวน หน่วยความจำเท่ากับ 3 (m = 3) อัตราการเข้ารหัส (Code rate, R) ของตัวเข้ารหัสจะถูกกำหนดด้วย จำนวนบิตค้านอินพุท (k) หารด้วยจำนวนบิตค้านเอ้าท์พุท (w) เช่นจากภาพที่ 2.2 มีค่า k=1 และ w=2 ดังนั้น R=0.5 เป็นค้น

การเข้ารหัสแบบคอนโวลูชันสามารถแทนด้วยแผนภูมิแบบต่าง ๆ ได้ 3 รูปแบบ คือ แผนภูมิสเตท (State diagram) แผนภูมิเทรลลิส (Trellis diagram) และ แผนภูมิคันไม้ (Tree diagram)

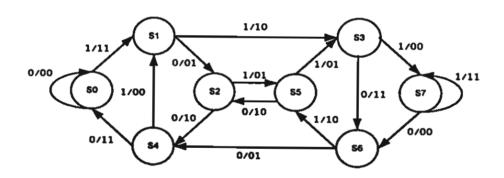

### แผนภูมิสเตท

จากตัวเข้ารหัสแบบคอนโวลูชันในภาพที่ 2.2 ซึ่งมีอันดับของหน่วยความจำ m=3 สเตท ณ เวลาใดเวลาหนึ่งของตัวเข้ารหัสหมายถึงบิดที่ตำแหน่ง 1, 2 และ 3 ในภาพที่ 2.2 จำนวนสเตทที่เป็นไป ได้ทั้งหมดของการเข้ารหัสนี้มีค่าเท่ากับ  $2^m=8$  สเตท ในกรณีนี้คือ ( $s_0=000$ ), ( $s_1=100$ ), ( $s_2=010$ ), ( $s_3=110$ ), ( $s_4=001$ ), ( $s_5=101$ ), ( $s_6=011$ ), ( $s_7=111$ ) เมื่อนำมาเขียนแผนภูมิจะได้ดังภาพ ที่ 2.3 ซึ่งการเข้ารหัสจะเริ่มค้นที่สเตทแรก ( $s_0=000$ ) ตัวเลขกำกับและเส้นลูกศรที่แสดงในภาพที่ 2.3 แสดงถึง ค่าที่ได้จากการเข้ารหัสและเส้นทางการเปลี่ยนสแตทเมื่อมีบิตอินพุทเข้ามา ณ สแตทนั้น ๆ เช่นขณะที่ สแตทของการถอดรหัสอยู่ที่สแตทสูนย์เมื่อบิตอินพุทเข้ามา เป็น "1" สแตทจะเปลี่ยนไปที่สแตทหนึ่งและ ได้ผลของการเข้ารหัสก็อ "11" ถ้าบิตอินพุทเข้ามาเป็น "0" สแตทจะยังกงเป็นสแตทสูนย์เช่นเดิมและได้ผลของการเข้ารหัสเป็น "00" เป็นค้น ในภาพที่ 2.3 แสดงสแตทของการเข้ารหัสเป็น "00" เป็นค้น ในภาพที่ 2.3 แสดงสแตทของการเข้ารหัสเป็น "00" เป็นค้น ในภาพที่ 2.3 แสดงสแตทของการเข้ารหัสเป็น "10 10 11 01 11 00 00

ภาพที่ 2.3 แผนภูมิสเตทของการเข้ารหัสแบบคอนโวลูชัน มี R=1/2 , m=3

## แผนภูมิเทรถถิส

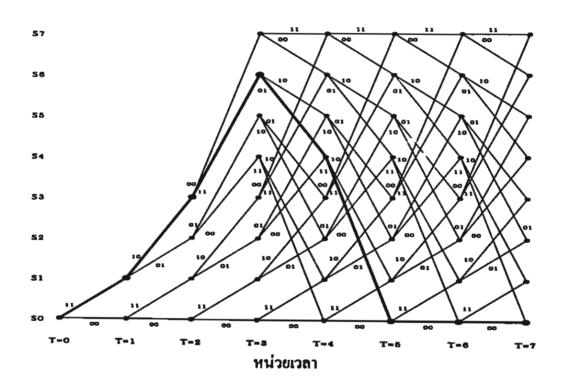

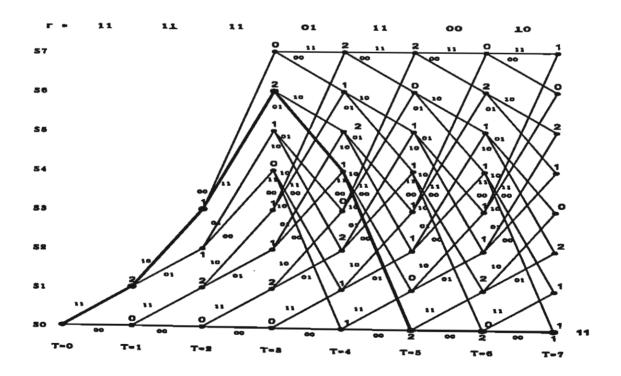

แผนภูมิเทรถลิสเป็นแผนภูมิแสดงผลจากการเข้ารหัสและเส้นทางการเปลี่ยนสเตทในแต่ละ ช่วงเวลา ช่วงเวลาทั้งหมดที่ใช้ในการเข้ารหัสซึ่งจะเริ่มตั้งแต่สเตทสูนย์และกลับมาที่สแตทสูนย์อีกครั้งจะ เท่ากับ L+mช่วงเวลา โดย L คือจำนวนของบิตข้อมูลในแต่ละบล็อก ในแผนภูมิเทรลลิสจะมีตัวเลขกำกับ บนเส้นทางการเปลี่ยนสแตทในแต่ละช่วงเวลาเพื่อบอกผลของการเข้ารหัสเมื่อบิดอินพุทเข้ามา ณ สแตท ใด ๆ ในช่วงเวลานั้น โดยเส้นกิ่งบนที่ออกจากสแตทแสดงผลจากการเข้ารหัสและเส้นทางการเปลี่ยนส เตทเมื่อบิดอินพุทที่เข้ามาสู่สเตท ณ เวลานั้นเป็น "!" เส้นกิ่งล่างที่ออกจากสแตทแสดงแสดงผลจากการ เข้ารหัสและเส้นทางการเปลี่ยน สเตทเมื่อบิดอินพุทที่เข้ามาสู่สเตท ณ เวลานั้นเป็น "0" โดยทั่วไปแล้ว จำนวนกิ่งที่ออกจากสเตทแต่ละสแตทในช่วงเวลาหนึ่งจะเท่ากับ  $2^k$  กิ่ง และจะมีเส้นทางการเข้ารหัสจากส แตทเริ่มต้นจนถึงสแตทสุดท้ายทั้งหมดเท่ากับ  $2^{kL}$  เส้นทาง โดยมีความยาวของรหัสสัญญาณที่ได้จากการ เข้ารหัสเท่ากับ n=w(L+m) บิด ตัวอย่าง เช่น ถ้ามีลำดับข้อมูล 1100 ถูกเข้ารหัสแบบคอนโวลูชันในภาพ ที่ 2.2 ซึ่งมีจำนวนหน่วยความจำเท่ากับ 3 ดังนั้นจะมีจำนวนครั้งของการเปลี่ยนสเตจเท่ากับ 7 ครั้ง และได้ ข้อมูลรหัสด็อ 11 10 11 01 11 00 00 โดยมีจำนวนบิดทั้งหมดเท่ากับ 14 บิด ซึ่งมีเส้นทางการเข้ารหัส(เส้น ทึบ)แสดงในแผนภูมิเทรลลิสดังภาพที่ 2.4

ภาพที่ 2.4 แผนภูมิเทรถลิสของการเข้ารหัสแบบคอน โวลูชัน (2,13) และ L=4 ,

# แผนภูมิดันไม้

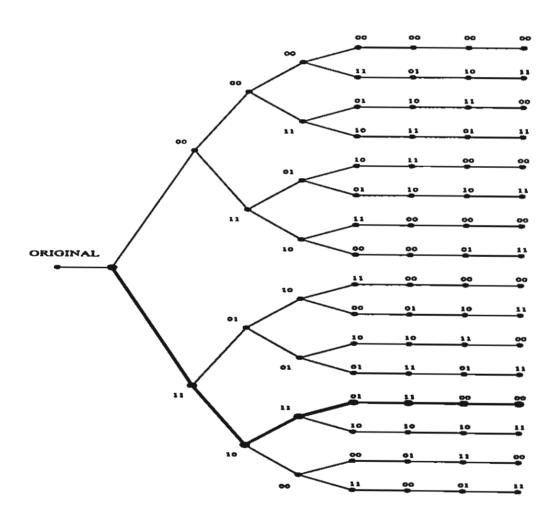

แผนภูมิดันใน้แทนรหัสใช้สำหรับแสดงเส้นทาง (Path) ของการเข้ารหัสแบบคอนไวลูชั่นซึ่ง จะมีเส้นทางที่เป็นไปได้จากจุดเริ่มด้นจนถึงจุดสุดท้ายทั้งหมดจะเท่ากับ  $2^{kL}$  เส้นทาง โดยที่ L คือความ ยาวของลำดับข้อมูลอินพุทในแค่ละบล็อก โดยที่แต่ละโนดบนเส้นทางเดินจะมีทางออกจากโนดสองเส้น ทางในภาพที่ 2.5 แสดงแผนภูมิดันไม้แทนรหัสใช้สำหรับการเข้ารหัสแบบคอนไวลูชันในภาพที่ 2.2 โดย มี R=1/2, m=3 และมีลำดับของข้อมูลอินพุทคือ 1100 โดยกำหนดให้เส้นที่ชี้ขึ้นที่ออกจากแค่ละโนด

หมายถึงมีอินพุท เข้ามาเป็น "!" และให้เส้นที่ชื่องหมายถึงมีอินพุท เป็น "0" คังนั้นได้ข้อมูลที่ถูกเข้ารหัส คือ 11 10 11 01 11 00 00 (เส้นทีบ)

# 2.3 การถอดรหัสสัญญาณที่เข้ารหัสแบบคอนโวลูชัน

การถอครหัสสัญญาณข้อมูลเป็นวิธีการนำสัญญาณข้อมูลที่ได้รับทางด้านรับมาผ่านขบวนการ ถอครหัสเพื่อให้ได้สัญญาณข้อมูลที่ถูกส่งมาอย่างถูกต้องมากที่สุดกระบวนการถอครหัสสัญญาณที่เข้า รหัสแบบ คอนโวลูชัน สามารถที่จะถูกถอครหัสได้ 2 วิธีใหญ่ๆ คือ การถอครหัสแบบวิเทอบิ (Viterbi algorithm, VA) และการถอครหัสแบบซีเควนเซียล (sequential decoding, SD) โดยจะกล่าวถึงรายละเอียด ในลำดับต่อไป

ภาพที่ 2.5 แผนภูมิดันไม้ ของการเข้ารหัสแบบคอนโวกูรัน มี R=1/2 , m=3

### 2.3.1 การถอดรหัสแบบวิเทอบิ (Viterbi algorithm, VA)

การถอดรหัสแบบวิเทอบิจะใช้หลักการของความคล้ายกันที่สุดของสัญญาณ โดยคำนวณ จากระยะแฮมมิ่งหรือระยะยูกลิเครียนทางสัญญาณที่รับได้กับสัญญาณรหัสซึ่งจะคำนวณบนแผนภูมิเทรล ลิส ในการส่งสัญญาณผ่านช่องสื่อสารแบบ Binary Symmetric Channel, BSC ถ้าให้สัญญาณที่รับได้ r และให้สัญญาณรหัสที่ถูกส่ง v บนเส้นทางในแต่ละช่วงบนแผนภูมิเทรลลิส โดยเรียกค่าเมตริกซ์ที่คำนวณ ในแต่ละช่วงเวลาบนแผนภูมิเทรลลิสว่า Bit Metrics,  $M(r_i^{(j)}/v_i^{(j)})$  และมีสมการการคำนวณค่าเมตริกซ์คัง สมการที่ 2.1 โดยที่ i=0,1,2..., (L+m-1) และ j=0,1,2..., (n-1) และเรียกค่าเมตริกซ์ที่คำนวณได้ทั้ง หมดตลอดเส้นทางจากช่วงเวลาเริ่มต้นจนถึงช่วงเวลาสุดท้ายบนเส้นทางบนแผนภูมิเทรลลิสว่า Path Metric, M(r/v) มีสมการการคำนวณดังสมการที่ 2.2 Stephen B. Wicker. (1995)

$$M(r_i^{(f)}/v_i^{(f)}) = \frac{1}{[\log_2(1-p) - \log_2(p)]} [\log_2 P(r_i^{(f)}/v_i^{(f)}) - \log_2(1-p)]$$

(2.1)

$$M(r/v) = \sum_{i=0}^{L+m-1} \left( \sum_{j=0}^{n-1} M(r_i^{(j)}/v)_i^{(j)} \right)$$

(2.2)

โดย p (crossover probability) เป็นความน่าจะเป็นของความผิดพลาดของสัญญาณระหว่างสัญญาณรหัส ที่ถูกส่งและสัญญาณที่รับได้ในช่องสื่อสาร

การถอดแบบวิเทอบิที่มีการส่งสัญญาณผ่านช่องสื่อสารแบบ BSC การคำนวณค่าบิตเมตริกซ์ สามารถเขียนได้ในรูปแบบตารางโดยใช้ระยะแฮมมิ่งระหว่างระหว่างสัญญาณรหัสที่ถูกส่งและสัญญาณที่ รับได้ดังแสดงในตารางที่ 2.1 ตัวอย่างการถอดรหัสแบบวิเทอบิ โดยกำหนดสัญญาณที่รับได้เป็น 11 11 11 01 11 00 10 โดยใช้แผนภูมิเทรถลิสในภาพที่ 2.4 และใช้ค่าเมตริกซ์จากดารางที่ 2.1 เมื่อคำนวณค่า เมตริกซ์ของทุกเส้นทางบนแผนภูมิเทรถลิสแล้วจะเลือกเส้นทางที่มีค่าเมตริกซ์สูงที่สุดเป็นเส้นทางการ ถอดรหัสและได้ข้อมูลของการถอดรหัสก็อ 11 10 11 01 11 00 00 ดังแสดงในภาพที่2.6 (สันทึบ) ซึ่งก็คือ สัญญาณอินพุท 1100

ตารางที่ 2.1 ค่าเมตริกซ์ของแต่ละบิตสำหรับการถอดรหัสแบบวิเทอบิ

| $M(r_i^{(f)}/v_i^{(f)})$ | $r_i^{(f)}=0$ | $r_i^{(f)}=1$ |

|--------------------------|---------------|---------------|

| $v_i^{(f)} = 0$          | 1             | 0             |

| $v_i^{(f)}=1$            | 0             | 1             |

### 2.3.2 การถอดรหัสแบบซีเควนเชียล (Sequential decoding, SD)

การถอดรหัสแบบซีเลวนเชียลเป็นวิธีการถอดรหัสสัญญาณที่เข้ารหัสแบบคอนโวลูชันที่ มีลักษณะคล้ำยกันกับการถอดรหัสแบบวิเทอบิคือมีการคำนวณค่าบิตเมตริกซ์ของสัญญาณที่รับได้กับ สัญญาณรหัสบนแผนภูมิของรหัสแบบคอนโวลูชัน แต่การถอดรหัสแบบซีเควนเชียลจะคำนวณค่าบิต เมตริกซ์ของเส้นทางเดินบนแผนภูมิต้นไม้ โดยคำนวณค่าบิตเมตริกซ์จากสมการการคำนวณค่าบิตเมตริกซ์ ที่เรียกว่า ฟาโนเมตริกซ์ (Fano metrics) Fano (1963) แสดงในสมการที่ 2.3 สำหรับการคำนวณค่าบิต เมตริกซ์ของสัญญาณที่ส่งสัญญาณผ่านช่องสื่อสารแบบ BSC ที่มีความน่าจะเป็นของความผิดพลาดของ สัญญาณ p สมการเมตริกซ์ของฟาโนจะสามารถเขียนได้ใหม่ดังสมการที่ 2.4

$$M(r_i^{(j)}/v_i^{(j)}) = \log_2 \left[ \frac{P(r_i^{(j)}/v_i^{(j)})}{P(r_i^{(j)})} \right] - R$$

(2.3)

$$M(r_i^{(j)}/v_i^{(j)}) = \begin{cases} \log_2 2p - R & \text{if } r_i^{(i)} \neq v_i^{(i)} \\ \log_2 2(1-p) - R & \text{if } r_i^{(i)} = v_i^{(i)} \end{cases}$$

(2.4)

# โดย R คืออัตราการเข้ารหัสของสัญญาณ

ภาพที่ 2.6 ตัวอย่างแผนภูมิเทรถลิสของการถอดรหัสสแบบวิเทอบิ

ในงานวิจัยนี้ได้ศึกษาวิธีการถอดรหัสแบบซีเควนเซียลที่มีการถอดรหัสโดยใช้สแตก โดยแบ่งเป็น สอง อัลกอริทึมตามจำนวนสแตกที่ใช้ในการถอดรหัสคือ การถอดรหัสโดยใช้สแตกเคียวหรือที่เรียกโดย ทั่วไปว่า สแตกอัลกอริทึม (Single Stack Algorithm, SSA) และการถอดรหัสโดยใช้หลายสแตกที่เรียกโดย ทั่วไปว่าการถอดรหัสแบบหลายสแตก (Multiple Stack Algorithm, MSA) ซึ่งการถอดรหัสทั้งสองแบบจะ ได้กล่าวในรายละเอียดต่อไป

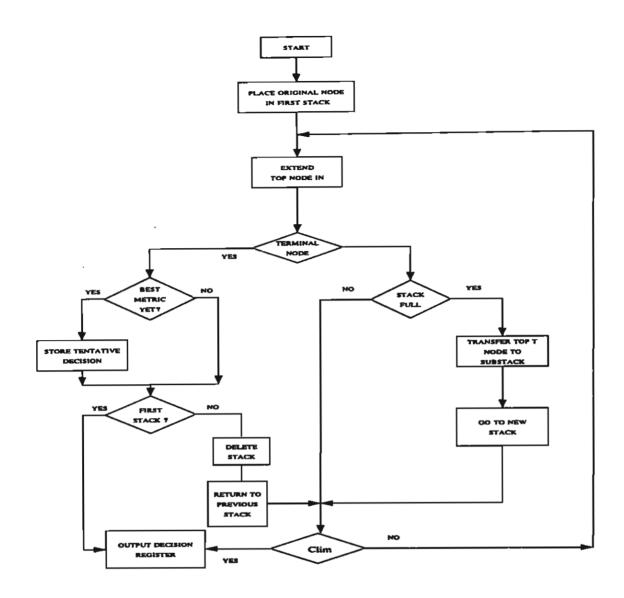

### 2.3.2.1 การถอดรหัสแบบสแตกเดียว

การถอดรทัสแบบสแตกเคียวเป็นการถอดรหัสแบบซีเควนเซียล โดยมีหลักการคือ สัญญาณที่รับได้จากช่องสื่อสารจะถูกนำมาคำนวณค่าเมตริกซ์ซึ่งมีสัญญาณรหัสบนแผนภูมิคันไม้เป็นตัว อ้างอิง ขบวนการถอดรหัสแบบสแตกเคียวมีลำคับการทำงานคังแสดงในภาพที่ 2.8 ซึ่งสามารถอธิบายได้ คังนี้ก็อ ขั้นตอนการถอดรหัสเริ่มค้นที่ P = root ซึ่งเป็นโนคเริ่มค้นสำหรับการถอดรหัสแบบสแตก เคียวบนแผนภูมิค้นไม้ ขั้นตอนการถอดรหัสต่อไปจะคำนวณหาค่าเมตริกซ์ของเส้นทางที่อยู่ถัดไปจาก P ไป 1 ระดับ (Compute Metrics of successors of top path) ทั้งหมด 2<sup>k</sup> เส้นทาง(ในงานวิจัยนี้ 2 เส้นทาง) แล้วเรียงเส้นทางที่มีค่าเมตริกซ์มากให้อยู่ค้านบน ขั้นตอนต่อไปให้ตัดเส้นทางที่มีค่าเมตริกซ์มากที่สุดออก (Delete top path from stack) และให้ P เท่ากับเส้นทางที่ถูกตัดออกไปสำหรับคำนวณค่าเมตริกซ์ในเส้นทางใหม่แล้วเก็บค่าเส้นทางที่เหลือไว้ใน สแต็ก (Reorder stack according to metric values) ในขั้นตอนต่อไปให้ตรวจสอบว่าเส้นทางที่มีคำแหน่งสูงที่สุดอยู่ที่จุดสิ้นสุดของแผนภูมิคันไม้แทนรหัสหรือไม่ (Top path at end of tree?) ถ้ายังไม่ถึงให้กลับไปทำขั้นตอนของการหาค่าเมตริกซ์ของทางเดินที่อยู่ถัดจาก P ไป 1 ระดับใหม่และทำไปเรื่อยๆจนกว่า P จะเป็นโนคสิ้นสุดของแผนภูมิคันไม้แทนรหัสซึ่งจะเห็นว่าสแตกจะใช้หน่วยกวามจำอย่างน้อยที่สุดเมื่อไม่มีสัญญาณรบกวนเลยเท่ากับ (2<sup>k</sup> – 1)L เพื่อให้เกิดความเข้าใจมากขึ้น จะแสดงตัวอย่างของการถอดรหัสแบบ สแตกเดียว

คัวอย่างที่ 1 การถอครหัสโดยใช้สแตกอัลกอริทึม โดยใช้แผนภูมิดันไม้แทนรหัสดังภาพที่ 2.5 และให้สัญญาณที่รับได้ก็อ 11 11 11 01 11 00 10 โดยใช้ก่าเมตริกช์จากตารางที่ 2 (กำหนด p = 0.125) จะ มีขั้นตอนการถอดรหัสดังภาพที่ 2.8 หลังจากทำการถอดรหัส 8 ขั้นตอนแสดงดังภาพที่ 2.7 แล้วจะได้กำ ของการถอดรหัสดือ 1100000 ซึ่งจะได้สัญญาณอินพุทจากถอดรหัสดือ 1100

ตารางที่ 2.2 คำเมตริกซ์ของแต่ละบิตสำหรับการถอครหัสแบบสแตกเคียว

| $M(r_i/v_i)$ | r, =0 | $r_i = 1$ |  |  |

|--------------|-------|-----------|--|--|

| $v_i = 0$    | 1     | -8        |  |  |

| $v_i = 1$    | -8    | 1         |  |  |

| Step 1  | Step 2  | Step 3    | Step 4    | Step 5     | Step 6     | Step 7      | Step 8       |

|---------|---------|-----------|-----------|------------|------------|-------------|--------------|

| 1 (+2)  | 10 (-5) | 11 (-5)   | 110 (-3)  | 1100 (-1)  | 11000 (+1) | 110000 (+3) | 1100000 (4)  |

| 0 (-16) | 11 (-5) | 100 (-12) | 100 (-12) | 100 (-12)  | 100 (-12)  | 100 (-12)   | 100 (-12)    |

|         | 0 (-16) | 101 (-12) | 101 (-12) | 101 (-12)  | 101 (-12)  | 101 (-12)   | 101 (-12)    |

|         |         | 0 (-16)   | 0 (-16)   | 0 (-16)    | 0 (-16)    | 0 (-16)     | 0 (-16)      |

|         |         |           | 111 (-21) | 1101 (-19) | 1101 (-19) | 1101 (-19)  | 1101 (-19)   |

|         |         |           |           | 111 (-21)  | 111 (-21)  | 111 (-21)   | 111 (-21)    |

|         |         |           |           |            |            |             | 1100000 stop |

ภาพที่ 2.7 ขั้นตอนการถอดรหัสแบบสแตกเคียวของตัวอย่างที่ 1

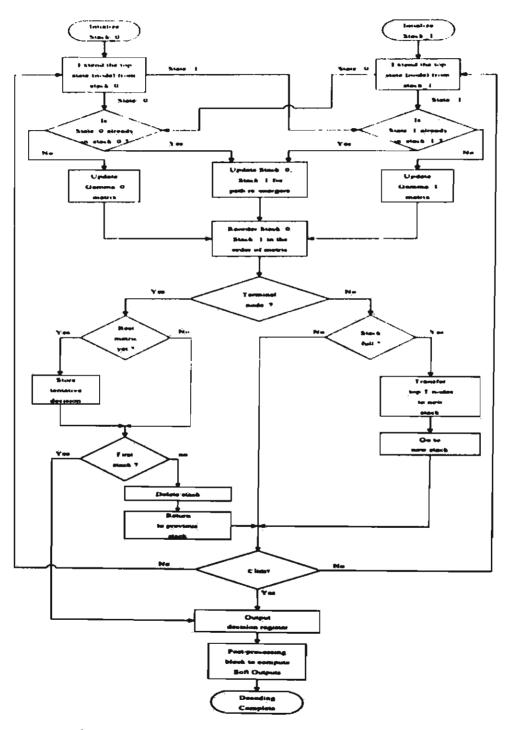

ภาพที่ 2.8 แผนภาพขั้นตอนการถอดรหัสของสแต็กอัลกอริทึม

#### 2.3.2.2 มัธติเปิธสแตกอัลกอริทีม

งานวิจัยนี้จะเกี่ยวข้องกับการถอครหัสแบบมัลติเปิลสแตก ( Multiple stack algorithm, MSA) ซึ่งเป็นการถอดรหัสที่ถูกพัฒนาขึ้นเพื่อแก้ไขการเกิดอิเรชัว (Erasure) ใน SSA กล่าวคือ บล็อกข้อมูลที่มีการรบกวนจากสัญญาณรบกวนมาก อาจจะใช้เวลาในการค้นหาทางเดินของการถอดรหัส ที่ถูกต้องบนแผนภูมิต้นไม้เกินกว่าค่าเวลาที่กำหนดไว้ทำให้จำเป็นต้องหยุดขบวนการถอดรหัสของบล็อก สัญญาณนั้นนั่นคือบล็อกนั้นจะถูกลบทิ้งไปและเรียกข้อมูลที่ถูกลบไปว่าอิเรชัว ต่อมา Chevillat และ Costello (1976) ได้พัฒนาการถอดรหัสแบบ MSA เพื่อแก้ปัญหาอิเรชัวหรือความไม่สมบูรณ์ในการถอด รหัส SSA โดยมีหลักการทำงานเริ่มต้นขั้นตอนการถอดรหัสกับ SSA แต่แตกต่างกันที่จำนวนสแตคที่ใช้ โดยใน MSA จำนวนสแตกจะมีมากกว่าหนึ่งสแตก และกำหนดขนาดของสแตกออกเป็น 2 ส่วนคือ สแตก หลักหรือสแตกแรกและกลุ่มของ สแตกรองหรือสแตกอันดับสูงซึ่งจะมีจำนวนหลายสแตก โดยที่ขนาด สแตกรองมาก ในกรณีปกติของการถอครหัสที่มีสัญญาณรบกวน ของสแตคหลักจะ โตกว่าขนาดของ น้อย การทำงานของขบวนการถอดรหัสมักจะสิ้นสดที่สแตกหลัก จะมีเพียงบางครั้งเท่านั้นที่สแตกรองจะ ถูกนำมาใช้ นั่นคือในกรณีที่ช่องสื่อสารมีสัญญาณรบกวนมาก ซึ่งกรณีนี้การถอครหัสแบบ MSA จะสิ้น สุดเมื่อก่ากำนวณของการถอดรหัสถึงช่วงเวลาที่กำหนดไว้ก่อนหน้า โดยทั่วไปแล้วอัตราความผิดพลาด บิตของการถอครหัสแบบหลาย MSA จะขึ้นกับปัจจัยต่าง ๆ คือ ขนาคของสแตกหลัก ขนาคของสแตกรอง จำนวนโนคข้อมูลที่ย้ายระหว่างสแตก ค่าลิมิตของการคำนวณ (Computational limit)  $C_{

m lim}$

แตกหลักหรือจำนวนรอบของการคำนวณถึงก่าลิมิตของการคำนวณ ( C<sub>lim</sub> ) และเลือกเส้นทางเดินที่ดีที่สุด เมื่อเปรียบเทียบกับ TD ให้เป็นเส้นทางการถอครหัสสุดท้าย (Final decoded path)

เพื่อให้การถอดรหัสแบบ MSA เป็นการถอดรหัสที่ไม่มีอีเรชัว สำหรับกรณีที่กำหนดจำนวนโนด ที่ย้ายระหว่างสแตกเท่ากับหนึ่ง (T=1) และอัตราการเข้ารหัสกอนโวลูชันเป็น 1/w เมื่อ w คือจำนวน เอาท์พุตของตัวเข้ารหัส และกำหนดค่าความยาวคอนสเตรนท์เป็น v คำลิมิตของการคำนวณ  $C_{lim}$  จะต้อง มีค่ามากกว่าค่าขอบเขตวิกฤตด่ำสุดของการคำนวน ( $C_{crit}$ ) ซึ่งกำหนดโดย (Chevillat และ Costello, 1976)

$$C_{crit} = \sum_{i=1}^{k-1} (Z_i - 1) + 2(\nu - 1)$$

(2.5)

โดยที่  $Z_i$ ,  $i=1,2,\cdots,k-1$  เป็นขนาดของสแตกที่ i และ k คือ จำนวนบิตของสัญญาณข้อมูลต่อบล็อก การถอดรหัสที่สิ้นสุดด้วยค่า  $C_{\text{lim}}$  ใน MSA ส่วนใหญ่จะเกิดขึ้นกับบล็อกที่มีสัญญาณรบกวนมาก ๆ ซึ่ง กรณีนี้ ค่าอัตราความผิดพลาดบิตมักจะมีค่าสูงเนื่องจากบ่อยครั้งที่ TD เป็นเส้นทางเดินที่ไม่ถูกต้อง ถึง แม้ว่าประสิทธิภาพของการถอดรหัสแบบ MSA จะสามารถทำให้ดีขึ้นได้โดยการเพิ่มค่าของ  $C_{\text{lim}}$  แต่ก็จะ ทำให้การถอดรหัสดำเนินไปได้ช้าและใช้หน่วยความจำในการถอดรหัสมากขึ้นตามไปด้วย

### ปัจจัยที่มีผลต่อประสิทธิภาพของการถอดรหัสแบบหลายสแตก

ปัจจัยที่มีผลค่ออัตราความผิดพลาดบิตของอัลกอริทึมแบบ MSA ที่จะสามารถถอดรหัสสัญญาณ ได้โดยที่ไม่มีอิเรชัวนั้น (Chevillat และ Costello ,1976) ได้นำเสนอไว้ดังนี้

## 1. ขนาดของสแตกหลัก $(Z_1)$

ในการถอดรหัสแบบ MSA อัตราความน่าจะเป็นที่ที่คาดว่าจะเกิดอิเรชัวในขณะที่สแตกแรก เต็มถูกกำหนดโดย

$$P_{es} = P\left(\hat{r} \neq \hat{v}/u > 1\right) \tag{2.6}$$

โดยที่  $\hat{r}$  คือจำนวนสัญญาณที่รับได้  $\hat{v}$  คือจำนวนรหัสสัญญาณรหัสอ้างอิง และ u คือจำนวนสแคก ถ้ากำหนด  $P_{E(SM)}$  คือความน่าจะเป็นของอัตราความผิดพลาดบิตของการถอดรหัสแบบ SSA ซึ่ง มี ขนาดของสแตกไม่จำกัด ดังนั้นความน่าจะเป็นของอัตราความผิดพลาดบิตของการถอดรหัสแบบ MSA ที่ จะไม่มีอิเรชัวจะถูกกำหนดดังสมการ ที่ 2.8

$$P_{E(MSA)} \le P_{E(SSA)} + P_{es} \bullet P_1 \tag{2.7}$$

โดยที่

$$P_1 = P(C > Z_1 - 1) = c_{SSA} \bullet (Z_1 - 1)^{-\psi}$$

(2.8)

ภาพที่ 2.9 แผนภาพขั้นตอนการถอครหัสแบบหลายสแตก (MSA)

โดยที่ A คือ ความน้ำจะเป็นที่สแตกแรกจะเด็ม ซึ่งมีลักษณะของการกระจายตามหลักการของ Pareto (Pareto Distributed) และ  $\psi$  คือ ค่าฟังก์ชันของช่องสัญญาณและอัตราการเข้ารหัส  $c_{\rm sst}$  เป็นค่าคง ที่ของการถอดรหัสแบบซีเควนเซียล (Forney, G. D. ,1974)

ถ้ากำหนดให้ขนาดของสแตกหลักมีขนาดไม่จำกัด ก่า  $P_1=0$  ( $\lim_{Z_1\to\infty}P_1=0$ ) ความน่าจะเป็นของอัตรากวามผิดพลาดบิดของการถอดรหัสแบบ MSA จะเท่ากับกวามน่าจะเป็นของอัตรากวามผิดพลาดบิดของการถอดรหัสแบบ SSA

$$\lim_{Z_{i}\to\infty} {}^{P}_{E(MSA)} = {}^{P}_{E(SSA)} \tag{2.9}$$

ถ้ากำหนดให้ขนาดของสแตกหลักมีขนาดจำกัด ก่า 4 > 0 จะได้

$$P_{E(MSA)} \le P_{E(SSA)} + P_1 \tag{2.10}$$

จากสมการที่ 2.10 จะเห็นว่าความน่าจะเป็นที่อัตราความผิดพลาดบิตของการถอดรหัสแบบ MSA จะลดลง เมื่อเพิ่มขนาดของสแตกแรกตามฟังก์ชันของ  $P_{\mathbf{i}}$

2. ค่าถิมิตของการคำนวณ (Computational limit,  $C_{\text{lim}}$  )

จากหัวข้อที่แล้วถ้ากำหนดขนาดของสแตกหลักของการถอดรหัสแบบ MSA ให้มีขนาดไม่ จำกัดแล้วประสิทธิภาพที่ได้จากถอดรหัสจะเท่ากับการถอดรหัสแบบ SSA ซึ่งหมายความว่าก่ารอบของ การกำนวณก็จะมีก่าเพิ่มตามขนาดของสแตกหลักด้วย คังนั้นถ้ากำหนดขนาดของสแตกหลักให้กงแต่ เปลี่ยนจำนวน  $C_{\text{lim}}$  แล้วก่าประสิทธิภาพในอัตรากวามผิดพลาดบิตที่ได้จะดีขึ้นในขณะที่มีการเพิ่มก่า  $C_{\text{lim}}$  ถือ

$$\lim_{C_{\rm in} \to \infty} P_{E(MSA)} \le P_{E(SSA)} \tag{2.11}$$

แต่อย่างไรก็ตามในการถอดรหัสแบบ MSA เพื่อไม่ให้เกิดอีเรชัวนั้น ก่าลิมิตของการกำนวณจะ ต้อง มีกำมากกว่ากำขอบเขตวิกฤตต่ำสุดของการกำนวน C<sub>crit</sub> ดังสมการที่ 2.5

3. จำนวนโนคที่ย้ายระหว่างสแตก (T) และขนาดของสแตกรอง (Z)

ในการถอดรหัสแบบ MSA นอกจากผลของขนาดสแตกหลัก และ คำ  $C_{lim}$  ที่มีผลต่อประสิทธิ์ ภาพในอัตรากวามผิดพลาดบิตแล้ว ในขั้นตอนการถอดรหัสถ้าการถอดรหัสไม่สามารถสิ้นสุดในสแตก หลักได้ จะมีการข้ายในคข้อมูลมายังสแตกรองซึ่งก็เป็นอีกปัจจัยที่มีผลต่อการถอดรหัสเช่นกัน จากผลการ ทดลองของ Chevillat และ Costello (1976) ได้แสดงให้เห็นว่าถ้ากำหนดจำนวน ในดที่ย้ายระหว่างสแตก ทั้งสองให้มีจำนวนมากขึ้นโอกาสที่เส้นทางเดินที่ถูกต้องของการถอดรหัสจะถูกข้ายไปดำเนินการถอด รหัสต่อในสแตกรองก็จะเพิ่มมากขึ้นค้วยและจะได้ผลของการถอดรหัสที่ดีขึ้นเช่นกัน แต่ไม่มีกวามแตก ค่างในอัตรากวามผิดพลาดบิตที่เป็นนัยสำคัญมากนัก และการเพิ่มจำนวนโนดที่ย้ายมากขึ้นขนาดของสแต กรอง(2) ก็จะต้องมีขนาดใหญ่มากตามด้วย อย่างไรก็ตามจุดประสงค์หลักที่สำคัญของการกำหนดให้มีส แตกรองของการถอดรหัสแบบ MSA ก็เพื่อให้ การถอดรหัสไม่เกิดอิเรชัว ซึ่งการถอดรหัสจะต้องดำเนิน การเพื่อให้ได้ค่า การตัดสินใจเบื้องดันอันดับแรก (First Tentative decision,TD) เร็วที่สุด ดังนั้นจะต้อง กำหนดให้จำนวนโนดข้อมูลที่ย้ายมีจำนวนน้อย และขนาดของสแตกรองด้องมีขนาดเล็กสามารถสรุปได้ ว่าประสิทธิภาพในอัตรากวามผิดพลาดบิตของการถอดรหัสแบบ MSA จะเพิ่มขึ้นได้โดยการเพิ่มขนาด ของสแตกหลัก หรือการเพิ่มค่าลีมิตของการกำนวณ เป็นปัจจัยสำคัญ แต่อย่างไรก็ตาม การเพิ่มขนาด ของสแตกหลัก หรือการเพิ่มค่าลีมิตของการกำนวณ เป็นปัจจัยสำคัญ แต่อย่างไรก็ตาม การเพิ่มขนาด

แตกหรือหน่วยความจำนั้นอาจจะไม่สามารถทำได้ และในกรณีที่มีสัญญาพรบกวนมาก ๆ ในช่อง สัญญาณ เมื่อการถอดรหัสดำเนินในสแตกรองแล้วโอกาสที่การถอดรหัสจะสามารถกลับมาสิ้นสุดที่สแตก หลักนั้นจะมีน้อยมาก ซึ่งจะทำให้การถอดรหัสจะสิ้นสุดโดยค่าของ  $C_{\rm lim}$  ซึ่งเป็นผลให้อัตราความผิดพลาด บิตมีค่าสูง และการเพิ่มค่า  $C_{\rm lim}$  ยังทำให้การถอดรหัสสิ้นสุดช้า ในงานวิจัยนี้ได้ทำการประยุกต์การถอด รหัสแบบ MSA โดยใช้มัลติโพรเชสเซอร์ เพื่อปรับปรุงประสิทธิภาพในอัตราความผิดพลาดบิตของ MSA เดิมให้ดีขึ้น ที่ค่า  $C_{\rm lim}$  และปริมาณหน่วยความจำที่เท่ากัน ซึ่งจะกล่าวถึงในบทต่อไป

#### บทที่ 3

### การถอดรหัสแบบหลายสแตกโดยมัลติโพรเซสเซอร์

#### 3.1 บทนำ

ในบทนี้จะกล่าวถึงวิธีการประยุกต์ใช้จำนวนหน่วยความจำรวมของระบบการถอดรหัสแบบ MSA และโครงสร้างของการถอดรหัสแบบขนานใน MSA โดยใช้ตัวประมวลผลหลายตัว เพื่อปรับปรุง ประสิทธิภาพในอัตราความผิดพลาดบิตของการถอดรหัสแบบ MSA เดิมให้ดีขึ้นที่ถ่า  $C_{lim}$  และปริมาณ หน่วยความจำที่เท่ากันโดยได้แบ่งขั้นตอนในการศึกษาออกเป็น 3 ส่วนคือ การจัดสรรหน่วยความจำ การ ออกแบบโครงสร้างการถอดรหัสโดยใช้ตัวประมวลผลหลายตัว และการทดสอบผลการออกแบบเบื้องดัน

### 3.2 รูปแบบ MSA โดยมักดิโพรเซสเซอร์

การออกแบบเพื่อประยุกด์ใช้จำนวนหน่วยความจำรวมของระบบการถอดรหัสแบบ MSA และนำ หน่วยความจำมาใช้ให้เป็นประโยชน์อย่างเต็มที่ ในการศึกษาเบื้องต้นนั้นได้ศึกษารูปแบบการใช้หน่วย ความจำของระบบการถอดรหัสแบบ MSA และศึกษาว่าควรจะใช้จำนวนโนดที่ย้ายระหว่างตัวประมวลผล ในลักษณะใด ดังนี้คือ

#### การจัดสรรหน่วยความจำ

การจัดสรรหน่วยความจำรวมของการถอดรหัสแบบMSA เดิม สำหรับตัวประมวลผลแต่ละตัว ในระบบการถอดรหัสใหม่สามารถแบ่งได้เป็น 2 รูปแบบคือ

1. ตัวประมวลผลมีจำนวนหน่วยความจำรวมไม่เท่ากัน

การจัดหน่วยความจำในลักษณะนี้จะนำหน่วยความจำทั้งหมดของสแตกรองของการ ลอดรหัสแบบMSA เดิมซึ่งเท่ากับ  $n_z(Z)$  โดยที่ Z คือขนาดของสแตกรอง,  $n_Z$  คือ จำนวนของสแตกรอง มาจัดสรรให้ตัวประมวลผล n ตัว และกำหนดให้ตัวประมวลผลตัวแรก (DEC #1) เท่านั้นที่มีสแตกหลัก  $Z_i$  ซึ่งกำหนดให้มีขนาดเท่ากับสแตกหลักเดิม และมีหน่วยความจำเท่ากับ  $Z_i + n_{xq}(Z)$  สำหรับตัวประมวลผล อื่น ๆ กำหนดให้มีขนาดสแตกเท่ากับสแตกรอง และมีหน่วยความจำรวมเท่ากับ  $n_{xq}(Z)$  โดยที่  $n_{xq} = \frac{\Gamma - Z_1}{nZ}$ ,  $\Gamma = Z_1 + n_z(Z)$  คือหน่วยความจำทั้งหมดของการลอดรหัสแบบ MSA เดิม

2. ตัวประมวลผลทุกตัวมีจำนวนหน่วยความจำรวมเท่ากัน

การจัดสรรหน่วยความจำในลักษณะนี้จะนำหน่วยความจำทั้งหมดของการถอดรหัส แบบ MSA เดิม ซึ่งเท่ากับ  $\Gamma = Z_1 + n_x(Z)$  โดยที่  $Z_i$  คือขนาดของสแตกหลัก, Z คือขนาดของสแตกรอง . $n_Z$  คือ จำนวนของสแตกรอง ดังนั้นถ้าระบบการถอดรหัสใหม่มีจำนวนดัวประมวลผล n ดัว จะสามารถ แบ่งหน่วยความจำให้ตัวประมวลผลได้เท่ากันหมดคือเท่ากับ  $\Gamma = Z_1 + n_{xx}(Z)$  โดยที่

$$n_{zp} = \frac{n_z - (n-1)(Z_{\parallel}/Z)}{n}$$

# การกำหนดขนาดโนดข้อมูลที่ย้ายระหว่างตัวประมวลผล

การข้ายโนคข้อมูลระหว่างสแตกจะมีผลต่อประสิทธิภาพของการถอครหัสอข่างไรนั้นผู้วิจัยได้ ศึกษาและได้ทคลองจำลองการถอครหัส โดยแบ่งลักษณะการข้ายจำนวนโนคข้อมูลและจำนวนโนคข้อมูล ที่ถูกข้ายให้มีความสัมพันธ์กับรูปแบบการจัดสรรหน่วยความจำคือ

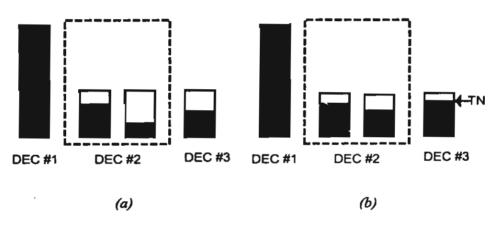

กำหนดให้จำนวนโนคที่ข้าขระหว่างตัวประมวลผลเท่ากับจำนวนโนคที่ข้าขระหว่างสแตก ของแต่ละตัวประมวลผล และใช้กับการจัดสรรหน่วขกวามจำรูปแบบที่ 1 โดยมีลักษณะการผู้ายโนคข้อมูล ตามโครงสร้างคังภาพที่ 3.1 ซึ่งมีลักษณะของขั้นตอนการถอครหัสและข้าขโนคข้อมูลได้คังนี้คือ

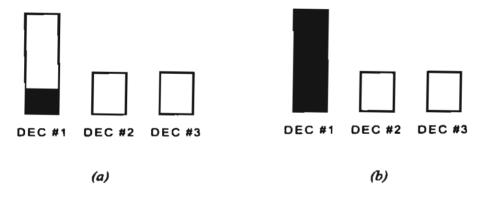

) รูปแบบการข้ายจำนวนในคเมื่อสแตคหลักของตัวประมวลผลตัวแรกเต็ม

b ) รูปแบบการข้ายจำนวนในดระหว่างตัวประมวลผล

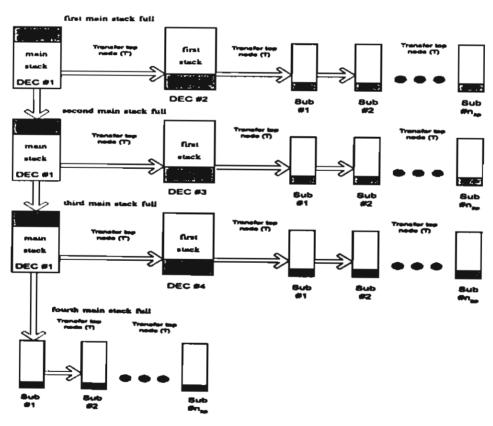

ภาพที่3.1 โครงสร้างการย้ายในคจ้อมูลของการถอครหัสแบบ MSA โดยมัลดิโพรเซสเซอร์รูปแบบที่ 1

เมื่อเนื้อที่หน่วยความจำของสแตกแรกของตัวประมวลผลตัวที่ 1(DEC #1) เต็มในขณะที่การถอด รหัสยังไม่ถึงโนคสุดท้ายของข้อมูลบนทางเคินของแผนภูมิต้นไม้แทนรหัส ขั้นตอนการถอดรหัสจะย้าย โนคข้อมูล T โนคจากสแตกแรกของ DEC #1 มายังสแตกแรกของตัวประมวลผลตัวที่ 2 (DEC #2) จาก นั้นย้าย T โนคอันคับถัดไปมายังตัวประมวลผลตัวที่ 3 (DEC #3) และย้ายจำนวน T โนคอันคับถัดไปมายัง ตัวประมวลผลตัวที่ 4 (DEC #4) ตามลำคับ (ในที่นี้สมมุติใช้ตัวประมวลผล 4 ตัว) เมื่อย้ายจำนวนโนคข้อ มูลมายังตัวประมวลผลครบทุกตัวแล้ว ทุกตัวประมวลผลจะเริ่มถอดรหัสต่อไปภายในสแตกแรกและ คำเนินการถอดรหัสเหมือนการถอดรหัสแบบ MSA อย่างอิสระจนกระทั่งการถอดรหัสดำเนินถึงค่าลิมิต ของการกำนวณ Clim เมื่อการถอดรหัสสิ้นสุด จะเปรียบเทียบก่า การตัดสินใจเบื้องต้น (Tentative decision, TD) ของแค่ละตัวประมวลผลและเลือกก่า TD ที่ดีที่สุดเป็นเส้นทางการถอดรหัสสุดท้าย

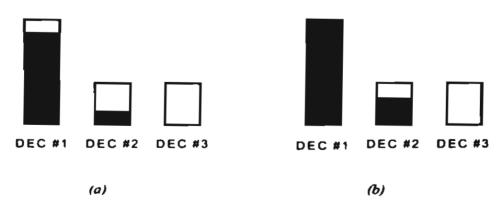

) รูปแบบการข้ายจำนวนในคเมื่อสแดคหลักของตัวประมวลผลตัวแรกเต็ม

๖ ) รูปแบบการข้ายจำนวนในคระหว่างตัวประมวลผล

ภาพที่ 3.2 โครงสร้างการย้ายในคข้อมูลของการถอครหัสแบบ MSA โดยมัลดีโพรเซสเซอร์ รูปแบบที่ 2

2. กำหนดให้จำนวนโนดที่ข้าขระหว่างตัวประมวลผลมีค่ามากกว่าจำนวนโนคที่ข้าข ระหว่าง สแตกของแต่ละตัวประมวลผล และใช้กับการจัดสรรหน่วขกวามจำตามรูปแบบที่ 2 โดยมี ลักษณะการข้าขโนคข้อมูลตามโครงสร้าง ดังภาพที่ 3.2 ซึ่งมีลักษณะของขั้นตอนการถอดรหัสและข้าข ในคข้อมูลได้ดังนี้ก็อ

เมื่อเนื้อที่หน่วยความจำของสแตกแรกของตัวประมวลผลตัวที่ 1(DEC #1) เต็มในขณะที่

การถอดรหัสยังไม่ถึงโนดสุดท้ายของข้อมูลบนทางเดินของแผนภูมิคันไม้แทนรหัส การถอดรหัสจะย้าย

โนค T โนดจากสแตกแรกของ DEC #1 มายังสแตกแรกของตัวประมวลผลตัวที่ 2 (DEC #2) จากนั้นถอด

รหัสแบบ MSA พร้อมกันทั้งสองตัวประมวลผล เมื่อสแตกแรกของตัวประมวลผล DEC #1 เต็มอีกครั้ง

จะย้ายโนค T โนดมายังตัวประมวลผลตัวที่ 3 (DEC #3) และดำเนินการถอดรหัสต่อเหมือนเดิมในขณะที่

ตัวประมวลผล DEC #2 ก็ยังคำเนินการถอดรหัสอยู่เช่นกัน และเมื่อสแตกแรกของตัวประมวลผล DEC

#1 เต็มอีกครั้งจะย้ายโนค T โนดมายังตัวประมวลผลตัวที่ 4 (DEC #4) (ในที่นี้สมมุติใช้ตัวประมวลผล 4

ตัว) แล้วทุกตัวประมวลผลทำการถอดรหัสแบบ MSA จนกระทั่งสิ้นสุดการถอดรหัส ในโครงสร้างนี้ตัว

ประมวลผลทุกตัวดำเนินการถอดรหัสเหมือนการถอดรหัสแบบ MSA อย่างอิสระเช่นเดียวกันกับโครง

สร้างรูปแบบที่ 1คือถ้าสแตกแรกของแต่ละตัวประมวลผลเต็มจะย้ายโนคข้อมูลจำนวน T โนคไปยังสแตก

อันดับถัคไป แล้วดำเนินการถอดรหัสต่อไปจนกระทั่งการถอดรหัสดำเนินถึงลิมิตของการกำนวณ Clim

เมื่อการถอดรหัสสิ้นสุดจะเปรียบเทียบค่า TD ของแต่ละตัวประมวลผลและเลือกค่า TD ที่ดีที่สุดเป็นเส้น

ทางการถอดรหัสสุดท้าย

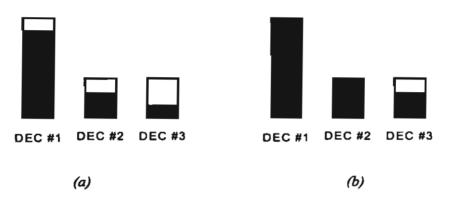

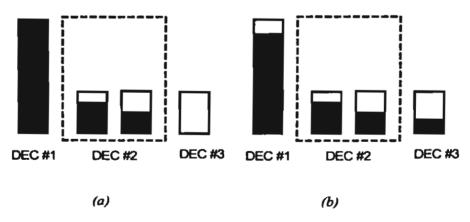

## 3.3 ผลการทคสอบโกรงสร้างรูปแบบ

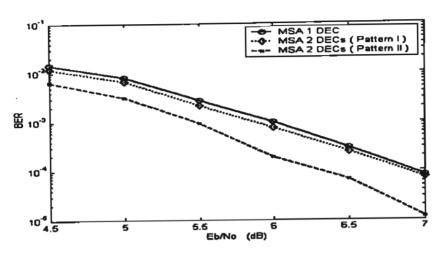

การทดสอบโกรงสร้างที่ได้ออกแบบข้างต้นเพื่อเปรียบเทียบประสิทธิภาพในอัตราความผิดพลาด บิตและเปรียบเทียบกับการถอดรหัสแบบ MSA ที่ใช้ตัวประมวลผลเดียว ผู้วิจัยได้จำลองระบบโดยการ เขียนโปรแกรมคอมพิวเตอร์ภาษาซี บนระบบปฏิบัติการถีนุกซ์ พารามิเตอร์ที่ใช้ในการจำลองที่สำคัญมีดัง ต่อไปนี้คือ ช่องสื่อสารเป็นแบบ AWGN (Additive White Gaussian noise) อัตราการเข้ารหัสคอนโวลูชัน เป็น 1/2 ก่ากวามยาวคอนสเตรนท์ของตัวเข้ารหัส m=5, Generator matrices  $G_i=110101$ ,  $G_2=101111$  จำนวนบิตต่อเฟรมเป็น 60 จำนวนบล็อกทั้งหมด 20,000 บล็อก (จำนวนบิตทดสอบรวม 1,200,000 บิต)  $C_{\lim}=2500$  จำนวนโนดที่ย้ายระหว่างสแตกหลักและสแตกรองภายในแต่ละตัวประมวลผล T เป็น 2 ขนาดของสแตกหลัก  $Z_1$  เป็น 150 ขนาดของสแตกรอง Z เป็น 12 จำนวนสแตกรองของระบบตัวประมวล เดียว  $n_Z$  เป็น 300 ดังนั้นจำนวนหน่วยกวามจำรวมของระบบตัวประมวลผลตัวที่ 1 (DEC #1) มีขนาดหน่วยกวามจำรวม 1950 ตัวประมวลผลตัวที่ 2 (DEC #2) มีขนาดหน่วยกวามจำรวม 1800 สำหรับโครงสร้างรูปแบบที่ 2 DEC #1 มีขนาดหน่วยกวามจำรวม 1725 และใช้ T=50 ภาพ ที่ 3.3 แสดงก่าอัตรากวามผิดพลาดบิตของทั้งสองโครงสร้าง ที่ ค่า  $E_E/N_o$  คือ 4.5 -7.0 dB

จากผลการทดสอบแสดงให้เห็นว่าการจัดสรรจำนวนหน่วยความจำและรูปแบบการย้ายโนคข้อ มูล ตามโกรงสร้างรูปแบบที่ 2 ให้ประสิทธิภาพในอัตราความผิดพลาดบิตที่ดีกว่า โครงสร้างรูปแบบที่ 1 อย่างเห็นได้ชัด ดังนั้นผู้วิจัยได้ตัดสินใจเลือกรูปแบบที่ 2 นี้เป็นแนวทางในการทดสอบการถอดรหัสแบบ ขนานใน MSA โดยใช้ตัวประมวลผลหลายตัว ซึ่งจะกล่าวถึงรายละเอียดของขั้นตอนการถอดรหัสในหัว ข้อถัดไป

ภาพที่ 3.3 ค่า BER ของการถอดรหัสแบบ MSA และ การถอดรหัสแบบ MSA 2 ตัวประมวลผล ตามโครงสร้างรูปแบบ ที่ เ และ โครงสร้างรูปแบบที่ 2 ที่ค่ำ  $E_b / N_o$  ต่างๆกัน

## 3.4 การถอครหัสแบบ MSA โดยมัลติโพรเซสเซอร์

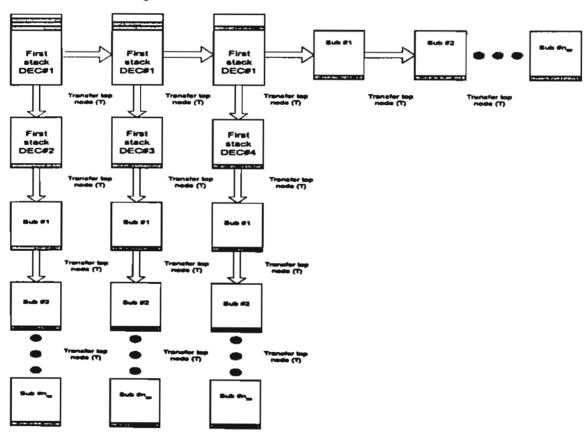

ในงานวิจัยนี้มีเป้าหมายหลักคือการปรับปรุงประสิทธิภาพของการถอดรหัสแบบ MSA โดยใช้ตัว ประมวลผลหลายตัว และได้ออกแบบการใช้ตัวประมวลผลที่มีคุณลักษณะเหมือนกันทุกประการจำนวน ท ตัว สำหรับถอดรหัสโดยใช้อัลกอริทึม MSA ไปพร้อมๆกัน(ตัวประมวลผลทุกตัวจะทำหน้าที่เป็นตัว ถอดรหัสอย่างอิสระ) ด้วยแนวความคิดของวิธีการถอดรหัสนี้ จะทำให้ค่า TD มีค่าที่ดีขึ้นเนื่องจากการถอด รหัสที่ใช้ตัวประมวลผลหลายตัวสามารถถึงโนดสุดท้ายได้จำนวนครั้งมากขึ้นในเวลาที่กำหนด ดังนั้น โอกาสที่จะได้ทางเดินที่ถูกต้องก็จะมากขึ้นตามไปด้วย ส่งผลให้ค่าอัตราความผิดพลาดบิตมีค่าลดลงเมื่อ เปรียบเทียบทั้งสองระบบที่กำหนดให้ค่า Clim และขนาดของหน่วยความจำรวมเท่ากัน

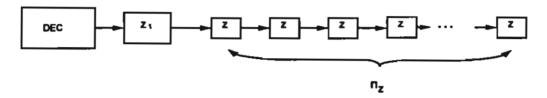

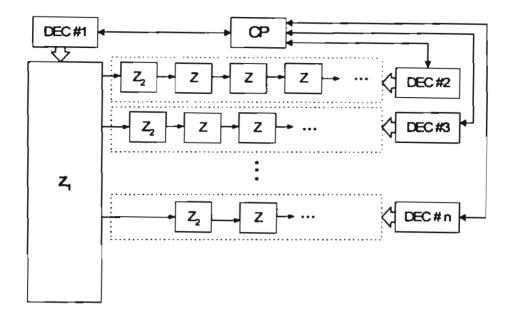

ภาพที่ 3.4 แสดงโครงสร้างของระบบการถอดรหัสแบบ MSA โดยใช้ตัวประบวถผลหลายตัวที่ใช้ สำหรับงานวิจัยนี้ ซึ่งสามารถอธิบายได้ดังนี้ กำหนดขนาดหน่วยความจำรวมของสแตกทั้งหมดในระบบ สำหรับใช้ในการถอดรหัสเท่ากันกับการถอดรหัสแบบ MSA เมื่อใช้ตัวประมวลผลตัวเดียว และมีขนาด ของสแตกทุก สแตกเท่ากัน ข้อแตกต่างของทั้งสองระบบคือ จำนวนสแตกรองในระบบ MSA เดิมจะมี จำนวนมากกว่าจำนวน สแตกรองของระบบใช้ตัวประมวลผลหลายตัว ถ้ากำหนดให้จำนวนของสแตกรองของการถอดรหัสแบบ MSA โดย ใช้ตัวประมวลผลหลายตัว ลำกำหนดให้จำนวนของสแตกรอง ใช้ตัวประมวลผลหลายตัวเท่ากับ  $n_{xy}$  และ ถ้านวนของสแตกรองของการถอดรหัสแบบ MSA โดย

เดิมนั่นคือ  $\Gamma = Z_1 + n_2 Z$  เมื่อ  $Z_1$  คือ ขนาดของสแตกหลัก และ Z คือ ขนาดของสแตกรอง หน่วยความ จำของตัวประมวลผลแต่ละตัวของระบบการถอดรหัสแบบ MSA โดยใช้ตัวประมวลผลหลายตัว สามารถ เขียนเป็นสมการได้ดังนี้ คือ

$$\Gamma' = Z_1 + n_{zp}Z, \qquad n_{zp} = \frac{n_z - (n-1)(Z_1/Z)}{n}$$

(3.1)

เมื่อ Г' คือ หน่วยความจำรวมของตัวประมวลผลแต่ละตัวของระบบการถอดรหัสแบบขนาน โดยที่

a. MSA Single Processor

ภาพที่ 3.4 โครงสร้างการถอครหัสสำหรับ MSA (a) MSA ตัวประมวลผลเคียว

(b) MSA หลายตัวประมวล

# 3.4.1 ขั้นตอนการถอดรหัสแบบ MSA โดยมัถติโพรเซสเซอร์

ขั้นตอนที่ 1 ตั้งค่า j=1 โหลดค่าโนดเริ่มต้นในสแตกหลักของตัวประมวลผลตัวแรก (DEC #1)

ขั้นตอนที่ 2 DEC #1 เริ่มทำการถอดรหัสแบบ MSA ในสแตกหลักเท่านั้น

งั้นตอนที่ 3 ดรวจสอบว่าสแตกหลักของ DEC #1 เต็มหรือไม่ ถ้าใช่, ตั้งค่า j=j+1 จากนั้นข้าขโนคข้อมูลจำนวน T' โนคในสแตกหลักของ DEC #1 มาขังสแตกหลักของตัวประมวลผลตัวที่ j (DEC # j )

ขั้นตอนที่ 4 ตรวจสอบว่า j = n หรือไม่, ถ้าใช่ ไปขั้นตอนที่ 5 ถ้าไม่ใช่ ให้กลับ ไปขั้นที่ 2 ในขณะเคียวกัน DEC #2 ถึง DEC# j จะเริ่มถอดรหัสสัญญาณแบบ MSA อย่างอิสระพร้อมๆ กันในขั้นตอนนี้

ขั้นตอนที่ 5 DEC #1 ถึง DEC # j คำเนินการถอครหัส โดยวิธีการถอดรหัสแบบ MSA ไปพร้อมๆกัน

# 3.4.2 กฎเกณฑ์การสิ้นสุดของขบวนการถอดรหัส

กระบวนการถอครหัสจะสิ้นสุดเมื่อตัวประมวลผลควบคุม (Control processor, CP) ตรวจสอบพบเงื่อนไขในข้อใดข้อหนึ่งต่อไปนี้ คือ

- 1. การถอครหัสคำเนินถึงโนคสุดท้ายของเส้นทางเดินในแผนภูมิต้นไม้แทนรหัสในส แตกหลัก (แรก) ของ DEC #1 ซึ่งกรณีนี้กำเมตริกซ์ของเส้นทางเดินจากโนคเริ่มต้นถึงโนคสุดท้ายจะถูกนำ มาเปรียบเทียบกับค่าเมตริกซ์ของทางเดิน TD จากนั้นเลือกทางเดินที่ดีกว่า (ค่าเมตริกซ์ที่สูงกว่า) เป็นเส้น ทางเดินของการถอครหัสสุดท้าย

- 2. จำนวนรอบของการถอครหัสมีค่าเท่ากับ C<sub>lim</sub> ในกรณีนี้ทางเดิน TD ที่ถูกบันทึกไว้ใน รีจิสเตอร์พิเศษจะเป็นเส้นทางการถอครหัสสุดท้าย

# 3.4.3 หน้าที่ของตัวประมวลผลควบคุม CP

- เปรียบเทียบและบันทึกค่าทางเคินที่ดีที่สุด TD ในรีจิสเตอร์พิเศษเมื่อตัวประมวลผลแต่ ละตัวถึงโนคสุดท้าย (ในกรณีที่การถอครหัสถึงโนคสุดท้ายในสแตกอื่นที่ไม่ใช่สแตกหลักของ DEC #1)

- 2. สั่งให้ตัวประมวลผลทุกตัวหยุดทำงานเมื่อกระบวนการถอดรหัสดำเนินมาถึงข้อใดข้อ หนึ่งของกฎเกณฑ์การสิ้นสุดของขบวนการถอดรหัส ข้างต้น

หลักการเบื้องค้นของการถอครหัสแบบ MSA โดยมัลดีโพรเซสเซอร์คือการใช้ประโยชน์จากสแต ครองให้มากที่สุดโดยการช่วยกันค้นหาทางเดินที่ดีที่สุดในแผนภูมิค้นไม้แทนรหัส โดยตัวประมวลผล หลายตัว ในบทต่อไปจะแสดงผลการจำลองการทดสอบและเปรียบเทียบผลการทดสอบกับการถอดรหัส แบบ MSA เดิม 3.5 การประยุกต์การถอดรหัสแบบ MSA ในรหัสแบบรีเกอร์ซีพซิสเต็มเมติกคอนโวลูชัน

หัวข้อนี้เป็นการนำเสนออัลกอริทึมการถอดรหัสแบบหลายสแตกชนิตดัดแปลง (A modified multiple stack algorithm, M-MSA) ในรหัสแบบรีเกอร์ชีพชิสเต็มเมติกกอนโวลูชัน (Recursive systematic convolutional codes, RSC) ซึ่งเป็นการนำเอาการถอดรหัสแบบหลายสแตกเดิม (Multiple Stack Algorithm, MSA) มาประยุกต์ใช้กับการถอดรหัสแบบทวินสแตก (Twin stack algorithm, TS) โดยนำเอา ข้อดีของการถอดรหัสแบบสมบูรณ์ใน MSA โดยไม่มีการลบข้อมูลเมื่อสแตกเต็ม แต่แบ่งกลุ่มของสแตกอ อกเป็น 2 กลุ่มหลัก รายละเอียดอยู่ในหัวข้อที่ 2 จากผลการทดสอบเบื้องต้นพบว่า ผลลัพธ์แบบฮาร์ดในอั ลกอริทึมมัลดีเพิลสแตกแบบดัดแปลง ให้ประสิทธิภาพในอัตราความผิดพลาดบิตใกล้เกียงกับการถอด รหัสแบบทวินสแตกอัลกอริทึม แต่ใช้เวลาในการคำนวณเพื่อถอดรหัสน้อยกว่าที่ค่าอัตราส่วนของ สัญญาณต่อสัญญาฉรบกวนมีค่าต่ำๆและทดสอบในสภาวะของการคำนวณเดียวกัน และในงานวิจัยนี้อยู่ ในระหว่างการดำเนินการประยุกต์ผลลัพธ์แบบฮาร์ดที่ได้ ไปสร้างเป็นผลลัพธ์แบบฮอฟท์ เพื่อนำไปใช้ใน การถอดรหัสแบบวนจ้ำในรหัสเทอร์โบ

ขั้นตอนการถอดรหัสโดยใช้อัลกอริทึม M-MSAเป็นไปตามแผนภูมิในภาพที่ 3.5 ซึ่งมีรายละเอียด ดังนี้ คือ จำนวนสแตกทั้งหมดในการถอดรหัสจะแบ่งออกเป็น 2 กลุ่มใหญ่ และในแต่ละกลุ่มใหญ่จะ กำหนดขนาดของสแตกออกเป็น 2 ขนาดย่อย คือ ขนาดสแตกหลักหรือสแตกแรกและขนาดของสแต ครองหรือสแตกอันดับสูงซึ่งจะมีจำนวนหลายสแตก โดยที่ขนาดของสแตกหลักจะโตกว่าขนาดของสแต ครองมาก ในกรณีปกติของการถอดรหัสที่มีสัญญาณรบกวนน้อย การทำงานของขบวนการถอดรหัสมักจะ สั้นสุดที่สแตกหลัก จะมีเพียงบางครั้งเท่านั้นที่สแตกรองจะถูกนำมาใช้ นั่นคือในกรณีที่ช่องสื่อสารมี สัญญาณรบกวนมาก จะใช้ สแตกเริ่มต้นซึ่งเป็นสแตกหลัก สองสแตกคือ สแตกู และ สแตกุ ซึ่งแสตก ทั้งสองนี้จะมีคุณสมบัติเหมือนกับตัวถอดรหัสแบบ SSA เพียงแต่ว่า สแตกู ใช้เก็บข้อมูลของทุกสเตท (State) ที่มีเส้นทาง (Path) ที่ลงท้ายด้วยศูนย์ และ สแตกุ ใช้เก็บข้อมูลของทุกสเตทที่มีเส้นทางที่ลงท้าย ด้วยหนึ่ง เนื่องจากตัวเข้ารหัสที่ใช้เป็นแบบ RSC จึงทำให้สเตทที่เกิดขึ้นลงท้ายด้วย 0 หรือ 1 ซึ่งทำ ให้ สเตทนั้นอาจอยู่ในทั้ง สแตกู และ สแตกุ พร้อมกันได้ที่ระดับความลึกเดียวกัน แต่ถ้าหากสเตทเกิดช้ำ กันในสแตกเดียวกัน ตัวถอดรหัสจะเลือกเก็บสเตทที่มีค่าเมดริกซ์ (Metric) มากกว่าไว้ และสบเสตทที่มีค่า เมดริกซ์น้อยกว่า ซึ่งเมตริกซ์ที่ใช้ในการถอดรหัสนีใช้เฟโนเมตริกซ์ (Fano metric) สำหรับอัตราการเข้า รหัส R=b/c และสัญญาณที่รับได้  $y_t=\{y_t^{(r)}\}$ , j=1,...,c ดังแสดงในสมการที่ (3.3)

$$\log\left[\mu_{AP}(K)\right] = \sum_{j=1}^{c} \log\left(\frac{\Pr(y_{k}^{(j)}/v_{k}^{(j)})}{\Pr(y_{k}^{(j)})}\right) + \sum_{j=1}^{b} \log\Pr(d_{k}^{j})$$

(3.3)

เมื่อ  $P(y_i^{(r)}/v_i^{(r)})$  หมายถึงความน่าจะเป็นที่รับสัญญาณ  $y_i$  ตัวที่ j ได้เมื่อส่งสัญญาณ  $v_i$  ตัวที่ j และในเทอมที่สองของสมการคือ ค่า APP (A posteriori probability) ของบิตข้อมูลและจะมีการเก็บค่าแกม

ม่าของบิดที่  $k_-(\gamma_e)$  ตามการอัพเดทเส้นทางในสแตกไปด้วย ตั้งภาพที่ 3.6 ซึ่งคำแกมม่านี้ใช้ในกระบวน การสร้างผลลัพธ์แบบชอฟท์ไปด้วย ดังสมการที่ (3.4)

$$\gamma_{k}(m',m) = \sum_{k} P_{k}(m \mid m') \cdot Q_{k}(X \mid m';m) \cdot R_{k}(Y_{k} \mid X)$$

(3.4)

ภาพที่ 3.5 แผนภาพขั้นตอนการทำงานของตัวถอดรหัสแบบ M-MSA

เมื่อ  $P_{k}(m|m')$ คือ ความน่าจะเป็นที่สเตท m'ใดๆ จะเปลี่ยนเป็นสเตท  $m,Q_{k}(X|m';m)$  คือ ความน่าจะ เป็นที่จะเกิดผลลัพธ์ X เมื่อสเตท m' ใดๆ จะเปลี่ยนเป็นสเตท m และ  $R_{k}(Y_{k}|X)$  หมายถึงความน่าจะเป็น ที่รับสัญญาณ  $Y_{k}$  ได้เมื่อส่งสัญญาณ X

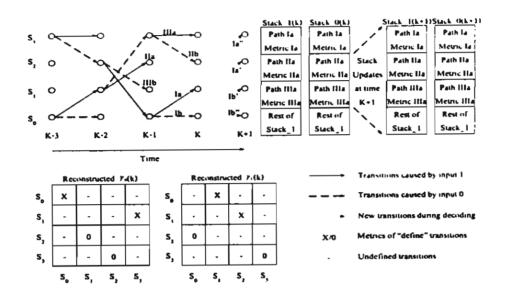

ภาพที่ 3.6 กระบวนการทำงานของ M-MSA และกระบวนสร้างแกมม่าที่เวลา k

ในกรณีที่สแตกหลักเต็ม จำนวนโนคข้อมูลที่มีค่าเมตริกซ์สูงสุดจำนวนหนึ่งจะถูกข้าขไปขังสแตกรอง จากนั้นกระบวนการถอดรหัสจะคำเนินต่อไปในสแตกรองโดยใช้จำนวนโนคที่ข้าขมา ถ้าการถอด รหัสถึงโนคสุดท้าขของแผนภูมิต้นไม้แทนรหัสก่อนที่สแตกรองเด็ม เส้นทางเดินจากโนคเริ่มต้นจนถึง โนคสุดท้าขจะถูกเก็บไว้ในรีจิสเตอร์พิเศษ (Special register) และเรียกทางเดินที่เก็บไว้ว่า การตัดสินใจ เบื้องค้น (Tentative decision, TD) หลังจากนั้นตัวถอดรหัสจะถบโนคที่เหลือในสแตกรองและกลับมาเริ่ม กระบวนการถอดรหัสอีกครั้งในสแตกหลักโดยเริ่มจากโนดที่อยู่บนสุด (ดีที่สุด) ในตอนนี้สแตกหลักจะมี เนื้อที่ว่างเท่ากับจำนวนโนคที่ถูกข้ายในตอนแรก ถ้าการถอดรหัสจำเนินมาถึงโนคสุดท้าขของแผนภูมิต้น ไม้แทนรหัส ก่อนที่สแตกหลักจะเต็มอีกครั้งตัวถอดรหัสจะเปรียบเทียบคำเมตริกซ์ของเส้นทางเดินใหม่นี้ กับเส้นทางเดิน TD และเลือกทางเดินที่มีคำเมตริกซ์ที่ดีกว่าเป็นเส้นทางการถอดรหัส อย่างไรก็ตามถ้าส แตกหลักเต็มอีกครั้งสแตกรองก็จะถูกสร้างขึ้นมาใหม่และมีการข้ายในคข้อมูลในลักษณะเดิม การสร้างส แตกรองก็จะเกิดขึ้นในลักษณะเช่นนี้ค่อไปเรื่อขๆ จนกระทั่งถึงเงื่อนไขของการสิ้นสุดการถอดรหัส ใน กรณีของเมื่อก่าคำนวณของการถอดรหัสถึงคำลิมิตของการกำนวณ TD ก็จะถูกเลือกให้เป็นเส้นทางการ ถอดรหัสสุดท้าย

# บทที่ 4 การทดสอบและผลการทดสอบ

#### 4.1 บทนำ

บทนี้เป็นการนำเสนอผลการจำลองระบบการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์ ตาม แบบโครงสร้างที่ได้ศึกษาในบทที่ 3 เนื้อหาภายในบทนี้เริ่มจากการวิเคราะห์พารามิเตอร์ที่เหมาะสม เริ่ม จากการหาจำนวนโนคที่เหมาะสมที่ข้ายระหว่างตัวประมวลผล (T) ซึ่ง T เป็นพารามิเตอร์ตัวใหม่ที่แตก ต่างจากระบบการถอดรหัสแบบ MSA ที่ใช้ตัวประมวลผลเดียว และได้ทดสอบพารามิเตอร์อื่น ๆ ที่มีผล ต่อการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์ เพื่อเปรียบเทียบประสิทธิภาพในอัตราความผิดพลาด บิดกับการถอดรหัสแบบ MSA ที่ใช้ตัวประมวลผลเดียว

# 4.2 การจำลองระบบสื่อสารและสมมุติฐานที่ใช้ในการทดสอบ

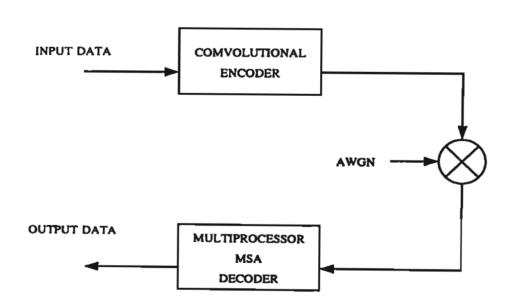

ในการทคสอบจะใช้แบบจำลองระบบตามภาพที่ 4.1 ที่มีการเข้ารหัสสัญญาณแบบคอน โวลูชัน อัตราการเข้ารหัส 1/2 ผ่านช่องสื่อสารเป็นแบบ AWGN (Additive White Gaussian noise) และนำสัญญาณ มาลอครหัสที่ภาครับสัญญาณค้วยการลอครหัสแบบซีเควนเซียล โดยใช้อัลกอริทึมแบบ MSA ที่ใช้ตัว ประมวลผลเดียวและ อัลกอริทึมแบบ MSA โดยมัลติโพรเซสเซอร์

ภาพที่ 4.1 บล็อกไดอะแกรมการเข้ารหัสและถอดรหัสสำหรับการทดสอบ

เพื่อทดสอบประสิทธิภาพของหลักการที่ได้นำเสนอในงานวิจัยนี้ ผู้วิจัยได้จำลองระบบโดยการเขียน โปรแกรมคอมพิวเตอร์ภาษาซี บนระบบปฏิบัติการลินุกซ์ พารามิเตอร์ที่ใช้ในการจำลองที่สำคัญมีดังต่อ ไปนี้คือ ช่องสื่อสารเป็นแบบ AWGN (Additive White Gaussian noise) อัตราการเข้ารหัสคอนโวลู ขันเป็น 1/2 ค่าของความยาวคอนสเตรนท์ของตัวเข้ารหัสมี 2 ค่า คือ m=5 โดยมีเมตริกซ์ของตัวกำเนิด (Generator matrices)  $G_1=110101$ ,  $G_2=101111$  และ m=7 ซึ่งใช้ Generator matrices  $G_1=10111101$ ,  $G_2=11001011$  จำนวนบิตค่อเฟรม K เป็น 60 บิต 120 บิตและ 180 บิตซึ่งมีจำนวนบิตทดสอบรวมเป็น 1,200,000 บิตเท่ากันในทุกกรณี  $G_{\text{lim}}=2500$  จำนวนโนคที่ย้ายระหว่างสแตกหลักและสแตกรองภายใน แต่ละตัวประมวลผล T เป็น 2 ขนาดของสแตกรอง Z เป็น 12 จำนวนสแตกรองของระบบตัวประมวล เดียว  $n_Z$  เป็น 300 และของตัวประมวลผลหลายตัว  $n_{ZP}$  เป็นไปตามสมการที่ (3.1)

# 4.3 ผลการทดสอบประสิทธิภาพกับค่าพารามิเตอร์ต่าง ๆ

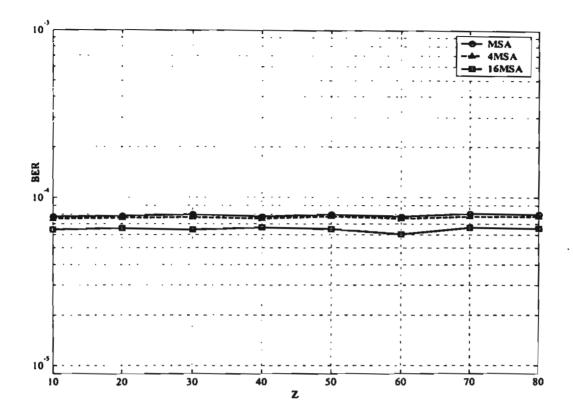

# 4.3.1 ผลจำนวนโนดที่ย้ายระหว่างตัวประมวลผล (T)

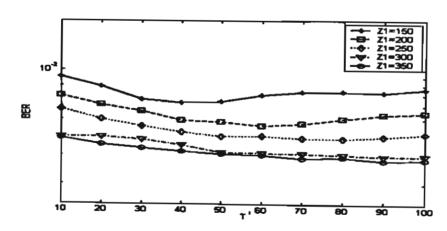

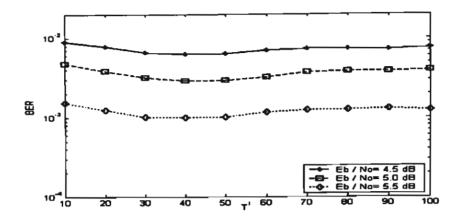

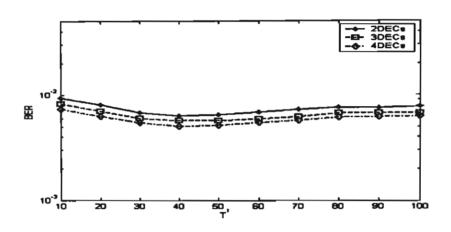

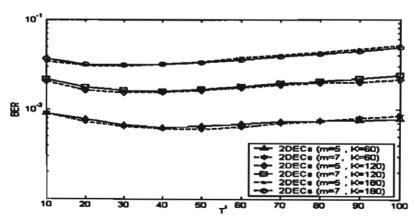

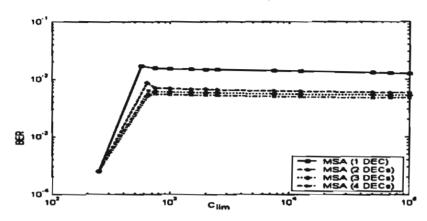

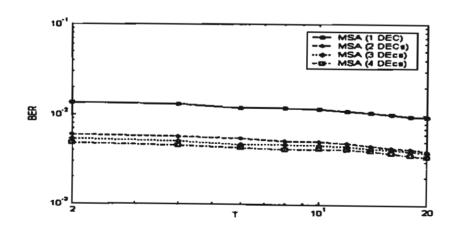

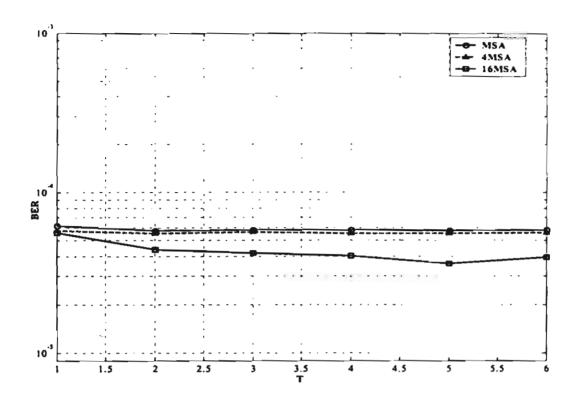

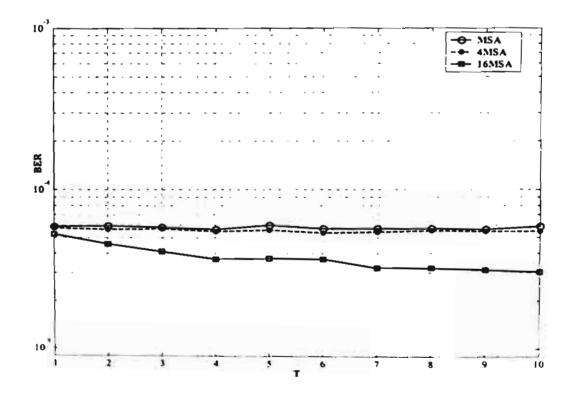

การทคสอบหาจำนวนโนคที่เหมาะสมที่ข้าขระหว่างตัวประมวลผลสำหรับงานวิจัย ผล การทคสอบ ภาพที่ 4.2 แสดงค่าอัตราความผิดพลาดบิต (Bit error rate, BER) เทียบกับจำนวนโนคที่ข้าข จาก สแตกหลักของ DEC #1 ไปยังสแตกหลักของ DEC #j (j=2,...,n) เมื่อกำหนดค่า  $E_b/N_o=4.5\,$  dB จะเห็นว่าค่า T ที่ให้ค่า BER ต่ำที่สุดจะมากขึ้นตามค่าของ  $Z_l$  (สังเกตจากกราฟแต่ละเส้นที่ให้ค่า BER ต่ำ สุด) และเมื่อกำหนดให้ขนาดของสแตกหลักคงที่ที่ค่า  $Z_l=150\,$  โดยปรับค่า  $E_b/N_o$  จาก 4.5-5.5 dB ให้ค่า BER เมื่อใช้ตัวประมวลผล 2 ตัวดังแสดงในภาพที่ 4.3 สำหรับภาพที่ 4.4 เป็นผลการจำลองเพื่อดูค่า BER เมื่อใช้ตัวประมวลผล 2 ตัว 3 ตัว และ 4 ตัว โดยกำหนดให้  $Z_l=150\,$  คงที่เช่นเดิม ภาพที่ 4.5 แสดงผลอัตรา ความผิดพลาดบิตที่ค่า m และ K ต่างๆกันจะเห็นว่าเมื่อใช้จำนวน m และ K มากขึ้นค่า T ที่ทำให้ BER ต่ำ ที่สุดมีค่าลดลง จากผลการทดสอบข้างต้นจะเห็นว่าที่ค่า  $Z_l=150\,$  ค่า T ที่เหมาะสมคือค่าตั้งแต่ 40 ถึง 50 ตังนั้นจึงได้เลือกค่า  $Z_l=150\,$  สำหรับ  $m=5\,$  และ  $T=50\,$ เพื่อใช้ทดสอบประสิทธิภาพในบทความนี้

ภาพที่ 4.2 ค่า BER กับ  $au^{\cdot}$  เมื่อเปลี่ยนจำนวน  $au_{i}$

ภาพที่ 4.3 ค่า BER กับ T ที่ค่า E, / N, ต่างๆกัน

ภาพที่ 4.4 ค่า BER กับ T ่เมื่อใช้จำนวนตัวประมวลผลต่างกัน

ภาพที่ 4.5 ค่า BER กับ T ่ เมื่อใช้ ค่าของ m และ K ค่างกัน

ตารางที่ 4.1 จำนวนบล็อกที่ถอดรหัสเสร็จในสแตกหลักของ DEC# I

| จำนวนตัวประมวล<br>ผล | จำนวนบล็อกที่ถอดรหิสเสร็จในสแตกหลักของ DEC #1 |        |        |        |        |        |  |

|----------------------|-----------------------------------------------|--------|--------|--------|--------|--------|--|

|                      | T = 20                                        | T = 30 | 7 = 40 | T = 50 | 7 - 60 | T = 70 |  |

| 1 DEC                | 18.507                                        |        |        |        |        |        |  |

| 2 DECs               | 18,548                                        | 18,578 | 18,582 | 18,639 | 18,682 | 18,745 |  |

| 3 DECs               | 18,569                                        | 18,635 | 18,692 | 18,763 | 18,832 | 18,903 |  |

| 4 DECs               | 18,594                                        | 18,691 | 18,790 | 18,895 | 18,915 | 19,045 |  |

<sup>•</sup> ตัวประมวลผลดัวเดียวไม่มีการย้ายในคข้อมูลระหว่างตัวถอดรหัส

ตารางที่ 4.1 แสดงผลจำนวนหลือกของการถอดรหัสซึ่งสิ้นสุดภายในสแดกหลักของตัวประมวล ผลตัวแรก การเพิ่ม T จะทำให้ได้จำนวนหลือกของการถอดรหัสที่สิ้นสุดในสแดกหลักของ DEC#1 เพิ่ม มากขึ้นด้วย แต่เส้นทางเดินของการถอดรหัสที่การถอดรหัสที่สิ้นสุดภายในสแดกหลักของ DEC#1 (หลัง การย้าย T)นั้นอาจจะไม่ได้เป็นเส้นทางเดินของการถอดรหัสที่มีค่าเมตริกซ์ที่ดีที่สุด

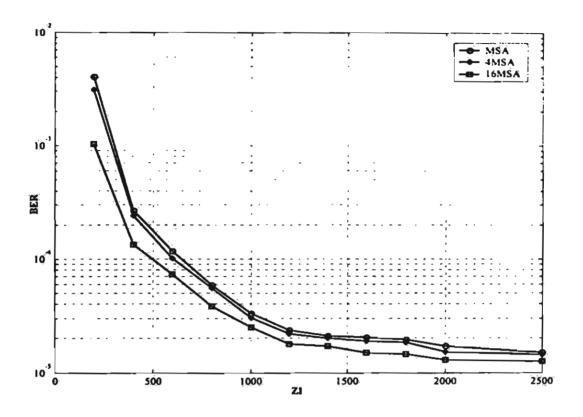

# 4.3.2 การทดสอบผลของขนาดสแตกหลัก $(Z_1)$ ต่อประสิทธิภาพ

โดยหลักการแล้วประสิทธิภาพในอัตราความผิดพลาดบิดของการถอดรหัสแบบ MSA ระบบตัวประมวลผลเดียวจะสามารถทำให้ดีขึ้นใต้โดยการเพิ่มขนาดของสแตกหลัก ในงานวิจัยนี้ใต้ ทดสอบผลของขนาดของ สแตกหลักสำหรับการถอดรหัสแบบ MSA โดยมัลดิไพรเซสเซอร์ และเปรียบ เทียบประสิทธิภาพในอัตราความผิดพลาดบิดกับค่าที่ได้จากการถอดรหัสแบบ MSA ระบบตัวประมวลผล เดียว จากผลการทดลองการเพิ่มขนาดของ Zi มีผลด่ออัตรากวามผิดพลาดบิดเช่นเดียวกันทั้งสองระบบ ภาพที่ 4.6 เป็นผลการทดสอบประสิทธิภาพ BER เมื่อเปลี่ยน Zi ค่าต่าง ๆ ที่ค่า Ei //o เป็น 4.5 dB เมื่อ เพิ่มขนาดของสแดกหลักขึ้นเรื่อย ๆค่าอัตราความผิดพลาดบิดของการถอดรหัสแบบ MSA ทั้งสองระบบ จะลดลงเรื่อย ๆตามลำดับเช่นกัน ด้วยเหตุผลเป็นไปตามสมการที่ (2.11) จนกระทั่งการเพิ่มขนาดสแดก หลักจะไม่มีผลต่ออัตราความผิดพลาดบิดของการถอดรหัสแบบ MSA ทั้งสองระบบ เมื่อเปรียบเทียบ ทั้งสองระบบจะเห็นว่าค่า BER ของการถอดรหัสระบบ MSA ซึ่งใช้ดัวประมวลผลตัวเดียวจะเริ่มคงที่เมื่อ ขนาด Zi เป็น 2000 และได้ค่า BER เท่ากับ 2.28 10 1 ในขณะที่การถอดรหัสแบบ MSA โดยมัลดิโพรเซสเซอร์ จะมีค่ากงที่เมื่อ Zi เป็น 1100 และได้ค่า BER เท่ากับ 2.24 10 2.10 1 แสดงให้เห็นว่าการใช้ จำนวนตัวประมวลผลมากขึ้นสามารถให้ค่าอัตราดวามผิดพลาดบิดที่เท่ากับหรือใกล้เดียงกับค่าอัตราดวามผิดพลาดบิดที่ได้จากการถอดรหัสแบบMSA ใช้ตัวประมวลผลตัวเดียว โดยใช้ขนาดของสแตกหลักเล็ก กว่า แต่อย่างไรก็ตามการเพิ่มจำนวนตัวประมวลผลกันระบบการถอดรหัส MSA โดยมัลดิโพรเซสเซอร์ จะ

มีผลต่ออัตราความผิดพลาดบิตน้อยลงเมื่อขนาดของ Z<sub>1</sub> มากกว่า 700 และการเพิ่มขนาดสแตคหลักจะไม่มี ผลต่ออัตราความผิดพลาดบิตของการถอดรหัสแบบ MSA ทั้งสองระบบ เมื่อค่ำ Z<sub>1</sub> มากว่า 2000 ซึ่งมีค่า BER ประมาณ 2.20\*10<sup>-3</sup> เนื่องจากการถอดรหัสแบบ MSA โดยระบบมัลติโพรเซสเซอร์สามารถถอด รหัสจำนวนบล็อกข้อมูลเสร็จภายในสแตคหลักของตัวประมวลผลตัวแรก DEC #1 ได้เพิ่มขึ้น ทำให้ จำนวนบล็อกที่ถูกถอดรหัสภายใน สแตครองมีจำนวนน้อยลงและจะเป็นบล็อกที่มีสัญญาณรบกวนมาก ๆ เท่านั้น

ภาพที่ 4.6 คำอัตรากวามผิดพลาดบิตเมื่อเปลี่ยนจำนวน  $Z_{\rm I}$

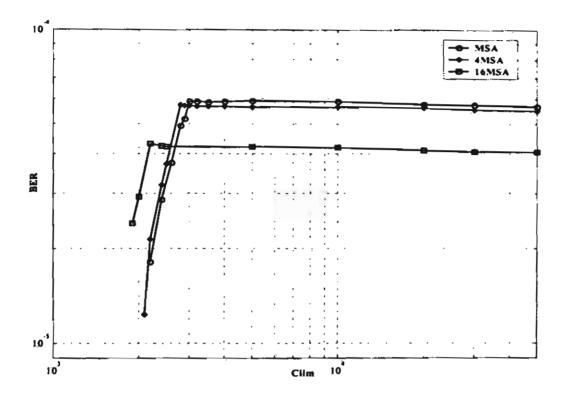

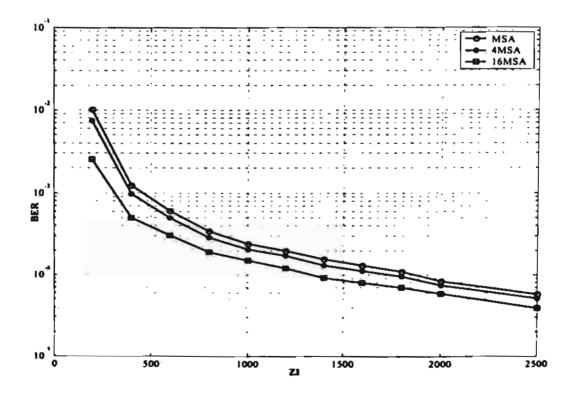

# 4.3.3 การทดสอบผลก่าลิมิตของการกำนวณ (Clim) ต่อประสิทธิภาพ

การถอดรหัสแบบซีเควนเซียลจะมีความแปรปรวนในการคำนวณ (Computational variability) คือค่าของการคำนวณของการถอดรหัสจะขึ้นอยู่กับปริมาณของสัญญาณรบกวน สำหรับการ ถอดรหัสแบบ MSA นั้นการกำหนดค่าลิมิตของการคำนวณเพื่อให้การถอดรหัสไม่มีอิเรชัว จะต้องกำหนด ให้  $C_{\rm lim}$  มีค่ามากกว่าค่าวิกฤตต่ำสุดของการคำนวณ  $C_{crit}$  ตามสมการที่ 2.6 การทดสอบหาต่ำสุดของการ คำนวณ  $C_{\rm min}$  ของระบบการถอดรหัสแบบ MSA โดยมัลดิโพรเชสเซอร์เพื่อให้การถอดรหัสไม่มีอิเรชัวนั้น แสดงตัวอย่างในดารางที่ 4.2 ผลการทดสอบค่า $C_{\rm min}$  ของการถอดรหัสแบบ MSA ที่ใช้ตัวประมวลผล เดียวเท่ากับ 569 ในขณะที่ค่า  $C_{crit}$  ที่ได้จากการคำนวณตามสมการที่ 2.6 เท่ากับ 897 ซึ่งการที่ค่า  $C_{\rm min}$  ด่ำ กว่าค่า  $C_{\rm crit}$  เนื่องจากการกำหนดให้ขนาดของสแตกรองมีขนาดเล็กกว่าขนาดของสแตกหลักมาก ๆ (Chevillat และ Costello ,1976) และการกำหนดค่า T เป็น 2 ผลการทดสอบเมื่อใช้ตัวประมวลผลหลายตัว ค่า  $C_{\rm min}$  ของการถอดรหัสแบบ MSA โดยมัลดิโพรเซสเซอร์ มีค่าเท่ากับ 640, 655 และ 655 เมื่อใช้ตัว ประมวลผล 2 ,3 และ 4 ตัวตามลำดับ การที่ค่า  $C_{\rm min}$  ของการถอดรหัสแบบ MSA ที่ใช้ตัวประมวลผลเดียว เนื่องจากการข้ายจำนวนโนดระหว่างตัวประมวลผล T ทำให้สแตกหลักของตัวประมวลผลดัวแรกมีเนื้อที่ในการคำนวณเพิ่มขึ้นเท่ากับ T แต่ค่า  $C_{\rm min}$  จะไม่ เปลี่ยนแปลงมากนักเมื่อเพิ่มจำนวนตัวประมวลผลเนื่องจากการถอดรหัสสามารถถึงค่า  $D_{\rm min}$  จะไม่ เปลี่ยนแปลงมากนักเมื่อเพิ่มจำนวนตัวประมวลผลเนื่องจากการถอดรหัสสามารถถึงค่า  $D_{\rm min}$

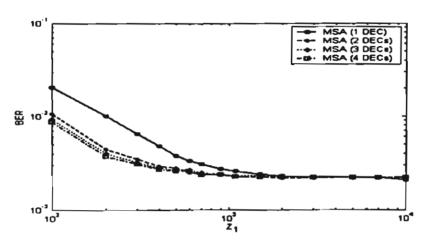

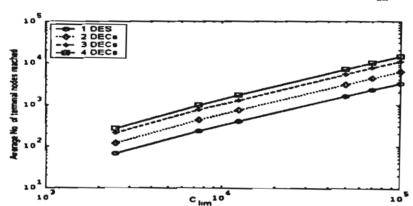

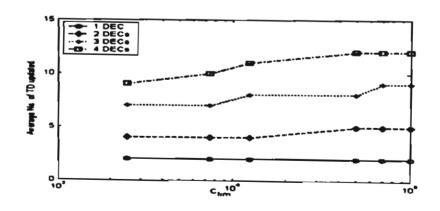

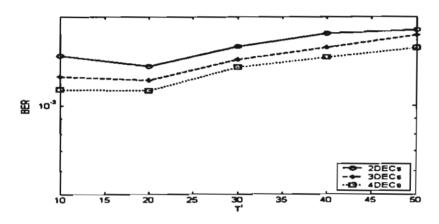

ศ้มอันคับแรก (First Tentative decision,TD) ภายในสแตกแรกของตัวประมวลผลอันคับก่อนหน้า ภาพที่ 4.7 แสดงคำอัตรากวามผิดพลาดบิตเนื่องจากผลการเพิ่มค่า  $C_{lim}$  ขึ้นเรื่อย ๆ เมื่อเพิ่มค่า  $C_{lim}$  คำอัตรากวามผิดพลาดบิตเนื่องจากการเพิ่มค่า  $C_{lim}$  จะทำให้โอกาสที่การถอดรหัสจะถึงโนดสุดท้ายในแผน ภูมิต้นไม้แทนรหัสมากขึ้น และที่ก่า  $C_{lim}$  เท่ากัน และการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์ให้ ค่าอัตรากวามผิดพลาดบิตที่ต่ำกว่า ในภาพที่ 4.8 แสดงจำนวนครั้งเฉลี่ยที่กระบวนการถอดรหัสถึงโนดสุด ท้ายในแผนภูมิต้นไม้แทนรหัสเทียบกับค่า  $C_{lim}$  จะเห็นว่าการประยุกต์ใช้วิธีการถอดรหัสแบบ MSA โดย มัลติโพรเซสเซอร์ให้จำนวนครั้งที่ถึงโนดสุดท้ายได้มากกว่า MSA ที่ใช้ตัวประมวลผลเดียว และนั่นหมาย ถึงโอกาสที่จะได้ทางเดินของการถอดรหัสที่ดีกว่าเมื่อใช้ตัวประมวลผลหลายตัว อย่างไรก็ตามจำนวนครั้ง ของการถึงโนดสุดท้ายในภาพที่ 4.8 ไม่ได้หมายถึงจำนวนครั้งของการบันทึกค่าใหม่ของ TD เสมอไป ภาพที่ 4.9 ได้แสดงให้เห็นถึงจำนวนครั้งเฉลี่ยที่มีการบันทึกค่าทางเดินใหม่ใน TD ซึ่งผลที่ได้สอดกล้อง กับภาพที่ 4.8 นั่นคือระบบการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์ให้คำเฉลี่ยของจำนวนครั้งใน การบันทึกค่าใหม่ที่สูงขึ้นและจะสูงกว่าเดิมเมื่อเพิ่มจำนวนตัวประมวลผลในการถอดรหัสมากขึ้น

ตารางที่ 4.2 ค่าจำนวนการคำนวณต่ำสุดที่ทำให้การถอครหัสสมบูรณ์ ( erasure free)

| จำนวนตัว | Z <sub>1</sub> = 150 | $Z_1 = 300$ |

|----------|----------------------|-------------|

| ประมวล   | C <sub>min</sub>     | $C_{min}$   |

| ผล       |                      |             |

| 1 DEC    | 569                  | 855         |

| 2 DECs   | 640                  | 942         |

| 3 DECs   | 655                  | 956         |

| 4 DECs   | 655                  | 954         |

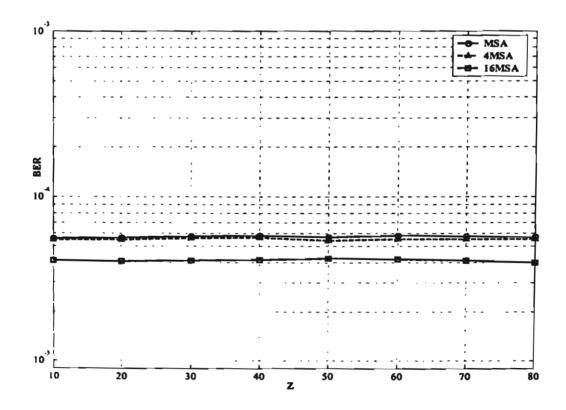

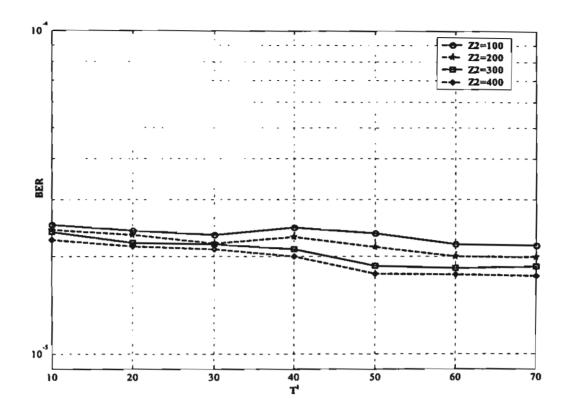

# 4.3.4 การทดสอบผลของขนาดของสแตกรอง (Z) ต่อประสิทธิภาพ

ขนาคของสแตกรองเป็นปัจจัยหนึ่งที่มีผลต่อการถอดรหัสแบบ MSA ซึ่งการกำหนด ขนาคของ สแตกรองจะมีผลต่ออิเรชั่วได้คือถ้ากำหนดขนาดของสแตกรองให้มีขนาดเล็กกว่าขนาดของส แตกหลักมาก ๆ จะทำให้การถอดรหัสสามารถถึงโนคสุดท้ายของเส้นทางตามแผนภูมิต้นไม้รหัสเร็วขึ้น และมีค่าของการกำนวณที่ต่ำลงด้วย ภาพที่ 4.10 แสดงก่าอัตราความผิดพลาดบิตเมื่อใช้ระบบการถอดรหัส แบบ MSA โดยมัลติโพรเซสเซอร์เมื่อทำการเปลี่ยนขนาดของสแตกรองผลการทดสอบแสดงให้เห็นว่ามี อัตราความผิดพลาดบิตที่ต่ำกว่าระบบการถอดรหัสแบบ MSA เดิม แต่การเปลี่ยนขนาดของสแตกรองมีผล ต่ออัตรากวามผิดพลาดบิตที่น้อยมากทั้งสองระบบ และเมื่อเปรียบเทียบกับระบบ MSA เดิม ที่ขนาดของส แตกหลักเป็นสองเท่า (300) ค่าอัตรากวามผิดพลาดบิตที่ได้จากระบบการถอดรหัสแบบ MSA โดยมัลติ โพรเชสเชอร์ก็ยังมีอัตรากวามผิดพลาดบิตที่ค่ำกว่าซึ่งแสดงว่าการเพิ่มจำนวนตัวประมวลผลให้ประสิทธิ ภาพที่ดีกว่าการเพิ่มขนาดของสแดกหลักในขณะที่ปัจจัยอื่น ๆเหมือนเดิม

ภาพที่ 4.7 คำอัตราความผิดพลาดบิตเมื่อเปลี่ยนจำนวน  $C_{\rm lm}$

ภาพที่ 4.8 จำนวนครั้งเฉลี่ยที่การถอดรหัสถึงในคสุดท้ายในแผนภูมิต้นไม้แทนรหัส

ภาพที่ 4.9 จำนวนครั้งเฉลี่ยที่มีการบันทึกค่า TD ใหม่

ภาพที่ 4.10 ค่าอัตราความผิดพลาดบิตเมื่อเปลี่ยนจำนวน Z

# 4.3.5 การทดสอบผลจำนวนโนด(T) ต่อประสิทธิภาพ

จำนวนโนคที่ข้าขระหว่างสแตกเป็นอีกปัจจัยหนึ่งที่มีผลต่อการถอดรหัสแบบ MSA ซึ่ง การกำหนดจำนวนโนคจะมีผลต่อจำนวนสแตกรองและมีผลต่ออิเรชัวกือถ้ากำหนดจำนวนโนคจ้อมูลที่ถูก ข้าขมากจำนวนสแตกรองที่ใช้ในการถอดรหัสก็เพิ่มมากขึ้น(ในขณะที่ขนาดของสแตกรองคงที่) และทำให้ การถอดรหัสสามารถถึงในคสุดท้าขของเส้นทางตามแผนภูมิคันไม้รหัสช้าและมีค่าของการคำนวณเพิ่ม ขึ้นด้วย ภาพที่ 4.11 แสดงค่าอัตราความผิดพลาดบิตเมื่อเปลี่ยนจำนวนโนคจ้อมูลที่ถูกข้าย ในขณะที่ T เท่ากันระบบการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์จะมีค่าอัตราความผิดพลาดบิตที่ค่ำกว่าระบบ การถอดรหัสแบบ MSA เดิม และการเพิ่มจำนวนโนคข้อมูลที่ข้าขระหว่างสแตกของตัวประมวลผลแต่ละ ตัวจะสามารถลดค่าอัตราความผิดพลาดบิตด้วย

ภาพที่ 4.11 ก่าอัตราความผิดพลาดบิตเมื่อเปลี่ยนจำนวน T

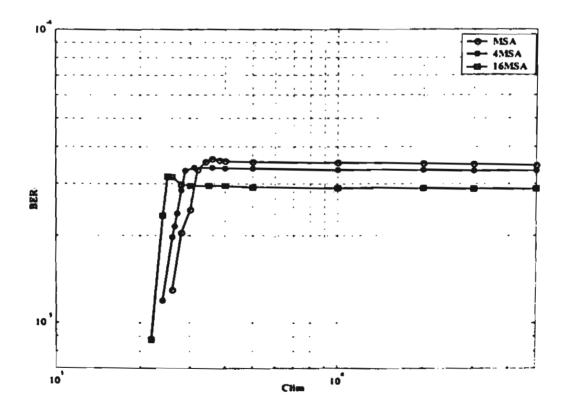

# 4.3.6 ค่าอัตราความผิดพลาดบิตที่ค่าสัญญาณรบกวนต่าง ๆ

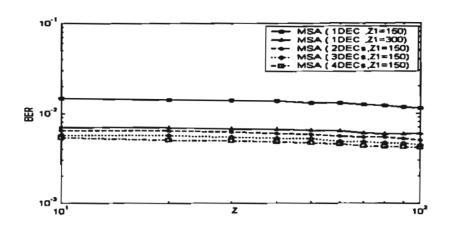

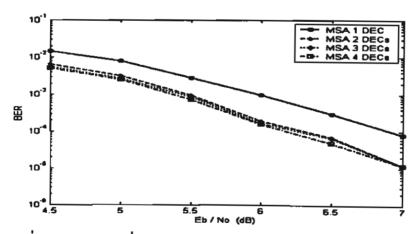

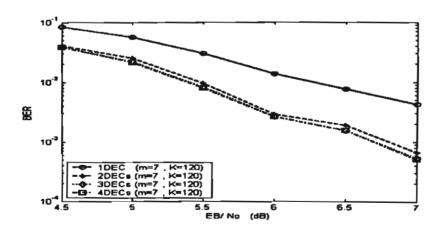

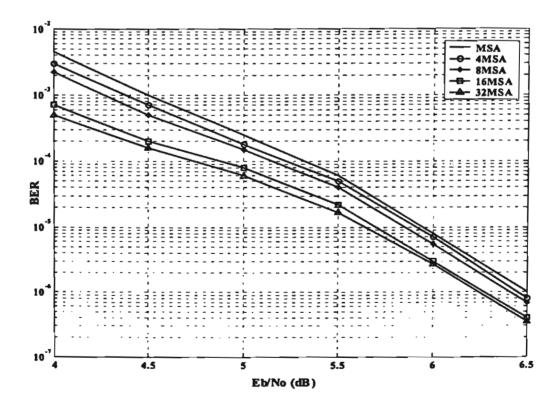

ผลการทคสอบการถอครหัสแบบ MSA โดยมัลติโพรเซสเซอร์ที่ค่าสัญญาณรบกวนค่า ต่าง ๆเพื่อเปรียบเทียบประสิทธิภาพในอัตราความผิดพลาดบิตกับการถอครหัสแบบ MSA ที่ใช้ตัว ประมวลผลเคียวภาพที่ 4.12 เป็นการทคสอบประสิทธิภาพของ BER เมื่อเปลี่ยนค่า  $E_b/N_o$  ในช่วง  $4.5-7.0\,dB$  (ค่าความยาวคอน สเตรนท์ของตัวเข้ารหัส m=5, Generator matrices  $G_i=110101$ ,  $G_2=101111$ ) จะเห็นว่าค่า BER ในการถอครหัสเมื่อใช้วิธีการถอครหัสแบบ MSA โดยมัลติโพรเซสเซอร์ มีค่าค่ำกว่า BER ของระบบ MSA เดิมซึ่งใช้ตัวประมวลผลตัวเดียวและค่า BER จะมีค่าลดลงต่อไปอีกเมื่อ เพิ่มตัวประมวลผล

ภาพที่ 4.12 เป็นการทดสอบประสิทธิภาพของ BER เมื่อเปลี่ยนค่า  $E_{\rm s}/N_{\rm s}$  ในช่วง 4.5-7.0 dB จะเห็นว่าก่า BER ในการถอดรหัสเมื่อใช้วิธีการถอดรหัสแบบขนานสำหรับ MSA มีค่าต่ำกว่า BER ของระบบ MSA เดิมซึ่งใช้ตัวประมวลผลตัวเดียว อย่างไรก็ตามเมื่อเพิ่มจำนวนตัวประมวลผลเป็น 3 และ 4 ตัว ไม่ช่วยให้ประสิทธิภาพในอัตราความผิดพลาดบิตของการถอดรหัสดีขึ้นจากเดิมมากนักในขณะที่ขนาดของ  $Z_{\rm l}$  ใหญ่มาก

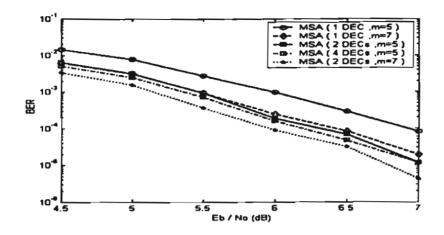

ภาพที่ 4.13 เป็นการทคสอบประสิทธิภาพของ BER เมื่อค่าความยาวคอนสเตรนท์ของตัว เข้ารหัสเป็น m=7 Generator matrices  $G_i=10111101$ ,  $G_2=11001011$  จะเห็นว่าค่า BER ในการถอด รหัสเมื่อใช้วิธีการถอดรหัสแบบ MSA โดยมัลติโพรเซสเซอร์ ที่ค่า m=5 สามารถให้ค่า BER ต่ำกว่าค่า BER ที่ได้จากการถอดรหัสระบบ MSA เดิมซึ่งใช้ค่าความยาวคอนสเตรนท์มากกว่า(m=7)

ภาพที่ 4.14 เป็นการทคสอบประสิทธิภาพของ BER ที่ค่า T ต่าง ๆ เมื่อทคสอบในขณะ ที่ขนาคของสแคกหลัก  $Z_1=75$  และใช้ m=7, K=120 จะเห็นว่าค่า T ที่เหมาะสมคือ T=20 ซึ่งให้ค่า BER ต่ำที่สุดในทุกกรณีของการถอครหัสแบบขนานเมื่อใช้จำนวนตัวประมวลผลต่างกัน และเมื่อทคสอบ ที่ค่า  $E_b/N_o$  ต่าง ๆกัน คังภาพที่ 4.15 ผลที่ได้แสคงให้เห็นว่าเมื่อเพิ่มค่า m และ K ในขณะที่ลดขนาคของ  $Z_1$  ลงจาก 150 เป็น 75 ตัวประมวลผลที่เพิ่มขึ้นสามารถปรับปรุงประสิทธิภาพของการถอครหัสในอัตรา ความผิดพลาดบิตได้เพิ่มขึ้นเล็กน้อยเมื่อเทียบกับรภาพที่ 4.12

ภาพที่ 4.12 ค่า BER ที่ค่า  $E_{\rm h}/N_{\rm o}$  ต่างๆ ( m=5 , K=60 ,  $Z_1=150$  , T'=50 )

ภาพที่ 4.13 ค่า BER ที่ค่า  $E_b$  /  $N_o$  ค่างๆ ( m=5 , m=7 K=60 ,  $Z_1=150$  , T'=50 )

ภาพที่ 4.14 ค่า BER กับ T เมื่อใช้ ค่าของ m=7 และ K=120  $Z_1=75$

ภาพที่ 4.15 ค่า BER ที่ค่า  $E_h / N_n$  ต่างๆ ( m=7 , K=120 ,  $Z_{\parallel}=75$  , T'=20 )

# 4.4 ผลการทดสอบประสิทธิภาพการลอดรหัสแบบ MSA ในรหัสแบบรีเคอร์ซีพซิสเต็มเมติกคอนโวลูชัน

หัวข้อนี้เป็นการแสดงผลการทดสอบประสิทธิภาพของการถอดรหัสแบบ M-MSA เปรียบเทียบกับ การถอดรหัสแบบ TS ซึ่งในการทดสอบจะใช้แบบจำลองระบบที่มีการเข้ารหัสสัญญาณแบบ RSC ผ่าน ช่องสื่อสารแบบ AWGN โดยใช้โปรแกรมคอมพิวเตอร์ภาษาซีเพื่อทำการจำลองตัวเข้ารหัส ตัวถอดรหัส และช่องสื่อสารในระบบปฏิบัติการลินุกซ์ พารามีเตอร์ที่สำคัญซึ่งใช้ในการทดสอบมีดังต่อไปนี้

- จำนวนข้อมูลที่ส่ง คือ 1,000,000 บิต โดยแบ่งอกเป็นบล็อก บล็อกละ 100 บิต

- เข้ารหัสแบบ RSC โดยมีเมตริกของตัวสร้างรหัส  $G = \begin{bmatrix} 1 & \frac{67}{51} \end{bmatrix}$ และค่าความยาวคอนสเตรนท์

- ใช้การตัดสินใจแบบซอฟท์ 8 ระดับ

- E, / N จาก 0.5 ถึง 1.5 dB

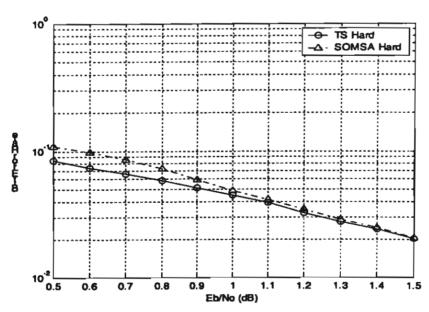

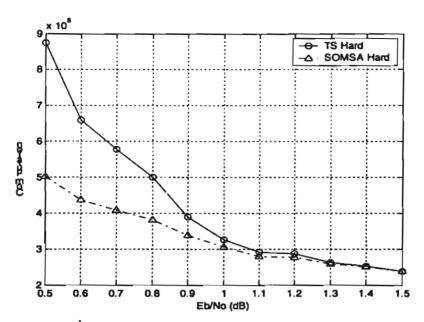

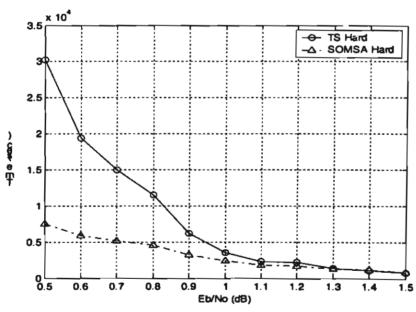

ภาพที่ 4.16 แสดงการเปรียบเทียบอัตราความผิดพลาดบิตของการถอดรหัสแบบ M-MSA และ TS จากรูปจะเห็นว่าการถอดรหัสแบบTS ให้อัตราความผิดพลาดบิตต่ำกว่าการถอดรหัสแบบ M-MSA เล็ก น้อย ในช่วงที่ก่า  $E_i/N_o$  ต่ำๆ และจะค่อยๆ ใกล้เกียงกันเมื่อ  $E_i/N_o$  มีค่ามากขึ้น แต่เมื่อพิจารณาทดสอบ เปรียบเทียบในจำนวนรอบของการกำนวณในการถอดรหัส และเวลาในการถอดรหัส ดังแสดงในภาพที่ 4.17 และ 4.18 พบว่าการถอดรหัสแบบ M-MSA มีจำนวนรอบของการกำนวณและเวลาในการถอดที่น้อย กว่าการถอดรหัสแบบ TS ในช่วงที่ก่า  $E_i/N_o$  ต่ำๆ และจะก่อยๆ ใกล้เกียงกันเมื่อ  $E_i/N_o$  มีค่ามากขึ้น

ภาพที่ 4.16 การเปรียบเทียบอัตราผิดพลาคบิตของการถอดรหัส

ภาพที่ 4.17 การเปรียบเทียบการคำนวณของการถอดรหัส

ภาพที่ 4.18 การเปรียบเทียบเวลาในการถอครหัส

# บทที่ 5 สรุปงานวิจัย

งานวิจัยนี้ได้นำเสนอการประยุกต์ใช้วิธีการถอดรหัสแบบขนานโดยใช้ตัวประมวลผลหลายตัวกับ อัล กอริทึมการถอดรหัสแบบ MSA สำหรับรหัสคอนโวลูชัน เพื่อปรับปรุงประสิทธิภาพในอัตราความผิด พลาดบิตของการถอดรหัสแบบ MSA เดิมให้ดีขึ้น ซึ่งปัญหาในการถอดรหัสแบบ MSA เดิมนั้น คือ บล็อก ที่มีปริมาณของสัญญาณรบกวนมากไม่สามารถสิ้นสุดกระบวนการถอดรหัสในสแตคหลักได้และเมื่อทำ การย้ายโนดบางส่วนในสแตคหลักมาทำการถอดรหัสต่อในสแตครอง โอกาสที่การถอดรหัสจะสามารถ กลับมาสิ้นสุดที่แสตคหลักนั้นมีก่าน้อยมาก ดังนั้นการถอดรหัสมักจะสิ้นสุดโดยก่าของ  $C_{\rm lm}$  ซึ่งให้ค่า อัตราความผิดพลาดบิตสูง ในงานวิจัยนี้ได้ทำการประยุกต์การถอดรหัสแบบขนานกับ MSA เพื่อปรับปรุง ประสิทธิภาพในอัตรากวามผิดพลาดบิตของ MSA เดิมให้ดีขึ้น ที่ก่า  $C_{\rm lm}$  และปริมาณหน่วยความจำที่เท่า กัน ผลการจำลองด้วยกอมพิวเตอร์ ปรากฏว่าการถอดรหัสแบบขนานโดยใช้ตัวประมวลผลหลายตัว สามารถทำให้ก่าอัตราความผิดพลาดบิตใน MSA ลดลงได้อย่างมาก

ค่อมาได้ทำการประยุกต์วิธีการการถอดรหัสแบบหลายสแตกชนิคคัดแปลงเพื่อใช้ถอดรหัส สัญญาณแบบรีเกอร์ซีพซิสเต็มมาติกกอนโวลูซัน โดยการประยุกต์วิธีการฉอดรหัสแบบทวินสแตกมาใช้ เพื่อสร้างผลลัพธ์แบบฮาร์ดและผลลัพธ์แบบซอฟท์ ผลการทดสอบประสิทธิภาพในอัลกอริทึมการถอด รหัสแบบหลายสแตกชนิคคัดแปลง พบว่า สามารถที่จะให้อัตราความผิดพลาคบิตที่ใกล้เกียงกับกรถอด รหัสแบบทวินสแตก แต่มีข้อที่น่าสนใจคือ เวลาที่ใช้ในการถอดรหัสและจำนวนรอบในการคำนวณใน กระบวนการถอดรหัส โดยเฉลี่ยมีค่าลดลงอย่างมากสำหรับค่า  $E_{IN_g}$  ต่ำๆ ปัจจุบันงานวิจัยนี้กำลังอยู่ใน ระหว่างการดำเนินการสร้างผลลัพธ์แบบซอฟท์โดยใช้ผลลัพธ์แบบฮาร์ดที่ได้ เพื่อที่จะนำไปประยุกต์ใช้ ในวิธีการถอดรหัสแบบวนซ้ำสำหรับถอดรหัสแบบเทอร์โบต่อไป

### เอกสารค้างอิง

- Forney, G.D. 1974. Convolutional Codes III: Sequential Decoding. Inf. Control, Vol. 25, pp. 267-297

- Lin, S., and Costello, D. J. Jr. 1983. Error Control Coding: Fundamentals and Applications.

Prentice-Hall

- Haccoun, D., and Begin, G. 1989. High-rate punctured convolutional codes for Viterbi and sequential decoding. IEEE Trans. Commun. Vol. 37 No. 11, pp. 1113-1125

- Forney, Jr., G.D., and Bower, E.K. 1971. A High-Speed Sequential Decoder Prototype Design and Test. IEEE Transaction on Communication Technology, COM-19(5), 821-835.

- Belanger, N., Haccoun, D., and Savaria, Y. 1994. A Multiprocessor Architecture for Multiple Path Sequential Decoders. IEEE Transactions on Communications, 42(2/3/4), 951-957.

- Chivillat, P.R., and Costello, Jr., D.J. 1976. A Multiple Stack Algorithm for Erasurefree Decoding of Convolutional Codes, IEEE Transactions on Commun., COM-25(12), 1460-1470

- Jelinek, F. 1969 A fast sequential decoding using a stack, IBM J. Res. Dev., Vol.13, pp. 675-685

- Lin, Y., and Tu, S.H. 1997. Modified multiple stack algorithm for decoding convolutional codes. IEE Pro.-Commun, Vol. 44, No. 4, August, 221-228.

- Kaiping, L., and Samir, K. 1999. A Bidirectional Multiple Stack Algorithm. IEEE Transactions on Communications, Vol. 47, No. 1, January, 6-9.

ภาคผนวก

### Parallel Decoding Scheme for Multiple Stack Algorithm

| Journal:                      | IEE Proc. Communications                                      |  |

|-------------------------------|---------------------------------------------------------------|--|

| Manuscript ID:                | COM-2005-0036.R1                                              |  |

| Manuscript Type:              | Research Paper                                                |  |

| Date Submitted by the Author: | 25-May-2005                                                   |  |

| Keyword:                      | CHANNEL CODING, CONVOLUTIONAL CODES, MULTIPLE STACK ALGORITHM |  |

powered by ScholarOne Manuscript Central\*\*

## Parallel Decoding Scheme for Multiple Stack Algorithm

Virasit Imtawil\*, Ph.D. and Wanlop Surakampontorn\*, Ph.D.

\*Department of Electrical Engineering, Faculty of Engineering,

Khon Kaen University, Khonkaen, THAILAND 40002

Corresponding author email address: virasit@kku.ac.th

Department of Electronics, Faculty of Engineering,

King Mongkut's Institute of Technology Ladkrabang, Bangkok, THAILAND 10520

Abstract In order to improve the error performance particularly in a very noisy block which requires excessive tree searches, a parallel decoding scheme for a multiple stack algorithm (MSA) is proposed in this paper. In this scheme, apart from the main decoder working on the main stack, a scalable set of multiple decoders working in parallel on their multiple stacks are incorporated. All the decoders are working almost independently with the help of the control processor, where the decoding process and the termination rules are outlined. Two cases, 4-processor MSA and 16-processor MSA, are employed as examples to investigate the performance of the proposed scheme. Comparing with the conventional MSA, extensive computer simulations show that the bit error probabilities (BER) are significantly improved.

Indexing terms: Multiple stack algorithm; Parallel decoding; Convolutional codes

#### 1. Introduction

Convolutional codes are widely used for error correction in both satellite and terrestrial communications. There are two main techniques for decoding convolutional codes namely the Viterbi algorithm (VA) and the sequential decoding [1]. For the sequential decoding, although it is not optimal, arbitrarily low error probabilities can be achieved since its decoding effort does not depend on the code constraint length [2-3]. In addition, increasing the code constraint length means to improve the error correcting capability of the code. However, the most undesirable attribute of the sequential decoding is that noisy blocks may require a large number of

#### Communications

computations and decoding times can occasionally exceed the computational limit ( $C_{lim}$ ), causing the information to be lost or erased (marked as an erasure). Chevillat and Costello [4] proposed an algorithm for erasurefree sequential decoding called the multi stack algorithm (MSA). The MSA is developed from the single stack algorithm (SSA) [5] by splitting the stack into many stacks, where the first stack is usually large and the second and higher order stacks with typically all the same sizes are relatively small. The basic idea of the MSA is to make use of higher order stacks for blocks that require an excessive number of computations to be decoded. The MSA decoding process will be terminated when either a terminal node is found in the main stack or the computation limit  $C_{\rm lim}$  is reached. However, decoding termination with  $C_{\rm lim}$  usually gives very high error rate. Later Y.Lin and S.H. Tu [6] proposed a modified multiple stack algorithm that rearranged the memory used to implement stacks as a ring-like structure. The main advantage of their work is the flexibility in defining the size of the top transferred nodes between stacks (T) and the size of higher order stacks (Z) to be as large as desired in order to improve the bit error performance. However, any increase in T or Z requires more computation and thereby a long delay may be occurred. Kallel and Li proposed a bidirectional multiple stack algorithm (BMSA) in 1999 [7]. Their technique was to apply the bi-directional tree search to the MSA. It has been shown that the performance of the conventional MSA is significantly improved with the use of a bidirectional decoding scheme.

Recently, in order to achieve high-throughput rate or to reduce decoding delay, parallel decoding has gained some interest from many researchers in the coding community [8-13]. In this study, a parallel decoding scheme for the MSA is proposed. The main idea is to exploit scalable multiple decoders working in parallel to search the correct path in the code tree. The scheme comprises of a main decoder extending paths on the main stack and many scalable sub-decoders extending paths on the sub-stacks. All the decoders work independently in parallel with the help of the control processor. It is found by extensive computer simulations that the error performance of our proposed scheme is better than that of the conventional MSA. The paper is organized as follows. Background on the MSA decoding is briefly discussed in Section 2. In Section 3, the proposed parallel decoding scheme for the MSA is described, where description of the scheme,

decoding process and the termination rules are given. In Section 4, performance of the proposed scheme is presented by computer simulation results in comparison with the conventional MSA. Finally, Section 5 is the conclusion of this paper.

#### 2. Background on the MSA

In the MSA, when the first stack fills up, the top T nodes with best metrics are transferred to a second stack. Decoding then continues in the second stack using only these T transferred nodes. If a path in the second stack reaches a terminal node before the stack fills up, the path is stored in a special register called the tentative decision (TD). The decoder then deletes the remaining nodes in the second stack and returns to the first stack where decoding continues. Since T nodes were removed there are now exactly T free places in the first stack. If the decoder reaches a terminal node before the first stack fills up again, the metric of the new path is compared to that of the TD. The path with the better metric is retained and becomes the final decoding decision. It can be shown that a decision made in this way is as good as that made by the SSA with an arbitrarily large stack. However, if the first stack fills up again before the end of the tree is reached, a new second stack is formed by transferring from the top T nodes of the first stack. Additional stacks are formed in a similar manner until a path to a terminal node is found. The decoder compares this path with the TD and retains the path with the best metric. The rest of the nodes in the current stack are then deleted and decoding proceeds in the previous stack. Occasionally, the decoder may not reach a terminal node in the first stack after the number of node extensions (computations) exceeds the computational limit  $C_{lim}$ . In this case, the TD becomes the final decoding decision. To guarantee erasurefree decoding  $C_{lim}$  must be carefully chosen. For the case T=1 and a rate of 1/w convolutional code (where w is the codeword length in bits) with the constraint length  $\nu$ the value of  $C_{lim}$  must be at least equal to the critical value  $C_{crit}$  given by

$$C_{crit} = \sum_{i=1}^{k-1} (Z_i - 1) + 2(\nu - 1)$$

(1)

where  $Z_i$  is the size of stack i, and k the number of tree branches without tail (the information frame size). The decoding termination with  $C_{lim}$  in the MSA usually happens with very noisy blocks that require excessive tree searches. The decoded bit error rate in this case is very high. Although, the error performance of the MSA can be improved by increasing the value of  $C_{lim}$  or increasing the size of the first stack, this choice may not be possible in some applications where decoding delays are not acceptable or the memory storage is limited with a single-processor decoder. In such situations we propose the use of a Parallel decoding process.

#### 3. A Parallel Decoding Scheme for the MSA

Our main goal is to apply a scalable set of multiple decoders concurrently searching the correct path in the code tree. Therefore, the probability of finding the correct path is raised up with our proposed scheme.

#### 3.1 Description of the proposed scheme

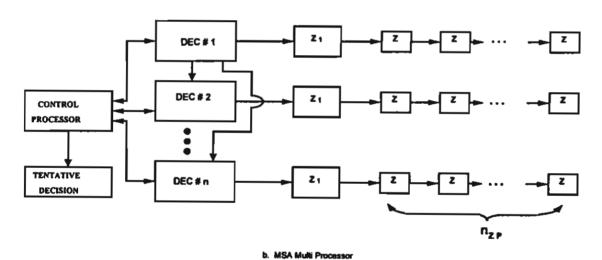

The proposed parallel decoding scheme for the MSA is shown in Fig. 1. The arrangement and the processing of the scheme are as follows.

- (1) It consists of the following components: the main (first) decoder (DEC#1), scalable multiple sub-decoders (DEC#2, DEC#3,..., DEC#n), the control processor (CP), the main (first) stack ( $Z_1$ ), n-1 primary sub-stacks ( $Z_2$ ), which equal to the number of sub-decoders and several secondary sub-stacks (Z).

- (2) The main decoder extends paths of the main stack only based on the SSA.

- (3) Each sub-decoder is identical. One sub-decoder extends paths of its primary sub-stack and secondary sub-stacks based on the conventional MSA.