## Redundant Three-Phase AC to DC Converter using Single-Phase CUK Rectifier Module with Minimized DC Bus Capacitance

Uthen Kamnarn and Surasak Yousawat

Department of Electrical Engineering

Rajamangala University of Technology Lanna

128 Huay Keew Road, Muang Distric, Chiang Mai,

Thailand 50000

Email:uthen@rmutl.ac.th, surasak@rmutl.ac.th

Yutthana Kanthaphayao and Viboon Chunkag

Department of Electrical Engineering

King Mongkut's University of Technology North Bangkok

1518 Pibulsongkram Road, Bangsue, Bangkok,

Thailand 10800

Email: yutthana\_k44@hotmail.com , vck@kmutnb.ac.th

Abstract— This paper presents a redundant three-phase ac to dc converter using single-phase CUK rectifier module with nearly power factor and minimized dc bus capacitance based on power balance control technique. The focus of the proposed control strategy is to reduce the dc bus capacitance value under condition step load change from 10% (75W) to 100% (750W). Using power balance control technique does minimized dc bus capacitance, inductor current sharing, redundant operation, high power factor and tight dc bus voltage works on the principle of modular three-phase rectifier with parallel single-phase CUK rectifier module. Simulation results are used to illustrate the operation and performance features of the modular three-phase rectifiers.

#### I. INTRODUCTION

Increasing demand for high power converters in telecommunication, and computer power supplies drives the need for higher flexibility in control, increased level of system integration, and more reliability, besides achieving high levels of performance [1]. In recent years, the low harmonic current in line side is required by the legislation of regulations for controlling harmonics [2]-[5]. The power range of the switching mode power supplies (SMPS) market starts from a few watts to some kilowatts. In the kilowatt range, the telecommunication power supplies form the major part of the SMPS market [6]-[7]. The supply voltage of most telecommunication switching equipment is 48V [8]-[12]. This voltage value is a universal standard for telecommunications equipment, and is well defined both by the European Telecommunications Standards Institute (ETSI) and the American National Standards Institute (ANSI). A 48V dc power supply system consists of a number of paralleled rectifiers that connected to one or more battery strings also connected in parallel. Generally, the power levels of the rectifier modules involved in telecommunication applications are 750W or 1,500W [13]-[15].

The conventional dc 48 V output power supply for the telecommunication system have the three-phase PWM rectifier in the first in order to obtain the sinusoidal input current waveforms [16]-[20]. In addition to this, the conventional power supplies have the dc to dc converter

which is isolated between input side and output one in second steps to obtain the dc -48 V. As described above, the conventional power supply is proposed of two power converter; three-phase PWM rectifier [21]-[25] and dc to dc converter. For this reason, the conventional power supply cause the low power efficiency and high cost. Also, a dc capacitor smoothing the intermediate voltage together with a voltage detector to control this voltage is required. To solve this problem, the power conversion system which has CUK converter is has been already proposed. Using the CUK converter, this power conversion system can convert three-phase ac input power into the isolated dc output power.

However, the capacitor technology has been getting more and more attention in industry application. The dc bus capacitor is the most important passive component in a telecommunication system. Conventional designs have been using a set of electrolytic bulk capacitors to smooth dc bus voltage.

So, the first issue of this paper presents a three-phase ac to dc converter using CUK rectifier module which can directly convert 3-phase ac input into the dc -48 V output with minimized dc bus capacitor. The proposed rectifier consists of three power converter which is connected in 3-phase line to neutral. Controlled the duty factor of each active switch, the proposed rectifier occur the sinusoidal waveforms with power factor of unity. The benefit of the proposed control strategy is excellent power factor correction, good inductor current sharing and fast dynamic transient response with minimized dc bus capacitance. Significant results are (1) size reduction, (2) cost reduction, and (3) transient response improvement.

In the second issue, redundant rectifiers meet two needs: battery recharging after mains outage and continued operation if one rectifier fails. The design concept and the feasible performance evaluations of the redundant three-phase ac to dc converter using single-phase isolated CUK rectifier module is discussed.

The objectives of this paper are: minimized dc bus capacitance, redundancy (n+1), inductor current sharing, nearly unity power factor, low harmonic distortion, and improve dynamic transient response. Simulation results are presented. It's in agreement with the theoretical analysis.

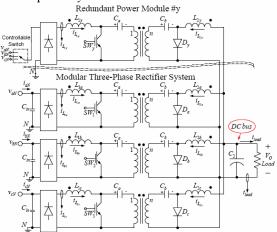

### II. REDUCTION OF DC BUS CAPACITANCE WITH THREE-PHASE AC TO DC CONVERTER BASED ON POWER BALANCE CONTROL TECHNIQUE

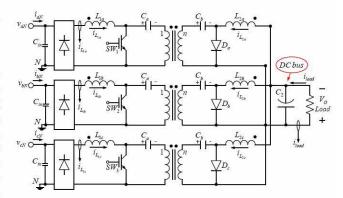

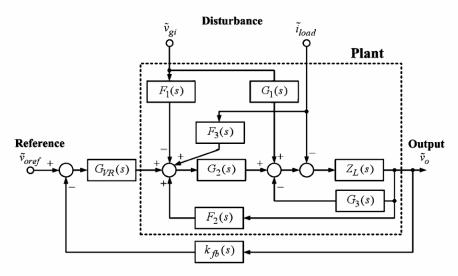

Fig. 1 shows power circuit of the modular three-phase ac to dc converter. In this topology, three identical single-phase isolated CUK rectifier modules are used. They are connected in parallel on a common dc bus to feed the dc load. The rectifier is termed as Y-connected. A power balance control technique is employed to give a fast dynamic transient response. The objectives of the proposed control strategy are to eliminate harmonics, inductor current sharing, regulated dc output voltage and meet the transient response requirements of step load change and minimized dc bus capacitance.

#### A. Average Small-Signal Analysis

The average small signal model of the modular threephase ac to dc converter using CUK rectifier module based on power balance control technique is:

$$3V_{gi}I_{L_{1i}} = V_{o}I_{o} \tag{1}$$

$V_{gi}$  is RMS value of the rectifier voltage,  $I_{L_{li}}$  is RMS value of the inductor current,  $V_o$  is average output voltage and  $I_o$  is average output current. The peak value of the inductor current is

$$\hat{I}_{L_{1i}} = \frac{K_2 V_o I_{load}}{3V_{oi}} \tag{2}$$

$$\hat{I}_{Lref_{1i}} = \hat{I}_{L_{1i}} + I_{VR} \tag{3}$$

$\hat{I}_{L_{ref_{1i}}}$  is peak value of the inductor reference current,  $\hat{I}_{L_{1i}}$  is peak value of the inductor current,  $I_{VR}$  is correcting signal from PI regulator and  $K_2$  is conversion gain of inductor current. The inductor reference current is:

$$i_{Lref_{11}} = \hat{I}_{Lref_{11}} \left| \sin(\omega t) \right|$$

(4

$$i_{Lref_{12}} = \hat{I}_{Lref_{12}} \left| \sin(\omega t - 120^{\circ}) \right| \tag{5}$$

$$i_{Lref_{13}} = \hat{I}_{Lref_{13}} \left| \sin(\omega t - 240^{\circ}) \right| \tag{6}$$

The dynamic equation at common dc bus is

$$\sum_{i=1}^{3} I_{L2i} = C_2 \frac{dV_o}{dt} + I_{load} \tag{7}$$

Where the  $\overline{V}$  means steady-state value and  $\tilde{v}$  means small-signal value. Applying the perturbations in (1), (2), (3), and (7), and performing the small-signal approximation ( $\tilde{v}$  .  $\tilde{v}$  =0) results in :

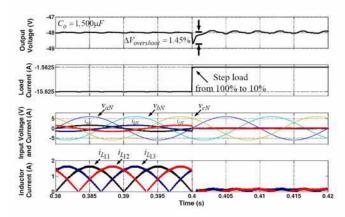

Fig. 1. Modular three-phase ac to dc converter using isolated CUK rectifier module with minimized dc bus capacitance based on power balance control technique.

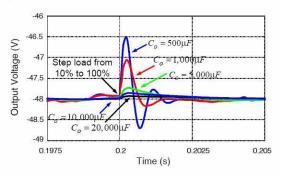

Fig. 2. Simulation result of transient response at common dc bus capacitor when step load change from 10% (75 W) to 100% (750 W).

$$\tilde{i}_{o} = \frac{3K_{1}\overline{\hat{I}}_{Lref_{1i}}}{\overline{V}_{o}}\tilde{v}_{gi} + \frac{3K_{1}\overline{V}_{gi}}{\overline{V}_{o}}\tilde{i}_{Lref_{1i}} - \frac{\overline{I}_{o}}{\overline{V}_{o}}\tilde{v}_{o}$$

(8)

$$\tilde{i}_o = C_2 \frac{d\tilde{v}_o}{dt} + \tilde{i}_{load} \tag{9}$$

$$\tilde{i}_{Lref_{1i}} = \tilde{i}_{L_{1i}} + \tilde{i}_{VR} \tag{10}$$

$$\tilde{\hat{i}}_{L_{1i}} = \frac{K_2 \overline{V}_o}{3 \overline{V}_{gi}} \tilde{i}_{load} + \frac{K_2 \overline{I}_{load}}{3 \overline{V}_{gi}} \tilde{v}_o - \frac{K_2 \overline{V}_o \overline{I}_{load}}{3 \left(\overline{V}_{gi}\right)^2} \tilde{v}_{gi} \qquad (11)$$

The transfer function of the proposed system is:

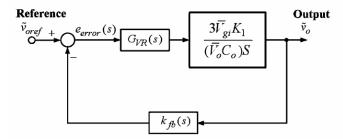

$$\frac{\tilde{v}_o}{\tilde{v}_{oref}} = \frac{3G_{VR}\bar{V}_{gi}K_1}{\bar{V}_oC_2S + 3G_{VR}\bar{V}_{oi}K_1k_{fb}}$$

(12)

Here, a PI regulator is

$$G_{VR}(s) = \frac{k_p \left(S + \omega_Z\right)}{S} \tag{13}$$

The proposed topology transfer function is:

$$PTF = \frac{3\overline{V}_{gt}K_1k_{fb}}{(\overline{V}_oC_2)S} \tag{14}$$

Open loop transfer function is:

$$OLTF = \frac{3G_{VR}(s)\overline{V}_{gi}K_1k_{fb}}{(\overline{V}_oC_2)S}$$

(15)

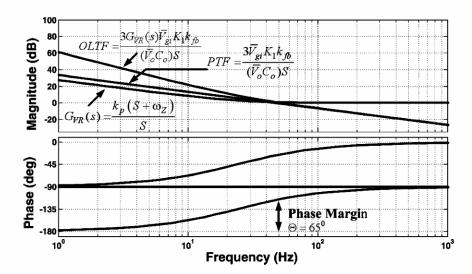

B. Performance of Three-Phase Rectifier with Minimized DC Bus Capacitance Base on Power Balance Control Technique

An average small-signal model of the modular three-phase rectifier has been shown in Eq. (12). The simulation result of the proposed system is considered. Analysis of steady-state and transient operation of the proposed system is presented. The control strategy provides a fast transient response under load disturbances condition. Such a fast response, in turn, minimizes the overshoot, droop and the settling time of the output voltage. The control strategy also provides the desired current sharing between the paralleled isolated CUK converters even during transients.

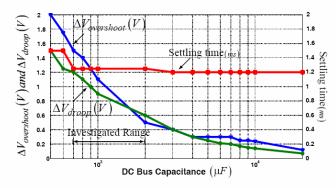

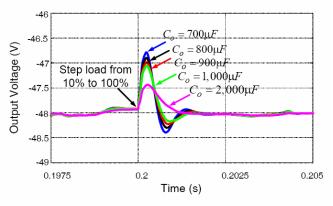

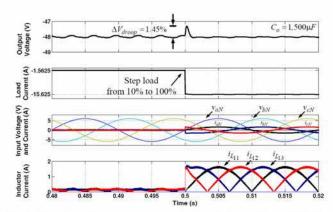

The proposed system which consists of a modular 250W CUK dc to dc converter with diode front end rectifier and a single de bus capacitor. It was simulated for different de bus capacitance values. A rated operation of 750W output power and -48V of dc output voltage with 220V of ac line-to-neutral voltage are assumed. The dc bus voltage is measured for the feedback control purposes. In addition, in order to improve dynamic response in the dc voltage control, load current and input voltage is also measured and added to the inductor current amplitude reference as load feedforward. The simulated results are discussed below. The steady state and dynamic performance of proposed topology is shown in Fig. 2 to Fig. 6. As a dynamic response example, Fig. 2 shows the simulation results of a sudden load change requiring changing over from 75W to 750W ( $\Delta P_Q = 0.675$  kW) for various output capacitance value (500 µF, 1,000 µF, 5,000 µF,  $10,000 \,\mu\,\text{F}$  and  $20,000 \,\mu\,\text{F}$ ). Figure 2 shows that the  $\Delta_{Vdroop}$  of output voltage at the common de bus capacitor is reduced when the power balance control technique is employed. By utilizing feedfoward, the low bandwidth of the voltage control loop is well compensated and the dc-link voltage is hardly disturbed. Transient response analysis for this paper is based upon  $\Delta_{Vdroop}$  ,  $\Delta_{Vovershoot}$  and settling time of output voltage for the dc bus capacitor chosen as various values. The influence of its value is shown in Fig. 3. The  $\Delta_{Vdroop}$  and  $\Delta_{Vovershoot}$  is typically unsymmetrical. The  $\Delta_{Vovershoot}$  is higher than  $\Delta_{Vdroop}$ for  $C_2 < 1,000 \mu F$ . However, for high values of dc bus capacitor with 1,500  $\mu F \le C_2 \le 20,000 \mu F$ , the  $\Delta_{Vdroop}$  and  $\Delta_{Vovershoot}$  is nearly equal and  $\Delta t$  of the settling time is 1.2 ms.

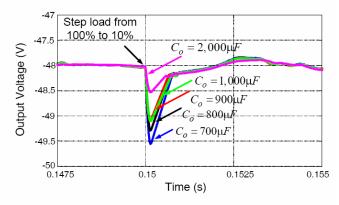

Fig 4 and Fig 5 shows the comparison of  $\pm \Delta v_O$  and settling time of dc bus voltage due to the step load change from 100% to 10% and vice versa. The output voltage waveforms represent the results corresponding to value of capacitor output at 700  $\mu$ F, 800  $\mu$ F, 900  $\mu$ F, 1,000  $\mu$ F, and 2,000  $\mu$ F respectively. The comparison between the results indicates that the small voltage dips and less variant in response trajectories are yielded by applying power balance control technique. Although the smaller value of output capacitor is chosen, the better control is obtained, the compromise between control performance and output capacitor should be considered. Thus  $C_2$ = 1,500  $\mu$ F will be adopted in the common dc bus capacitor at load terminal.

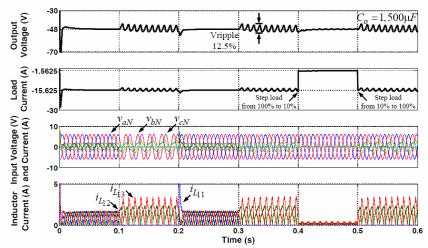

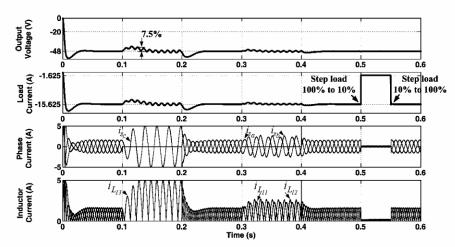

Simulation results of the proposed system with a nominal output power of  $P_o = 750$ W operating at balanced and

unbalanced three-phase mains (220V line to neutral voltage) are shown in Fig. 6. The simulation does analyze the following modules and load condition: 0...100ms: symmetric mains, 100...200ms: two-phase supply (main phase a loss), 200...300ms: return of the missing main phase, 300...400ms: one-module loss (in phase a), 400...500ms: step load change from 100% to 10% under one-module loss (in phase a) and 500...600ms: step load change from 10% to 100% under one-module loss (in phase a).

Fig. 3. The  $\Delta_{Vdroop}$  (V),  $\Delta_{Vovershoot}$  (V) and Settling time (ms) comparison of DC bus capacitor components.

Fig. 4. The transient performance indexes at different values of a common dc bus capacitor when step load change from 10% (75 W) to 100 %.(750 W).

Fig. 5. The transient performance indexes at different values of a common dc bus capacitor when step load change from 100% (750 W) to 10% (75 W).

Fig. 6. Time behavior of the dc output voltage  $v_o$ , the load current  $i_{load}$ , the line to neutral voltages  $v_{xN}(x=a,b,c)$ , the individual line current  $i_{zx}(x=a,b,c)$  and the individual inductor current  $i_{ly}(j=1,2,3)$  for symmetric mains condition, mains phase a loss, power module # in phase a fault and a load step from 100% (750 W) to 10% (75 W) and vice versa under power module in phase a fault.

At t = 100 ms, the loss of the main phase a does occur. The calculation of the rms value of the main line to neutral voltage does require a minimal calculation time of  $t_A = 10 \text{ ms}$ , resulting in a temporarily false value of the input phase current. These wrong value do cause a significant drop of the output voltage  $(v_o)$  and load current  $(i_{load})$  during the time period t = 100...110 ms. As soon as the rms value is calculated correctly the rapid fall of the output voltage is stopped due to the PI controller increased value of the reference inductor current. A detailed view on the return of the missing phase a at t = 200 ms is given in Fig. 6. The phase currents  $i_{saN}$ ,  $i_{sbN}$  and  $i_{scN}$  do increase very rapidly because of the values of the correcting signal. The behavior for a loss of module in phase a shown in Fig. 6 within the time interval t =300...600 ms. Again the delayed calculation of the peak values of the inductor current does cause a drop of the dc output capacitor voltage within the time interval t = 300...320ms. A load variation within the time interval t = 400...500ms. The simulation result of transient response of the output voltage and current waveforms at load change from 750 W to 75 W and vice versa are shown in Fig. 6 ( $C_2 = 1,500 \mu F$ ). A load dump at t=400 ms is completely handled by the power balance control technique. However, it has been found from this study that the three-phase connection of three-phase rectifier modules under loss condition of module in phase a offers drawback such as : very large output voltage ripple at the common dc bus capacitor (v<sub>ripple</sub>=12.5%), this significantly increases capacitor heating and does not improves its operating life, high  $THD_i$  and low power factor. So, redundancy is required when continuous operation of the system is required in mission critical applications.

#### III. REDUNDANT OPERATION

Redundancy (n+1): in determining the number of the modules it should be taken into account that for the reason of safety at least two rectifier modules must be installed (n≥2). It is an additional requirement that the power supply system

must meet the requirement of the telecommunications load even in the case of a module fault.

There are a number of ways to construct redundant or faulttolerant power systems. The most common method is to have at least one supply with sufficient output power to fully satisfy the system's power requirements. Then, a redundant power supply of the exact same ratings is provided as a "back-up" in the event one of the three supplies fails. This forms a basic n+1 redundant and fault-tolerant power system (3+1 system). "n" equals the number of supplies required to fully three-phase ac to dc converter and "+1" equals one backup or redundant supply that will take over for a failed supply. "n" must consist of three power supplies, each providing 33.3% of the total load power with "+1" supply having the same power rating as the others. One advantage of this type of power system (3+1) is that under normal operating conditions each of the three main power supplies are only providing 33.3% of the total system power, thus reducing the thermal stress on each supply, and improving the reliability of the distributed power system.

Fig. 7. Redundant three-phase ac to dc converter using single-phase CUK rectifier module with minimized dc bus capacitor (Number of module 3+y) based on power balance control technique.

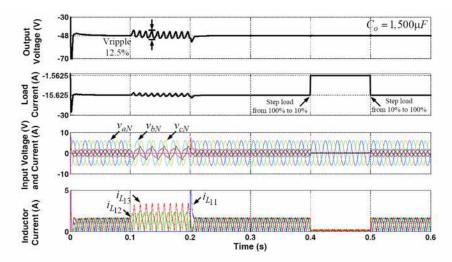

Fig. 8. Time behavior of the dc output voltage  $v_o$ , the load current  $i_{load}$ , the line to neutral voltages  $v_{xN}(x=a,b,c)$ , the individual line current  $i_{tx}(x=a,b,c)$  and the individual inductor current  $i_{ty}(j=1,2,3)$  for symmetric mains condition, mains phase a loss, power module # in phase a fault and a load step from 100% (750 W) to 10% (75 W) and vice versa under redundant power system condition.

Fig. 9. Closed up of transient responses when  $i_{load}$  is changed from -1.5625 A (75 W) to -15.625 A (750 W). [ $v_o$ : output voltage (1 V/div),  $i_L$ : inductor current (1 A/div),  $i_{zN}$ : line current (5 A/div),  $v_{zN}$ : line to neutral voltage (300 V/div) and t: time (5ms/div)] with a common de bus capacitor at 1,500  $\mu$ F based on power balance control technique.

Fig. 10. Closed up of transient responses when  $i_{load}$  is changed from -15.625 A (750 W) to -1.5625 A (75 W). [ $v_o$ : output voltage (1 V/div),  $i_L$ : inductor current (1 A/div),  $i_{zN}$ : line current (5 A/div),  $v_{zN}$ : line to neutral voltage (300 V/div) and t: time (5ms/div)] with a common dc bus capacitor at 1,500  $\mu$ F based on power balance control technique.

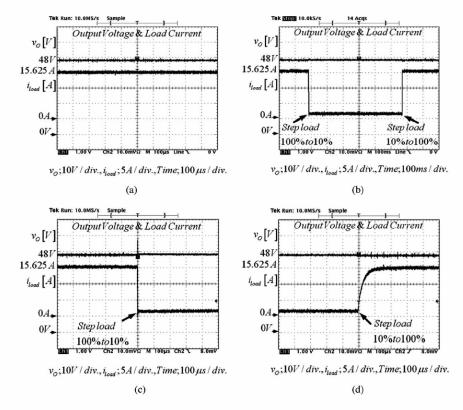

Performance characteristics of the redundant three-phase ac to dc converter using isolated single-phase CUK rectifier module with minimized dc bus capacitance based on power balance control technique are given in Figs. 8-10 illustrating the steady state and transient behavior at different loads under balance condition.

The simulation results of the proposed system in Fig. 7 with operating at balanced and unbalanced three-phase mains under redundant power system condition are shown in Fig. 8. The simulation does analyze the following modules and load conditions: 0...100ms: symmetric mains, 100...200ms: two-phase supply (main phase a loss), 200...300ms: return of the missing main phase, 300...600ms: at this time redundant power system condition has been began (one-module loss in phase a), 400...500ms: step load change from 100% to 10% and 500...600ms: step load change from 10% to 100%.

Fig. 9 shows the source voltage, 3-phase currents, individual inductor current, load current and dc bus voltage when step load change from 10% (75 W) to 100% (750 W). The source currents respond very quickly and settle to steady state value within a 1.2 ms. The individual inductor current increases almost instantaneously to feed the increased load current demand by taking the energy instantaneously from de bus capacitor. Output voltage recovers within 1.2 ms. Source currents always remain sinusoidal and power factor nearly unity. Fig. 10 shows similar results as in Fig. 9 for sudden decrease of load. The proposed topology power supplied from source is decreased form 100 % (750 W) to 10% (75 W). Source currents settle to steady state value within 1.2 ms demonstrating the excellent transient response of the DC bus voltage rises only to 48.696 V but reaches the steady state value within 1.2 ms. Source currents remain always nearly sinusoidal under all operating conditions. The proposed topology meets the requirements of harmonic components of source current and maintains the source currents sinusoidal in transient and steady state conditions. The performance of the proposed control algorithm of the proposed topology is found

to be excellent and the source current is practically sinusoidal and in phase with the source voltage. The fast response of the proposed topology ensures that the proposed topology is not overburdened during transient conditions. The voltage ripple is quite small in de bus capacitor voltage and may be reduced further by increasing the capacitor value.  $\Delta V_{overshoot}$  in dc bus voltage is observed to be  $\approx 1.45$  % during transients which may be controlled by the design to a lower value but at the expense of increased value of dc bus capacitor.

In summary, we have discussed how you can provide increased reliability by connecting one or more power supplies in parallel. We have also covered how to construct an n+1 redundant and fault-tolerant power system and the features required of the supplies in order to accomplish this with the greatest amount of reliability and ease of system maintenance.

#### IV. CONCLUSIONS

Analysis, design and simulation of the redundant three-phase ac to dc converter using single-phase isolated CUK rectifier module with nearly unity power factor and minimized dc bus capacitor are studies. It's operated based on power balance control technique. The proposed control strategy provides fast transient response and good inductor current sharing. In order to improve dynamic response in the dc voltage control, load current and input voltage is also measured and added to the inductor current loop. The condition under mains failure (loss of one main phase), module loss and heavily step load change has been presented.

In this case, DC bus capacitor  $C_2 = 1,500 \, \mu \, \mathrm{F}$  according to  $\Delta_{Vdroop}$ ,  $\Delta_{Vovershoot}$  and settling time of output voltage. The proposed method is based on the reliability and electrical performance for these rectifiers. This paper has demonstrated that, with a minimized dc bus capacitor, excellent power factor correction, module load sharing under load transients can be achieved. Reliability is also increased due to the redundant operation system.

#### ACKNOWLEDGMENT

The authors of this work deeply appreciate the support of project MRG5180328 of the Commission on Higher Education, Ministry of Education and Thailand Research Fund (TRF). and as well as the resources provided by the Rajamangala University of Technology Lanna (RMUTL), Chiang Mai, THAILAND.

#### REFERENCES

- [1] B. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, D.P. Kothari, "A review of single-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 50, Issue 5, pp. 962 981, Oct. 2003.

- [2] W. Stefanutti, P. Mattavelli, G. Spiazzi, P. Tenti, "Digital Control of Single-Phase Power Factor Preregulators Based on Current and Voltage Sensing at Switch Terminals," *IEEE Trans. Power Electron.*, vol. 21, Issue: 5, pp. 1356-1363, Sept. 2006.

- [3] Yungtaek Jang; M.M. Jovanovic, Kung-Hui Fang; Yu-Ming Chang, "High-power-factor soft-switched boost converter," *IEEE Trans. Power Electron.*, vol. 21 Issue: 1, pp. 98-104, Jan. 2006.

- [4] Min Chen and Jian Sun, "Low-Frequency Input Impedance Modeling of Boost Single-Phase PFC Converters," *IEEE Trans. Power Electron.*, vol. 22, Issue: 4, pp. 1402-1409, July 2007.

- [5] L. Huber, Irving, M.M. Jovanovic, "Open-Loop Control Methods for Interleaved DCM/CCM Boundary Boost PFC Converters," *IEEE Trans. Power Electron.*, vol. 23, Issue 4, Page(s): 1649-1657, July 2008.

- [6] Jingquan Chen, D. Maksimovic, R.W. Erickson, "Analysis and design of a low-stress buck-boost converter in universal-input PFC applications," *IEEE Trans. Power Electron.*, vol. 21, Issue: 2, pp. 320- 329, March 2006.

- [7] R. Zane, D. Maksimovic, "Nonlinear-carrier control for high-power-factor rectifiers based on up-down switching converters," *IEEE Trans. Power Electron.*, vol. 13, Issue 2, pp. 213 221, March 1998.

- [8] Ching-Jung Tseng and Chern-Lin Chen; "A novel ZVT PWM Cuk power-factor corrector," *IEEE Ind. Electron.*, vol. 46, Issue 4, pp. 780 787, Aug. 1999.

- [9] S. Buso, G. Spiazzi, D. Tagliavia, "Simplified control technique for high-power-factor flyback Cuk and Sepic rectifiers operating in CCM," *IEEE Trans. Ind. Appl.*, vol. 36, Issue 5, Page(s):1413 1418, Sept.-Oct. 2000.

- [10] M. Brkovic and S. Cuk, "Input current shaper using Cuk converter," in *Proc. IEEE INTELEC Conf.*, 1992, pp. 532-539.

- [11] G. Ranganathan and L. Umanand, "Power factor improvement using DCM Cuk converter with coupled inductor," in *Proc. IEE Electric Power Applications Conf.*, 1999, pp. 231-236.

- [12] D.S.L. Simonetti, J. Sebastian, F.S. dos Reis, and J. Uceda, "Design criteria for SEPIC and Cuk converters as power factor preregulators in discontinuous conduction mode," *IEEE PEMC Conf.*, pp. 283-288, 1992,

- [13] A. Newton, T.C. Green, and D. Andrew, "AC/DC Power Factor Correction Using Interleaved Boost & CUK Converters," *IEE PEVSD Conf.*, pp. 293-298, 2000.

- [14] S. Kim and P.N. Enjeti, "Control of multiple single-phase PFC modules with a single low-cost DSP," *IEEE Trans. Ind. Appl.*, vol. 39, pp. 1379-1385, Sept.-Oct 2003.

- [15] Sangsun Kim and P.N. Enjeti, "A parallel-connected single phase power factor correction approach with improved efficiency," *IEEE Trans. Power Electron.*, vol. 19, Issue 1, pp. 87 93, Jan. 2004.

- [16] B. Singh, S. Gairola, B.N. Singh, A. Chandra, K. Al-Haddad, "Multipulse AC–DC Converters for Improving Power Quality: A Review," *IEEE Trans. Power Electron.*, vol. 23 Issue: 1, pp. 260-281, Jan. 2008.

- [17] B. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, D.P. Kothari, "A review of three-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol.51, Issue 3, pp. 641 660, June 2004

- [18] G. Spiazzi and F.C. Lee, "Implementation of Single-Phase Boost Power-Factor-Correction Circuits in Three-Phase Applications," *IEEE Trans. Ind. Electron.* vol. 44, no. 3, pp. 365-371, June 1997.

- [19] H.M. Suryawanshi, M.R. Ramteke, K.L. Thakre, V.B. Borghate, "Unity-Power-Factor Operation of Three-Phase AC–DC Soft Switched Converter Based On Boost Active Clamp Topology in Modular Approach," *IEEE Trans. Ind. Electron.* vol. 23 Issue: 1, pp. 229-236, Jan. 2008.

- [20] X.H. Wu, S.K. Panda, J.X. Xu, "Analysis of the Instantaneous Power Flow for Three-Phase PWM Boost Rectifier Under Unbalanced Supply Voltage Conditions," *IEEE Trans.Power Electron.* vol. 23 Issue: 4, pp. 1679-1691, July 2008.

- [21] P. Xiao, K.A. Corzine, G.K. Venayagamoorthy, "Multiple Reference Frame-Based Control of Three-Phase PWM Boost Rectifiers under Unbalanced and Distorted Input Conditions," *IEEE Trans. Power Electron.*, vol. 23, Issue: 4, pp. 2006-2017, July 2008.

- [22] T. Nussbaumer, J.W. Kolar, "Improving mains current quality for three-phase three-switch buck-type PWM rectifiers," *IEEE Trans. Power Electron.*, vol. 21, Issue 4, Page(s): 967- 973, July 2006.

- [23] T. Nussbaumer, M. Baumann, J.W. Kolar, "Comprehensive Design of a Three-Phase Three-Switch Buck-Type PWM Rectifier," *IEEE Trans. Power Electron.*, vol. 22, Issue: 2, pp. 551-562, March 2007.

- [24] Lung-Sheng Yang; Tsorng-Juu Liang; Jiann-Fuh Chen, "Analysis and Design of a Novel Three-Phase AC–DC Buck-Boost Converter," *IEEE Trans. Power Electron.*, vol. 23, Issue 2, pp. 707-714 March 2008.

- [25] Y.K. Eric Ho, S.Y.R. Hui, and Yim-Shu Lee, "Characterization of Single-Stage Three-Phase Power-Factor-Correction Circuit Using Modular Single-Phase PWM DC-to-DC Converters," *IEEE Trans. Power Electron.*, vol.15, pp. 62-71, January 2000.

IEEE 13th European Conference on Power Electronics and Applications, 2009. EPE '09. 2009 , Page(s): 1-10

#### Analysis, Design and Implementation of a Three-Phase AC to DC Converter Using Single-Phase Isolated CUK Rectifier Modules with Small DC Bus Capacitor

Uthen KAMNARN and Surasak YOUSAWAT RAJAMANGALA UNIVERSITY OF TECHNOLOGY LANNA

128 Huay Keew Road, Muang Distric Chiang Mai, Thailand, 50300 Tel.: +66 / (0) – 53 892 780 Ext. 2120

Fax: +66 / (0) - 53 892 / 80 Ext. 2120 Fax: +66 / (0) - 53 213 183.

E-Mail: uthen@rmutl.ac.th and surasak@rmutl.ac.th

Yutthana KANTHAPHAYAO and Viboon CHUNKAG KING MONGKUT'S UNIVERSITY OF TECHNOLOGY NORTH BANGKOK

> 1518 Pracharaj sai 1 Road (Pibulsongkram Road), Bangsue Bangkok, Thailand, 10800

> > Tel.: +66 / (0) – 25 853 581 Ext. 2401, 8416

Fax: +66/(0) - 25874357.

E-Mail: yutthana k44@yahoo.com and vek@kmutnb.ac.th

#### Acknowledgements

The authors wish to acknowledge the financial support received from the Commission on Higher Education, Ministry of Education and Thailand Research Fund (TRF), THAILAND under Contract MRG5180328 as well as Rajamangala University of Technology Lanna (RMUTL) and King Mongkut's University of Technology North Bangkok (KMUTNB), THAILAND.

#### **Keywords**

«DC power supply», «Harmonics», «Power factor correction», «Power supply», «Switched-mode power supply».

#### **Abstract**

The paper presents an implementation and control of a high power-factor and fast dynamic transient response of the modular three-phase ac to dc converter using three CUK rectifier modules with a small de bus capacitor. The methodology aims at finding the small de bus capacitor which meets the desired system performance, with power balance control technique. Modeling a modular three-phase rectifier system is considered as the first step in the optimal sizing procedure. In this paper, mathematical average small-signal model for characterizing modular three-phase rectifier is proposed. Design of an analog controller for a small dc bus capacitor based modular three-phase rectifier is presented. The controller senses the parameters of the proposed system, and makes decisions about reject load and input voltage disturbances. The second step consists in minimize the sizing of the dc bus capacitor according to the transient response of dc bus output voltage and the delivered energy of capacitor concepts. Considering various types and capacities of dc bus capacitor, which can meet the desired system performance, are obtained by changing the type and size of the dc bus capacitors. The proposed system with the dc bus capacitor 470 µF gives the optimal choice. A 750W laboratory prototype with 470 µF is implemented and tested to verify the feasibility of the proposed system. The experimental results show that the proposed system, meet the desired system performance. Therefore the system choice plays an important role in cost reduction.

#### Introduction

Among various PFC converters, a modular three-phase ac to dc converter composed of three modified single-phase single-switch modules with a single dc bus capacitor has been proposed for medium and high-power applications in distributed power system (DPS) [1]-[3]. A single dc bus capacitor,  $C_O$  is connected at the output terminal for filtering the output voltage ripples. It can be used as dc bus for distributing power to load converter. Compared to the conventional six-switch topology [4]-[5], this type of three-phase PFC converter features a simple and robust configuration.

Capacitors are available today may be made in five basic technologies and used across a broad spectrum of application. The currently commercially available technologies are listed below: 1) ceramic; 2) aluminum electrolytic; 3) tantalum electrolytic; 4) film (polymeric); 5) film (mica and paper). Electrolytic capacitor technology, providing moderate energy and power density, but has relatively high losses and is polarity dependent, and therefore primarily used in dc circuits. Typical applications are moderate to large capacitors at up to 600 V, mainly for dc applications involving filtering and rectified circuits. When a capacitor is selected to perform properly in an electronic circuit, its characteristics are optimized to provide the designer with a well-defined level of reliability for the component throughout the design lifetime of the circuit. The selection of a capacitor design requires the matching of available capacitor characteristics and parameters to the application needs. In addition to the basic capacitance value and voltage rating, specifying all the characteristics allows the supplier to provide the most cost-effective capacitor for a given application.

In general, dc bus capacitors are installed in switching power supply systems for voltage regulation, power factor correction, and reactive power control. This process involves determining capacitor size, type, location, voltage constraints, load variation and control method. The main effort usually is to determine capacitor size for voltage regulation. The dc bus in any distributed power system is normally equipped with an electrolytic capacitor, which provides decoupling between the rectifier and the load converter. However, the dc bus capacitor is a large, heavy, and expensive component. Moreover, the dc bus capacitor is the prime factor of degradation of system reliability. This problem is well recognized by the industry. Manufacturers of low cost and high volume systems are looking for ways to reduce the size and cost of this electrolytic capacitor.

This paper presents a three-phase ac to dc converter using single-phase isolated CUK rectifier module with nearly unity-power factor and reduce dc bus capacitor. This research project has attempted the development of a power balance control technique that will allow the use of a smaller dc-link capacitor without affecting the output performance of the converter.

The proposed method implemented in three-phase ac to dc converter applications will result in the following advantages:

- High power factor, modularity, fast dynamic transient response, small capacitor size, reduced converter weight and volume.

- Significant improvement in system reliability by the use of a smaller link capacitor.

- Power balance control technique to simplify the design procedure of the dc bus voltage regulator, to provide fast transient response, high performance, and increased reliability.

- An analog controller insensitive to environment, simple control strategy, offering stable operation under most operating conditions. It is easy to understand and to implement.

#### **Proposed system**

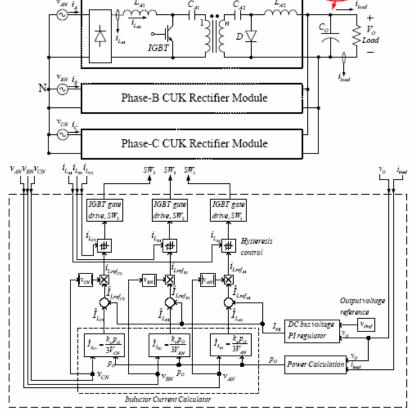

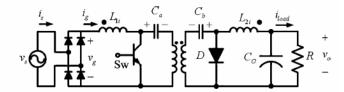

Fig. 1 shows a modular three-phase ac to dc converter using single-phase single-switch isolated CUK rectifier modules. The power circuit is formed by an input-side Y-connected of three power modules with parallel connected at dc bus voltage. The capacitor  $C_O$  is shared by three power modules. The control strategy consists of single output voltage loop control and three inductor current calculators.

Phase-A CUK Rectifier Module

Fig. 1: Three-phase ac to dc converter using three single-phase isolated CUK rectifier modules with small dc bus capacitor.

#### Selecting the value of the dc bus capacitor

Traditional PFC converter, the relationship between the energy of bulk capacitors and the hold-up time, this given as:

$$C_{O,\min} = \frac{2P_{O}T_{hld}}{V_{O}^{2} - V_{O,\min}^{2}}$$

(1)

Where,  $P_O$  is the power of the dc-dc converter;  $V_O$  is normal operation voltage of the bulk capacitors;  $V_{O,min}$  is the minimum operation input voltage for the dc-dc converter at the latter stage. Typically, with a proper design, ripple voltage and current in the capacitor will not be an issue. By choosing  $T_{hld}$  = 2 ms,  $\Delta v_o = \pm 5\%$ , one can find  $C_{O,min} = 10,683 \, \mu F$ . In order to guarantee minimum capacitance requirement is satisfied, thus assuring minimum hold up time.

$$C_O = \frac{C_{O,\text{min}}}{1 - \Delta C_{tol}} = 13,353 \ \mu\text{F}$$

(2)

Pick  $C_0 = 13{,}600 \mu F$ . Table I shows the design results of a 750 W, -48 V, a three-phase ac to dc converter using isolated CUK rectifier modules.

#### Average small signal model

The analytical model derivation is based on the power stage schematic shown in Fig. 1 where the ideal switches and zero equivalent series resistance in the capacitors are assumed.

$$\sum_{i=A}^{C} V_{gi} I_{L_{li}} = V_O I_O \tag{3}$$

When, i = A, B and C,  $V_{gi}$  is rectifier voltage,  $I_{L_{li}}$  is inductor current,  $V_O$  is de output voltage,  $I_o$  is average output current over a half-line cycle. The peak value of the inductor current is

$$\hat{I}_{L_{1i}} = \frac{K_2 V_O I_{load}}{3V_{\sigma i}} \tag{4}$$

$$\hat{I}_{Lrefi_i} = \hat{I}_{L_{ii}} + I_{VR} \tag{5}$$

$\hat{I}_{L_{refli}}$  is peak value of the inductor reference current,  $\hat{I}_{L_{li}}$  is peak value of the inductor current,  $I_{VR}$  is correcting signal of PI controller,  $K_2$  is conversion gain of inductor current. The dynamic equation of the output voltage is

$$\sum_{i=A}^{C} I_{Oi} = C_O \frac{dV_O}{dt} + I_{load}$$

(6)

$I_{load}$  is the load current. Applying the perturbations in (1), (2), (3), and (6), and performing the small-signal approximation ( $\tilde{v}$ . $\tilde{v}$ =0). Therefore, the output voltage can be expressed as

$$\tilde{v}_o = T_C \tilde{v}_{Oref} + T_A \tilde{v}_{g_i} - Z_O \tilde{i}_{load}$$

(7)

When, applying Mason gain formula.

$$\frac{\tilde{v}_{O}}{\tilde{v}_{Oref}} = \frac{G_{2}Z_{L}G_{VR}}{1 + k_{fb}G_{2}Z_{L}G_{VR} + G_{3}Z_{L} - G_{2}Z_{L}F_{2}}$$

(8)

Therefore, the gain  $K_2$  can be expressed as:

$$K_2 = K_1^{-1} = \sqrt{2}$$

(9)

The transfer function of Fig.1 can be obtained from the average small-signal model proposed:

$$\frac{\tilde{v}_O}{\tilde{v}_{Oref}} = \frac{3G_{VR}\overline{V}_{gi}K_1}{\overline{V}_OC_2S + 3G_{VR}\overline{V}_{gi}K_1k_{fb}}$$

(10)

$K_I$  is RMS gain,  $k_{fb}$  is feedback gain. Here, a PI controller is chosen for voltage regulation

$$G_{VR}(s) = \frac{k_p \left(S + \omega_Z\right)}{S} \tag{11}$$

$G_{VR}(s)$  is PI controller,  $k_p$  is the gain of controller,  $\omega_Z$  is the location of the zero.

#### Experimental verification

#### Performance evaluation of the modular three-phase rectifier system

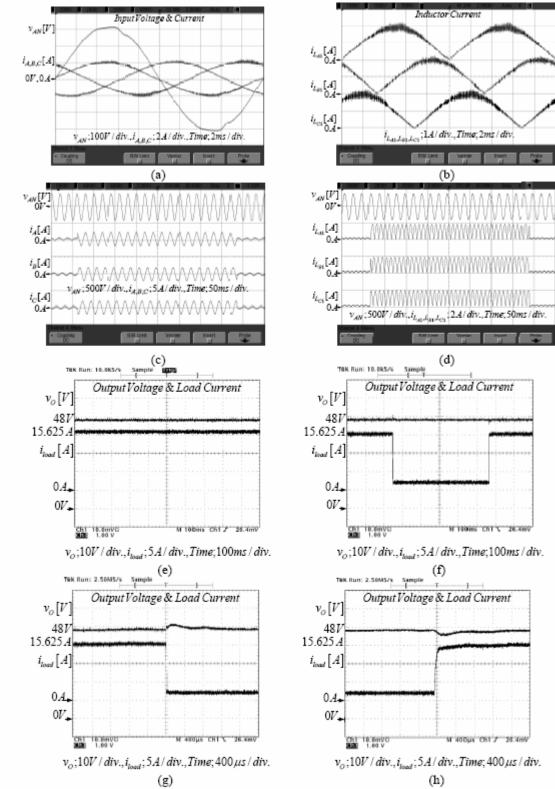

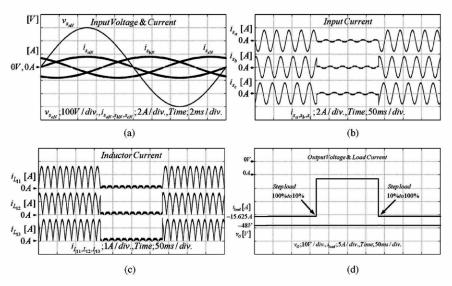

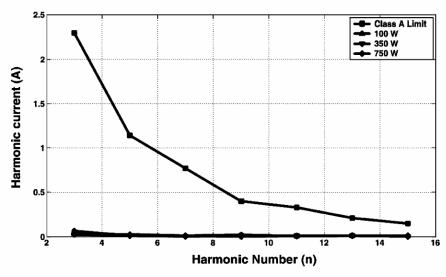

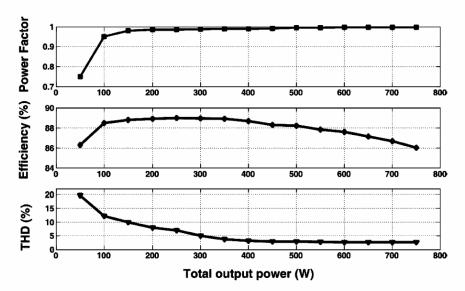

A 750 W laboratory prototype was implemented and tested to verify the feasibility of the proposed control strategy. The specifications of the laboratory prototype are listed in table I. Steady state input currents of the proposed system with three different values of dc bus capacitor ( $C_0 = 150 \, \mu\text{F}$ , 1,000  $\mu\text{F}$  and 13,600  $\mu\text{F}$ ) are shown in Fig. 2. They are nearly sinusoidal. The measured power-factors are 0.99 and total harmonic distortions (THD) are lower than 3%, respectively. They have been illustrated that the proposed system can achieved a high power-factor and low THD<sub>i</sub>.

Fig. 2: Steady state condition of the modular three-phase rectifier with  $C_O = 150 \, \mu\text{F}$ , 1,000  $\mu\text{F}$  and 13,600  $\mu\text{F}$ .

Table I: Design results for the laboratory prototype

| Characteristic/Symbol                                               | Value                                                                                     |  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Input Chokes / $L_{Al}$ , $L_{Bl}$ , $L_{Cl}$                       | Chokes / L <sub>AL</sub> , L <sub>BL</sub> , L <sub>Cl</sub> 5.069 mH, 5.068 mH, 5.066 mH |  |

| Output Chokes / $L_{A2}$ , $L_{B2}$ , $L_{C2}$                      | 1.066 mH, 1.086 mH, 1.044 mH                                                              |  |

| Output Capacitor / Co                                               | 156 μF (min), 13,600 μF (max)                                                             |  |

| Input voltage / v <sub>AN</sub> , v <sub>BN</sub> , v <sub>CN</sub> | ge / $v_{AN}$ , $v_{BN}$ , $v_{CN}$ 220 V                                                 |  |

| Line frequency                                                      | frequency 50 Hz                                                                           |  |

| Switching frequency                                                 | ning frequency ≈ 20-30 kHz                                                                |  |

| Rated module                                                        | tated module 250 W/ module                                                                |  |

| Total output power                                                  | 750 W                                                                                     |  |

| Output voltage                                                      | -48 V                                                                                     |  |

| n                                                                   | 0.5                                                                                       |  |

| Storage capacitor/ $C_A$ , $C_B$ , $C_C$                            | 0.68 μF                                                                                   |  |

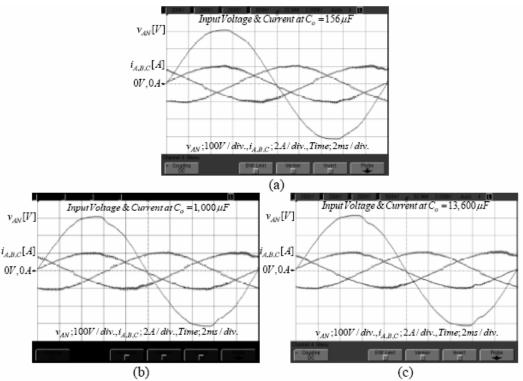

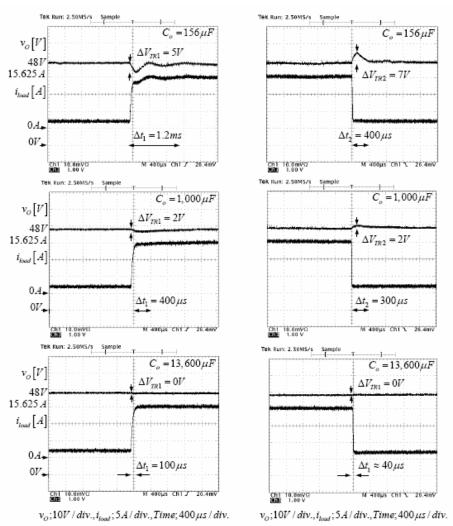

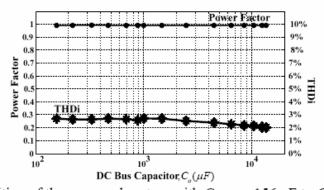

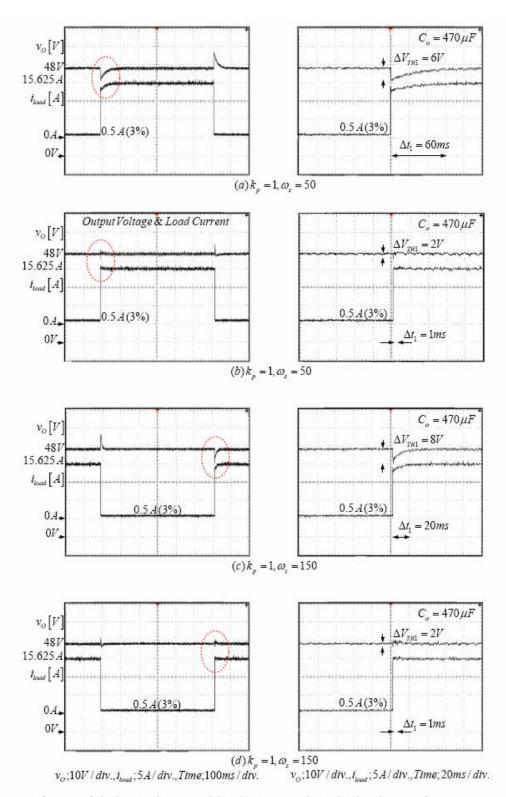

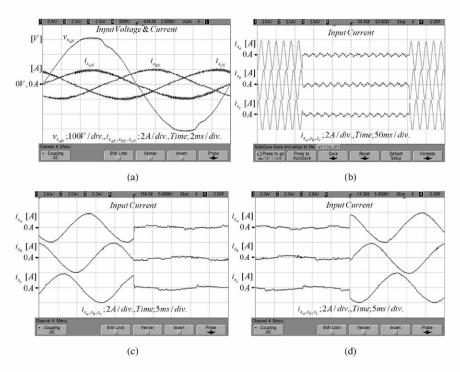

The experimental results of the proposed system operating at step load change from 75 W to 750 W and vice versa under three different output capacitors (156  $\mu$ F, 1,000  $\mu$ F and 13,600  $\mu$ F) are shown in Fig. 3. The comparison between the results indicates that the small voltage dips and less variant in response trajectories are yielded by applying power balance control technique. The main performance features of the proposed system for input power-factor (PF) and input current total harmonic distortion (THD<sub>i</sub>) are plotted in Fig. 4 as a function of the different dc capacitor size ( $C_{O,min}$  = 150  $\mu$ F to  $C_{O,max}$  = 13,600  $\mu$ F) at rated input and output voltage and output power (220V, -48 V and 750 W). They are measured with the Digital power meter YOKOGAWA model 2531A.

#### The following can be concluded:

- Power-factor is nearly unity, greater than 0.99 for all difference values of output capacitor,

- Input current THD<sub>i</sub> remains low, lower than 3% (750 W), for fifteen values of output capacitor.

Fig. 3: Transient condition of the modular three-phase ac to dc converter: dc bus voltage and load current at step load change from 10% (75 W) to 100% (750 W) and vice versa (parameter of PI controller  $k_p = 1$  and  $\omega_z = 150$  with power balance control technique).

Fig. 4: Steady state condition of the proposed system with  $C_{O,min} = 156 \,\mu\text{F}$  to  $C_{O,max} = 13,600 \,\mu\text{F}$ .

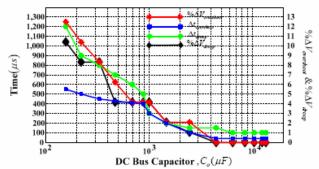

The influence of its value on  $\Delta V_{droop}$ ,  $\Delta V_{overshoot}$ ,  $\Delta t_{droop}$ , and  $\Delta t_{overshoot}$  is shown in Fig. 5. As expected the  $\Delta t_{droop}$  decreases as the capacitance increases, down to 100 $\mu$ s for  $C_O \geq 4,000~\mu$ F, and the  $\Delta V_{droop}$ ,  $\Delta V_{overshoot}$  decreases as well. The voltage  $\Delta V_{overshoot}$  is higher than  $\Delta V_{droop}$  for  $C_O \leq 700~\mu$ F. At low values of dc bus capacitor with  $C_O \leq 1,000~\mu$ F, sum of  $\Delta V_{droop}$  and  $\Delta V_{overshoot}$  is larger than 5%. However, for high values of dc bus capacitor with 4,000  $\mu$ F  $\leq C_O \leq 13,600~\mu$ F, the  $\Delta V_{droop}$  and  $\Delta V_{overshoot}$  are nearly zero and  $\Delta t_{droop}$  is nearly zero as well. If we define optimal range of dc bus capacitor is  $C_{O,optR}$ . The  $\%\Delta V_{droop} \leq \%\Delta V_{transpec}$  (5%) is the system recovers faster. For the optimal range of dc bus capacitor with 470  $\mu$ F  $\leq C_O \leq 1,000~\mu$ F, the  $\%\Delta V_{droop}$  is lower than 5% and  $\Delta t$  of the settling time is very small ( $\approx 400~\mu$ s).

Fig. 5: Performance as a function of step load change from 75 W (10%) to 750 W (10%) and vice versa ( $v_s = 220 \text{ V}$  and  $v_o = -48 \text{ V}$ ).

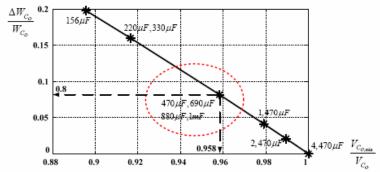

Fig. 6: Normalized delivered energy from the energy storage capacitor during hold-up time  $\Delta W_{CO}$  / $W_{CO}$  as a function of normalized minimum energy-storage capacitor voltage  $V_{CO,min}$  / $V_{CO}$  for different  $C_{O}$ .

In this paper, requirements are 400  $\mu$ s or 500  $\mu$ s at nominal input voltage. The less restrictive option can be usually complied with a 0.62  $\mu$ F/W capacitor (i.e., a 750 W application wound need a 470  $\mu$ F). The most restrictive option can be complied with 1.3  $\mu$ F/W. When,  $\Delta W_{Co}$  is the amount of delivered energy to the output during hold-up time and  $W_{Co}$  is the total stored energy in  $C_O$  at  $V_{Co}$ . As seen from Fig. 6, only 8% of the stored energy is delivered to the load during the hold-up time if  $V_{Co,min}$  is selected to be 0.958  $V_{Co}$  ( $C_{O,opt}$  = 470  $\mu$ F).

#### Steady-state and dynamic response of the proposed system with small dc bus capacitor

The dynamic responses of the modular three-phase rectifier corresponding to conventional control and proposed control are shown in Fig. 7. It shows the experimental result of the output voltage to a load step between 24 W and 750 W with and without power balance control technique, for two different PI controller conditions ( $k_p = 1$  and  $\omega_z = 50$ ,  $k_p = 1$  and  $\omega_z = 150$ ). The waveforms shown in Fig. 7(a) and Fig. 7(b) pertain to a step change in load between 24 W and 750 W under rated input voltage condition with  $k_p = 1$  and  $\omega_z = 50$ . The upper trace of Fig. 7 (a) is the dc bus voltage and the lower one in Fig. 7 (a) is the load current during the transient. It can be seen that the output voltage waveform has a large dip and a longer settle time, indicating a poor dynamic performance. Fig. 7 (b) shows that, during the transient, the output voltage waveform (upper trace) recovery quickly without voltage dip, indicate very good dynamic performance. This demonstrates that the load disturbance is effectively removed from the voltage-feedback loop. The settling time of the transients without power balance control is 60 ms and the one with power balance control is about 1 ms. Fig. 7 (c) and Fig. 7 (d) correspond to a step change in load between 750 W and 24 W. Fig. 7 (c) is the waveform of dc bus voltage and load current. It can be seen that the dc bus voltage response is improved due to the increased  $k_p$  and  $\omega_z$ . The dc bus voltage waveform in Fig. 7 (d) is greatly improved. It recovers very quickly without voltage dip at all. The settling time of the transients without power balance control is 20 ms and the one with power balance control is about 1 ms. The response is upper 20 times faster with the proposed power balance control than without power balance control in both cases ( $k_p = 1$  and  $\omega_z = 50$ ,  $k_p = 1$  and

$\omega_z = 150$ ).

Fig. 7: Waveforms of dc bus voltage and load current when the load steps from 3% to 100% and vice versa: (a) and (c) without power balance control technique; (b) and (d) with power balance control technique.

It is quite obvious that a system having a fast voltage loop exhibits better dynamic responses over the one having a slow voltage loop. It is experimentally shown that the rectifier system with the conventional controller also exhibits similar dynamic performances as those shown in Fig. 7(b) and Fig 7(d), when its voltage-loop bandwidth is design with  $k_p = 1$ ,  $\omega_z = 50$  and  $k_p = 1$ ,  $\omega_z = 150$  based on power balance control technique.

Fig. 8: Experimental steady state and transient response of the modular three-phase rectifier with small dc bus capacitor ( $C_0 = 470 \ \mu\text{F}$ ): source voltage and line current, inductor current, dc bus voltage and load current.

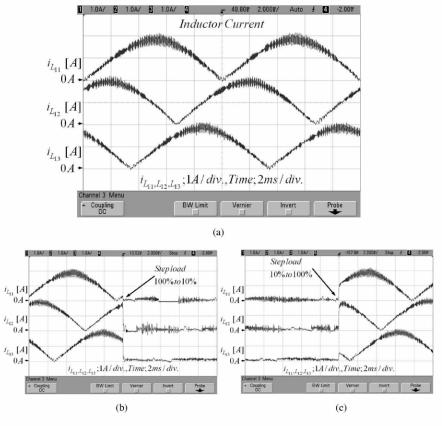

Steady state and transient response of the proposed system are shown in Fig. 8 (a)–(h), respectively. The parameters PI controllers are:  $k_p = 1$  and  $\omega_z = 150$ . The steady-state input characteristics of the rectifier for output power of 750 W are shown in Fig. 8 (a). Line current is in phase with their relative voltages. It has been illustrated that the proposed system can achieved a high power factor. Since  $i_A$  is

proportional to  $v_{AN}$  under this control method, the distortion shown in  $i_A$  is due to the corresponding distortion in  $v_{AN}$ . Fig. 8 (b) shows the steady state of three-individual inductor current waveforms at full load. It can be noted that the inductor currents are almost balanced. The transient response of the three-input line currents and three-individual inductor currents at load step change from 75 to 750W and vice versa are shown in Fig. 8 (c) and Fig. 8 (d). For the given range of output power, the power factor is close to unity and the THD<sub>i</sub> is low. Due to the effects of difference inductance values and parasitic in input inductors, these three-individual inductor currents are not exactly equal. However, all inductor current has approximately same amplitude. Fig. 8 (e) shows the output voltage at -48 V and load current at -15.625A when output capacitor is 470  $\mu$ F. Fig. 8 (f) shows the dynamic response of the output voltage and load current of the proposed system due to step load changes at the load current from 750 to 75 W and vice versa. The settling time of the output transient without power balance control technique is 30 ms, while the one with power balance control technique is 400  $\mu$ s. The experimental results in Fig. 8 (g) and (h) indicate that such scheme is effective and fast transient response characteristic.

Therefore, according to the results obtained we have a modular three-phase rectifier with the following features:

- It has only one small de bus capacitor.

- It can achieve a fast dynamic transient response and high power factor.

- · It is easy to understand and to implement.

- It is simple and robust.

- · It is naturally isolation.

- It operates either as step-up or step-down voltage.

- It can allow a regulated output voltage with only one power processing stage.

#### Conclusion

The modular three-phase rectifier with a small dc bus capacitor, using an average small-signal model, has been developed in this work. The system configuration can be obtained in terms of a system power supply performance requirement by using the power balance control concept. A simple method is presented to improve the dynamic response of the proposed system against load disturbance while maintaining low input current distortion. Design equations are presented to model the power circuit and to select the controller parameters. The paper has presented that, with reduce dc bus capacitor, high power factor, good inductor current sharing and fast dynamic transient response can be achieved for a three-phase ac to dc converter using isolated CUK rectifier modules. In this case, dc bus capacitor  $C_O = 470 \,\mu\text{F}$  according to  $\Delta V_{droop}$ ,  $\Delta V_{overshoot}$ , and delivered energy. Bus voltage is regulated by the designed PI controller with power balance control technique. Control circuit is simple and implemented by analog circuit. The experimental results prove that proposed system is meet harmonic distortion standards (IEC 61000-3-2 Class A limits).

#### References

- [1] B. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, D.P. Kothari, "A review of single-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol. 50, Issue 5, pp. 962 981, Oct. 2003.

- [2] B. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, D.P. Kothari, "A review of three-phase improved power quality AC-DC converters," *IEEE Trans. Ind. Electron.*, vol.51, Issue 3, pp. 641 660, June 2004.

- [3] H.M. Suryawanshi, M.R. Ramteke, K.L. Thakre, V.B. Borghate, "Unity-Power-Factor Operation of Three-Phase AC-DC Soft Switched Converter Based On Boost Active Clamp Topology in Modular Approach," *IEEE Trans. Ind. Electron.* vol. 23 Issue: 1, pp. 229-236, Jan. 2008.

- [4] P. Xiao, K.A. Corzine, G.K. Venayagamoorthy, "Multiple Reference Frame-Based Control of Three-Phase PWM Boost Rectifiers under Unbalanced and Distorted Input Conditions," *IEEE Trans. Power Electron.*, vol. 23, Issue: 4, pp. 2006-2017, July 2008.

- [5] X.H. Wu, S.K. Panda, J.X. Xu, "Analysis of the Instantaneous Power Flow for Three-Phase PWM Boost Rectifier Under Unbalanced Supply Voltage Conditions," *IEEE Trans. Power Electron.* vol. 23 Issue: 4, pp. 1679-1691, July 2008.

IEEE Transactions on Power Electronics, Volume: 24 , Issue: 8, 2009 , Page(s): 2000–2012

#### IEEE TRANSACTIONS ON

## POWER ELECTRONICS

A PUBLICATION OF THE IEEE POWER ELECTRONICS SOCIETY

This Print Collection Contains the Following Issues:

JULY 2009 VOLUME 24 NUMBER 7 ITPEE8 (ISSN 0885-8993)

AUGUST 2009 VOLUME 24 NUMBER 8

For the July 2009 issue, see p. 1669 for the Table of Contents. For the August 2009 issue, see p. 1857 for the Table of Contents.

#### IEEE TRANSACTIONS ON

## POWER ELECTRONICS

A PUBLICATION OF THE IEEE POWER ELECTRONICS SOCIETY

**VOLUME 24**

**AUGUST 2009**

| High Power Converters                                                                                              |      |

|--------------------------------------------------------------------------------------------------------------------|------|

| Pulsewidth Modulations for the Comprehensive Capacitor Voltage Balance of n-Level Two-Leg Diode-Clamped Converters | 1951 |

| Power Quality & Utility Applications                                                                               |      |

| Current Harmonics Cancellation in Three-Phase Four-Wire Systems by Using a Four-Branch Star Filtering Topology     | 1939 |

| Renewable Energy                                                                                                   |      |

| A Review of the State of the Art of Power Electronics for Wind Turbines Z. Chen, J. M. Guerrero, and F. Blaabjerg  | 1859 |

| Low Power Converters                                                                                               |      |

| PWM Resonant Single-Switch Isolated Converter                                                                      | 1876 |

| Large-Sized Plasma Display Panel                                                                                   | 1887 |

|                                                                                                                    | 1977 |

| Control in Power Electronics                                                                                       |      |

| A Novel Robust Control Method for the Series–Parallel Resonant Converter                                           | 1896 |

| L. Huber, B. T. Irving, and M. M. Jovanović                                                                        | 1992 |

| Analysis and Design of a Modular Three-Phase AC-to-DC Converter Using CUK Rectifier Module With Nearly Unity       | 1//2 |

| Power Factor and Fast Dynamic Response                                                                             | 2000 |

| Improved Online Identification of a DC–DC Converter and Its Control Loop Gain Using Cross-Correlation Methods      | 2021 |

**NUMBER 8**

ITPEE8

(Contents Continued on Page 1858)

(ISSN 0885-8993)

# Analysis and Design of a Modular Three-Phase AC-to-DC Converter Using CUK Rectifier Module With Nearly Unity Power Factor and Fast Dynamic Response

Uthen Kamnarn and Viboon Chunkag

Abstract-In this paper, the analysis and design of a modular three-phase ac-to-dc converter using single-phase isolated CUK rectifier modules is discussed based on power balance control technique. This paper analyzes the operation of a modular converter as continuous-conduction-mode power factor correction (CCM-PFC). Design equations, as well as an average small-signal model of the proposed system to aid the control loop design are derived. It is used to obtain the inductor current compensator, thus the output impedance and audio susceptibility become zero, and therefore, the output voltage of the converter presented in this paper is independent of the variations of the dc load current and the utility voltage. The control strategy consists of a single output voltage loop and three-inductor current calculator. The main objective of the proposed system is to reduce the number of stages and improve dynamic response of dc bus voltage for distributed power system. The proposed scheme offers simple control strategy, flexibility in three-phase delta or star-connected, simpler design, fast transient response, good inductor current sharing, and power factor closed to unity. Both simulation and experimental results are presented. They are in agreement with the theoretical analysis and experimental work.

Index Terms—Current sharing control, fast response, modular rectifier, power factor correction (PFC), three-phase converter.

|            | Nomenclature                                                        |

|------------|---------------------------------------------------------------------|

|            | NOMENCLATURE                                                        |

| $C_a, C_b$ | Intermediate capacitor.                                             |

| $C_o$      | Output capacitor.                                                   |

| d          | Duty-cycle.                                                         |

| D          | Diode.                                                              |

| $F_1$      | Open-loop load current to input inductor current transfer function. |

|            |                                                                     |

Manuscript received August 18, 2008; revised November 22, 2008. Current version published August 12, 2009. This work was supported by the Commission on Higher Education, Ministry of Education and Thailand Research Fund (TRF), Thailand, under Contract MRG5180328 and by Rajamangala University of Technology Lanna (RMUTL) and King Mongkut's University of Technology North Bangkok (KMUTNB), Thailand. This paper was presented in part at the 39th Power Electronics Specialists Conference, Island of Rhodes, Greece, on June 15–19, 2008. Recommended for publication by Associate Editor P.-T. Cheng.

U. Kamnarn is with the Faculty of Engineering, Department of Electrical Engineering, Rajamangala University of Technology Lanna, Chiang Mai 50300, Thailand (e-mail: uthen@rmutl.ac.th).

V. Chunkag is with the Faculty of Engineering, Department of Electrical Engineering, King Mongkut's University of Technology North Bangkok, Bangkok 10800, Thailand (e-mail: vck@kmutnb.ac.th).

Digital Object Identifier 10.1109/TPEL.2009.2019575

| $F_2$                                                                                                                                  | Open-loop output voltage to input inductor<br>current transfer function. |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| $F_3$                                                                                                                                  | Open-loop phase voltage to input inductor                                |

| 1.3                                                                                                                                    | current transfer function.                                               |

| $G_1$                                                                                                                                  | Open-loop phase voltage to output current                                |

| -                                                                                                                                      | transfer function.                                                       |

| $G_2$                                                                                                                                  | Open-loop inductor current to output                                     |

|                                                                                                                                        | current transfer function.                                               |

| $G_3$                                                                                                                                  | Open-loop output voltage to output current                               |

|                                                                                                                                        | transfer function.                                                       |

| $G_{VR}$                                                                                                                               | Transfer function of PI controller.                                      |

| $ar{I}_{ m load},  \widetilde{i}_{ m load}$                                                                                            | Load current.                                                            |

| $\hat{I}_{L{ m ref}_{1i}},\hat{i}_{L{ m ref}_{1i}}$                                                                                    | Reference for the peak value of inductor current.                        |

| $\hat{\hat{I}}_r$ $\hat{\hat{i}}_r$                                                                                                    | Peak inductor current.                                                   |

| $\begin{array}{l} \bar{\hat{I}}_{L_{1i}},\tilde{\hat{i}}_{L_{1i}}\\ \bar{\underline{I}}_{L_{1i}},\tilde{\hat{i}}_{L_{1i}} \end{array}$ | Inductor current.                                                        |

| $ar{I}_{O}, ar{i}_{O}$                                                                                                                 | Average output current over a half-line                                  |

| $\iota_o, \iota_o$                                                                                                                     | cycle.                                                                   |

| $ar{I}_{VR}$ , $	ilde{i}_{VR}$                                                                                                         | Correcting signal of proportional-integral                               |

| IVR, $VVR$                                                                                                                             | controller.                                                              |

| $k_{fb}$                                                                                                                               | Feedback gain.                                                           |

| $K_a(K_{a,crit})$                                                                                                                      | Conduction parameter; critical conduction                                |

|                                                                                                                                        | parameter.                                                               |

| $K_1$                                                                                                                                  | RMS gain.                                                                |

| $K_2$                                                                                                                                  | Conversion gain of inductor current.                                     |

| $L_{11}; L_{12}; L_{13}$                                                                                                               | Input side inductor.                                                     |

| $L_{21}; L_{22}; L_{23}$                                                                                                               | Output side inductor.                                                    |

| $M, n_{\mathrm{Tr}}$                                                                                                                   | The voltage relation in CCM; the turn ratio                              |

| ,                                                                                                                                      | between primary and secondary.                                           |

| _                                                                                                                                      | 1                                                                        |

Audio susceptibility.

Input phase voltage.

signal value).

DC output voltage.

output voltage.

Dynamic impedance.

Location of the zero.

Output impedance.

Rectified input voltage.

Instantaneous voltage and current.

Caret  $\bar{V}$  means steady state and  $\tilde{v}$  means

Reference for the small-signal value of

the introduced perturbation (small-

Control function. Switching period.

0885-8993/\$26.00 © 2009 IEEE

$T_A$

$V_{gi}$ ,  $\tilde{v}_{gi}$

$V_o, \tilde{v}_o$

v,i

$Z_L$

$Z_o$

$\omega_Z$

$\tilde{v}_{\text{oref}}$

$\begin{array}{c} V_{S_{aN}}$  ,  $V_{S_{bN}}$  ,  $V_{S_{cN}}$   $\bar{V}$  ,  $\tilde{v}$

#### I. INTRODUCTION

N RECENT years, high-quality rectifiers have been increasingly used in industrial, commercial, residential, aerospace, electronic equipment, telecommunication, and computer systems due to advantages of high quality, high power density, high efficiency, high reliablility, long lifetime, and low-cost power supplies. In order to comply with the international standards for electromagnetic compatibility and precise regulation, an approach to achieve almost unity power factor is to use an active power factor correction (PFC) circuit [1] followed by a dc-to-dc stage, which provides high-frequency insulation as well as tight output voltage regulation. As compared to boost [2]-[7], pushpull [8], buck-boost [9] or flyback [10], CUK, and single-ended primary inductor converter (SEPIC), PFC's are less popular due to their higher complexity. However, they overcome some basic limitations of other topologies. SEPIC [11] and CUK [12]–[15] converters can be attractive for PFC applications because they offer easy implementation of transformer isolation, inherent inrush current limitation during start-up and overload conditions, and ability to generate arbitrary output voltages. It has been shown that SEPIC and CUK converters have advantages over the boost converter in terms of the conducted noise or electromagnetic interference (EMI). In particular, in both configurations, all inductive components can be realized on the same core, and the magnetic components can be designed for very low inductor current ripples. To satisfy such requirements, the isolated CUK PFC converter is proposed.

An isolated dc-dc CUK converter is shown in Fig. 1. The input section resembles that of a boost converter, while the output section is similar to a buck stage. It offers either step-up or step-down output voltage with respect to the input, producing a negative output voltage from a positive input voltage. The magnetizing inductance of CUK converter does not carry a dc current component, so that the transformer can be fully utilized. It is interesting to note that, with a proper choice of the inductances, the line current of CUK converter remains continuous even if one or both of the inductors operate in the discontinuous conduction mode, and thus, input filter requirement can be reduced. Advantages can be gained by magnetically coupling the two inductors [16]–[18]. In the continuous conduction mode of operation, the voltage waveforms of the input inductor, output inductor, and transformer windings are proportional in magnitude, and have the same frequency and phase shift. Therefore, it is possible to integrate these three elements in one magnetic structure, with zero current ripples in both input and output inductors. Many additional benefits are achieved from the magnetic integration, such as high power density, low cost, lower operating frequency, low noise and EMI, high efficiency, and small-size filteringcomponent at the input and output side.

The active rectifier front end of a dc distributed power system (DPS) has been attracting increased attention due to incessantly growing power quality concerns. Modular design of each unit in the DPS is good for maintainability. Therefore, a single-phase parallel configuration using ac-to-dc boost, SEPIC, and CUK converters for dc DPS have been developed [19]–[21]. Due to its high efficiency, good current quality, and low EMI emissions,

Fig. 1. Single-phase CUK rectifier.

a three-phase PWM rectifier is normally applied for high-power applications. However, this type of three-phase PFC converter has more component counts and a complicated controller design that causes poor reliability. A three-phase converter using single-phase single-switch modular rectifier topology has the merits of simple control and few components. They are becoming popular for low- voltage or medium-power applications [22], [23]. A great amount of work has already been done concerning the three-phase PWM boost [24]–[28], buck [29], [30], buck-boost [31], full-bridge [32], or CUK rectifiers [33]. They often require input or output transformer isolation for safety, and also offer a unity input power factor, limited input harmonic currents fed back to the ac power distribution system, high efficiency, and high power density.

A three-phase converter using three modified single-phase single-switch boost rectifier modules was proposed for highpower and high-voltage applications. Normally, a single-phase boost PFC converter converts an ac voltage to a dc voltage, which is higher than the ac peak value (for an ac three-phase 380 V supply, the dc output voltage may be higher than 588 V<sub>dc</sub>). Compared to the conventional three-phase PWM rectifier, this type of three-phase PFC converter features a simple and robust configuration. The converter can achieve almost unity power factor, nearly sinusoidal input current, and adjustable output voltage. Some of the topologies are suitable only for step-up voltage conversion. When step-down voltage conversion is required, an additional power stage must be added, which will result in an increase in circuit components and cost. For telecommunications and computer system, usually a second-stage dc-dc converter is used to change the voltage from 380 to 48 V or -48 V. Existing high-power PFC approaches use a three-phase boost-type switched-mode rectifier as a first-stage converter to achieve ac-dc power conversion with a typical dc output voltage of 680 V. A second-stage dc-dc converter then converts the voltage from 680 to 48 V or -48 V. The major problems of existing boost-type schemes include the redundancy in the two-stage arrangement and the high intermediate dc voltage for a three-phase ac-dc converter. The two-stage operation would lead to reduced efficiency, and increased size and cost of magnetic, filtering components. To avoid the problem arising from the traditional two-stage conversion approach, a single-stage three-phase ac-dc converter, as shown in Fig. 2, is examined. It consists of three modules connected in parallel. Each module comprises a diode rectifier and a CUK converter with electrical isolation. The performance of the CUK converter suggests that this is the best topology. The CUK converter also offers greater flexibility in the configuration thatcan be implemented as isolation is easily incorporated.

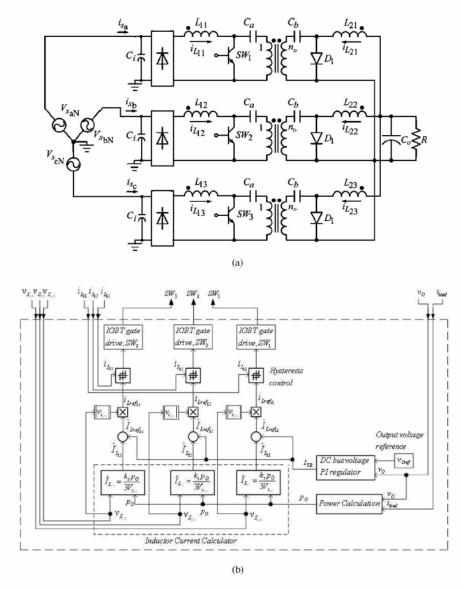

Fig. 2. Proposed system. (a) Power circuit of the modular three-phase ac-to-dc converter using CUK rectifier modules. (b) Control structure and detailed control block.

In this paper, the implementation and control of the modular three-phase ac-to-dc converter using three single-phase isolated CUK rectifier modules with nearly unity power factor and fast dynamic transient response for telecommunication systems is presented under the continuous-conduction-mode (CCM) of operation. The objective of the proposed scheme is to overcome the disadvantages of the three conversion stages in cascade (PFC stage, dc-to-ac stage, and ac-to-dc stage) to simplify the design procedure of the dc bus voltage regulator, PFC, and inductor current sharing, and to improve the dynamic response. The average small-signal model of the proposed system will be analyzed and designed. It is used to obtain the inductor current compensator, thus resulting in the output impedance and audio susceptibility becoming zero, i.e., the output voltage of the converter presented in this paper is independent of the variations of the dc load current and the utility voltage. This control strategy has high dynamic features, and can achieve a fast dynamic transient responseby action of the inductor current compensator.

The deduction of the proposed inductor current compensator is also quite easy, but the effect is sensible. Its main features include: the proposed system's modularity, simple control strategy, and design; the second-order harmonic current component in the output capacitor is cancelled, and this significantly reduces capacitor heating, improves its operating life, and could minimized a dc bus capacitor. The system behavior will be described for symmetric module conditions by simulation and experimental results. The experimental results demonstrate that the proposed system works well, has fast dynamic response, with simple control strategy, good PFC, and the inductor current sharing. In the following sections, a power stage topology and control scheme, dynamic modeling for controller design, results of circuit simulations, and hardware experiments are presented.

#### II. SINGLE-PHASE CUK RECTIFIER MODULE

A single-phase CUK PFC with input—output isolation is shown in Fig. 1, which consists of a diode full-bridge rectifier, a dc-to-dc isolated CUK converter, and an output filter. A CUK PFC was designed with the following characteristics: input voltage  $V_s=220~{\rm V}\pm10\%$ , line frequency 50 Hz, power factor  $\geq 0.95$ , maximum output power per module  $P_o=250~{\rm W}~(R=9.216~\Omega)$ , output dc voltage  $V_o=-48~{\rm V}$ , the turn ratio between primary and secondary  $n_{\rm Tr}=0.5$ , and efficiency  $\eta \geq 85\%$ . The input current is sinusoidal with unity power factor, and the interaction between modules is neglected.

The power factor circuit can also be optimized over a wide range of current ripple and efficiency. As the current ripple increases, the inductance decreases. The smallest inductance occurs at the discontinuous mode. Therefore, running the circuit in the discontinuous mode results in the smallest inductor size and power stage weight. The penalty is higher current stress and conduction loss. The input filter size also increases as the current ripple increases. Experiment has shown that a power factor circuit with smaller current ripple is suitable for high-power applications, when the noise generated by the inductor current and switch current stress are the primary concern. The discontinuous-mode operation, on the other hand, is better suited for low-power application when the objectives are small core size and low-cost control circuits. To operate at CCM, one can find the following.

1) The dc voltage conversion ratio  $m(\theta) = V_o/(\hat{V}_g |\sin(\theta)|)$ , the M ratio is

$$M = \frac{V_o}{\hat{V}_o} = 0.1543. \tag{1}$$

2) The conduction parameter of the CUK PFC circuit

$$K_a > \frac{1}{(2(M + n_{\text{Tr}} |\sin(\theta)|)^2)} > 1.167.$$

(2)

Here,  $K_a$  is chosen to be equal to 2.

3) An equivalent inductance

$$L_{\rm eq} = \frac{RT_{\rm sw}K_a}{2} = 0.3072 \text{ mH}$$

(3)

where, the diode voltage drops are neglected.

By choosing the input inductor current with 30% current ripple,  $\Delta i_{L_{1i}} = 0.482$  A. The design of  $L_{1i}$  and  $L_{2i}$  is made using the desired ripple value of the input current. When the nominal duty cycle d=0.235, the input-side inductor  $L_{1i}$  is chosen based on the specified maximum current ripple

$$L_{1i} = \frac{\hat{V}_g dT_{\text{sw}}}{\Delta i_{L_{1i}}} = 5.068 \text{ mH}.$$

(4)

Switching period  $T_{\rm sw}$  is  $1/f_{\rm sw}$ . The measured inductance of the designed input inductor is 5 mH at 30 kHz. The output-side inductor  $L_{2i}$  is then selected using

$$L_{2i} = \frac{n_{\text{Tr}}^2 L_{1i} L_{\text{eq}}}{L_{1i} - L_{\text{eq}}} = 81 \ \mu\text{H}.$$

(5)

TABLE I SPECIFICATION AND PARAMETERS OF A MODULAR THREE-PHASE AC-TO-DC CONVERTER USING CUK RECTIFIER MODULES

| Characteristic                 | Power Modules                   |

|--------------------------------|---------------------------------|

| Input Phase Voltage            | 220 V                           |

| Input Frequency                | 50 Hz                           |

| Switching Frequency            | Variable frequency, ≈ 25-30 kHz |

| Rated Module                   | 250 W/module                    |

| Total Output Power             | 750 W                           |

| Output Voltage                 | -48 V                           |

| $L_{II}, L_{I2}, L_{I3}$       | 5.069 mH, 5.068mH, 5.066 mH     |

| $L_{21}$ , $L_{22}$ , $L_{23}$ | 1.066 mH, 1.086 mH, 1.044 mH    |

| $C_a$ , $C_b$ , $C_o$          | 0.68 μF, 13,600 μF              |

| $k_p, \omega_Z$                | 1, 150                          |

| $K_1, K_2$                     | 0.707, 1.414                    |