# รายงานวิจัยฉบับสมบูรณ์

โครงการ การออกแบบวงจรกรองสัญญาณปรับตัวได้ย่านกว้างแบบไฟเลี้ยงและกำลังงานต่ำ

โดย หาย อมร จิรเสรือมรกุล

# รายงานวิจัยฉบับสมบูรณ์

# โครงการ การออกแบบวงจรกรองสัญญาณปรับตัวได้ย่านกว้างแบบไฟเลี้ยงและกำลังงานต่ำ

ผู้วิจัย สังกัด

นายอมร จิรเสรีอมรกุล มหาวิทยาลัยเทคโนโลยีมหานคร

สนับสนุนโดยสำนักงานคณะกรรมการการอุดมศึกษา สำนักงานกองทุนสนับสนุนการวิจัย และ มหาวิทยาลัยเทคโนโลยีมหานคร

(ความเห็นในรายงานนี้เป็นของผู้วิจัย สกอ. และ สกว. ไม่จำเป็นต้องเห็นด้วยเสมอไป)

#### บทคัดย่อ

รหัสโครงการ: MRG5480056

ชื่อโครงการ: การออกแบบวงจรกรองสัญญาณปรับตัวได้ย่านกว้างแบบไฟเลี้ยงและ กำลังงานต่ำ

ชื่อหักวิจัย และสถาบัน: อมร จิรเสรือมรกุล มหาวิทยาลัยเทคโนโลยีมหานคร

อีเมล์: amorn@mut.ac.th

ระยะเวลาโครงการ: 2 ปี

#### บทคัดย่อ:

โครงการวิจัยนี้มุ่งพัฒนาระบบวงจรกรองเลือกช่องสัญญาณในวงจรส่วนหน้าของระบบ รับ-ส่งสัญญาณไร้สายด้วยเทคโนโลยีวงจรรวม ที่มีความสามารถในการปรับเปลี่ยนคุณลักษณะ เพื่อชดเชยความผิดพลาดจากความแปรปรวนของอุปกรณ์อันเนื่องมาจากกระบวนการผลิต อุณหภูมิ และสภาพแวดล้อมได้ โดยยังจำเป็นต้องมีความเป็นเชิงเส้นสูงเนื่องจากต้องประมวล สัญญาณย่านความถี่กว้าง ซึ่งสัญญาณอื่นนอกเหนือย่านความถี่ที่สนใจสามารถถูกโอนย้ายเข้า มารบกวนชุดข้อมูลได้ผ่านความไม่เป็นเชิงเส้นของวงจรกรองสัญญาณเอง หัวใจสำคัญคือการใช้ เทคนิคสวิตช์-ตัวต้านทาน ซึ่งจะทำการเปิด-ปิดสวิตช์ที่ต่ออนุกรมอยู่กับตัวต้านทานพาสซิฟ เพื่อควบคุมปริมาณกระแสเฉลี่ยที่ใหลผ่านตัวต้านทาน โดยการปรับเปลี่ยนค่ารอบเวลาทำงาน ของสัญญาณนาพิกา ส่งผลให้เสมือนหนึ่งว่าค่าความต้านทานประสิทธิผลเปลี่ยนแปลงได้ และ ทำให้ค่าคงตัวเวลาซึ่งเป็นตัวกำหนดช่วงความถี่ตัดของวงจรกรองสัญญาณถูกปรับเปลี่ยนไป ด้วยเช่นกัน และเนื่องจากการปรับเปลี่ยนค่าความต้านทานกระทำในโดเมนเวลา จึงไม่เกิด ข้อจำกัดจากระดับแรงดันไฟเลี้ยงอีกด้วย นอกจากนี้ ยังได้ประยุกต์เอาโพลภายในของ วงจรขยายสัญญาณมาใช้เป็นส่วนหนึ่งในการสร้างโพลของวงจรกรอง ส่งผลให้สามารถออกแบบ วงจรขยายให้มีช่วงปฏิบัติการทางความถี่ที่ใกล้เคียงกับความถี่ตัดของวงจรกรอง ช่วยให้ลดการ ใช้พลังงานลงได้อย่างมากเมื่อเทียบกับหลักการออกแบบด้วยโครงสร้างทั่วไป ซึ่งผลจำลองการ ทำงานของวงจรกรองสัญญาณช่วงความถี่ต่ำผ่านที่มีความถี่ตัด 10 เมกกะเฮิรตซ์ โดยอาศัย เทคนิคสวิตซ์-ตัวต้านทาน ด้วยเทคโนโลยีซีมอสขนาด 18 ไมครอนให้ผลที่สอดรับกับที่ คาดหมายไว้

คำหลัก : ไฟเลี้ยงและกำลังงานต่ำ, สวิตช์-ตัวต้านทาน, วงจรกรองสัญญาณปรับตัวได้

Abstract

Project Code: MRG5480056

Project Title: Low-voltage low-power reconfigurable active filter

Investigator: Amorn Jiraseree-amornkun, Mahanakorn University of Technology

E-mail Address: amorn@mut.ac.th

**Project Period: 2 years**

Abstract:

This project has developed a reconfigurable channel select filter for front-end circuits in telecommunication systems. This filter is a crucial part as it helps in separating the desired channel from the others and from interference. The challenge has arisen because several strong signals may exist within the wide receiving frequency range. These pose a stringent linearity requirement on analog filters, which is difficult especially if a wide tuning range is also needed. The continuous-time active-RC filters comprising operational amplifiers (opamps) and highly linear passive resistors and capacitors have superior linearity properties for baseband applications, where opamps with sufficient gain are feasible. Nevertheless, there is a critical issue, which is the RC time-constant variation due to process uncertainty, temperature drift, and aging. The Switched-Resistor techniques make use of switch(es) with duty-cycle-controlled clock(s) to achieve tenability of the effective resistance and, hence, the RC time constant. Such tuning occurs in the time domain, thereby decoupling the tuning ranges from supply voltages. For low-power concerns, the internal pole of the opamp has been used to realize the filter transfer function so that only one opamp is required to implement a second-order filter and its unity-gain-bandwidth is comparable to the filter cut-off frequency. Thus, the opamp power consumption is strongly reduced with respect to other closed-loop filter configurations. Simulation results of a 10-MHz low-pass filter based on the Switched-Resistor techniques, in a standard 0.18-μm CMOS process, show good agreement with theories.

Keywords: low-voltage low-power, switched-resistor, reconfigurable filter

## ความสำคัญและที่มาของปัญหาที่ทำการวิจัย

วงจรกรองสัญญาณไฟฟ้า เป็นส่วนประกอบสำคัญที่นิยมใช้อย่างแพร่หลายในระบบ อิเล็กทรอนิกส์ทั่วไป เพื่อใช้ประมวลผลคัดกรองเฉพาะสัญญาณในย่านความถี่ที่สนใจและกำจัด ทิ้งสัญญาณส่วนที่ไม่ต้องการ ในระบบสื่อสารไร้สายสมัยใหม่ที่กำลังมีบทบาทอย่างสูงต่อ ชีวิตประจำวัน ไม่ว่าจะเป็นระบบโทรศัพท์เคลื่อนที่ ระบบการชี้เฉพาะด้วยคลื่นความถี่วิทยุ (radio frequency identification หรือ RFID) และระบบระบุพิกัดตำแหน่งบนพื้นผิวโลก (global positioning system หรือ GPS) เป็นต้น เหล่านี้ล้วนมีการประยุกต์ใช้วงจรกรองสัญญาณเป็น ส่วนสำคัญหลายจุดด้วยกัน องค์ประกอบหนึ่งที่น่าสนใจและมีบทบาทสำคัญคือวงจรกรองเลือก ช่องสัญญาณ (channel select filter) ในวงจรส่วนหน้า (front-end) ซึ่งทำหน้าที่แยก ช่องสัญญาณข้อมูลที่ต้องการออกจากช่องสัญญาณอื่นรวมถึงสัญญาณรบกวนที่กระจายอยู่ ทั่วไป ช่วยลดภาระการทำงานของวงจรภาคถัดไปโดยเฉพาะอย่างยิ่งภาคแปลงสัญญาณแอนะล็ อกเป็นดิจิตัล (analog-to-digital converter) ลงได้อย่างมาก ถ้าหากไม่มีวงจรกรองส่วนนี้ แล้ว วงจรแปลงสัญญาณแอนะล็อกเป็นดิจิตัลจะต้องรองรับสัญญาณย่านกว้างเกินความจำเป็น ทำให้ออกแบบสร้างได้ยาก หรือแม้หากสามารถสร้างได้ก็จะใช้กำลังงานสูงเกินกว่าจะนำมาใช้ ประโยชน์ได้จริง สำหรับวงจรกรองเลือกช่องสัญญาณนั้นคุณสมบัติสำคัญคือต้องมีความเป็นเชิง เส้นสูงเนื่องจากต้องประมวลสัญญาณย่านความถี่กว้าง ซึ่งสัญญาณอื่นนอกเหนือย่านความถี่ที่ สนใจสามารถถูกโอนย้ายเข้ามารบกวนชุดข้อมูลได้ผ่านความไม่เป็นเชิงเส้นของวงจรกรอง สัญญาณเอง โดยวงจรในภาคถัดไปสามารถลดข้อจำกัดด้านความเป็นเชิงเส้นลงได้ เพราะวงจร กรองนี้ได้ช่วยกำจัดสัญญาณส่วนเกินออกไปแล้ว

ปัญหาหลักของการสร้างวงจรกรองสัญญาณด้วยเทคโนโลยีวงจรรวม (integrated circuit หรือ IC) คือ ค่าความแปรปรวนของอุปกรณ์อันเนื่องมาจากกระบวนการผลิต อุณหภูมิ และสภาพแวดล้อม ซึ่งส่งผลให้คุณลักษณะของวงจรกรองผิดเพี้ยนไปใด้ วงจรกรองจึงต้องมี ความสามารถในการปรับเปลี่ยนค่าเพื่อชดเชยความผิดพลาดจากข้อจำกัดเหล่านี้ นอกจากนั้น ทิศทางการพัฒนาระบบสื่อสารสัญญาณไร้สายในปัจจุบัน ยังมุ่งเน้นไปที่การออกแบบระบบรับส่งสัญญาณไร้สายที่สามารถปรับตัวได้ (reconfigurable transceiver) เพื่อให้สามารถรองรับ มาตรฐานการสื่อสารได้หลายรูปแบบด้วยการปรับเปลี่ยนทางซอร์ฟแวร์ (software-defined-radio หรือ SDR) ซึ่งจะช่วยให้ตัวอุปกรณ์สามารถประยุกต์ใช้งานได้หลากหลายและมีราคาที่ถูก ลงอย่างมาก อย่างไรก็ตาม โดยทั่วไปแล้วมาตรฐานการสื่อสารแต่ละแบบมักมีคุณลักษณะที่ แตกต่างกันมาก เช่น ย่านความถี่คลื่นพาห์ ช่วงความถี่ของสัญญาณข้อมูล และชนิดของการ ผสมสัญญาณ เป็นตัน ทำให้การออกแบบวงจรอิเล็กทรอนิกส์ที่สามารถรองรับการเปลี่ยนแปลง ต่างๆ เหล่านี้เป็นเรื่องที่ท้าทายมาก [1] โดยเฉพาะวงจรกรองเลือกช่องสัญญาณที่จำเป็นจะต้อง กำจัดสัญญาณส่วนเกิน ซึ่งอาจมีขนาดใหญ่กว่าสัญญาณข้อมูลมากๆ ได้ตลอดย่านความถี่ที่

กว้างยิ่งขึ้น นั่นหมายถึง วงจรกรองสัญญาณที่ออกแบบจะต้องมีความเป็นเชิงเส้นสูงในขณะที่ สามารถปรับเปลี่ยนคุณลักษณะของวงจรได้ในย่านกว้าง [2 – 4] อันนับเป็นเรื่องยาก เพราะ คุณสมบัติสองอย่างนี้มักจะมีแนวโน้มสวนทางกัน และโดยเฉพาะอย่างยิ่ง เมื่อต้องออกแบบให้ สามารถใช้งานที่ระดับแรงดันและกินกำลังงานต่ำสำหรับอุปกรณ์พกพาด้วยแล้ว ความยากก็ จะ ยิ่งเพิ่มสูงขึ้นเนื่องจากระดับสัญญาณภายในวงจรจะถูกลดทอนลงด้วยนั่นเอง ทำให้จำเป็นต้องมี การลดระดับของสัญญาณรบกวนในสัดส่วนเดียวกัน ยังผลให้การกินกระแสและกำลังงานของ วงจรเพิ่มมากขึ้นและสมรรถนะโดยรวมต่ำลงในที่สุด

ในโครงการนี้จะทำการพัฒนาวงจรกรองสัญญาณที่มีความเป็นเชิงเส้นสูง เหมาะสมกับ การทำงานที่ระดับแรงดันไฟเลี้ยงต่ำและกินกำลังงานต่ำด้วยเทคนิคสวิตช์-ตัวต้านทาน (switched-resistor) [5] ซึ่งอาศัยหลักการเปิด-ปิดสวิตช์ที่ต่ออนุกรมอยู่กับตัวต้านทานพาสซิฟ เพื่อควบคุมปริมาณกระแสเฉลี่ยที่ใหลผ่านตัวต้านทาน โดยการปรับ เปลี่ยนค่ารอบเวลาทำงาน (duty cycle) ของสัญญาณนาพิกา ส่งผลให้เสมือนหนึ่งว่าค่าความต้านทานประสิทธิผล (effective resistance) เปลี่ยนแปลงใด้ และทำให้ค่าคงตัวเวลา (time-constant) ซึ่งเป็น ตัวกำหนดช่วงความถี่ตัดของวงจรกรองสัญญาณถูกปรับเปลี่ยนไปด้วยเช่นกัน เมื่อออกแบบให้ ตัวสวิตช์มีความต้านทานภายในต่ำมากพอ สัญญาณขาเข้าส่วนใหญ่จะตกคร่อมที่ตัวต้านทาน พาสซิฟซึ่งมีความเป็นเชิงเส้นสูง ส่งผลให้ระบบมีความเพี้ยนต่ำ และเนื่องจากการปรับเปลี่ยนค่า ความต้านทานกระทำในโดเมนเวลา จึงไม่เกิดข้อจำกัดจากระดับแรงดันไฟเลี้ยงอีกด้วย เทคนิค นี้จึงเหมาะสมอย่างยิ่งสำหรับการนำไปประยุกต์ใช้ในระบบสื่อสารไร้สายยุคใหม่ ที่ต้องการการ ปรับเปลี่ยนคุณลักษณะได้และทำงานที่ระดับแรงดันไฟเลี้ยงและกำลังงานต่ำ

องค์ความรู้ใหม่ที่มุ่งพัฒนา คือการลดพลังงานที่ใช้ในวงจรกรองลงและผลักดันให้ สามารถใช้งานได้ที่ความถี่สูงขึ้น ทั้งนี้เนื่องจากวงจรกรองเลือกช่องสัญญาณนี้นิยมสร้างด้วย เทคนิคแอกทิฟ-อาร์ซี (active-RC) เพราะมีความเป็นเชิงเส้นสูง แต่เงื่อนไขในการออกแบบที่ สำคัญคือวงจรออปแอมป์ซึ่งเป็นอุปกรณ์แอกทิฟหลักจำเป็น ต้องมีช่วงความถี่ปฏิบัติงานสูงกว่า ความถี่ตัดของวงจรกรองมากๆ ส่งผลให้ย่านปฏิบัติการของวงจรกรองมีค่าจำกัดและเกิดกำลัง งานสูญเสียมากอีกด้วย ดังนั้นการพัฒนาโครงสร้างวงจรที่เหมาะสมเพื่อทำงานได้ที่ย่านความถี่ สูงและกินกำลังงานต่ำ จึงเป็นส่วนสำคัญที่จะทำให้การออกแบบวงจรกรองสัญญาณมี ประสิทธิภาพสูงมากยิ่งขึ้นโดยแนวทางการพัฒนาก็คือ การพยายามใช้โพลภายในของวงจรออป แอมป์เองเป็นส่วนหนึ่งของโพลวงจรกรอง [6 – 7] ด้วยหลักการนี้จะสามารถลดข้อจำกัดของ ย่านความถี่ปฏิบัติงานและกำลังงานสูญเสียลงได้อย่างมาก นอก จากนี้ ยังต้องพยายามพัฒนา วงจรกรองความถี่ที่สามารถปรับค่าได้ในย่านกว้าง เพื่อให้มีความคล่องตัวในการใช้งานเป็นวงจร ส่วนหน้าของระบบสื่อสารไร้สายตามมาตรฐานที่มีอยู่อย่างหลากหลาย หรือประยุกต์ใช้สำหรับ รับ-ส่งข้อมูลจากทรานสดิวเซอร์ประเภทต่างๆ ทั้งในด้านชีวะการแพทย์ (Biomedical sensors) ด้านสิ่งแวดล้อม (Environmental sensors) และอื่นๆ ซึ่งโดยส่วนใหญ่จะมีความต้องการด้าน แบนด์วิดท์สัญญาณที่ค่อนข้างแตกต่างกันมาก ทำให้จำเป็นต้องมีวงจรกรองปรับค่าความถี่ย่าน

กว้าง ที่สามารถปรับแต่งสมรรถนะให้เหมาะสมสำหรับการใช้งานเฉพาะเพื่อลดการกินกำลังงาน ให้มากที่สุด

ทั้งนี้จะเห็นได้ว่า หลักการที่นำเสนอในโครงการนี้ มีศักยภาพต่อการนำไปพัฒนาวงจร รวมกรองสัญญาณสำหรับระบบที่ต้องการความเป็นเชิงเส้นสูง ทำงานได้ที่ระดับแรงดันไฟเลี้ยง ต่ำและกินกำลังงานต่ำ มีประโยชน์อย่างยิ่งต่อการนำไปประยุกต์ใช้งานในระบบอิเล็กทรอนิกส์ ต่างๆ โดยเฉพาะระบบการสื่อสารไร้สายแบบพกพา หรือระบบรับ-ส่งสัญญาณจากหน่วย ตรวจจับขนาดเล็กที่มีขีดจำกัดเรื่องแหล่งพลังงาน ซึ่งวงจรกรองสัญญาณนี้เป็นจุดสำคัญหนึ่งที่ กำหนดสมรรถนะและประสิทธิภาพในการใช้พลังงานของระบบเลยทีเดียว และด้วย ความสามารถปรับเปลี่ยนคุณลักษณะทางความถี่ได้ในย่านกว้าง จึงช่วยชดเชยความผิดพลาดที่ อาจเกิดขึ้นจากกระบวนการผลิต ตลอดจนครอบคลุมมาตรฐานของระบบที่มีอยู่อย่างหลากหลาย เหล่านี้ เป็นส่วนสำคัญยิ่งที่จะช่วยประหยัดทั้งด้านต้นทุนการผลิตและพัฒนา และต้นทุนทางด้าน พลังงานไปด้วยพร้อมกัน

## 3. วัตถุประสงค์ของโครงการ

- 1. พัฒนาองค์ความรู้ด้านการออกแบบวงจรกรองสัญญาณปรับตัวได้ย่านกว้าง ด้วย เทคนิคการสุ่มเลือกสัญญาณแบบปรับรอบเวลาทำงาน

- 2. พัฒนาเทคนิควงจรกรองสัญญาณที่ทำงานในระดับแรงดันไฟเลี้ยงต่ำและกินกำลังงาน ต่ำ

- 3. ศึกษาและเปรียบเทียบสมรรถนะของวงจรกรองสัญญาณที่ปรับตัวได้ด้วยเทคนิคสวิตช์ ตัวต้านทานแบบชุดเดียวและแบบสองชุด เทียบกับวงจรมาตรฐานแบบต่อเนื่องทาง เวลา

- 4. เพิ่มพูนศักยภาพของนักวิจัยในด้านการออกแบบ สร้าง และทดสอบวงจรกรอง สัญญาณแบบปรับตัวได้

#### 4.1 เทคนิคสวิตช์-ตัวต้านทานแบบชุดเดียว

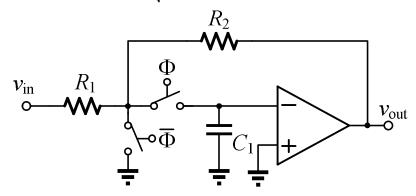

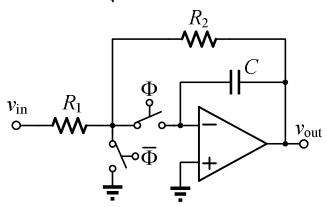

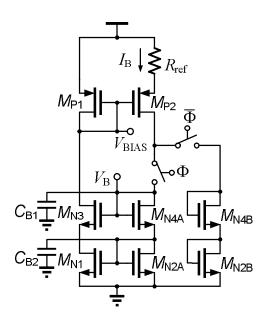

ร**ูปที่ 4.1** วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานชุดเดียว

สำหรับการทดลองนั้นจะเป็นการทดสอบวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลัง งานต่ำแบบที่ใช้ชุดสวิตช์-ตัวต้านทานเพียงชุดเดียวที่นำเสนอซึ่งรูปวงจรแสดงดังในรูปที่ 4.1 และเพื่อ ประเมินสมรรถนะการทำงานของวงจรกรองสัญญาณกินกำลังงานต่ำแบบสวิตช์-ตัวต้านทานชุดเดียว ที่นำเสนอ จึงได้ทำการออกแบบวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองแบบปลายเปิดสองด้าน ที่มีอัตราขยาย  $A_{\rm LP}=0$  dB ช่วงความถี่ตัด  $f_{\rm LP}=1$  MHz และค่าองค์ประกอบคุณภาพ  $Q_{\rm LP}=0.8$  (ภาคผนวก 7.1) ด้วยเทคโนโลยีแบบซีมอสมาตรฐานขนาด 0.18 ไมครอน ทำงานที่ระดับแรงดัน 1.8 โวลต์ ใช้สัญญาณนาพิกาควบคุมความถี่ 100 เมกะเฮิรตซ์ และตัวสวิตช์ใช้โครงสร้างแบบทรานสมิช ชันเกต (transmission gate) กำหนดให้ค่าตัวเก็บประจุชดเชย  $C_{\rm C}=1.5$  pF และอัตราส่วนในชุด วงจรปรับค่าอัตราขยายความนำภาคแรก p=0.25 จะทำให้ได้ค่าอุปกรณ์  $C_1=3.84$  pF และ  $R_1=R_2=33.15$  k $\Omega$  และเมื่อกำหนดค่าตัวปรับกระแสภาคแรก a=2 และค่าตัวปรับกระแสภาคที่สอง b=4 (ภาคผนวก 7.3) จะทำให้ได้ค่าขนาดของมอสทรานซิสเตอร์แสดงดังตารางที่ 4.1

#### ขั้นตอนการทดสอบประกอบด้วย

- 1. การวิเคราะห์ PSS (Periodic Steady State) ร่วมกับ PAC (Periodic AC) เพื่อดู ผลตอบสนองทางความถี่ของวงจรกรองสัญญาณ และความสามารถในการปรับค่าความถึ่ ตัดด้วยการปรับค่ารอบเวลาการทำงานของสัญญาณนาฬิกา

- 2. การป้อนสัญญาณทดสอบสองความถี่ (two-tone test) ที่มีย่านความถี่ประมาณหนึ่งใน สามของค่าความถี่ตัด เพื่อหาค่าองค์ประกอบความเพื้ยนเชิงอินเตอร์มอดูเลตอันดับที่ สาม IMD<sub>3</sub>

- 3. การประเมินสมรรถนะด้านสัญญาณรบกวนด้วยการวิเคราะห์ PSS ร่วมกับ PNOISE (Periodic Noise)

**ตารางที่ 4.1** ขนาดของอุปกรณ์มอสทรานซิสเตอร์สำหรับวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับ สองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานชุดเดียว

| มอสทรานซิสเตอร์                                                     | ขนาด       |  |  |  |

|---------------------------------------------------------------------|------------|--|--|--|

| $M_1$ , $M_2$ , $M_{P1}$ , $M_{B2}$ , $M_{B3}$ , $M_{F5}$           | 7.5µm/1µm  |  |  |  |

| <i>M</i> <sub>B1</sub>                                              | 15μm/1μm   |  |  |  |

| $M_{P2}, M_{B4}, M_{B5},$                                           | 30μm/1μm   |  |  |  |

| M <sub>F1</sub> , M <sub>F2</sub>                                   | 3.75µm/1µm |  |  |  |

| $M_{\rm N1}-M_{\rm N4}$                                             | 5μm/1μm    |  |  |  |

| $M_{\text{F3}}, M_{\text{F4}}$                                      | 2.5μm/1μm  |  |  |  |

| $M_3 - M_5$                                                         | 10μm/1μm   |  |  |  |

| M <sub>7</sub> , M <sub>8</sub> , M <sub>C1</sub> , M <sub>C2</sub> | 20μm/1μm   |  |  |  |

#### 4.2 เทคนิคสวิตช์-ตัวต้านทานแบบสองชุด

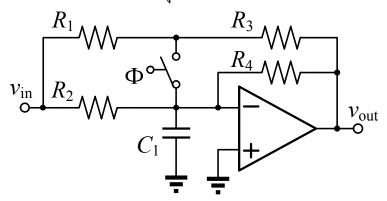

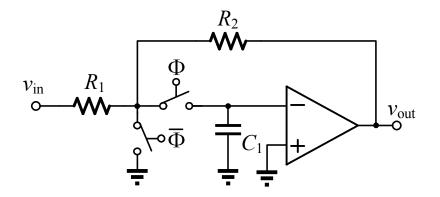

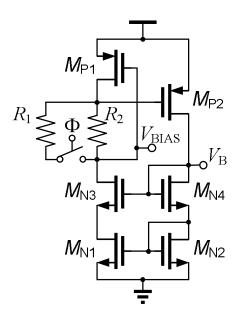

รู**ปที่ 4.2** วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานสองชุด

สำหรับการทดสอบวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบที่ใช้ชุด สวิตซ์-ตัวต้านทานสองชุดที่นำเสนอแสดงรูปวงจรดังรูปที่ 4.2 ได้ทำการออกแบบวงจรกรองสัญญาณ ความถี่ต่ำผ่านอันดับสองแบบปลายเปิดสองด้าน ที่มีอัตราขยาย  $A_{\rm LP}$  = 0 dB ช่วงความถี่ตัด  $f_{\rm LP}$  =1 MHz และค่าองค์ประกอบคุณภาพ  $Q_{\rm LP}$  = 0.8 (ภาคผนวก 7.2) ด้วยเทคโนโลยีแบบซีมอสมาตรฐาน ขนาด 0.18 ไมครอน ทำงานที่ระดับแรงดัน 1.8 โวลต์ ใช้สัญญาณนาพิกาควบคุมความถี่ 100 เมกะเฮิรตซ์ และตัวสวิตซ์ใช้โครงสร้างแบบทรานสมิชชันเกต เลือกให้อัตราส่วนระหว่างตัวต้านทาน ของชุดสวิตซ์-ตัวต้านทาน k = 3 ซึ่งจะทำให้ได้ช่วงปรับจูนความถี่ตัดของวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานชุดเดียวเพื่อสะดวกต่อการเปรียบเทียบสมรรถนะระหว่างโครงสร้าง นั่นคือ กำหนดค่าตัวเก็บ

ประจุชดเชย  $C_{\rm C}$  = 1.5 pF อัตราส่วนระหว่างพีมอสทรานซิสเตอร์ในชุดวงจรปรับค่าอัตราขยายความ นำภาคหน้า p = 0.25 จะทำให้ได้ค่าอุปกรณ์  $C_1$  = 3.84 pF,  $R_1$  =  $R_3$  = 44.2 k $\Omega$  และ  $R_2$  =  $R_4$  = 132.6 k $\Omega$  และเมื่อกำหนดค่าตัวปรับกระแสภาคแรก a = 2 และค่าตัวปรับกระแสภาคที่สอง b = 4 (ภาคผนวก 7.3) จะทำให้ได้ค่าขนาดของมอสทรานซิสเตอร์เหมือนกันกับวงจรกรองสัญญาณแบบ สวิตช์-ตัวต้านทานชุดเดียวดังตารางที่ 4.1 สำหรับขั้นตอนการทดสอบก็จะเป็นเช่นเดียวกับวงจรกรอง สัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานชุดเดียวในตอนที่ 4.1 เช่นกัน

#### 5.1 เทคนิคสวิตช์-ตัวต้านทานแบบชุดเดียว

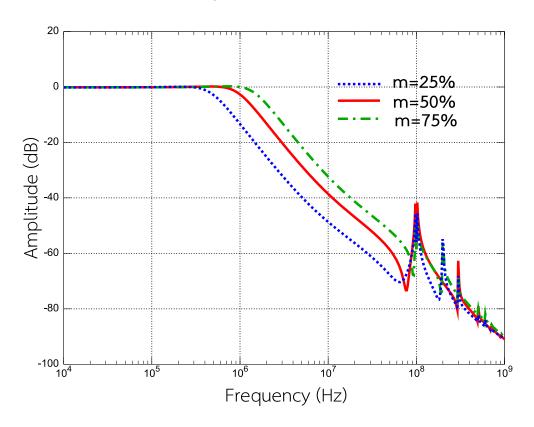

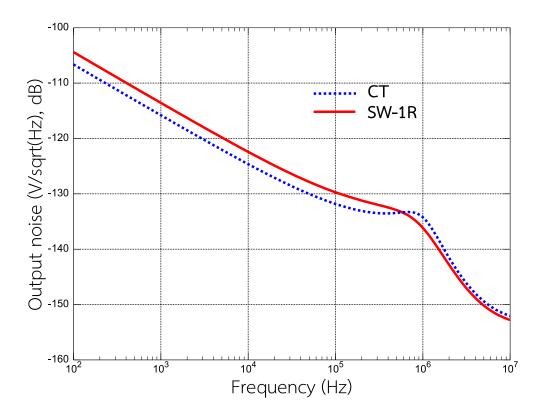

รูปที**่ 5.1** ผลตอบสนองทางความถี่ของวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำ แบบสวิตช์-ตัวต้านทานชุดเดียว เมื่อปรับค่ารอบเวลาทำงานเป็น 25%, 50% และ 75%

ผลการจำลองผลตอบสนองทางความถี่ของวงจรกรองสัญญาณด้วยการวิเคราะห์ PSS ร่วมกับ PAC เมื่อปรับค่ารอบเวลาทำงานสัญญาณนาพิกา (m) เป็น 25%, 50% และ 75% แสดงดัง รูปที่ 5.1 ซึ่งจะได้ค่าความถี่ตัดของวงจรกรองสัญญาณเป็น 0.54, 1.02 และ 1.57 เมกะเฮิรตซ์ ตามลำดับ โดยให้ช่วงการปรับค่าความถี่ประมาณ ±50% ดังที่ได้ออกแบบไว้ และจะสามารถ สังเกตเห็นองค์ประกอบรบกวนจากสัญญาณนาพิกาได้ค่อนข้างชัดเจน

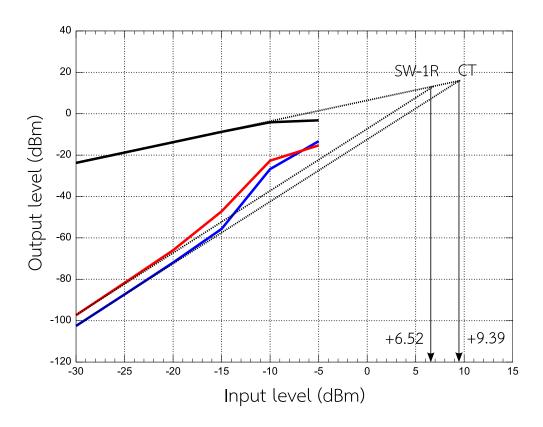

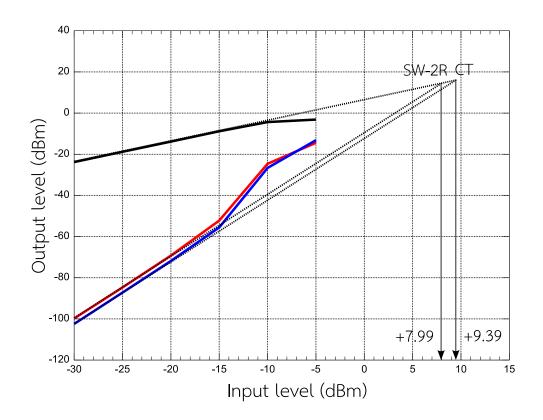

เมื่อทำการป้อนสัญญาณทดสอบสองความถี่ (two-tone test) ที่มีย่านความถี่ประมาณหนึ่งใน สามของค่าความถี่ตัด นั่นคือความถี่ 300 กิโลเฮิรตซ์ และ 400 กิโลเฮิรตซ์ สำหรับค่ารอบเวลาทำงาน 50% ด้วยขนาดสัญญาณ 0.1 V<sub>p</sub> จะได้ค่าองค์ประกอบความเพี้ยนเชิงอินเตอร์มอดูเลตอันดับที่สาม IMD<sub>3</sub> = -41.46 dB ทั้งนี้สำหรับโครงสร้างวงจรกรองสัญญาณเดิมแบบต่อเนื่องทางเวลา ที่ใช้วงจร ออปแอมป์ที่เหมือนกันทุกประการ จะให้ค่าองค์ประกอบความเพี้ยน IMD<sub>3</sub> = -47.34 dB และเมื่อทำ การทดสอบเปลี่ยนค่าขนาดกำลังงานขาเข้าเพื่อหาค่าจุดตัดสัญญาณขาเข้าอันดับสาม IIP<sub>3</sub> ก็จะได้ค่า เท่ากับ +6.52 dBm และ +9.39 dBm สำหรับวงจรกรองสัญญาณแบบสวิตซ์-ตัวตำนทาน (SW-1R) และแบบต่อเนื่องทางเวลา (CT) ตามลำดับ ดังแสดงในรูปที่ 5.2

ร**ูปที่ 5.2** ค่าจุดตัดสัญญาณขาเข้าอันดับสาม IIP<sub>3</sub> ของวงจรกรองแบบสวิตช์-ตัวต้านทานชุด เดียวเทียบกับแบบต่อเนื่องทางเวลา

ร*ูปที่ 5.3* ค่าสัญญาณรบกวนรวมด้านขาออกของของวงจรกรองแบบสวิตช์-ตัวต้านทานชุดเดียวเทียบ กับแบบต่อเนื่องทางเวลา

**ตารางที่ 5.1** สมรรถนะรวมของวงจรกรองสัญญาณแบบสวิตช์-ตัวต้านทานชุดเดียว

| สมรรถนะ                                            | СТ     | SW-1R (m) |        |        |

|----------------------------------------------------|--------|-----------|--------|--------|

|                                                    |        | 25%       | 50%    | 75%    |

| ความถี่ตัด (MHz)                                   | 1.03   | 0.54      | 1.02   | 1.57   |

| $f_{ m u}$ ออปแอมป์ (MHz)                          | 1.8    | 0.9       | 1.82   | 2.67   |

| กำลังงานสูญเสีย (μW)                               | 35.4   | 15.5      | 35.7   | 59.7   |

| IMD <sub>3</sub> * (dB)                            | -47.34 | -35.48    | -41.46 | -48.98 |

| IIP <sub>3</sub> * (dBm)                           | 9.39   | 3.2       | 6.52   | 9.92   |

| ์ สัญญาณรบกวนรวมด้านออก** $(x10^{-8} \text{ V}^2)$ | 6.45   | 8         | 8.4    | 9.24   |

| สัญญาณรบกวนอ้างอิงด้านเข้า** (μV <sub>rms</sub> )  | 125    | 172.6     | 159.7  | 161.5  |

#### หมายเหตุ:

- \* สัญญาณสองความถี่ห่าง 100 กิโลเฮิรตซ์ ที่ความถี่ประมาณหนึ่งในสามของความถี่ตัด

- \*\* สัญญาณรบกวนผลต่าง อินทีเกรตตั้งแต่ความถี่ 100 เฮิรตซ์ ถึงความถี่ตัด

ในส่วนของสมรรถนะด้านสัญญาณรบกวนนั้นจะอาศัยการวิเคราะห์ PSS ร่วมกับ PNOISE ซึ่งผลจำลองค่าสัญญาณรบกวนรวมด้านขาออกที่ค่ารอบเวลาทำงาน 50% เปรียบเทียบกับวงจรกรอง สัญญาณแบบต่อเนื่องทางเวลา แสดงไว้ในรูปที่ 5.3 ซึ่งจะเห็นได้ว่าวงจรกรองสัญญาณแบบสวิตช์-ตัว ต้านทานนั้นมีค่าสัญญาณรบกวนโดยรวมสูงกว่าถึงแม้ว่าค่าความต้านทานรวมของระบบจะมีขนาดต่ำ กว่าก็ตาม ทั้งนี้ก็เนื่องมาจากปรากฏการณ์พับกลับของสัญญาณรบกวน (noise folding) นั่นเอง โดย ปรากฏค่าสัญญาณรบกวนขาออกที่ทำการอินทีเกรตตั้งแต่ความถี่ 100 เฮิรตซ์ ถึง 1.02 เมกะเฮิรตซ์ มีค่าประมาณ 8.4×10<sup>-6</sup> V² และ 6.45×10<sup>-6</sup> V² สำหรับวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทาน และแบบต่อเนื่องทางเวลา ตามลำดับ สำหรับสมรรถนะต่างๆ ของระบบรวมถึงค่ากำลังงานสูญเสีย และค่าความถี่ที่อัตราขยายของออปแอมป์เป็นหนึ่ง ที่ค่ารอบเวลาทำงานอื่น ได้แสดงสรุปไว้ในดาราง ที่ 5.1 ซึ่งจะเห็นได้ว่าแม้สมรรถนะโดยรวมจะลดลงจากวงจรแบบต่อเนื่องทางเวลาไปบ้าง และจะยิ่ง ลดลงเมื่อความถี่ตัดมีค่าเข้าใกล้สัญญาณนาพิกามากขึ้น แต่ก็สามารถปรับกำลังงานขึ้นชดเชยเพื่อ เพิ่มสมรรถนะได้ แลกกับความสามารถในการปรับคุณลักษณะได้อย่างละเอียดและประหยัดพื้นที่ เพราะหากใช้วิธีการปรับค่าความถี่โดยชุดเลือกตัวต้านทานหรือตัวเก็บประจุแล้ว ก็จะต้องใช้พื้นที่ เพิ่มขึ้นอย่างมาก

## 5.2 เทคนิคสวิตช์-ตัวต้านทานแบบสองชุด

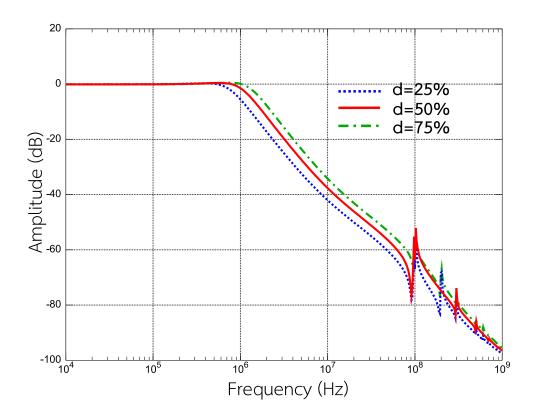

รูปที**่ 5.4** ผลตอบสนองทางความถี่ของวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำ แบบสวิตช์-ตัวต้านทานสองชุดเมื่อปรับค่ารอบเวลาทำงานเป็น 25%, 50% และ 75%

ผลการจำลองผลตอบสนองทางความถี่ของวงจรกรองสัญญาณด้วยการวิเคราะห์ PSS ร่วมกับ PAC เมื่อปรับค่ารอบเวลาทำงานสัญญาณนาพิกา (d) เป็น 25%, 50% และ 75% แสดงดังรูป ที่ 5.4 ซึ่งจะได้ค่าความถี่ตัดของวงจรกรองสัญญาณเป็น 0.83 MHz, 1.15 MHz และ 1.47 MHz ตามลำดับ โดยให้ค่าความถี่ตัดสูงกว่าที่คำนวณเล็กน้อย สำหรับช่วงการปรับค่าความถี่จะได้ ค่าประมาณ ±27% สูงกว่าที่ได้ออกแบบไว้เล็กน้อยเช่นกัน และจะสังเกตได้ว่าองค์ประกอบรบกวน จากสัญญาณนาพิกาจะมีค่าน้อยกว่าวงจรกรองแบบสวิตช์-ตัวต้านทานชุดเดียวในรูปที่ 5.1

เมื่อทำการป้อนสัญญาณทดสอบสองความถี่ ที่มีย่านความถี่ประมาณหนึ่งในสามของ ค่าความถี่ตัด นั่นคือความถี่ 300 กิโลเฮิรตซ์ และ 400 กิโลเฮิรตซ์ สำหรับค่ารอบเวลาทำงาน 50% ด้วยขนาดสัญญาณ 0.1 V<sub>p</sub> จะได้ค่าองค์ประกอบความเพี้ยนเชิงอินเตอร์มอดูเลตอันดับที่สาม IMD<sub>3</sub> = —46.12 dB ซึ่งมีสมรรถนะที่ดีกว่าวงจรกรองแบบสวิตช์-ตัวต้านทานชุดเดียวและมีค่าใกล้เคียงวงจร กรองแบบต่อเนื่องทางเวลา ที่ใช้วงจรออปแอมป์ที่เหมือนกันทุกประการ และเมื่อทำการทดสอบ เปลี่ยนค่าขนาดกำลังงานขาเข้าเพื่อหาค่าจุดตัดสัญญาณขาเข้าอันดับสาม IIP<sub>3</sub> ก็จะได้ค่าเท่ากับ +7.99 dBm และ +9.39 dBm สำหรับวงจรกรองสัญญาณแบบสวิตช์-ตัวต้านทานสองชุด (SW-2R) และแบบต่อเนื่องทางเวลา (CT) ตามลำดับ ดังแสดงในรูปที่ 5.5

ร*ูปที่ 5.5* ค่าจุดตัดสัญญาณขาเข้าอันดับสาม IIP<sub>3</sub> ของวงจรกรองแบบสวิตช์-ตัวต้านทานสองชุดเทียบ กับแบบต่อเนื่องทางเวลา

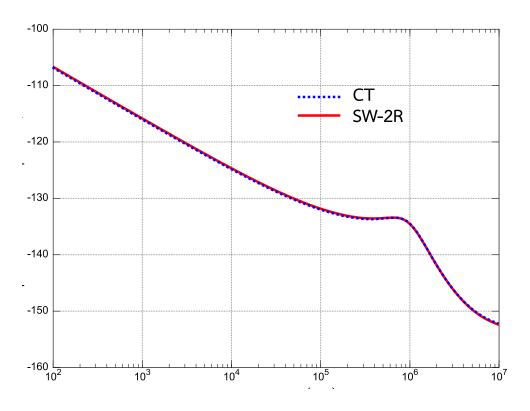

ร*ูปที่ 5.6* ค่าสัญญาณรบกวนรวมด้านขาออกของของวงจรกรองแบบสวิตช์-ตัวต้านทานสองชุดเทียบ กับแบบต่อเนื่องทางเวลา

*ตารางที*่ 5.2 สมรรถนะรวมของวงจรกรองสัญญาณแบบสวิตช์-ตัวต้านทานสองชุด

| สมรรถนะ                                                       | СТ     | SW-2R (d) |        |        |

|---------------------------------------------------------------|--------|-----------|--------|--------|

|                                                               |        | 25%       | 50%    | 75%    |

| ความถี่ตัด (MHz)                                              | 1.03   | 0.83      | 1.15   | 1.467  |

| $f_{ m u}$ ออปแอมป์ (MHz)                                     | 1.8    | 1.39      | 1.82   | 2.28   |

| กำลังงานสูญเสีย (μW)                                          | 35.4   | 25.3      | 36.1   | 48.0   |

| IMD <sub>3</sub> * (dB)                                       | -47.34 | -41.07    | -46.12 | -49.45 |

| IIP <sub>3</sub> * (dBm)                                      | 9.39   | 6.72      | 7.99   | 9.32   |

| ์ สัญญาณรบกวนรวมด้านออก** (x10 <sup>-8</sup> V <sup>2</sup> ) | 6.45   | 5.87      | 6.78   | 7.57   |

| สัญญาณรบกวนอ้างอิงด้านเข้า** (μV <sub>rms</sub> )             | 125    | 156.2     | 177.6  | 196.9  |

#### หมายเหตุ:

- \* สัญญาณสองความถี่ห่าง 100 กิโลเฮิรตซ์ ที่ความถี่ประมาณหนึ่งในสามของความถี่ตัด

- \*\* สัญญาณรบกวนผลต่าง อินทีเกรตตั้งแต่ความถี่ 100 เฮิรตซ์ ถึงความถี่ตัด

ในส่วนของสมรรถนะด้านสัญญาณรบกวนนั้นจะอาศัยการวิเคราะห์ PSS ร่วมกับ PNOISE ซึ่งผลจำลองค่าสัญญาณรบกวนรวมด้านขาออกที่ค่ารอบเวลาทำงาน 50% เปรียบเทียบกับวงจรกรอง สัญญาณแบบต่อเนื่องทางเวลา แสดงไว้ในรูปที่ 5.6 ซึ่งจะเห็นได้ว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัว ต้านทานสองชุดนั้นมีค่าสัญญาณรบกวนใกล้เคียงกับวงจรกรองสัญญาณแบบต่อเนื่องทางเวลาอย่าง มาก นั่นแสดงให้เห็นว่าปรากฏการณ์พับกลับของสัญญาณรบกวนส่งผลต่อระบบนี้น้อยมาก โดย ปรากฏค่าสัญญาณรบกวนขาออกที่ทำการอินทีเกรตตั้งแต่ความถี่ 100 เฮิรตซ์ ถึง 1.15 เมกะเฮิรตซ์ มีค่าประมาณ 6.78×10<sup>-8</sup> V² ซึ่งใกล้เคียงกับค่า 6.45×10<sup>-8</sup> V² ของวงจรกรองสัญญาณแบบต่อเนื่อง ทางเวลาอย่างมาก สำหรับสมรรถนะต่างๆ ของระบบรวมถึงค่ากำลังงานสูญเสียและค่าความถี่ที่ อัตราขยายของออปแอมป์เป็นหนึ่ง ที่ค่ารอบเวลาทำงานต่างๆ ได้แสดงสรุปไว้ในตารางที่ 5.2 ซึ่งจะ เห็นได้ว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานสองชุดจะให้สมรรถนะโดยรวมดีกว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานสองชุดจะให้สมรรถนะโดยรวมดีกว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานสองรุดจะให้สมรรถนะโดยรวมดีกว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานสองรุดจะให้สมรรถนะโดยรวมดีกว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัวต้านทานสุดเดียว และมีความเกล้เคียงวงจรกรองสัญญาณแบบต่อเนื่องมาก ขึ้น จึงเป็นทางเลือกที่ดีสำหรับระบบที่ต้องการความสามารถในการปรับคุณลักษณะได้อย่างละเอียด และประหยัดพื้นที่

### 6. สรุปและวิจารณ์ผลการทดลอง และข้อเสนอแนะ

โครงการวิจัยนี้นำเสนอการพัฒนาวงจรกรองสัญญาณแบบปรับคุณลักษณะได้โดยอาศัย เทคนิคสวิตซ์-ตัวต้านทาน ซึ่งสามารถปรับคุณลักษณะค่าความถี่ตัดของสัญญาณได้โดยอาศัยการ ควบคุมปริมาณกระแสเฉลี่ยที่ไหลผ่านตัวต้านทานด้วยสวิตช์ ร่วมกับการประยุกต์ใช้โพลภายในของ วงจรออปแอมป์เป็นส่วนหนึ่งของโพลวงจรกรองสัญญาณ จึงสามารถใช้ออปแอมป์ตัวเดียวสร้างเป็น วงจรกรองอันดับสองได้ ช่วยให้สามารถลดอัตราการใช้กำลังงานลงได้มาก โดยได้นำเสนอวงจรกรอง สัญญาณไว้ 2 โครงสร้างด้วยกันนั่นคือ วงจรกรองสัญญาณความถี่ผ่านแบบสวิตช์-ตัวต้านทานชุด เดียว และวงจรกรองสัญญาณความถี่ผ่านแบบสวิตช์-ตัวต้านทานสองชุด ซึ่งสมรรถนะของระบบที่ นำเสนอแสดงด้วยผลจำลองการทำงานของวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองที่มีความถี่ตัด 1 เมกกะเฮิรตซ์ ออกแบบด้วยเทคโนโลยีซีมอสขนาด 0.18 ไมครอน ที่แรงดันไฟเลี้ยง 1.8 โวลต์

โดยวงจรกรองสัญญาณความถี่ต่ำผ่านแบบสวิตช์-ตัวต้านทานชุดเดียว จะสามารถปรับค่าความถี่ได้ในช่วง ±50% กินกำลังงานเพียง 36 ไมโครวัตต์ และให้สมรรถนะโดยรวมด้อยกว่าวงจรกรองสัญญาณแบบต่อเนื่องทางเวลาเล็กน้อย แต่อย่างไรก็ตามด้วยข้อจำกัดด้านความเป็นเชิงเส้นของระบบ การนำไปประยุกต์ใช้งานจึงเหมาะกับระบบที่ต้องการความสามารถของการปรับคุณลักษณะได้อย่างละเอียด มีกำลังงานสูญเสียต่ำ ความถี่ไม่สูงมากนักเนื่องจากติดข้อจำกัดของสัญญาณนาพิกาและต้องการความเป็นเชิงเส้นในระดับปานกลาง

สำหรับวงจรกรองสัญญาณความถี่ต่ำผ่านแบบสวิตซ์-ตัวตำนทานสองชุด จะให้สมรรถนะ โดยรวมได้ดีกว่า ใกล้เคียงกับวงจรกรองสัญญาณแบบต่อเนื่องทางเวลาอย่างมาก อีกทั้งตัวโครงสร้าง ยังได้รับผลกระทบและข้อจำกัดของสัญญาณนาพิกาที่น้อยกว่าวงจรกรองสัญญาณแบบสวิตซ์-ตัว ตำนทานชุดเดียวอีกด้วย แต่ก็จะมีจุดด้อยตรงความสามารถในการปรับช่วงความถี่ที่แคบกว่า จึง เหมาะกับการประยุกต์ใช้งานที่ต้องการความสามารถของการปรับคุณลักษณะได้อย่างละเอียดในช่วง ที่ไม่กว้างนัก

ในส่วนแนวทางการพัฒนา อาจมุ่งเน้นในการลดผลกระทบจากสัญญาณนาพิกาให้มากยิ่งขึ้น และอีกปัจจัยสำคัญที่ต้องคำนึงถึงคือ การประยุกต์ใช้โพลภายในของวงจรออปแอมป์เป็นส่วนหนึ่งของ โพลวงจรกรองสัญญาณนั้น ส่งผลต่อสมรรถนะความเป็นเชิงเส้นของระบบโดยตรงโดยเฉพาะบริเวณ ใกล้ช่วงความถี่ตัด เนื่องจากการลดลงของอัตราขยายลูปของการป้อนกลับ หากสามารถปรับปรุง โครงสร้างให้มีความเป็นเชิงเส้นมากขึ้นได้ก็จะสามารถใช้งานกับระบบต่างๆ ได้ดียิ่งขึ้น

#### 7.1 เทคนิคสวิตช์-ตัวต้านทานแบบชุดเดียว

ร**ูปที่ 7.1** วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับหนึ่งแบบสวิตช์-ตัวต้านทานชุดเดียว

วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับที่หนึ่งแบบสวิตช์-ตัวต้านทานชุดเดียวแสดงดังรูปที่ 7.1 โดยกระแสที่ใหลผ่านตัวต้านทานเข้าสู่ตัวเก็บประจุจะถูกควบคุมผ่านการเปิด-ปิดของสวิตช์ที่ต่อ อนุกรมอยู่ ปริมาณกระแสเฉลี่ยจึงถูกควบคุมด้วยการปรับเปลี่ยนค่ารอบเวลาทำงานของสัญญาณ นาฬิกา ส่งผลให้เสมือนหนึ่งว่าค่าความต้านทานประสิทธิผลเปลี่ยนแปลงได้สัมพันธ์กับรอบเวลา ทำงาน และทำให้ช่วงความถี่ตัดของวงจรกรองสัญญาณถูกปรับเปลี่ยนไปด้วยเช่นกัน ระบบนี้มีความ เพี้ยนต่ำเนื่องจากสัญญาณแรงดันขาเข้าส่วนใหญ่จะตกคร่อมที่ตัวต้านทานพาสซิฟซึ่งมีความเป็นเชิง เส้นสูง ส่วนตัวสวิตช์ก็อยู่บริเวณกราวนด์เสมือนซึ่งมีการเปลี่ยนแปลงของแรงดันต่ำ ความไม่เป็นเชิง เส้นจากตัวสวิตช์จึงส่งผลต่อระบบได้น้อย นอกจากนี้ เนื่องจากการปรับเปลี่ยนค่าความต้านทาน เสมือนนั้นกระทำในโดเมนเวลา จึงไม่เกิดข้อจำกัดจากระดับแรงดันไฟเลี้ยงอีกด้วย

อย่างไรก็ตาม โครงสร้างวงจรกรองสัญญาณแบบแอกทิฟ-อาร์ซีที่ใช้ร่วมกับเทคนิคสวิตช์-ตัว ต้านทานแบบเดิม จะมีเงื่อนไขการออกแบบที่สำคัญอันหนึ่งคือ วงจรออปแอมป์ซึ่งเป็นอุปกรณ์ แอกทิฟหลักจำเป็นต้องมีช่วงความถี่ปฏิบัติงานสูงกว่าความถี่ตัดของวงจรกรองสัญญาณมากๆ ส่งผล ให้ย่านความถี่ปฏิบัติการของวงจรกรองมีค่าจำกัดและเกิดกำลังงานสูญเสียมากอีกด้วย ดังนั้นเพื่อให้ ระบบมีประสิทธิภาพเชิงกำลังงานสูงมากยิ่งขึ้น จึงได้ประยุกต์เทคนิคการอาศัยโพลภายในของวงจร ออปแอมป์เองมาเป็นส่วนหนึ่งของโพลวงจรกรองสัญญาณ ส่งผลให้ไม่จำเป็นต้องออกแบบให้วงจร ออปแอมป์มีช่วงความถี่ปฏิบัติงานสูงกว่าความถี่ตัดของวงจรกรองสัญญาณมากๆ จึงช่วยลดอัตรา การใช้กำลังงานลงได้

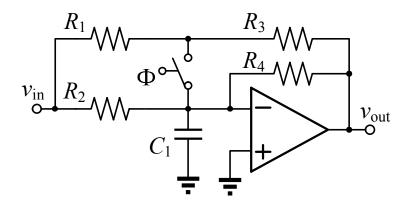

โครงสร้างวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองปลายออกด้านเดียวกินกำลังงานต่ำ แบบสวิตช์-ตัวต้านทานชุดเดียวแสดงดังรูปที่ 7.2 กำหนดให้วงจรออปแอมป์มีฟังก์ชันการถ่ายโอน แรงดันเป็นแบบโพลเดี่ยว (ในช่วงความถี่ที่พิจารณา) ซึ่งสามารถแสดงความสัมพันธ์ได้ดังสมการ

รูปที่ 7.2 วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานชุดเดียว

$$A(s) = \frac{A_0}{1 + s/\omega_0} = \frac{\omega_u}{s + \omega_0} \tag{7.1}$$

เมื่อ  $A_0$  ,  $\omega_{\scriptscriptstyle

m u}$  และ  $\omega_{\scriptscriptstyle

m 0}$  คือ อัตราขยายแรงดันไฟตรง ความถี่เชิงมุมเมื่ออัตราขยายแรงดันเป็นหนึ่ง และความถี่เชิงมุมโพลตัวแรกของวงจรออปแอมป์ ตามลำดับ

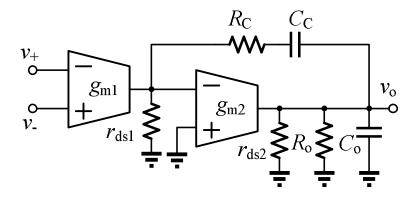

*รูปที่* **7.3** วงจรสมมูลโครงสร้างภายในของออปแอมป์แบบสองภาค

บล็อกโครงสร้างภายในของวงจรออปแอมป์แบบสองภาคพื้นฐานสามารถแสดงได้ดังรูปที่ 7.3 โดยภาคหน้ามีอัตราขยายความนำส่งผ่าน  $g_{\rm m1}$  และความต้านทานขาออก  $r_{

m ds1}$  ภาคที่สองมี อัตราขยายความนำส่งผ่าน  $g_{

m m2}$  และความต้านทานขาออก  $r_{

m ds2}$  ภาระของวงจรประกอบด้วยตัว ต้านทาน  $R_{

m o}$  และตัวเก็บประจุ  $C_{

m o}$  มีการชดเชยความถี่ด้วยตัวเก็บประจุมิลเลอร์  $C_{

m C}$  และตัวต้านทาน  $R_{

m C}$

เนื่องจากโครงสร้างวงจรกรองสัญญาณได้อาศัยโพลภายในของวงจรออปแอมป์เพื่อเป็นส่วน หนึ่งของโพลระบบ และกำหนดให้วงจรออปแอมป์มีฟังก์ชันการถ่ายโอนแรงดันเป็นแบบโพลเดี่ยว ดังนั้นเมื่อต้องการให้ความถี่ตัดของวงจรกรองสัญญาณสามารถปรับเปลี่ยนได้ด้วยค่ารอบเวลาทำงาน ของสัญญาณนาฬิกา องค์ประกอบสำคัญภายในตัวออปแอมป์ที่จำเป็นต้องสามารถถูกปรับตามได้

ด้วยก็คือค่าอัตราขยายความนำส่งผ่านของภาคแรก หรือ  $g_{\rm ml}$  โดยจะต้องมีวงจรไบอัสที่ช่วยควบคุม ค่า  $g_{\rm ml}$  ให้ปรับเปลี่ยนตามค่ารอบเวลาทำงานของสัญญาณนาพิกาด้วย โดยในที่นี้จะกำหนดให้  $g_{\rm ml}=m/(A_{\rm g}.R_1)$  เมื่อ m คือค่ารอบเวลาทำงานของสัญญาณนาพิกา  $\Phi$  ในรูปที่ 7.2 และ  $A_{\rm g}$  เป็น ค่าคงที่ที่สามารถกำหนดได้เอง

เมื่อทำการวิเคราะห์บล็อกวงจรในรูปที่ 7.3 หากออกแบบให้ค่า  $g_{\rm ml}$   $r_{\rm ds1}>>1$  และ  $1/R_2>>1/r_{\rm ds2}+sC_{\rm o}$  พร้อมทั้งเลือกให้  $R_2=n.R_1$  เมื่อ n คือค่าคงที่แล้ว จะสามารถพิสูจน์ได้ว่า ฟังก์ชันถ่ายโอนแรงดันของวงจรกรองสัญญาณความถี่ต่ำผ่านแบบสวิตช์-ตัวต้านทาน  $H_{\rm LP}$  จะขึ้นอยู่ กับค่าของอุปกรณ์พาสซิฟเพียงอย่างเดียวเท่านั้น และสามารถปรับเปลี่ยนได้ด้วยค่ารอบเวลาทำงาน ของสัญญาณนาพิกา ดังแสดงในสมการ

$$H_{LP}(s) = -\frac{\frac{m^2}{A_g R_1^2 C_1 C_c}}{s^2 + s \cdot \frac{m(R_1 + R_2)}{R_1 R_2 C_1} + \frac{m^2}{A_g R_1 R_2 C_1 C_c}}$$

(7.2)

โดยค่าองค์ประกอบที่สำคัญได้แก่ อัตราขยายแรงดันไฟตรง  $A_{\mathsf{LP}}$  ค่าความถี่ตัด  $f_{\mathsf{LP}}$  และค่า องค์ประกอบคุณภาพ  $Q_{\mathsf{LP}}$  ของวงจรกรองสัญญาณจะสามารถแสดงได้ดังสมการ

$$A_{LP} = \frac{R_2}{R_1} = n {(7.3)}$$

$$f_{LP} = \frac{m}{2\pi} \cdot \sqrt{\frac{1}{A_g R_1 R_2 C_1 C_c}}$$

(7.4)

$$Q_{\rm LP} = \frac{1}{1 + A_{\rm LP}} \cdot \sqrt{\frac{A_{\rm LP}}{A_{\rm g}} \cdot \frac{C_{\rm l}}{C_{\rm C}}}$$

(7.5)

ซึ่งเห็นได้ชัดเจนว่าค่าความถี่ตัดของวงจรกรองสัญญาณ  $f_{\rm LP}$  สามารถถูกปรับได้อย่างเป็นเชิงเส้นด้วย การเปลี่ยนค่ารอบเวลาทำงานของสัญญาณนาฬิกา m โดยไม่ส่งผลกระทบต่อค่าอัตราขยายแรงดันไฟ ตรงและค่าองค์ประกอบคุณภาพของวงจรกรองสัญญาณแต่อย่างใด

และเมื่อทำการวิเคราะห์หาค่าความถี่ที่อัตราขยายเป็นหนึ่ง  $f_{

m u}=g_{

m ml}$  / $(2\pi C_{

m C})$  ของวงจรออป แอมป์เทียบกับค่าความถี่ตัดของวงจรกรองสัญญาณ  $f_{

m LP}$  ตามสมการ (7.4) แล้ว จะทำให้ได้ ความสัมพันธ์

$$\frac{f_u}{f_{LP}} = Q_{LP} \cdot (1 + A_{LP}) \tag{7.6}$$

ซึ่งจะเห็นได้ว่าค่าความถี่ที่อัตราขยายเป็นหนึ่งของวงจรออปแอมป์นี้แปรผันตรงกับค่าความถี่ตัดของ วงจรกรองสัญญาณ และค่าที่ได้มีขนาดน้อยมากเมื่อเทียบกับโครงสร้างแบบดั้งเดิม ส่งผลให้สามารถ ลดกำลังงานที่ต้องใช้ลงสำหรับวงจรออปแอมป์ลงได้อย่างมาก

#### 7.2 เทคนิคสวิตช์-ตัวต้านทานแบบสองชุด

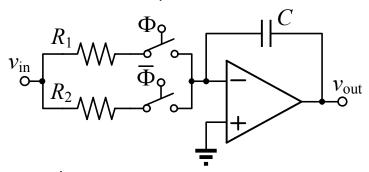

รูปที**่ 7.4** วงจรอินทิเกรเตอร์แบบสวิตช์-ตัวต้านทานสองชุด

วงจรอินทิเกรเตอร์แบบสวิตช์-ตัวต้านทานสองชุดแสดงดังในรูปที่ 7.4 จะเห็นได้ว่ากระแสที่ ไหลเข้าสู่ตัวเก็บประจุเกิดจากการไหลผ่านตัวต้านทานพาสซิฟ 2 ค่าที่สลับกันนำกระแสผ่านการเปิด-ปิดของสวิตช์ที่ต่ออนุกรมอยู่ ปริมาณกระแสเฉลี่ยจึงถูกควบคุมด้วยการปรับเปลี่ยนค่ารอบเวลา ทำงานของสัญญาณนาพิกา ส่งผลให้เสมือนหนึ่งว่าค่าความต้านทานประสิทธิผล เปลี่ยนแปลงได้ และ ทำให้ช่วงความถี่ตัดของวงจรกรองสัญญาณถูกปรับเปลี่ยนไปด้วยเช่นกัน [8]

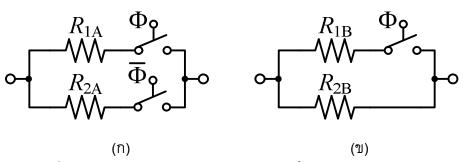

ร**ูปที่ 7.5** สวิตช์-ตัวต้านทานสองชุด (ก) แบบดั้งเดิม (ข) แบบปรับปรุง

จากวงจรอินทิเกรเตอร์แบบสวิตช์-ตัวต้านทานสองชุดในรูปที่ 7.4 เมื่อแยกพิจารณาเฉพาะ ส่วนสวิตช์-ตัวต้านทานจะได้ดังรูปที่ 7.5(ก) ซึ่งหากกำหนดให้  $R_{\rm 2A}$  มีขนาดเป็น k เท่าของ  $R_{\rm 1A}$  แล้วจะทำให้ได้ค่าความต้านทานประสิทธิผล  $R_{\rm eff}$  ของระบบเป็น

$$R_{eff} = \frac{k \cdot R_{1A}}{(k-1) \cdot d + 1} \tag{7.7}$$

เมื่อกำหนดให้ d คือค่ารอบเวลาทำงานของสัญญาณนาพิกาควบคุม  $\Phi$  และเมื่อกำหนดให้ค่าความ ต้านทานกลางเกิดขึ้นเมื่อค่ารอบเวลาทำงานอยู่ที่ 50% หรือ d=0.5 จะสามารถหาช่วงการ เปลี่ยนแปลงค่าความต้านทานด้วยการปรับค่ารอบเวลาทำงานของสัญญาณนาพิกาได้เป็น

$$\Delta R_{eff}(\pm\%) = \frac{(k-1)\cdot 0.5 + 1}{(k-1)\cdot (d_{\text{max/min}} - 0.5)} \times 100\%$$

(7.8)

เมื่อ  $d_{

m max/min}$  คือค่ารอบเวลาทำงานสูงสุดหรือต่ำสุดของสัญญาณนาพิกา

จุดหนึ่งที่สังเกตได้จากชุดสวิตช์-ตัวต้านทานในรูปที่ 7.5(ก) คือ จำเป็นต้องใช้สัญญาณ นาพิกาควบคุม 2 ชุดทำงานสลับกันและไม่มีช่วงที่ซ้อนทับกัน (non-overlapping clock) ซึ่งเป็น การเพิ่มความยุ่งยากในการออกแบบระบบควบคุม จึงได้นำเสนอชุดสวิตช์-ตัวต้านทานแบบปรับปรุง ดังรูปที่ 7.5(ข) ซึ่งลดการใช้สัญญาณนาพิกาลงเหลือเพียงชุดเดียวเท่านั้น โดยในขณะที่สัญญาณ นาพิกาเป็น "0" จะมีกระแสไหลผ่านเฉพาะตัวต้านทาน  $R_{2B}$  แต่เมื่อสัญญาณนาพิกาเป็น "1" จะมี กระแสไหลผ่านตัวต้านทาน  $R_{1B}$  และ  $R_{2B}$  พร้อมกัน จึงเสมือนหนึ่งมีกระแสไหลผ่านตัวต้านทาน 2 ค่า เช่นเดียวกันกับวงจรในรูปที่ 7.5(ก) นั่นเอง

ในกรณีที่ต้องการออกแบบให้วงจรในรูปที่ 7.5(ข) มีคุณสมบัติเหมือนกับวงจรในรูปที่ 7.5(ก) สามารถทำได้ด้วยการกำหนดให้  $R_{\mathrm{2B}}$  =  $R_{\mathrm{2A}}$  และ  $R_{\mathrm{1B}}$  //  $R_{\mathrm{2B}}$  =  $R_{\mathrm{1A}}$  ซึ่งจะทำให้ได้ความสัมพันธ์ ของค่าความต้านทาน เป็น

$$R_{\rm 1B} = \frac{k}{k-1} \cdot R_{\rm 1A} \tag{7.9}$$

วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองปลายออกด้านเดียวแบบสวิตช์-ตัวต้านทานสอง ชุดแสดงดังรูปที่ 7.6 เมื่อพิจารณาออปแอมป์ว่ามีฟังก์ชันถ่ายโอนเป็นแบบโพลเดี่ยวดังสมการ (7.1) มีโครงสร้างภายในเป็นแบบสองภาคพื้นฐานและมีคุณสมบัติเช่นเดียวกับในกรณีเทคนิคสวิตช์ตัว ต้านทานชุดเดียวในตอนที่ 7.1 จะพบว่าวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองแบบสวิตช์-ตัว ต้านทานสองชุดจะมีฟังก์ชันถ่ายโอนแรงดันดังสมการ

$$H_{LP}(s) = -\frac{\frac{m^2}{A_g^2 R_1^2 C_1 C_C}}{s^2 + s \cdot \frac{m(R_1 + R_3)}{R_1 R_3 C_1} + \frac{m^2}{A_g R_1 R_3 C_1 C_C}}$$

(7.10)

ร**ูปที่ 7.6** วงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองกำลังงานต่ำแบบสวิตช์-ตัวต้านทานสองชุด

ซึ่งมีความใกล้เคียงกับฟังก์ชันถ่ายโอนของวงจรกรองสัญญาณความถี่ต่ำผ่านอันดับสองแบบสวิตช์-ตัวต้านทานชุดเดียวในสมการ (7.2) อย่างมาก โดยมีตัวแปรหลักที่แตกต่างคือตัวแปรการปรับค่าด้วย รอบสัญญาณนาฬิกา

$$m = \frac{(k-1)\cdot d + 1}{k-1}$$

(7.11)

สำหรับค่าองค์ประกอบที่สำคัญได้แก่ อัตราขยายไฟตรง  $A_{\mathsf{LP}}$  ค่าความถี่ตัด  $f_{\mathsf{LP}}$  และค่า องค์ประกอบคุณภาพ  $Q_{\mathsf{LP}}$  ของวงจรกรองสัญญาณแสดงได้ดังสมการ

$$A_{LP} = \frac{R_3}{R_1} = \frac{R_4}{R_2} = n \tag{7.12}$$

$$f_{\rm LP} = \frac{m}{2\pi} \cdot \sqrt{\frac{1}{A_{\rm g} R_{\rm l} R_{\rm s} C_{\rm l} C_{\rm c}}}$$

(7.13)

$$Q_{\rm LP} = \frac{1}{1 + A_{\rm LP}} \cdot \sqrt{\frac{A_{\rm LP}}{A_{\rm g}} \cdot \frac{C_{\rm l}}{C_{\rm C}}}$$

(7.14)

ซึ่งมีความสอดคล้องกับสมการ (7.3) – (7.5) อย่างมาก

และเมื่อทำการวิเคราะห์จะพบว่าค่าความถี่ที่อัตราขยายเป็นหนึ่ง  $f_{\rm u}$  ของออปแอมป์จะแปรผัน ตรงกับค่าความถี่ตัดของวงจรกรองสัญญาณ  $f_{\rm LP}$  เช่นเดียวกันกับสมการ (7.6) ซึ่งมีค่าน้อยลงมากเมื่อ เทียบกับโครงสร้างแบบดั้งเดิม

## 7.3 วงจรออปแอมป์ที่เลือกใช้

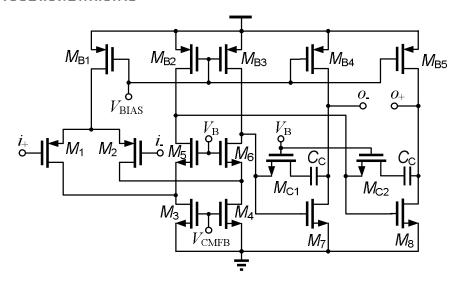

ร*ูปที่* 7.7 วงจรออปแอมป์สองภาคแบบคาสโคดพับปลายเปิดสองด้าน

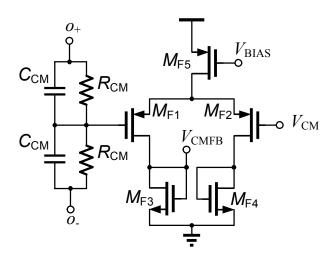

สำหรับวงจรออปแอมป์แบบสองภาคที่เลือกใช้จะเป็นโครงสร้างแบบคาสโคดพับ (folded cascode) และเป็นแบบปลายเปิดสองด้านดังแสดงในรูปที่ 7.7 เพื่อเพิ่มสมรรถนะช่วงขนาดสัญญาณ แรงดันมากยิ่งขึ้น โดยวงจรป้อนกลับโหมดร่วมสำหรับทำหน้าที่ผลิตแรงดัน  $V_{\mathrm{CMFB}}$  มาควบคุมไบอัส ของวงจรเป็นแบบต่อเนื่องทางเวลาแบบทั่วไปดังแสดงในรูปที่ 7.8 [9]

ร**ูปที่ 7.8** วงจรขยายสำหรับการป้อนกลับเพื่อควบคุมโหมดผลร่วม

รูปที่ 7.9 วงจรไบอัสและปรับค่าอัตราขยายความนำภาคหน้าสำหรับวงจรกรองสัญญาณแบบสวิตช์-ตัวต้านทานชุดเดียว

ส่วนแรงดัน  $V_{

m BIAS}$  จะถูกสร้างขึ้นโดยวงจรปรับค่าอัตราขยายความนำแบบสวิตช์-ตัว ต้านทาน ซึ่งพัฒนามาจากโครงสร้างของวงจรไบอัสค่าความนำคงที่เป็นพื้นฐาน [9] และจะมีความ แตกต่างกันระหว่างเทคนิคสวิตช์-ตัวต้านทานแบบชุดเดียวกับแบบสองชุด โดยวงจรปรับค่า อัตราขยายความนำสำหรับเทคนิคสวิตช์-ตัวต้านทานชุดเดียวแสดงดังในรูปที่ 7.9 ทรานซิสเตอร์  $M_{

m P1}$  และ  $M_{

m P2}$  ต่อร่วมกับตัวต้านทาน  $R_{

m ref}$  ทำหน้าที่กำหนดค่ากระแสไบอัส  $I_{

m B}$  ดังความสัมพันธ์

$$I_{B}R_{ref} = V_{SG,P1} - V_{SG,P2} (7.16)$$

และเมื่อออกแบบให้ขนาดของมอสทรานซิสเตอร์  $(W/L)_{P1}=p.(W/L)_{P2}$  เมื่อ p เป็นค่าคงที่ ความ ต้านทาน  $R_{\rm ref}$  มีค่าเท่ากับ  $R_1$  ในรูปที่ 7.2 และชุดวงจรสะท้อนกระแสแบบคาสโคด  $M_{\rm N1}-M_{\rm N4}$  ทำงานได้อย่างสมบูรณ์แล้ว จะสามารถพิสูจน์ได้ว่าค่ากระแสไบอัสของวงจรมีค่าเป็น

$$I_{B} = \frac{2}{\mu_{P} C_{OX} (W/L)_{P2}} \cdot \left(\frac{1}{\sqrt{p}} - 1\right)^{2} \cdot \left(\frac{m}{R_{1}}\right)^{2}$$

(7.17)

โดยชุดสวิตซ์ 2 ตัวที่ถูกควบคุมด้วยสัญญาณนาพิกาแบบไม่ซ้อนทับกัน  $\Phi$  และ  $\overline{\Phi}$  จะทำหน้าที่ตัด ต่อกระแสที่ไหลในวงจรเพื่อทำให้ค่ากระแสไบอัสแปรผันตาม  $(m/R_1)^2$  ส่วนชุดมอสทรานซิสเตอร์  $M_{\rm N2B}$  และ  $M_{\rm N4B}$  จะมีขนาดเท่าชุดมอสทรานซิสเตอร์  $M_{\rm N2A}$  และ  $M_{\rm N4A}$  ทำหน้าที่เป็นภาระจำลอง ให้กับทรานซิสเตอร์  $M_{\rm P2}$  เพื่อไม่ให้เกิดสภาวะกระแสถูกตัดขาดทันทีทันใด และตัวเก็บประจุ  $C_{\rm B1}-C_{\rm B2}$  ทำหน้าที่ปรับระดับแรงดันและกระแสไบอัสให้มีความราบเรียบเพียงพอต่อการนำไปใช้งาน

เมื่อนำแรงดัน  $V_{\rm BIAS}$  ที่ได้จากวงจรในรูปที่ 7.9 ไปป้อนให้กับวงจรในรูปที่ 7.7 และ 7.8 และ หากกำหนดให้ขนาดของมอสทรานซิสเตอร์  $({\rm W/L})_{\rm B1}=2.({\rm W/L})_{\rm 1,2}=a.({\rm W/L})_{\rm P2}$  เมื่อ a เป็น ค่าคงที่แล้วละก็ จะสามารถพิสูจน์ได้ว่าค่าอัตราขยายความนำส่งผ่านภาคแรกจะมีค่าเป็น  $g_{\rm m1}=m/(A_{\rm g}.R_{\rm 1})$  ตามที่ต้องการ โดยที่

$$A_g = \frac{1}{a} \cdot \frac{\sqrt{p}}{1 - \sqrt{p}} \tag{7.18}$$

นอกจากนี้ตัววงจรไบอัสยังทำหน้าที่สร้างแรงดันเพื่อไบอัสให้กับ คาสโคดมอสทรานซิสเตอร์  $M_5-M_6$  และมอสทรานซิสเตอร์ชดเชยทางความถี่  $M_{\rm C1}-M_{\rm C2}$  ในวงจรรูปที่ 7.7 อีกด้วย ซึ่งหาก กำหนดให้  $({\rm W/L})_{\rm N2}=({\rm W/L})_{\rm N4}$  และ  $({\rm W/L})_{\rm B4,B5}=b.({\rm W/L})_{\rm P2}$  เมื่อ b เป็นค่าคงที่ ก็จะ สามารถหาค่าขนาดของมอสทรานซิสเตอร์  $M_{\rm C1}-M_{\rm C2}$  ได้ดังสมการ

$$(W/L)_{c_{1,C2}} = \frac{(W/L)_{7,8}}{\sqrt{\frac{4}{b} \cdot \sqrt{\frac{(W/L)_{7,8}}{(W/L)_{N_{2,N_4}}}} - 1}}$$

(7.19)

ร**ูปที่ 7.10** วงจรไบอัสและปรับค่าอัตราขยายความนำภาคหน้าสำหรับวงจรกรองสัญญาณแบบสวิตช์-ตัวต้านทานสองชุด

สำหรับวงจรปรับค่าอัตราขยายความนำสำหรับเทคนิคสวิตช์-ตัวต้านทานสองชุดแสดงดังใน รูปที่ 7.10 ประกอบด้วยทรานซิสเตอร์  $M_{\rm P1}$  และ  $M_{\rm P2}$  ต่อร่วมกับตัวต้านทาน  $R_1,\,R_2$  และสวิตช์ที่ ควบคุมด้วยสัญญาณนาฬิกา  $\Phi$  และวงจรสะท้อนกระแสแบบคาสโคด  $M_{\rm N1}-M_{\rm N4}$  ทำหน้าที่กำหนด

ค่ากระแสไบอัส  $I_{

m B}$  โดยค่าความต้านทานจะเลือกตามวงจรกรองสัญญาณ และแม้จะมีความแตกต่าง จากวงจรสำหรับเทคนิคสวิตช์-ตัวตำนทานชุดเดียวในรูปที่ 7.9 แต่ก็จะให้ความสัมพันธ์เหมือน เช่นเดียวกันทุกประการ ตามเงื่อนไขและสมการ (7.16) – (7.19) เมื่อ ค่า m เป็นตามสมการ (7.11)

#### 7.4 เอกสารอ้างอิง

- [1] B. Debaillie et.al., "Analog/RF Solutions Enabling Compact Full-Duplex Radios," IEEE J. Selected Areas in Communications, vol. 32, no. 9, pp. 1162–1673, Jun. 2014.

- [2] A. M. Durham, J. B. Hughes, and W. Redman-White, "Circuit architectures for high linearity monolithic continuous-time filtering," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 39, no. 9, pp. 651–657, Sep. 1992.

- [3] S. Pavan, Y. P. Tsividis, and K. Nagaraj, "Widely Programmable High-Frequency Continuous-Time Filters in Digital CMOS Technology," *IEEE J. Solid-State Circuits*, vol. 35, no. 4, pp. 503–511, Apr. 2000.

- [4] T. EL-Zomor, E. A. Soliman, and S. A. Mahmoud, "Reconfigurable baseband chain for Software-Defined Radio receivers," in *Proc. Int. Conf. Microelectronics*, 2009, pp. 276–279.

- [5] A. Jiraseree-amornkun, A. Woraphishet, E.A.M. Klumperink, B. Nauta, and W. Surakampontorn, "Theoretical Analysis of Highly Linear Tunable Filters using Switched-Resistor Technique," *IEEE Trans. on Circuits Syst. I*, vol. 55, no. 11, pp.1508-1514, Dec. 2008.

- [6] S. D'Amico, V. Gianini, and A. Baschirotto, "A 4th-Order Active-Gm-RC Reconfigurable (UMTS/WLAN) Filter," *IEEE J. Solid-State Circuits*, vol. 41, no. 7, pp. 1630–1637, Jul. 2006.

- [7] F. Xianging, Z. Lei, and Z. Chisheng, "An Active-gm-RC Structured CMOS Analog Filter with Time Constant Auto-Tuning," in *Proc. Int. Wireless Commu. Networking and Mobile Computing*, 2010, pp. 1–4.

- [8] A. Jiraseree-amornkun and W. Surakampontorn, "Low-power fine-tuning switchedresistor reconfigurable filter," in *Proc. IEEE Symp. Circuits Syst.*, Melbourne, Australia, June 2014, pp. 2101–2104.

- [9] B. Razavi, "Design of Analog CMOS Integrated Circuit" Los Angeles: University of California, 2001.

## Output จากโครงการวิจัยที่ได้รับทุนจาก สกว.

1. ผลงานตีพิมพ์ในวารสารวิชาการนานาชาติ

จะได้ทำการส่งต้นฉบับบทความ ชื่อ "Low-Power Fine-Tuning Biquadratic Low-Pass Filters using Switched-Resistor Techniques" ไปยังวารสาร Microelectronics Journal

- 2. การนำผลงานวิจัยไปใช้ประโยชน์

- เชิงวิชาการ องค์ความรู้ที่ได้จากงานวิจัยในโครงการนี้ ได้ถูกนำไปถ่ายทอดในการเรียน การสอนวิชาการออกแบบวงจรรวมเชิงแอนะล็อก และมีการบรรยายให้บุคคลทั่วไปผู้สนใจ ด้านการออกแบบวงจรรวมและวงจรกรองสัญญาณ

- 3. อื่นๆ คือผลงานตีพิมพ์ในที่ประชุมวิชาการระดับนานาชาติ ดังนี้

- A. Jiraseree-amornkun and W. Surakampontorn, "Low-power fine-tuning switchedresistor reconfigurable filter," in Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS 2014), Melbourne, Australia, June 2014, pp. 2101 – 2104.