# รายงานใจัยฉบับสมบูรณ์

โครงการการออกแบบวงจรที่ใช้พลังงานต่ำมากโดยใช้ซึมอลในยานต่ำกว่า แรงตันขีดเริ่มและมอสเฟทแบบเกทลอยสำหรับอุปกรณ์ชีวการแพทย์

Micropower circuit designs for Biomedical Applications using Subthreshold CMOS and Floating-gate MOSFET

Ton

ผศ ดร.จิตรเกษม งามนิล มหาวิทยาลัยเทคโนโลยีมหานคร กฤษณพงศ์ นันทศรี มหาวิทยาลัยเทคโนโลยีมหานคร กรณิการ์ มูลไพธิ์ มหาวิทยาลัยเทคโนโลยีมหานคร

บันวาคม 2546

# รายงานวิจัยฉบับสมบูรณ์

โครงการการออกแบบวงจรที่ใช้พลังงานต่ำมากโดยใช้ซีมอสในย่านด่ำกว่า แรงดันขีดเริ่มและมอสเฟทแบบเกทลอยสำหรับอุปกรณ์ชีวการแพทย์

Micropower circuit designs for Biomedical Applications using Subthreshold CMOS and Floating-gate MOSFET

โดย

ผศ.ดร.จิตรเกษม งามนิล มหาวิทยาลัยเทคโนโลยีมหานคร กฤษณพงศ์ นันทศรี มหาวิทยาลัยเทคโนโลยีมหานคร กรณิการ์ มูลไพธิ์ มหาวิทยาลัยเทคโนโลยีมหานคร

ชันวาคม 2546

สัญญาเลขที่ PDF/42/2542

รายงานวิจัยฉบับสมบูรณ์

โครงการการออกแบบวงจรที่ใช้พลังงานต่ำมากโดยใช้ซีมอสในย่านต่ำกว่า แรงตันขีดเริ่มและมอสเฟทแบบเกทลอยสำหรับอุปกรณ์ชีวการแพทย์

Micropower circuit designs for Biomedical Applications using Subthreshold CMOS and Floating-gate MOSFET

โดย

ผศ.ดร.จิตรเกษม งามนิล มหาวิทยาลัยเทคโนโลยีมหานคร กฤษณพงศ์ นันทศรี มหาวิทยาลัยเทคโนโลยีมหานคร กรณีการ์ มูลโพซิ์ มหาวิทยาลัยเทคโนโลยีมหานคร

สนับสนุนโดยสำนักงานกองทุนสนับสนุนการวิจัย

# กิดติกรรมประกาศ

โครงการวิจัยการออกแบบวงจรอิเล็กทรอนิกส์ที่ใช้พลังงานส่ามากโดยใช้ซีมอสในย่านค่ำกว่า แรงคันชีดเริ่มและมอสเฟทแบบเกทลอยสำหรับอุปกรณ์ชีวการแพทย์นี้ ได้รับทุนสนับสนุนการ วิจัยจากสำนักงานกองทุนสนับสนุนการวิจัย สัญญาเลขที่ PDF/42/2542 และได้รับการสนับสนุน อุปกรณ์และเครื่องมือการทดลองจากมหาวิทยาลัยเทคโนโลยีมหานคร คณะผู้วิจัยขอบพระคุณ เป็นอย่างสูงมา ณ โอกาสนี้ รหัสโครงการ PDF/42/2542

ชื่อโครงการ การออกแบบวงจรที่ใช้พลังงานดำมากโดยใช้ขีมอสในย่านดำกว่าแรงดันชีดเริ่ม และมอสเฟทแบบเกทลอยลำหรับอุปกรณ์ชีวการแพทย์

ชื่อนักวิจัยและสถาบัน ผศ.ดร.จิดรเกษม งามนิล มหาวิทยาลัยเทคโนโลยีมหานคร

กฤษณพงศ์ นั้นทศรี

มหาวิทยาลัยเทคในโลยีมหานคร

กรณิการ์ มูลโพธิ์

มหาวิทยาลัยเทคโนโลยีมหานคร

อีเมล์ jitkasam@mut.ac.th

วงจรอิเล็กทรอนิกส์ที่ใช้พลังงานค่ำมากหมายถึงวงจรที่มีอัตราการใช้พลังงานในระดับ ใมโครวัตต์ ซึ่งเป็นการกำหนดว่าวงจรใดๆ ที่ใช้แหล่งจ่ายไฟมากกว่าหนึ่งโวลด์จะสามารถใช้ กระแสไบอัสให้แก่อุปกรณ์ทรานซิสเตอร์ใต้ในระดับพิโคหรือนาโนแอมแปร์เท่านั้น หรือสามารถ ใช้กระแสไบอัสได้ในระดับไมโครแอมแปร์ถ้าวงจรนั้นๆ ใช้แหล่งจ่ายไฟประมาณหนึ่งไวลด์ หรือ ในอีกทางหนึ่งคือการออกแบบวงจรให้มีจำนวนกิ่งที่ต่ออยู่ระหว่างแหล่งจำยไฟเป็นจำนวนน้อย ที่สุดเท่าที่จะทำใต้ เพื่อให้สามารถบรรลูเป้าประสงค์นี้ เราสามารถออกแบบวงจรโดยใช้อุปกรณ์ ชีมอสในย่านท่ำกว่าแรงต้นขีดเริ่มและมอสเฟทแบบเกตลอยจากเทคโนโลยีแบบชีมอสใน ปัจจุบัน โดยเฉพาะอุปกรณ์มอลเฟดแบบเกดลอยบนเทคโนโลยีซีมอสมารดฐานที่มีชั้นสารโพลี สองชั้นนั้น สามารถอำนวยให้นักออกแบบสร้างสรรค์วงจรไหม่ ๆ เพื่อการประยุกต์ใช้งานในด้าน วงจรแรงตันต่ำและใช้พลังงานต่ำมาก วงจรประมวลผลข้อมูลแบบอนาลอกและอื่นๆ งานวิจัยนี้ ใต้ทำการรวบรวมความรู้พื้นฐานเกี่ยวกับอุปกรณ์มอสเฟตแบบเกตลอยใต้แก่ คุณสมบัติหลัก คุณลักษณะในการทำงานและแบบจำลองทั้งทางคณิตศาสตร์และทางการจำลองการทำงานโดย โปรแกรมจำลองการทำงานวงจรอีเล็กทรอนิกส์ นอกจากนี้ ยังใต้นำเสนอการออกแบบวงจร ประมวลผลสัญญาณเชิงอนาลอกพื้นฐานอีกหลายวงจรเพื่อการนำไปประยุกต์ใช้งานทางด้าน ระบบชีวการแพทย์ อาที วงจรเลียนแบบการทำงานของเขลและอวัยระ การปรับปรุงสัญญาณ และการเชื่อมต่อกับอุปกรณ์ตรวจจับต่างๆ

คำหลัก แรงดันค่ำ พลังงานค่ำ พลังงานค่ำมาก มอสเฟตแบบเกตลอย การประมวลผล สัญญาณเชิงอนาลอก วงจรในใหมดกระแส

#### Abstract

Project Code; PDF/42/2542

Project Title: Micropower circuit designs for Biomedical Applications using

Subthreshold CMOS and Floating-gate MOSFET

Investigator: Jitkasame Ngarmnil, Mahanakom University of Technology

Krissanapong Nundhasri, Mahanakorn University of Technology

Komika Moolpho, Mahanakom University of Technology

Email Address: jitkasam@mut.ac.th

Project Period: 4 years

The term 'Micropower' defines a class of circuits with power consumption in micro watts level. It implies that the bias current level must be between the level of pico and nano Amp for circuit operation above 1V power supply or the bias current level can also be in the range of micro Amp for circuit operation around 1V power supply. The other mean is to design circuits with as less as possible the branches drawing current from the supply rails. In state of the art CMOS technologies, weak inverted MOSFET and Floating-gate MOSFET allow circuit designers to achieve the goals. The Floating-gate MOSFET or FGMOS on a standard double-poly CMOS offers various new useful functions which can be used to create many novel circuits such as low voltage low power circuits, analogue computational circuits and etc. This research gives a review of the FGMOS such as the principle properties, characteristics and modeling for simulations. Several analog signal processing building blocks have been proposed. They are very useful to applications in biomedical systems such as biologically inspired circuits, signal conditioning and sensor interfacing.

Keywords: Low voltage, Low power, Micropower, Floating-gate MOSFET, Analog signal processing, Current-mode circuit

# Contents

|     | 15                                                       | PAGE |

|-----|----------------------------------------------------------|------|

| 1.  | INTRODUCTION                                             | 3    |

| 2.  | FLOATING GATE MOSFET                                     | 5    |

| 3.  | FGMOS DEVICE AND MODELING                                | 9    |

| 4.  | HYSTERESIS ANALOG FGMOS COMPARATOR                       | 16   |

| 5.  | DIGITAL FGMOS COMPARATOR                                 | 27   |

| 6.  | FGMOS COMPARATOR ON CLASS-D POWER AMPLIFIER              | 34   |

| 7.  | A LOW-VOLTAGE WIDE-SWING FGMOS CURRENT AMPLIFIER         | 42   |

| 8.  | A LOW-VOLTAGE WIDE-SWING HIGH PRECISION CURRENT CONVEYOR | 49   |

| 9.  | A HIGH SPEED LOW INPUT CURRENT LOW VOLTAGE CMOS CURRENT  |      |

|     | COMPARATOR                                               | 57   |

| 10. | CONCLUSIONS                                              | 65   |

| 11. | REFERENCES                                               | 68   |

#### 1. INTRODUCTION

Nowadays, Low power and Low voltage circuits are significantly demanded by the market of portable devices and applications. Together with the further device shrinking of new coming commercial CMOS technologies, the continuously down scaling of supply voltage is obviously inevitably in modern microelectronic environments. In the contrary, performances and capabilities of electronic systems have never been scaled down. System complexities are increasing significantly every year. Design caution has then been seriously given to the management of power consumption. Currently, most computational systems are performed digitally and based on applications of microcomputers where high speed and high complexity functions have little been considered to optimize power consumption and complexity. Excessive resources and devices have been provided to achieve the required speed and complexity functions. Hence the higher the component counts the higher the power consumption. In biomedical applications where electronic circuits are operated by battery cells and sometimes used intact with or inner human body, power consumption must be limited in order to prolong the battery life and to require very less battery changing, while the speed and system functionalities are still the main requirement. In this case, analog circuits and systems are a good candidate, having a high potential to achieve a high complexity and high computational capability with less power consumption than in digital systems, In this case, Floating-gate MOSFET devices (FGMOS) will play an important role in performing low power analog signal processing because the FGMOS devices have multiple gate terminals which enable the MOSFET to theoretically compute multiple signals at a time. However, this goal can only be achieved in conjunction with a support of new circuit techniques and structures.

In early days, FGMOS devices have been used in digital circuits as storage devices. Currently, FGMOS devices receive a widespread use as a data storage element in commercial EPROM and EEPROM circuits that are typical examples where data are stored in a form of charge on the floating-gates. The devices have been proven to be very efficient in binary information storage because of ease in programming as well as the long-term charge retention. In the present binary data processing, information storing is achieved by effectively depositing on or removing off the charges on the floating-gate. Today, the device has been proved to be very reliable and very compact integration as indicated by the commercial manufacturing of megabit

flash memory. In the last decade while FGMOS devices played very important roles in Memories, FGMOS transistors had received little attention as analog circuit elements. However, during the transition of the new decade, there have been many applications of these devices in analog circuits based on their unique characteristics of the variable threshold voltage. In other words, the threshold voltage is programmable. As the trend of integrated circuits moves toward low voltage applications, the floating-gate MOSFET is now very useful in analog integrated circuits and signal processing applications. In reduced power supply voltage, FGMOS transistor with programmable threshold voltage can then be used with reduced effective threshold voltage and hence the smaller required gate-source voltage. The floating-gate transistors can also be used in analog circuit trimming of which the advantage over traditional fuse trimming technologies is that the trimming is reversible if drift in the circuit occurs. There are also other applications, such as input offset trimming of differential pairs, low voltage op-amp with floating-gate input stages, D/A [1], electronic programming [2,3], multiple input Op-Amp [4], low-voltage operation [5], circuit trimming [6], neural network [7] and four-quadrant analog multiplier [8,9].

At the beginning of this report, reviews and basic principle of the FGMOS devices are introduced in Section 2, where the fundamental and literature reviews from previous reported works are summarized to give an overview of Floating-gate devices, circuits and systems.

In Section 3, Floating-gate devices and modeling are addressed including a physical structure of floating-gate device, capacitive models, mathematical and macro models for SPICE simulations including some simulation results.

In Section 4, a novel Hysteresis Tunable Voltage Comparator is presented. The circuit is basically a simple voltage comparator embedded with a positive feedback scheme to create the hysteresis. In this work, two FGMOS devices are employed to perform the feedback where one of the control gate voltages is used to tune an amount of the feedback current to the input devices. As a result, the trip voltages; V<sub>TRP</sub>, and V<sub>TRP</sub>, of the comparator can be tuned electronically. The proposed idea is demonstrated on a standard double-poly CMOS processes. Since the design normally incorporates with layout of the FGMOS in order to get the value of the gate capacitances effectively. Magic Program is used to create the layouts on AMI 1.2µm CMOS process available

through MOSIS. Simulation results from HSPICE are given to demonstrate the functionality.

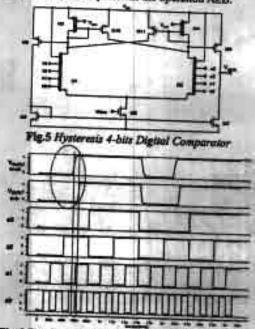

In section 5, Digital comparators using FGMOS devices are proposed here as another version of comparator for digital domain. The comparators use FGMOS devices as an input stage to create a 4-bit digital comparator based on classical analog voltage comparator. Two types of the 4-bit digital comparator are explained in this section, a normal 4-bit comparator and a regenerative 4-bit comparator. Based on the two type comparators, an 8-bit digital comparator is also presented. Simulation results verifying the functionality of the proposed comparators are demonstrated.

In section 6, an application of the multiple-input FGMOS comparator is also proposed in this section as a design of Class-D amplifier. Based on the used of the proposed comparators, the amplifiers have a simple architecture and are easy to be integrated with other circuit blocks on a chip scale system level. This amplifier exploits the proposed multiple-inputs FGMOS voltage comparators.

In Section 7, a new low voltage current amplifier is proposed. The circuit is totally formed in the class AB structure, utilizing CMOS inverters and the recently proposed additive analog inverter using floating-gate MOSFETs. Operating in a negative feedback topology, the amplifier can deal with wide signal swings up to  $\pm 200 \mu A$ , with 1% of the THD and 10pF of C<sub>L</sub>. Designs and HSPICE simulation results are demonstrated on 0.5 $\mu$ m double poly CMOS processes with 1.5V and 1V power supplies to indicate high frequency and low power capabilities respectively.

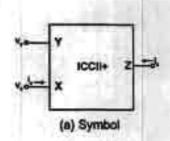

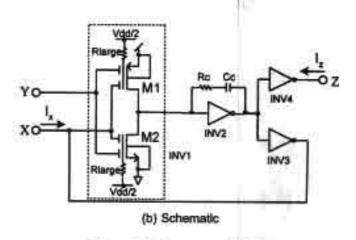

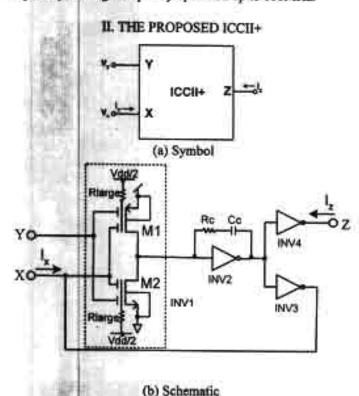

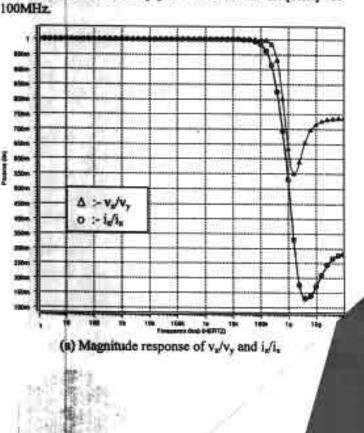

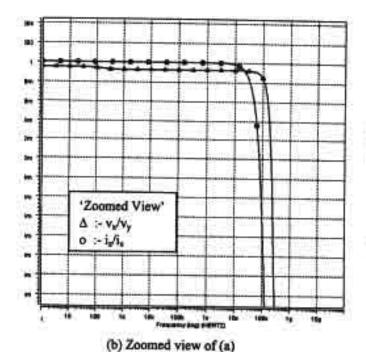

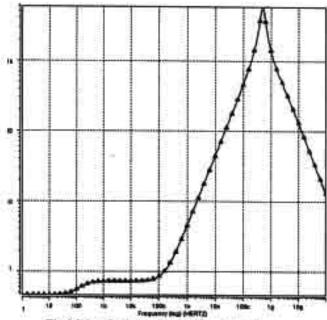

In Section 8, a low voltage inverting second generation current conveyor is proposed. The circuit can be operated up to a 100MHz with ±0.75V power supply. The circuit is formed in class AB structure using CMOS inverters and a pseudo floating-gate MOSFETs additive analog inverter facilitating a negative feedback loop to regulate accurate signal tracking of the terminal voltage X to Y and the terminal current Z to X. Simulation results on 0.5µm double poly CMOS processes confirm high precision conveying features, wide signal swing and low voltage capabilities of the current conveyor.

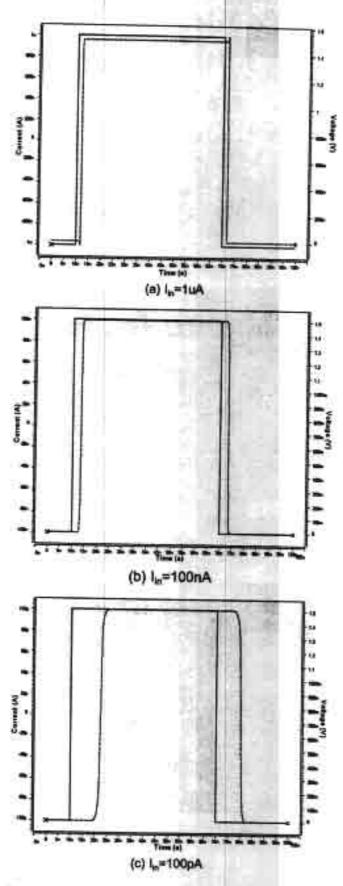

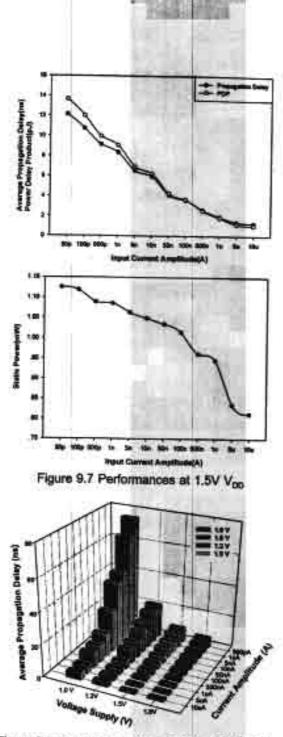

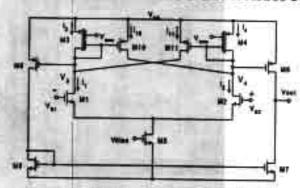

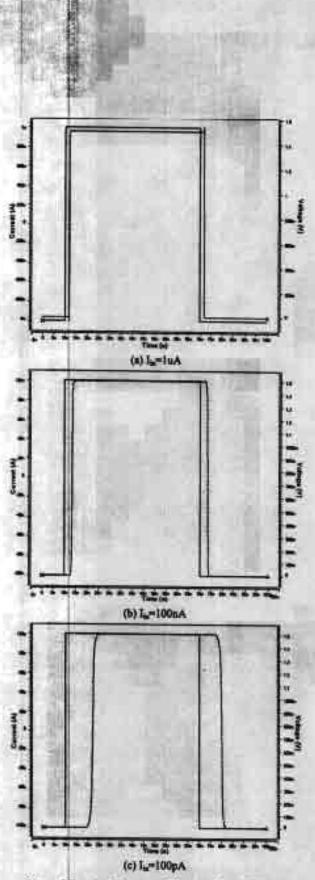

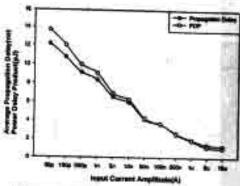

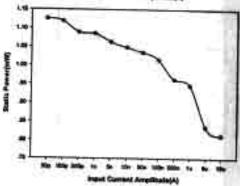

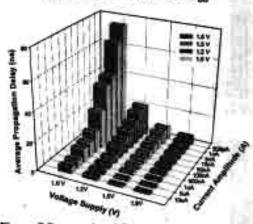

In section 9, a new high speed low input current comparator is proposed in this section. Based on a simple negative feedback scheme around the transimpedance stage with an emphasis on a very large loop-gain, the transformed voltage signal is

maintained at the lowest swing that results in a speed improvement. On a 0.25um TSMC CMOS process, simulation results demonstrate propagation delays of 3.6ns with  $\pm$ 100nA input current and 1.5Volts power supply, while the smallest input current is  $\pm$ 50pA. Performances are also shown with other  $V_{DO}$  such as 1.0, 1.8 Volts.

Finally, conclusions and suggestions for future improvements are discussed in Section 10.

### 2. FLOATING GATE MOSFET

Floating-gate MOSFET abbreviated as FGMOS is a device on standard doublepoly CMOS processes. It offers various new useful functions which can be used to create many novel circuits such as low voltage low power circuits, analogue computational circuits etc. This section gives a review of FGMOS and also includes some of examples from earlier reported works as a background understanding for this device

## 2.1 LITERATURE REVIEWS: INITIAL WORKS ON FLOATING-GATE CIRCUITS

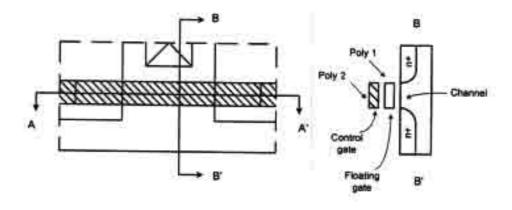

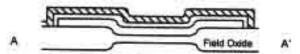

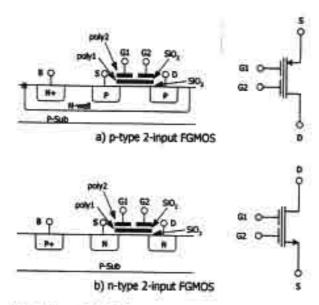

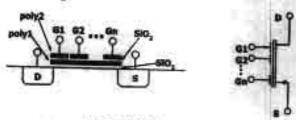

Floating-gate MOSFET (FGMOS) structure has been invented for a long time since 1967 by Kahng and Sze [10]. Until now FGMOS is widely use for many famous nonvolatile digital storage device such as EPROMs, EEPROMs and flash EPROMs. The floating-gate structure has a unique structure different from a conventional MOSFET. The gate of FGMOS is composed of two layers; poly1 and poly2, as shown in Fig.2.1. The gate on poly1 is basically a conventional gate of MOSFETs but it is completely encased in an insulator made of Silicon Dioxide (SiO2). Since SiO2 is a very good isolator, so this electrode has no direct electrical connection to any other electrical conductor, then it is often referred to as "floating-gate". The other adjacent gate conductor plate made of poly2 is an input gate which is a capacitive coupling terminal to the floating-gate. Potential at the input gate can be coupled to modulate the potential on the floating-gate which then controls the current flow in the channel of the MOSFET. If electrons are trapped inside the floating-gate, they cannot leak out due to the property of the oxide. Changing the number of electrons on the floating-gate means alter this potential. In memory applications, altering the logic output by changing the number of charge on the floating-gate is referred to as "writing" to the memory device and the state can be maintained for more than 10 years without an effect during read cycle. After the invention of FGMOS device in 1967, there are many researchers working to develop the device as shown in growth vs. year of developments in Fig.2.2

Figure 2.1 Top view and cross-section views through a typical EPROM

Figure 2.2 Development of floating-gate [11]

The current interest in floating-gate circuits started from developing large-scale computations in neuromorphic systems [11]. The introduction of the ETANN chip by Intel in 1989 showed the potential of using floating-gate devices for applications other than digital memory elements [12]. The core of the chip's function was an analog vector-matrix calculation employing a floating-gate array of 10240 analog matrix elements. This floating-gate device developed in a specialized EEPROM fabrication process, were used as an analog floating-gate memory. The chip has an impressive computational ability but the production cost of this chip cause it receiving less interests.

After Intel's invention chip, a new functional transistor had been proposed in 1992, which worked more intelligently than a mere switching device by Shibata and Ohmi [14]. This transistor can calculate the weighted sum of all input signals at the gate level, and controls the "on" and "off" of the transistor based on the result of such a

weighted sum calculation of all input gate potentials. Since the function is quite analogous to that of a biological neuron, the new transistor is called "a neuron MOSFET" or "neuMOS" (abbreviated as VMOS) in short. The device as shown in Fig.2.3 is composed of a floating-gate and multiples of input gates that introduce the capacitive coupling effect for the weight sum calculation. There is essentially no power dissipation occurs in the calculation mechanism, making the device ideal for ULSI implementation that need less power consumption as possible.

Figure 2.3 Simplified 2-input FGMOS structure and symbol (a) p-type (b) n-type MOS

Three research group accomplishments laid the groundwork for most of the current floating-gate circuit developments. The earlier accomplishments could be defined into three approaches of using the FGMOS devices as follows.

- 1) Thomsen and Brook [13] demonstration and use of electron tunneling in a standard CMOS double-poly process allowed many researchers to investigate and to exploit floating-gate circuit concepts without requiring accessing to specialized fabrication process. This research works laid a new approach to accurately control the amount of charge on the floating gate. As a result, it led to later developments and researches in analog memory [2, 3].

- 2) The VMOS approached by Shibata and Ohmi [14] provided the initial inspiration and framework to use capacitors for linear computations that using multiple input FGMOS to compute analog information. These researchers concentrated on the floating-gate circuit properties instead of the device properties, and used either ultra-

violet (UV) light to equalize charge, or simulated floating-gate elements by opening and closing MOSFET switches. Today many researchers work on computational systems with the floating-gate devices that were firstly established by Shibata and Ohmi. The way of thinking about FGMOS transistors introduced by Shibata and Ohmi has resulted in a number of interesting analog and digital information-processing circuits [1, 4, 8, 9, 16, 17, 18, 21-27], including a multiple-input floating-gate differential amplifier, a four-quadrant floating-gate multiplier, simple D/A converters, Translinear circuits and etc.

3) Carver Mead's adaptive retina [15] gave the first example of using continuously operating floating-gate programming/erasing techniques, as the backbone of an adaptive circuit technology. The works led to the later developments and implementations of adaptive circuits in neuron network [19, 20].

## 2.2 OUTSTANDING PROPERTIES OF FGMOS DEVICE

FGMOS device is basically a multiple-input device of which the main properties can be very useful for analog and digital computational circuits. It has unique and attractive characteristics of which the most important properties to be applied in this research and report are as follows:

- As a multiple-input gate device, the voltage appears at the floating gate is a linear summation of its input voltage at all input terminals. This characteristic makes the device suitable for analog computation.

- 2) The effective threshold voltage (V<sub>th</sub>) seen at the input gate is tunable.

These two phenomena are very attractive to analog designers. The first feature of the multiple-input gates allows analog designers to design a novel or to adapt many existing circuits to work with more complexity function without adding power consumption, while the second feature allows FGMOS devices to be operated at a very low the supply voltage as a result of the threshold voltage tunability. Both low voltage and low power operations are the most important requirement for biomedical applications.

#### 3. FGMOS DEVICE AND MODELING

Floating gate MOSFET has many impressive characteristics that can be used to design a novel circuit or to enhance exist analog circuits for additional special features such as very low power, low voltage. With the available FGMOS device, one can put a new function into the present circuits. However, one problem that can cause trouble to designers is how to design and simulate an FGMOS circuit in the conventional simulation programs. This section describes a basis of floating gate structure, modeling and simulate macro models that are essential to design and simulation of FGMOS circuits. Threshold voltage shifting and weight summation characteristics of FGMOS are demonstrated by simulation results.

#### 3.1 DEVICE STRUCTURES AND THEORY

Many applications using multiple-input floating-gate transistors in analog circuits have been reported over the last few years, based on the main properties that make these devices attractive for analog applications as follows.

- The long-term retention characteristic of the charge injected into the floatinggate features analog memory, which are very useful applications for DC offset trimming, neural networks for weight storage and etc.

- The simple implementation of linear weighted voltage addition is performed by only one FGMOS device.

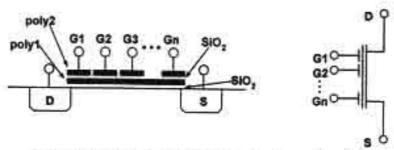

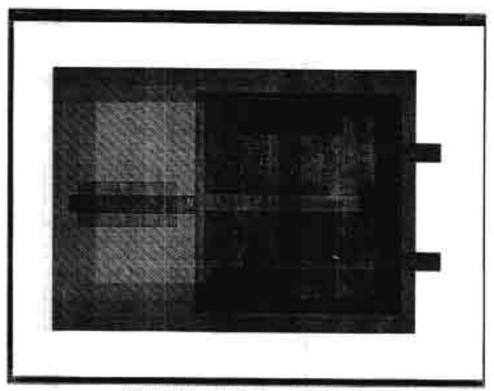

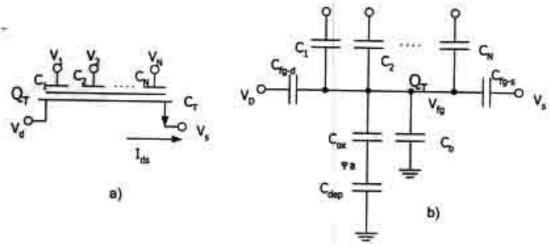

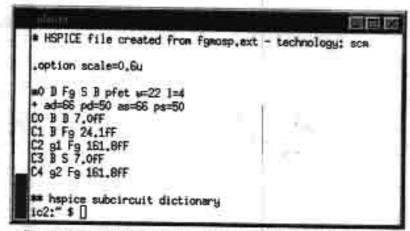

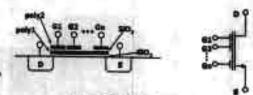

Normally, these operations require relatively complex circuitry when using conventional MOS or bipolar devices but they are performed by only one FGMOS device. However, a practical problem with a multiple-input floating-gate device is that all circuit simulators consider capacitor as an open circuit for DC analysis and for this reason there is obviously a DC convergence problem with the floating-gate nodes, if the conventional MOSFET model and capacitors are used straightforwardly. Consider the floating-gate transistor represented Fig.3.1, of which the practical layout is given in Fig.3.2. The equivalent circuit of this device including capacitors between each of the inputs and the floating gate (denoted as poly1-poly2 capacitors) has shown in Fig.3.3. These capacitors are labeled C<sub>1</sub>, C<sub>2</sub>, ..., C<sub>n</sub>. The conventional gate-source and gate-drain capacitances are labeled C<sub>1ga</sub> and C<sub>1ga</sub> respectively. For example, if we assume a FGMOS device with only two input gates, the extract netlist of the layout will be derived as shown in Fig.3.4, in which we can see that there is only one conventional MOSFET

and five capacitors denoted as C<sub>0</sub> to C<sub>4</sub>. C<sub>2</sub> and C<sub>4</sub> are input coupling capacitors between the input gate g1 and g2 to the floating-gate node respectively. It is noted that floating-gate node is floating for the time being and can not be used for simulation directly although the netlist has been extracted from the correct layout. It is concluded that the conventional equivalent circuit and netlist always lead to DC convergence problems in DC analysis of the simulator as a result of the floating node. There is a need to modify the extracted netlist in order to provide a DC path to the floating node with affecting the circuit behavior. This will allow a successful simulation of the extracted netlist.

Figure 3.1 Multiple-input floating-gate structure and symbol

Figure 3.2 Layout of two-input floating-gate

Figure 3.3 Multiple-input FGMOS a) symbol, b) capacitive model

Figure 3.4 Extraction of layout of two-input floating-gate in Fig.3.2

## 3.2 MODELING OF MULTIPLE INPUT FLOATING-GATE MOSFET

The basic structure of the FGMOS transistor is shown in Fig.3.2. It consists of a MOS transistor with a floating-gate (1<sup>st</sup> polysilicon layer) over the channel and in some cases extending over to the field oxide area. Array of control gates (multiple input gates) are formed by the  $2^{nd}$  polysilicon layer over the  $1^{st}$  polysilicon which is the same layer with the floating-gate. The capacitive couplings between the multiple input gates and floating-gate and the channel are shown in Fig.3.3(b) while Fig.3.3(a) is a symbolic representation of such the device. At the floating-gate node, total charge must be conserved [28-30] and the stored charge in the floating-gate,  $Q_T$ , is

$$Q_{T} = \left(\sum_{i=1}^{n} -C_{i}(V_{i} - V_{FG})\right) - C_{FD}(V_{D} - V_{FG}) - C_{FS}(V_{S} - V_{FG}) - C_{FS}(V_{B} - V_{FG}) - Q_{ch}(3.1)$$

where  $C_i$  is the capacitance between the floating-gate and each of the  $i^{th}$  input gate.  $V_i$  is the  $i^{th}$  input voltage.  $V_{FG}$ ,  $V_D$ ,  $V_S$  and  $V_B$  are the floating-gate, drain, and

substrate voltages, respectively.  $C_{FD}$ .  $C_{FS}$ , and  $C_{FB}$  are the overlap capacitances between the floating-gate and drain, source, and bulk, respectively.

Now  $Q_{ch}$  is the total channel charge obtained by integration of the channel charge per unit area,  $Q_n(y)$ , along the channel and can be given as (3.2) [30, 31].

$$Q_{n}(y) = -\frac{C_{OX}}{WL} (V_{PG} - V_{T}^{*} - V_{V}(y) + V_{S})$$

(3.2)

where y is the distance along the channel,  $V_{\rm ch}(y)$  is the voltage along the channel,  $C_{\rm cox}$  is the floating-gate gate oxide capacitance, and  $V_{\rm f}^{\star}$  is the threshold voltage seen from the floating-gate. The variation of depletion charge along the channel is neglected by using only its value at the source. Hence, by taking the integral of (3.2) and substituting  $Q_{\rm ch}$  into (3.1), the equation for the drain current of the FGMOS transistor in saturation is obtained.

$$I_{d} = \frac{1}{2} K \left[ \frac{Q_{T}}{C_{T}} + \frac{\sum_{i=1}^{n} C_{i} V_{i}}{C_{T}} + \frac{C_{FD} V_{D}}{C_{T}} + \frac{C_{FB}}{C_{T}} V_{d} - V_{d} \times \left[ 1 + \left( \frac{C_{FB}}{C_{T}} + \frac{2C_{OX}}{3C_{T}} \right) \right] - \left( 1 - \frac{2C_{OX}}{3C_{T}} \right) V_{T}^{*} \right]^{2}$$

$$(3.3)$$

where  $K = \mu_n \left( C_{OX} / L^2 \right)$  is the transconductance parameter,  $\mu_n$  is the electron mobility, and L is the channel length.  $C_T$  is the total capacitance associated with the floating-gate, which is given by

$$C_{T} = \frac{2}{3}C_{OX} + C_{FD} + C_{FS} + C_{FS} + \sum_{i=1}^{n} C_{i}$$

(3.4)

With UV illumination after fabrication, zero initial stored charge on the floating-gate can be assumed, neglecting charge injection during device operation, and assuming  $C_{FD}$  is much less than  $C_{\tau}$ , (3.3) can be simplified to the following form.

$$I_d = \frac{1}{2} K \left( \sum_{i=1}^{n} w_i V_i + w_B V_B - w_S V_S - w_T V_T^* \right)^2$$

(3.5)

where the capacitive coupling ratios are defined as  $w_i = \left(\frac{C_i}{C_T}\right)$ ,  $w_B = \left(\frac{C_{PB}}{C_T}\right)$ ,

$$w_S = \left[1 - \left(\frac{C_{PS}}{C_T}\right) - \frac{2C_{OX}}{3C_T}\right], \quad w_T = 1 - \frac{2C_{OX}}{3C_T}$$

. Equation (3.5) shows that the FGMOS

transistor drain current in saturation is proportional to the square of the weighted sum of the input voltage signals, where the weight of each input signal is determined by the capacitive coupling ratio of the input to the total capacitance around the floating-gate area. Hence, the squaring operation on the two signals is inherently performed in the FGMOS transistor. From (3.5), the drain current of a multiple input floating gate MOSFET, can be rearranged as (3.6) and (3.7).

$$I_d = \frac{1}{2} \mu C_{OX} \frac{W}{L} [(w_1 V_{G1} - V_S) - (V_{TH} - w_2 V_{G2})]^2$$

(3.6)

$$I_d = \frac{1}{2} \mu C_{OX} \frac{W}{L} [(w_1 V_{G1} + ... + w_n V_{Gn}) - V_S - V_{TH}]^2$$

(3.7)

The drain current is essentially a linear sum voltage of all inputs weighted by the capacitive coupling ratios. Equation (3.6) is arranged to show the threshold tuning operation with only two input gates are assumed. It is seen that  $V_{G1}$  can be utilized as a signal port while  $V_{G2}$  is used to tune the effective threshold voltage seen from the input G1. Equation (3.7) is written to show a linear sum of the weighted multiple-input voltages. The two characteristics will be exploited in this work.

Equation (3.5) can be used to derive an equivalent circuit that allows calculation of a DC operating point at the floating-gate node and also satisfies the charge conservation shown in (3.1). This circuit is shown in Fig.3.5. It includes the necessary additional branch with an arbitrarily large resistor  $R_G$  (1000G $\Omega$ ) and n+2 voltage sources controlled by the voltages  $V_1, V_2,...,V_s$ ,  $V_s$  and  $V_D$ . These elements are connected in series between the floating-gate and ground. The gain control factor for each voltage source corresponds to the ratio of the input voltage source corresponds to the ratio of the input capacitance associated to each control voltage over the total capacitance  $C_{\scriptscriptstyle T}$ . This branch is included in order to allow DC convergence during DC analysis of the simulation and is neglected on the AC and/or transient performance of the circuit. The equation given above assumes that the gate-source and gate-drain capacitances,  $C_{{\scriptscriptstyle FS}}$  and  $C_{{\scriptscriptstyle FD}}$ , are approximation constant. This, in practice is a good approximation if the transistor remains in triode or saturated mode, which is the case for most analog circuit applications. For the case that  $C_{FS}$ ,  $C_{FD} << C_1$ ,  $C_2$ ,...,  $C_n$ then  $C_7 \approx C_1 + C_2 + K + C_s$ , and variations in  $C_{FS}$  and  $C_{FD}$  when the transistor changes from saturations to triode mode (or to cutoff) do not cause a significant change in the gain coefficients of voltage control voltage source (VCVS:E) a1, a2,...,an. The listing of a SPICE sub-circuit for a two-input floating-gate N-channel transistor with width over length ratio W/L=25/3 and input capacitance C2=2C1=288fF is given in Table 3.1.  $C_1$  and  $C_2$  correspond to poly1-poly2 capacitors with area of  $300u^2$  and  $600u^2$ respectively.  $C_{FS}$  and  $C_{FD}$  have values of 44.5fF. They were calculated using 2um CMOS N-well technology parameters according to Co=CoxWL+CosoW, C'o=CopoW,

where Cox, Coso and Coso are the oxide capacitance density and the gate-source overlap capacitance per unit length respectively.

Figure 3.5 Macro model of multiple-input FGMOS [26]

#### Table 3.1 Multiple FGMOS sub-circuit

SUBCKT input3 B D g1 g2 g3 S

C1 fg g1 50fF

C2 fg g2 50fF

C3 fg g3 50fF

M4 D fg S B NMOS L=1u W=20u AD=66p PD=24u AS=66p PS=24u

R5 fg N9 5g

e6 N9 N5 g1 S 0.5

e7 N5 N2 g2 S 0.5

e8 S N2 S g3 0

.ENDS input3

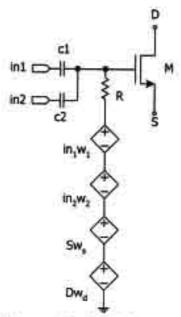

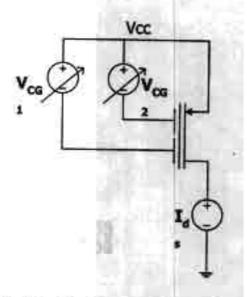

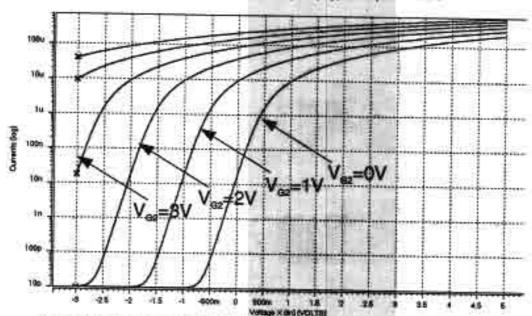

Based on the FGMOS model in (3.6), a tested circuit for the threshold voltage tuning can be shown in Fig.3.6 of which the drain current versus voltage at control gates curve of the drawn p-type 2-input FGMOS in Fig.3.2 can be demonstrated in Fig.3.7. In order to show  $V_{\rm SM}$  tuning capability, the circuit has been tested under the condition that  $V_{\rm CG2}$

is used as the threshold tuning voltage and set to 0V, 1V, 2V, ..., 5V while  $V_{G1}$  is used as an input terminal

Figure 3.6 Test circuit for DC sweep of p-type 2-input FGMOS

Figure 3.7 Simulation result of test circuit in Fig.3.6 using macro model in Fig.3.5

Regarding the drain current equation in (3.6) and (3.7), the initial stored charge on the floating-gate is assumed to be zero. The drain current equations are quite trivial. However, the stored charge is normally unpredictable. Thus before any operations in analog applications, the stored charge should be removed completely. The means in controlling the charge relating to two physical phenomena such as: hot carrier injection [31] and Fowler-Nordheim tunneling (F-N tunneling) [32]. These are the phenomena used for writing process in commercial UV-EPROMs [33], byte-alterable E<sup>2</sup>PROMs and flash EEPROMs.

## 4. HYSTERESIS ANALOG FGMOS COMPARATOR

A voltage comparator is a circuit that compares the instantaneous value of an input signal v<sub>in</sub>(t) with a reference voltage V<sub>ref</sub> and produces a logic output level depending on whether the input is targer or smaller than the reference level. The most important application for a high-speed voltage comparator occurs in and analog-to-digital converter system and etc. In this section, a design of analog voltage comparator that capable to tune window size of its hysteresis loop is presented. This comparator based on conventional analog comparator but there is a tuning capability on the ratio of positive feedback performed by multiple-input FGMOS devices. Some fundamental of the comparator are reviewed and then design and simulation results are shown in this section.

## 4.1 FUNDAMENTAL COMPARATOR

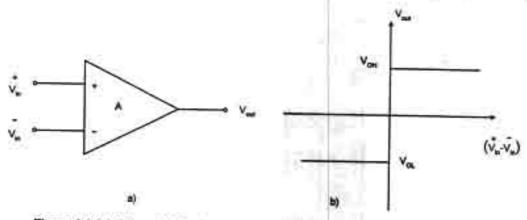

One very important and widely used comparator configuration is a high-gain differential input, single-ended output amplifier [34]. Fig.4.1 (a) shows the symbol of a differential comparator which is very similar to that of an operational amplifier. Usually, the comparator stage is followed by a latch, which is essentially a bi-stable multivibrator. The latch provides a large and fast output signal of which amplitude and waveform are independent of those of the input signal and is hence well suited for the logic circuits following the latch. If no latch is used, the output V<sub>out</sub> should have a large swing, say, 0 to +5, as the input changes from -1mV to +1mV. Thus the required gain is around 5V/2m = 2500, or 68dB. If a latch is used, V<sub>out</sub> is only needed to be higher than the combined offset and threshold voltages of the latch; this value is around 0.2V or less. Hence a gain of 200 is adequate. A comparator is therefore essentially a high-gain opamp designed for open-loop operation but it does not require frequency compensation.

Figure 4.1 (a) Differential-input comparator (b) Transfer curve of ideal comparator

The transfer curve of the ideal differential comparator is shown in Fig.4.1(b). In this figure the negative input of the comparator in Fig4.1(a) is tled to a reference voltage  $V_{\rm ref}$ . When the positive input is greater than  $V_{\rm ref}$  the output is logic high  $(V_{\rm OH})$ , and when it is less than  $V_{\rm ref}$ , the output is logic low  $(V_{\rm OL})$ . The ideal transfer curve of Fig.4.1(b) corresponds to a differential gain of infinity. In actuality the differential gain has a finite value equal to Av. Another non-ideal effect of the differential comparator is the input-referred dc transfer curve will begin changing only after the input difference exceeds  $V_{\rm off}$ . The dc transfer curve of a practical differential comparator with finite gain of Av and a dc-offset voltage of  $V_{\rm off}$  are shown in Fig.4.2 where  $V_{\rm IL}$  and  $V_{\rm IH}$  are the input excess of that required to cause the output to switch state. Finally, the speed or response time is another important parameter of a comparator. In most applications it is required that following an appropriate input level change, the comparator must switch between two output levels with fast rise and fall times in the shortest amount of time.

Figure 4.2 Transfer curve of comparator with finite gain and dc offset voltage

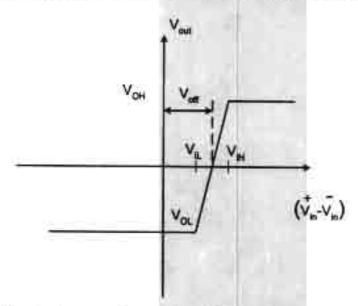

#### 4.2 COMPARATOR WITH HYSTERESIS

Hysteresis is the quality of the comparator in which the input threshold or the trip voltages change as a function of the input (or output) level. In particular, when the input passes the threshold, the output changes and the input threshold is subsequently reduced so that the input must return beyond the previous threshold before the comparator output changes its state again. This can be illustrated much clearer with the diagram shown in Fig.4.3. Notice that as the input starts negative and goes positive, the output dose not change until it reaches the positive trip point, V<sub>TRP+</sub>. Once the output

goes high, the effective trip point is changed. When the input returns in the negative direction, the output dose not switch until it reaches the negative trip point, V<sub>TRP</sub>.

Figure 4.3 Comparator Hysteresis curve

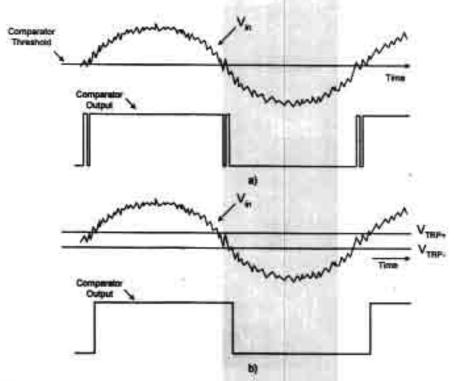

The advantage of hysteresis in a noisy environment can be clearly seen from the illustration given in Fig.4.4. In this figure, a noise signal is shown as the input to a comparator without hysteresis. The intention is to have the comparator output follow the low-frequency signal. Because of noise variations near the threshold points, the comparator output is too noisy the response of the comparator can be improved by adding hysteresis equal to or greater than the amount of the largest expected noise amplitude. The response of such a comparator is shown in Fig.4.5.

Figure 4.4 (a) Comparator response to noisy input (b) Comparator response to noisy input when hysteresis is added

#### 4.2.1 CMOS HYSTERESIS COMPARATOR

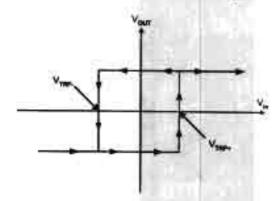

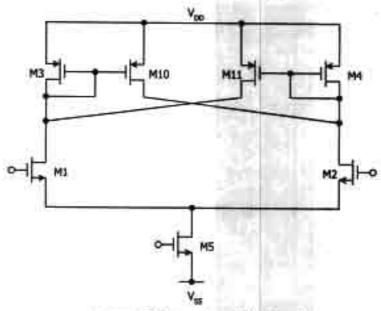

There are many ways to accomplish hysteresis in a comparator. All of them involve some from of positive feedback. Referring to the differential input stage given in Fig.4.5, it is seen that there are two paths of feedback. The first is current-series feedback through the common-source node of transistors M1 and M2. This feedback path is negative. The second path is the voltage-shunt feedback through the gate-drain connections of transistors M10 and M11. This path of feedback is positive. If the positive feedback factor is less than the negative feedback factor, then the overall feedback will be negative and there is no hysteresis. If the positive feedback factor becomes greater than the negative feedback, the overall feedback will be positive, which will give rise to hysteresis in the voltage transfer curve. As long as the ratio  $\beta_{10}/\beta_3$  is less than one, there is no hysteresis in the transfer function. When this ratio is greater than one, hysteresis will result. The following analysis will develop the equations for the trip points when there is hysteresis.

Figure 4.5 Comparator with hysteresis

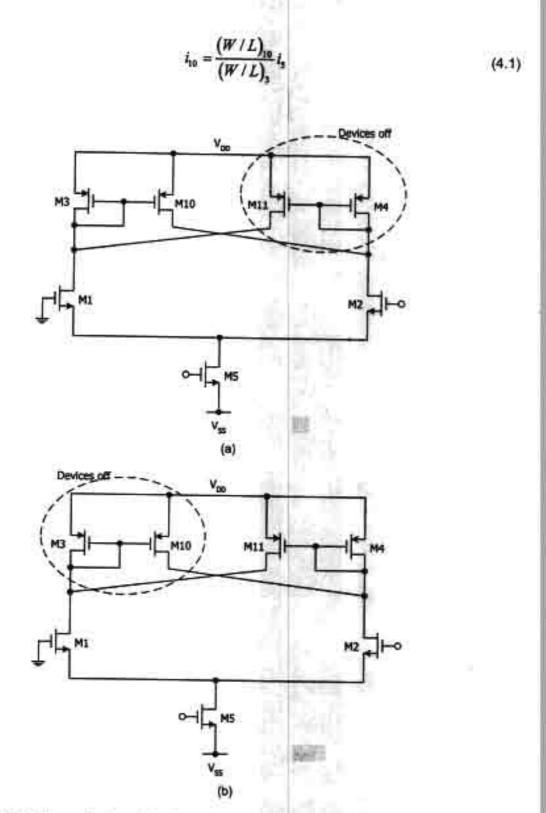

It is assumed that the plus and minus supply voltages are used and the gate of M1 is tied to ground while an input voltage signal is applied to the gate of M2. With the input of M2 of much less than zero, M1 is on and M2 off, thus turning on M3 and M10 and turning off M4 and M11. All drain current of M5 flows through M1 and M3, so the voltage at the drain of M1 is logic high. The resulting circuit is shown in Fig.4.6 (a). (Notice that, M2 is shown even though it is off.) At this point, M10 is attempting to source the following amount of current.

Figure 4.6 (a) Comparator in a state where V<sub>in</sub> is vary negative and increasing toward V<sub>TRP+</sub> (b) Comparator in a state where V<sub>in</sub> is vary positive and decreasing toward V<sub>TRP+</sub>.

As V<sub>in</sub> increases toward the threshold point, some of the tail current beginning to flow through M2 is supplied by the current of M10. As long as M10 still can supplied current to M2, there is no state switching. Just beyond this point the comparator switches state.

To approximately calculate one of the trip points, the circuit must be analyzed right at the point where the current of M2 equals to those of M10. Mathematically this is

$$i_{10} = \frac{(W/L)_{10}}{(W/L)_{3}}i_{3} \qquad (4.2)$$

$$i_2 = i_{10}$$

(4.3)

$$i_5 = i_2 + i_1$$

$(i_1 = i_2)$  (4.4)

$$i_3 = \frac{i_3}{1 + \left[ (W/L)_{10} / (W/L)_3 \right]} = i_1$$

(4.5)

$$i_2 = i_3 - i_1$$

(4.6)

Knowing the currents in both M1 and M2, It is easy to calculate their respective V<sub>gs</sub> voltage. Since the gate of M1 is at ground, the difference in their gate-source voltages will yield the positive trip point as given below

$$v_{GS1} = \left(\frac{2i_1}{\beta_1}\right)^{1/2} + V_{r_1} \tag{4.7}$$

$$v_{GS3} = \left(\frac{2I_3}{\beta_2}\right)^{1/2} + V_{T2} \qquad (4.8)$$

$$V_{TRP+} = v_{GS2} - v_{GS1} (4.9)$$

Once the threshold is reached, the comparator changes state so that the majority of the tail current now flows through M2 and M4. As a result, M11 is also turned on thus turning off M3 and M10 and M1. As in the previous case, as the input returns negative the circuit reaches a point at which the current in M1 increases until it equals the current in M11. The input voltage at this point is the negative trip point V<sub>TRP</sub>. The equivalent circuit in this state is shown in Fig.4.7 (b). To calculate the trip point, the following equations will be applied.

$$i_{11} = \frac{(W/L)_{11}}{(W/L)_4} i_4$$

(4.10)

$$\hat{i}_1 = \hat{i}_{11}$$

(4.11)

$$i_3 = i_2 + i_1$$

(4.12)

Therefore,

$$i_4 = \frac{i_5}{1 + \left[ (W/L)_{11} / (W/L)_4 \right]} = i_2$$

(4.13)

using (4.7) and (4.8) to calculate V<sub>GS</sub>, the trip point is

$$V_{TRP-} = v_{GS2} - v_{GS1} (4.15)$$

while these equations do not take into account the effect of channel length modulation.

The differential stage described so far is generally not useful alone, and thus requires an output stage to achieve reasonable voltage swings and output resistance. There are a number of ways to implement an output for this type of input stage. One of these is given in Fig.4.7. Differential-to-single-ended conversion is accomplished at the output and thus provides a class-AB type of driving capability.

Figure 4.7 Complete schematic of a CMOS comparator with hysteresis

#### 4.3 DESIGN OF HYSTERESIS TUNABLE VOLTAGE COMPARATOR

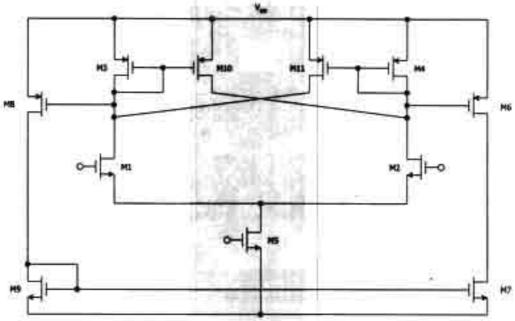

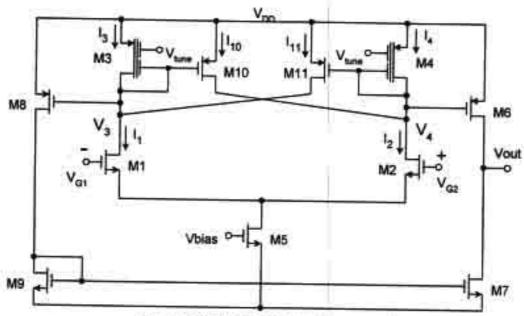

Regarding to the mentioned hysteresis mechanism, a simple hysteresis tunable analog comparator can be designed and shown in Fig.4.8 where M3 and M4 are replaced by the FGMOSs. The hysteresis involves a positive feedback produced by M10 and M11. The positive feedback occurs only when the current ratio of I<sub>10</sub>/I<sub>3</sub> is greater than one. If the ratio is higher, the amount of the feedback current will also increase and result in a wider of the positive and negative trip point voltage, V<sub>TRP+</sub> and V<sub>TRP-</sub>. Hence the hysteresis can be controlled. However, the V<sub>TRP+</sub> and V<sub>TRP-</sub> can be developed from the condition that I<sub>2</sub> equals to I<sub>10</sub> and I<sub>1</sub> equals to I<sub>11</sub>, correspondingly.

$$V_{TRP+} = \sqrt{\frac{2I_5}{\beta_1}} \left( \frac{\sqrt{I_{10}/I_3} - 1}{\sqrt{1 + I_{10}/I_3}} \right)$$

$$V_{TRP-} = \sqrt{\frac{2I_5}{\beta_1}} \left( \frac{\sqrt{I_{11}/I_4} - 1}{\sqrt{1 + I_{11}/I_4}} \right)$$

(4.16)

Figure 4.8 Hysteresis tunable analog comparator

Thus, by the virtue of the FGMOS, the ratio of  $I_{D10}/I_{D3}$  and  $I_{D11}/I_{D4}$  can be tuned electronically by  $V_{tune}$  at the input gate of M3 and M4. Hence  $V_{TRP*}$  and  $V_{TRP}$  can be tuned orthogonally. If the tuning voltage at the input gates of M3 and M4 are different. M3 and M4 are designed with an equal area of  $G_1$  and  $G_2$  as  $10.8\times22.8\mu\text{m}^2$  while the floating-gate area is set to  $13.2\times2.4~\mu\text{m}^2$ , which also equal to those of M10 and M11.

# 4.4 SIMULATION RESULTS OF HYSTERESIS TUNABLE ANALOG VOLTAGE COMPARATOR

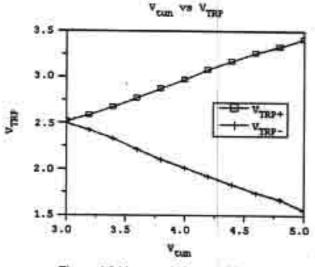

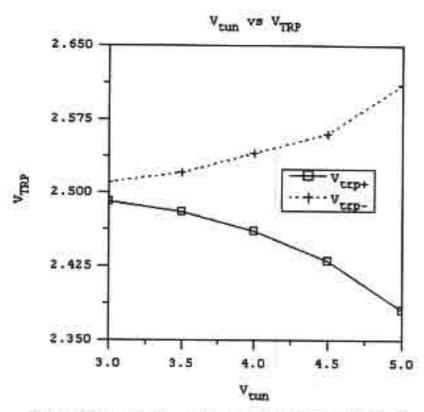

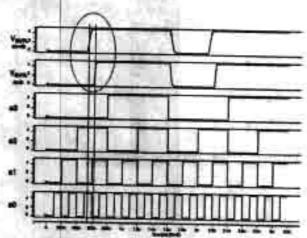

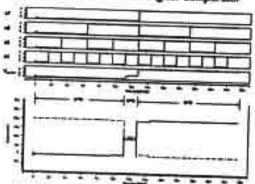

The circuit has been simulated on Hspice with an assistance of the FGMOS macro model in [22] and supply voltage is set to 5.0V. Fig.4.9 shows  $V_{TRP*}$  and  $V_{TRP*}$  vs.  $V_{tune}$  varied in the range of 2.5-5.0V,

Figure 4.9 V<sub>TRP</sub>, and V<sub>TRP</sub>, vs. V<sub>kre</sub>

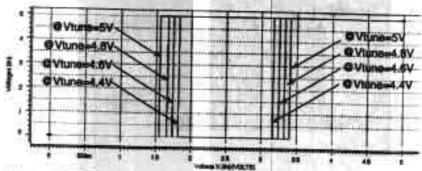

A DC transfer curve of the hysteresis tunable comparator is also shown in Fig.4.10 where the input gates G1 and G2 are tied together and connected to the tuning voltages, V<sub>tun</sub>. Fig.4.10 shows the input-output DC transfer curve with the hysteresis. V<sub>tun</sub> are varied in the range of 2.5-5.0V which correspond to V<sub>TRP+</sub> in the range of 2.5-3.4V and V<sub>TRP-</sub> in the range of 2.5V down to 1.6V.

Figure 4.10 DC transfer curve of hysteresis tunable voltage comparator

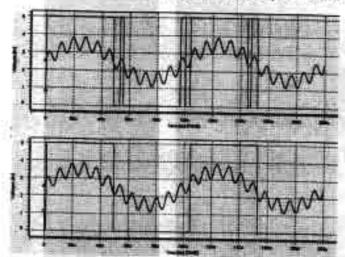

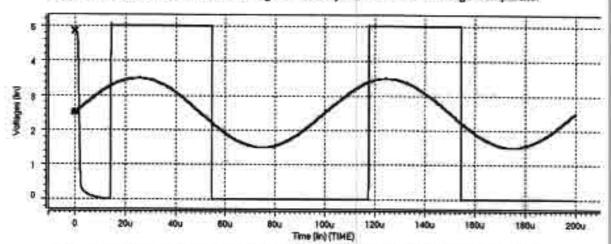

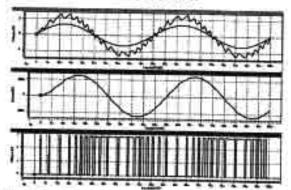

Time-domain simulation is also performed to express the performance of the comparator in a noisy environment. The circuit is tested with a noise-modulated signal with the noise amplitude set to 0.4V<sub>peak</sub> while V<sub>tune</sub> is set to 3.8V. Simulation results are shown in comparison with those from a non-hysteresis comparator in Fig.4.11.

Figure 4.11 Time-domain comparisons between a non-hysteresis comparator and hysteresis tunable voltage comparator

From Fig.4.8, it could also be noted that the terminal G1 of both M3 and M4 are not necessarily connected to the same voltage, V<sub>tun</sub>. With the different voltages at both inputs, V<sub>TRP+</sub> and V<sub>TRP</sub>, are asymmetrically tuned. Hence, V<sub>TRP+</sub> and V<sub>TRP</sub>, can be tuned orthogonally. If G1 of M3 and M4 are connected to V<sub>tun1</sub> and V<sub>tun2</sub> respectively, the simulation results are shown in Fig.4.12 and Fig.4.13 where V<sub>TRP+</sub>=3.3V and V<sub>TRP</sub>=2.2V are set by V<sub>tun1</sub>=4.6V and V<sub>tun2</sub>=3.6V.

Figure 4.12 DC transfer curve of orthogonal tune hysteresis tunable voltage comparator

Figure 4.13 Transient analysis of orthogonal tune hysteresis tunable voltage comparator

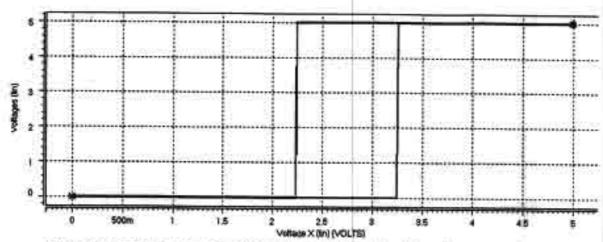

An experiment of the back-gate tuning of M3 and M4 has also been investigated with a result in Fig.4.14 showing that the range of V<sub>TRP</sub>, and V<sub>TRP</sub>, are not as wide as those offered by the circuit employing FGMOS. Also, the back-gate biasing always experiences an amount of leakage current because the bulk terminal is not fully isolated as in the case of poly1 and poly2 gates.

Figure 4.14 V<sub>TRP+</sub> and V<sub>TRP-</sub> vs. V<sub>ture</sub> at the back gate of M3 and M4

A Hysteresis Tunable Voltage Comparator using FGMOS is already proposed. The circuit is essentially exploiting FGMOS devices in the positive feedback scheme to create the hysteresis. Based on the tunability of the FGMOS, the current ratio of l<sub>D10</sub>/l<sub>D3</sub> and l<sub>D11</sub>/l<sub>D4</sub> corresponding to the amount of feedback current is used to tune the hysteresis effectively. An experiment of the back-gate tuning of M3 and M4 has also been investigated with a result showing that the range of V<sub>TRP+</sub> and V<sub>TRP-</sub> are not as wide as those offered by the circuit employing FGMOS. Also, the back-gate biasing always experiences an amount of leakage current because the bulk terminal is not fully isolated as in the case of poly1 and poly2 gates. The proposed idea is implementable on any standard double-poly CMOS processes. The work has been performed on AMI 1.2μm CMOS process available through MOSIS. All the simulation results confirm well the functionality. Performance optimizing will be placed as future works.

## 5. DIGITAL FGMOS COMPARATOR

Designs of digital comparators are presented in this section. The main idea is to exploit the well-known characteristics of the floating-gate MOSFET onto an opamp based voltage comparator. The threshold voltage operation of the floating-gate MOSFET is exploited to achieve a hysteresis tunable analog voltage comparator of which the positive feedback factor is tunable. Based on the analog comparator circuit, a digital comparator is realized with replacement of the floating-gate MOSFETs for the input devices of which the drain currents as a linear sum of the weighted multiple-input voltages is exploited. Basically the internal mechanisms of both proposed comparators are analog functions. Designs and simulation results on Hapice on 1.2 µm AMI CMOS are given to demonstrate the functionalities.

## 5.1 4-BIT DIGITAL COMPARATOR

A 4 bits digital comparators are presented in this section. Based on the same opamp based comparator as in the analog case, the new comparator can also be realized by employing the floating-gate MOSFETs as the input devices. The 4-bits digital comparators are proposed separately as non-hysteresis and hysteresis types. Both circuits are utilized further for designing an 8-bits digital comparator that will be discussed in the next section. Input of 4-bits comparators are using 5-inputs FGMOS, 4 input gates are used for 4-bits digital input and another for biasing. From (3.5) and (3.6), drain current equations of multiple input floating gate MOSFET, can be rearranged to (5.1) and (5.2) for 5-inputs FGMOS as shown below.

$$I_d = \frac{1}{2} \mu C_{OX} \frac{W}{L} \left[ \sum_{i=1}^4 (w_i V_{Oi} - V_S) - (V_{TH} - w_S V_{OS}) \right]^2$$

(5.1)

$$I_d = \frac{1}{2} \mu C_{OX} \frac{W}{L} \left[ \left( w_1 V_{G1} + ... + w_5 V_{GS} \right) - V_S - V_{TH} \right]^2$$

(5.2)

The drain current is essentially a linear sum of all inputs weighted by the capacitive coupling ratios. Equation (5.2) is written to show a linear sum of the weighted multiple-input voltages. This equation is used to design all comparators in this section.

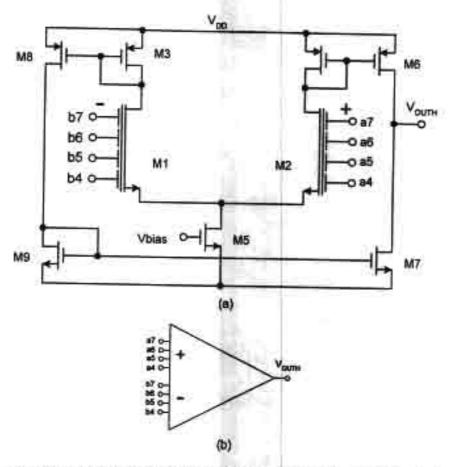

## 5.1.1 NON-HYSTERESIS 4-BITS DIGITAL COMPARATOR

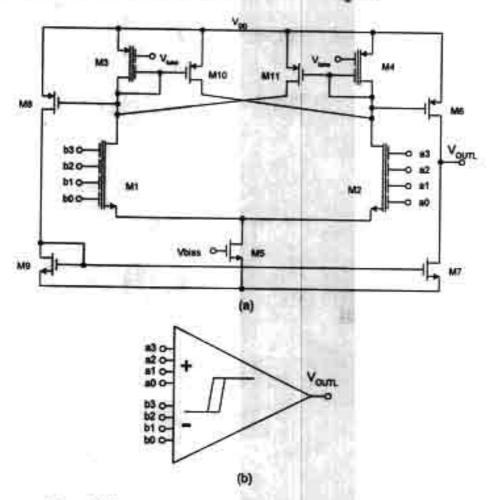

The non-hysteresis digital comparator is shown in Fig.5.1. It is seen that FGMOSs are employed as the input devices in order to exploit the drain current, which is written in (5.2) as a linear sum of the weighted multiple-input voltages of the binary

bits. Then the circuit is digital at the input and output but it internally works as an analog circuit.

Figure 5.1 Non-hysteresis 4-bits Digital Comparator (a) schematic (b) symbol

From Fig.5.1 (a), the FGMOS  $M_1$  and  $M_2$  are designed with the floating-gate area of  $12\times3\mu\text{Lm}^2$ . Let  $k_4,...,k_7$  are the weights of the input gates denoted as a4,...,a7 and b4,...,b7 respectively, where a4 and b4 are the least significant bit of this comparator. The inputs gates have the sizes set by the binary weights as in Table 5.1.

Table 5.1 Design parameters of the FGMOS

|                 | k4        | k5        | k6        | k7        |

|-----------------|-----------|-----------|-----------|-----------|

| Binary weights  | 1/16      | 1/8       | 14        | 1/2       |

| Sizes(µm²)      | 10.8×22.8 | 21.6×22.8 | 43.2×22.8 | 86.4×22.8 |

| Capacitance(fF) | 159.7     | 319.5     | 638.9     | 1277.8    |

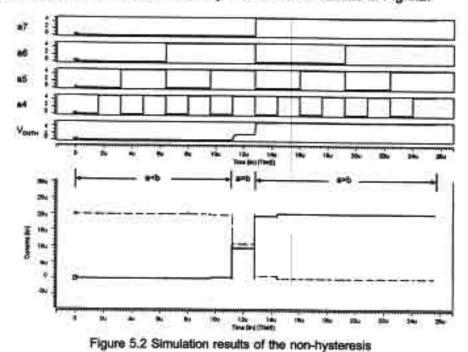

This non-hysteresis 4-bits comparator can be represented as a symbol in Fig.5.1(b). The circuit delivers three levels of the output signal such as logic High or  $V_{\rm dd}$  when the total weighted sum of the binary inputs at the positive terminal is higher than that of the negative terminal. The output signal is logic Low or GND when the total weighted sum of the binary inputs at the positive terminal is lower than that of the negative terminal. The output is  $V_{\rm dd}/2$  when the total weighted sums of the binary inputs of both terminals are equal. This particular function implies an ability to detect the equality of the binary inputs. The functionalities are confirmed by the simulation results in Fig.5.2.

Fig.5.2 shows output signal as V<sub>OUTH</sub> and drain currents of the input devices where the binary a7-a4 are swept digitally and the binary b7-b4 are set to #b0111. It is seen that the output voltage is at V<sub>dd</sub>/2 and the input drain currents are equal when the binary a7-a4 equals to b7-b4. This property will also be utilized further in the design of the 8-bits comparator.

#### 5.1.2 4-BIT HYSTERESIS COMPARATOR

The hysteresis comparator is shown in Fig.5.3 (a), which is similar to Fig.5.1(a) except that the hysteresis tuning part used in the analog comparator is employed. Because of the hysteresis operation, this circuit delivers only two levels of the output signal at high or low. As a result of the hysteresis tuning, the output signal is delivered according to the arithmetic functions of A>B or A≥B that are selected by V<sub>tune</sub>. Based on the same dimensions of all MOSFETs in Fig.5.1(a) and M3, M4 are set to

$15\times2.4\mu\text{m}^2$  and the two input gates are set to  $77\times31\mu\text{m}^2$  for the signal input gate and  $11\times31\mu\text{m}^2$  for  $V_{\text{tune}}$ . The simulation results are shown in Fig.5.4.

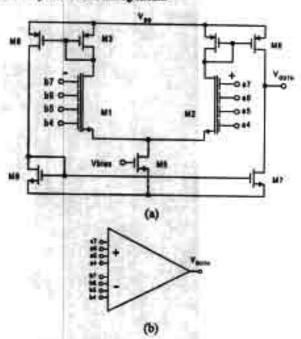

Figure 5.3 Hysteresis 4-bits Digital Comparator a) schematic b) symbol

Figure 5.4 Simulation results of the hysteresis comparator

From Fig.5.4, the binary b3-b0 are set to #b0101 while the binary a3-a0 are swept digitally. It is seen that if V<sub>tune</sub> is set to High, the output signal changes its stage when both binary sets are equal. The circuit performs the function A≥B. If V<sub>tune</sub> is set to Low, the comparator will perform the function A>B. In the next section, both hysteresis and non-hysteresis digital comparator will be utilized for the design of 8 bits digital comparator.

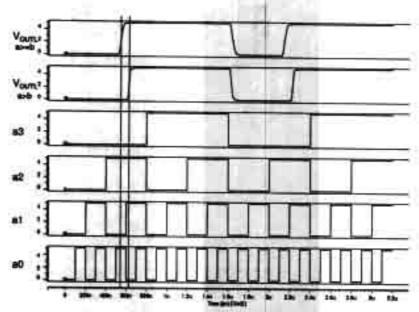

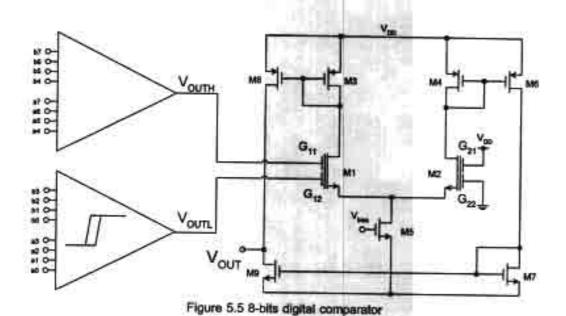

# 5.2 8-BITS DIGITAL COMPARATOR

An 8-bits digital comparator is realized by using those two 4-bits comparators described in section 5.1 and another two input voltage comparator as shown in Fig.5.5.

From Fig.5.5, it is seen that the 4-bits non-hysteresis comparators is used to compare the upper 4-bits where the three levels of output voltage at V<sub>OUTH</sub> are delivered out when A>B, A<B and A=B. The 4-bits hysteresis comparator is used for the comparison of the lower 4-bits where only two levels of output voltage at V<sub>OUTL</sub> are delivered. The third comparator is used as the main comparator, of which the referenced input is connected to V<sub>dd</sub> and GND. The functions of the main comparator are concluded in Table 5.2.

Table 5.2 Functions of the main comparator

| Jpper 4 bits output       | Lower 4 bits output    | Output<br>High / V <sub>ee</sub> |  |

|---------------------------|------------------------|----------------------------------|--|

| High / V <sub>ee</sub>    | x                      |                                  |  |

| Equal / Va/2              | High / V <sub>ed</sub> | High / V <sub>eq</sub>           |  |

| Equal / V <sub>d</sub> /2 | Low / GND              | Low / GND                        |  |

| Low / GND                 | x                      | Low / GND                        |  |

where X denotes don't care condition. It is seen that when the upper 4-bits inputs of A are higher or lower than those of B, the output is High or Low right away. If the upper 4-bits inputs of A are equal to those of B, the output will correspond to the comparison of the lower 4-bits of A and B. However, in order to have the functions correspond to Table 5.2, the main comparator must have the four input gates such as G<sub>11</sub>, G<sub>12</sub>, G<sub>21</sub>, G<sub>22</sub> be designed with proper sizes. The weights of each input are denoted as k<sub>11</sub>, k<sub>12</sub>, k<sub>21</sub>, correspondingly, which are considered as in Table 5.3.

Table 5.3 Sizing criteria for the main comparator

| Inp   | uts  | Output | West and the second second                                                                                                 |  |

|-------|------|--------|----------------------------------------------------------------------------------------------------------------------------|--|

| Vouth | Voun | Vour   | Weight sum operations                                                                                                      |  |

| 5V    | ×    | 5V     | k <sub>11</sub> ×5+ k <sub>13</sub> ×0 > k <sub>21</sub> ×5+ k <sub>22</sub> ×<br>.†. k <sub>11</sub> > k <sub>21</sub>    |  |

| 0     | ×    | 0      | $k_{11} \times 0 + k_{12} \times 5 < k_{21} \times 5 + k_{22} \times 0$<br>$\therefore k_{12} < k_{21}$                    |  |

| 2.5V  | o    | 0      | $k_{11} \times 2.5 + k_{12} \times 0 < k_{21} \times 5 + k_{22} \times 0$<br>$k_{11} < 2 \cdot k_{21}$                     |  |

| 5V    | 5V   | 5V     | $k_{11} \times 2.5 + k_{12} \times 5 > k_{21} \times 5 + k_{22} \times 0$<br>$\therefore k_{11} + 2 \cdot k_{12} > k_{21}$ |  |

where 5V and 0 stands for the logic High and Low and X denotes the don't care condition. Examining the weight sum operations, we can conclude that all weights must conform to the condition that  $k_{21} < k_{11} < 2k_{21} < k_{11} + 2k_{12}$ . So, the weights and sizes of the input gate capacitances are designed and calculated as in Table 5.4.

Table 5.4 Design parameters of G<sub>11</sub>, G<sub>12</sub>, G<sub>21</sub>, G<sub>22</sub>

|                     | G <sub>11</sub> | Gtz       | G <sub>21</sub> | G <sub>22</sub> |

|---------------------|-----------------|-----------|-----------------|-----------------|

| Binary weights      | 12/16           | 4/16      | 7/16            | 9/16            |

| Sizes(µm²)          | 129.6×22.8      | 43.2×22.8 | 75.6×22.8       | 97.2×22.8       |

| Capacitance<br>(fF) | 1916.4          | 638.8     | 1117.9          | 1437,3          |

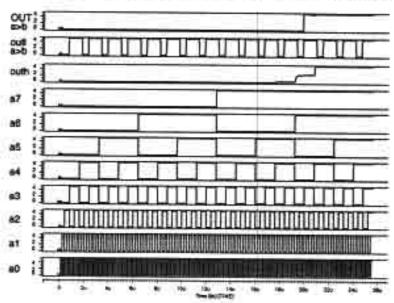

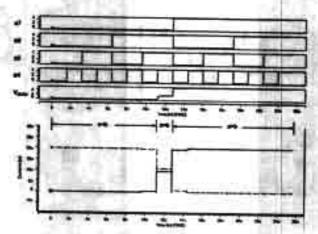

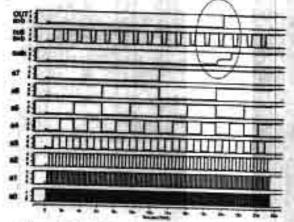

Then the functionalities can be demonstrated by the simulation results in Fig.5.6.

Figure 5.6 Simulation results of the 8-bits comparator

In Fig.5.6, the binary B is set to #b11000110 while the binary A is swept digitally from 0. It is seen that the  $V_{OUTH}$  of the upper comparator contributes  $V_{dd}/2$  when the binary A=B, and then the output corresponds to the  $V_{OUTL}$  of the lower comparator.

This section presents a design of a non-clocked 8-bits digital comparator that essentially manipulates the proposed analog voltage comparator to realize the new digital circuit in which the signal is Internally processed in an analogue fashion. The proposed idea can be implemented on any standard double-poly CMOS and be useful to mixed signal and computational applications. All the simulation results confirm well the functionality.

# 6. FGMOS COMPARATOR ON CLASS-D POWER AMPLIFIER

Most audio power amplifiers are designed in Class-A or class-AB, which normally delivers a limited efficiency because their power transistors operate in the linear area that consumes a huge biasing current, and then result in power dissipation or heat. In order to improve the efficiency, switching converters such as the Pulse Width Modulation (PWM) can be applied to an audio amplifier, which is then referred as switching amplifiers or class-D amplifiers [35, 36]. This type of amplifiers presents several advantages over the conventional class-A or AB amplifiers in their high efficiency and low internal power dissipation. However, this section presents the development of another type of the class-D amplifier based on the RWDM technique [37]. The circuit is designed for applications of battery-operated-devices such as output drives in mobile speakerphones, hearing-aid devices and implantable medical devices. The design also incorporates with a multiple input hysteresis comparator using floating-gate MOSFETs, which gave more computational ability than any other comparators that will discussed in detail.

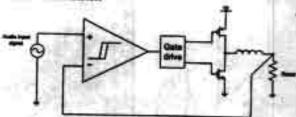

#### 6.1 CLASS-D AMPLIFIER

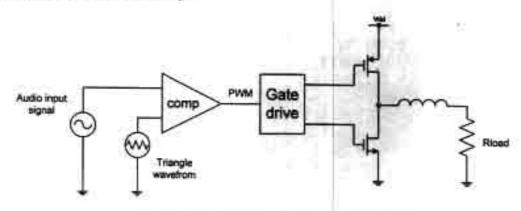

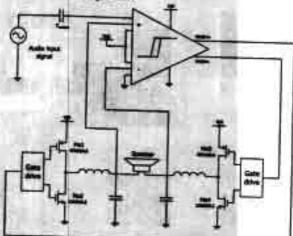

Conventionally, most class-D amplifiers are based on the Pulse Width Modulation (PWM) technique where the pulse width of the output PWM signal is made proportional to the amplitude of the modulating signal between the audio Input signal and the triangular signal. The signal at the output is recovered from PWM signal by passing it through a low pass filter, which could be formed by a resistor and inductor circuit inherently obtained from earphones or speakers. Fig.6.1 shows basic building blocks of a conventional class D amplifier such as 1) triangular waveform generator 2) comparator and 3) output stage.

Figure 6.1 Conventional PWM class-D amplifler

From Fig.6.1, the comparator compares the audio signal input with the triangular waveform from the waveform generator to produce a PWM signal, which is then used to control the switching timing of the output stage transistors to drive a low impedance load. The output power is delivered to the load by mean of the average output current controlled by the duty cycle of the PWM signal. The duty cycle is 50% when there is no signal at the input, thus the average output voltage is zero. The PWM class-D amplifiers can dissipate less power by properly arranging the switching timing of the output power MOSFETs between two lowest-dissipation modes such as fully on and fully off. In an actual amplifier, the efficiency of 98% could be obtained [38].

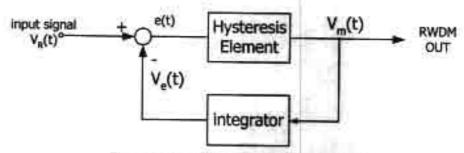

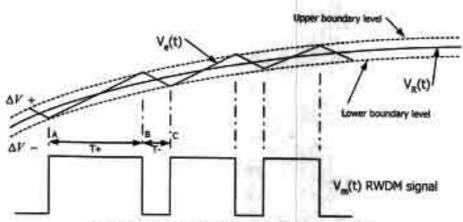

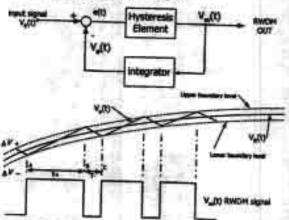

RWDM principle is also another technique used in class-D amplifier and shown in Fig.6.2. The concept of RWDM is mostly like PWM, except that the input signal  $V_R(t)$  is compared with the feedback signal  $V_e(t)$  in the negative feedback loop. The feedback signal  $V_e(t)$  is essentially the integration signal of RWDM by a low-pass filter. Since there is a hysteresis in the comparator,  $V_e(t)$  can track the amplitude of  $V_R(t)$  within the  $\pm \Delta V$  boundary as can be shown in Fig.6.2.

Figure 6.2 Block diagram of RWDM technique

Figure 6.3 Signaling of RWDM technique in Fig.6.2

Based on the RWDM mechanism in Fig.6.2, the switching frequency of the RWDM output signal can be calculated as in (6.1).

$$f = \frac{1}{T} = \frac{S_C}{4\Delta V} \left[ 1 - \left( \frac{S_R(t)}{S_C} \right)^2 \right]$$

(6.1)

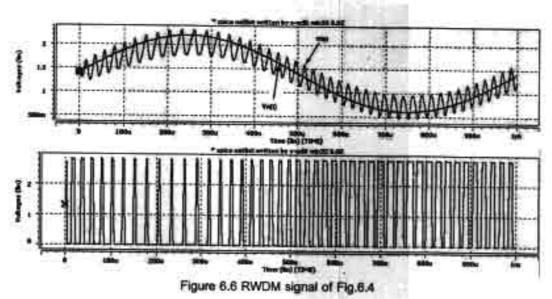

where  $S_R$  and  $S_C$  denote the slope of the input signal  $V_R(t)$  and the feedback signal  $V_e(t)$  correspondingly and  $\Delta V$  is the magnitude of the hysteresis loop which is controlled directly by the trip voltage of the hysteresis comparator.  $S_C$  is also controlled by the time constant of the integrator in the feedback path. An example of a simulated RWDM signal of a sinusoid signal can be shown in Fig.6.3.

## 6.2 THE PROPOSED RWDM CLASS-D AMPLIFIER

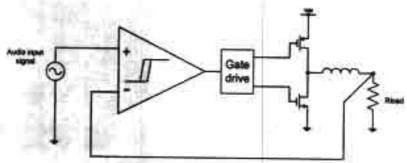

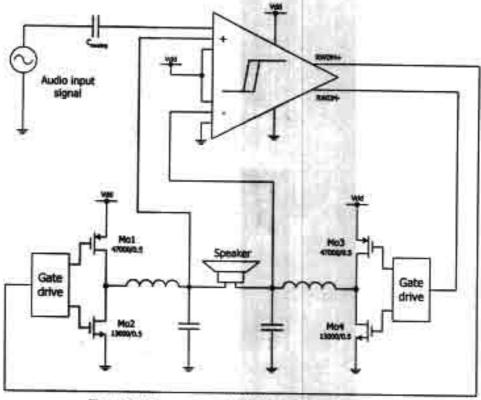

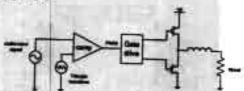

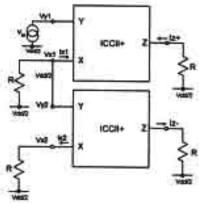

A new proposed class-D amplifier based on RWDM technique is presented as a block diagram in Fig.6.4, which is seen that the amplifier comprises only a hysteresis comparator, driving circuits and an integrator formed by an RL low-pass network. The circuit can be integrated onto a monolithic chip except the inductor and the load resistor.

Figure 6.4 Proposed Class-D audio amplifier

From Fig.6.4 the audio input signal is directly connected to the input gate of the comparator, which is basically a high impedance node. The comparator then compares the input signal with the feedback signal from the output, which is initially zero. With the hysteresis loop, the comparator can delivers an RWDM signal comprising only logic low or high that is then integrated by the inductor resistor network. The feedback signal is a saw-tooth-like signal used to compare with input signal in the next cycle. All circuit blocks of the proposed amplifier such as comparator, driving circuit and the low-pass filter will be described in the detail in the following sections.

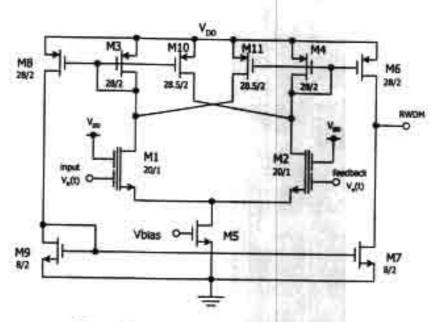

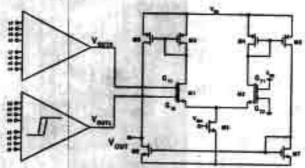

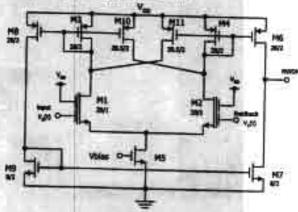

Figure 6.5 Rail to rail input Hysteresis comparator

The hysteresis comparator shown in Fig.6.5 is a schematic of the comparator in Fig.6.4. This circuit is capable to receive a wide-range input signal. The particular capability is achieved by the employment of two-inputs FGMOS as the input transistor M1 and M2. This characteristic allows the feedback signal at the gate of M2 to track the amplitude of the input signal at the gate of M1 effectively between the supply voltage and ground. Both two-inputs n-type FGMOSs are identical and also have equal size of the input gates. With one of the input gates connected to Vdd, the FGMOSs are ensured to be turned on at all level of the input signal. In other words, the comparator possesses the rail-to-rail characteristic.

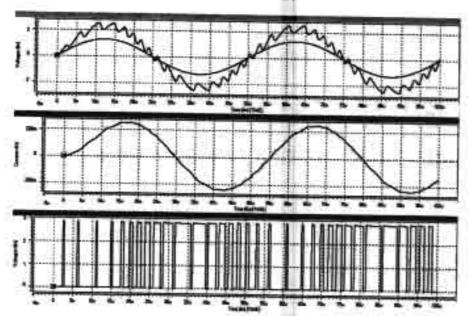

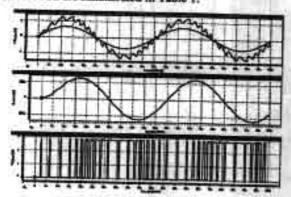

All the signal of the proposed circuit are shown in Fig.6.6 that the pure sinusoid is the input that compares with the "saw-tooth-like" signal from the output to generate the PWM signal shown in the lower of the figure.

# 6.3 THE PROPOSED RWDM BTL CLASS-D

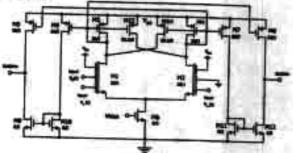

A Bridge Tied Load (BTL) class-D amplifier based on the RWDM technique is presented in Fig.6.7. It is basically a fully differential version of the proposed RWDM concept shown in Fig.6.4. With the BTL configuration the output voltage swing can be double those of the half-bridge configuration in Fig.6.4. The audio input signal is directly connected to the input of the comparator, which is normally in the range of 0~V<sub>DD</sub> so we use 3-inputs floating-gate MOSFETs as the input differential pairs of the hysteresis comparator.

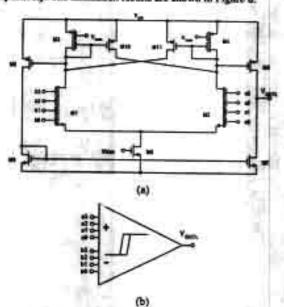

Figure 6.7 The proposed RWDM BTL class-D amplifier

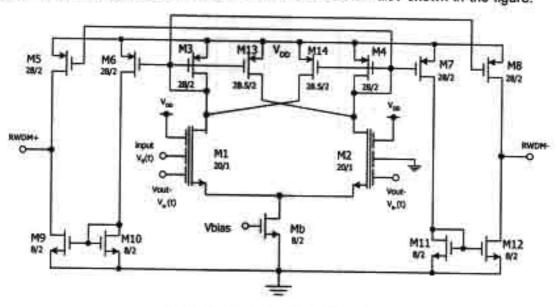

In Fig.6.8, the 6-inputs fully differential hysteresis comparator comprises three-input gates FGMOS devices as the differential pairs of which the coupling capacitors are designed as C<sub>1</sub>=200fF, C<sub>2</sub>=128fF and C<sub>3</sub>=64fF which correspond to the capacitive coupling ratios of k1, k2 and k3 to 0.5, 0.32 and 0.16 respectively. The first inputs of both plus and minus terminals having the weight factor of 0.5 are connected to V<sub>DD</sub> to bias the differential pairs. This results in a DC potential of 0.5V<sub>DD</sub> at the floating-gate on Poly1 of the differential pairs. The 2<sup>nd</sup> input gates having weight of 0.32 are used as the

inputs of the comparator while the 2<sup>nd</sup> gate of M1 is connected to the AC-coupled audio input signal and the 2<sup>nd</sup> gate of M2 is connected to Gnd. The weights of the 2<sup>nd</sup> inputs allow a wide input swing for the comparator. The 3<sup>nd</sup> input gates with the weight of 0.16 are connected to output nodes of the amplifier respectively. They are designed with half of the weight factor of the 2<sup>nd</sup> gates in order to make the close loop gain of the amplifier equal to 2, which is the requirement to have an output signal swing of +/- 2.8V while the input signal swing is only in the range 0~2.8V. The other advantage of this fully differential comparator is that the RWDM output signals from the comparator are exactly out of phase without any delay. The control of the power MOSFETs of both sides of the loads will be very precise. Dimensions of all MOSFETs are also shown in the figure.

Figure 6.8 Fully differential comparator

#### 6.4 SIMULATION RESULTS

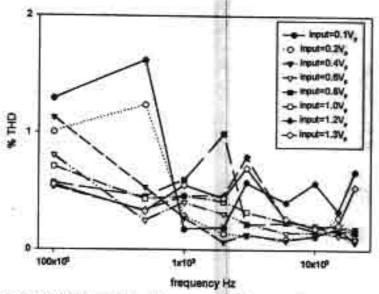

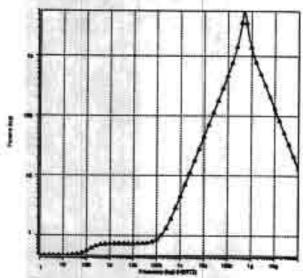

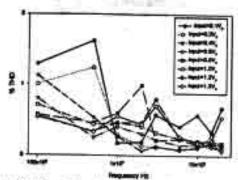

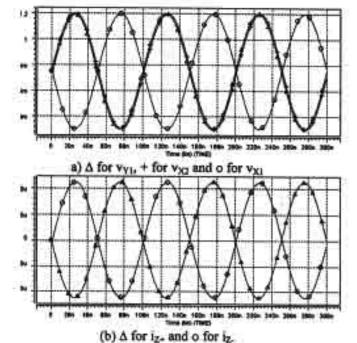

Based on the proposed amplifier circuit in Fig.6.7 with the comparator shown in Fig.6.8, the amplifier can deliver current to the  $8\Omega$  resistive loads and correspond to the output signal of  $5.2V_{p-p}$ . Time domain simulation is show in Fig.6.9 and THD vs Signal frequency and input amplitude is show in Fig.6.10. Other performances based on simulation results on HSPICE are summarized in Table 6.1.

Table 6.1 Summary of the proposed amplifier

| Process technology       | Alcatel 0.5µm CMOS |

|--------------------------|--------------------|

| Supply voltage           | 2.8V               |

| Static Power dissipation | 79.51µW            |

| Maximum output swing | 5.2V <sub>pp</sub> |

|----------------------|--------------------|

| Output load          | εΩ                 |

| Maximum power        | 0.88W              |

| Efficiency           | 95%                |

Figure 6.9 Voltage output signal, current output signal and the RWDM output signal at input 1.3V<sub>p</sub>, 20kHz

Figure 6.10 THD vs. Signal frequency and input amplitude

A single-chip low-voltage high-efficiency Class-D Power Amplifier for portable devices has been proposed. The amplifier has a very simple architecture that makes it easier to be integrated with other circuit blocks on a system level. By virtue of the high efficiency of Class-D architecture coupled with the low voltage operation provided by the use of floating-gate MOSFET hysteresis comparator, this amplifier is suitable for portable devices with battery operations. It exhibits high distortion at low input signal due to the small changing of the input signal compared to the ripple at the output. The efficiency of this circuit is 95% at 0.88Watt with a 2.8V power supply.

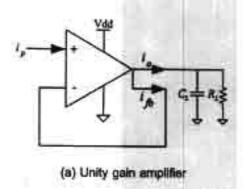

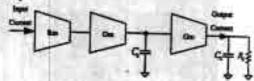

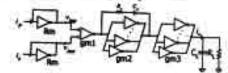

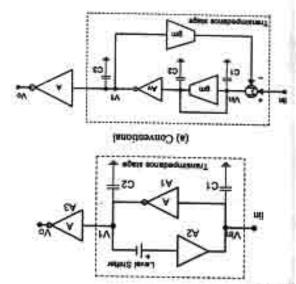

# 7. A LOW-VOLTAGE WIDE-SWING FGMOS CURRENT AMPLIFIER

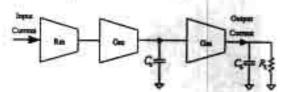

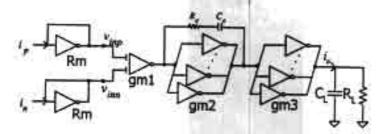

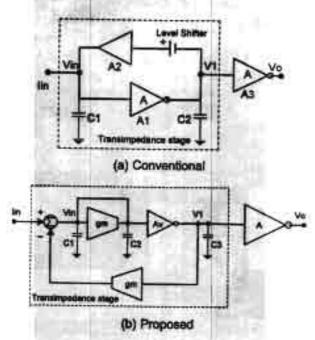

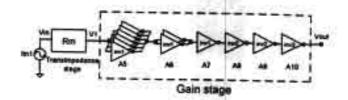

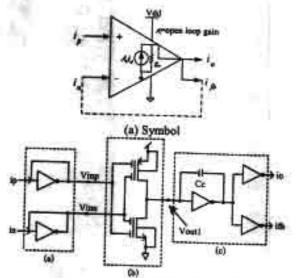

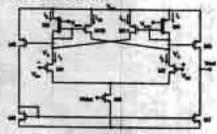

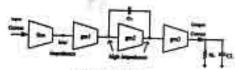

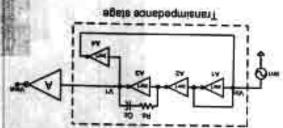

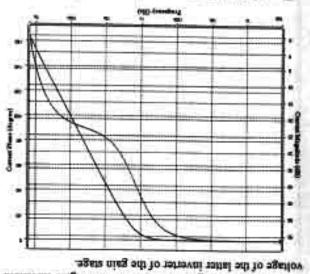

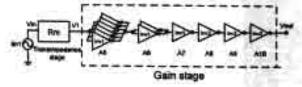

In the last decade, current-mode circuits [39] have drawn lots of interest due to their attractive features such as wide bandwidths, wide dynamic ranges and low voltage operations, all of which are very important for modern integrated circuits. Several elegant techniques for current-mode signal processing have been demonstrated successfully. These have mostly utilized current mirror cells, Gilbert gain cells and logdomain, square-root domain or translinear cells to perform filtering, multiplications, modulations, etc. For amplification purposes, current-mode amplifiers [40] based on a high open-loop current gain used for an accurate closed-loop configuration is also a very promising technique since use of a high gain device in a negative feedback loop allows large collection of transfer functions, performances of which are independent of the large but sensitive open-loop gain. So far, several high performance current amplifiers and opamps [41-47] have been proposed on CMOS technologies with various structures and topologies such as Differential Input Differential Output (DIDO), Differential Input Single-ended Output (DISO) or Single Input Differential Output (SIDO), etc. In general, the current opamp principle can be shown as a block diagram as in Fig.7.1, where the input current signal is firstly converted to a voltage quantity by the transimpedance amplifier (Rm) and then amplified again by the transconductance amplifiers (Gm) to produce the output current and hence the open-loop current gain. There is usually at least one high impedance node in the circuit that should be connected by a compensation capacitor for stability.

Figure 7.1 Current opamp principle

So far, most design efforts have been directed at the development of fully differential structures and enhancement of the open-loop gain and CMRR. In this work, we aim for a high signal swing by trying to avoid a class A circuit for which the limitation of current signal swing and slew rate is a result of the existing current sources, which also limit the charging current for the compensation capacitor at the high impedance node. Thus this section proposes a new current amplifier circuit totally formed in the class AB structure utilizing CMOS inverters and the recently proposed additive analog inverter [27] using floating-gate MOSFETs. Since there is no biasing current source to

timit the signal swing, our amplifier possesses a wide swing and high slew rate. The design is applied on a 0.5 µm CMOS with 1.5 Volts power supply to demonstrate high frequency operation and with 1 Volt power supply to show the feasibility of low power operations at a lower frequency range where all MOSFETs are biased in the weak inversion region.

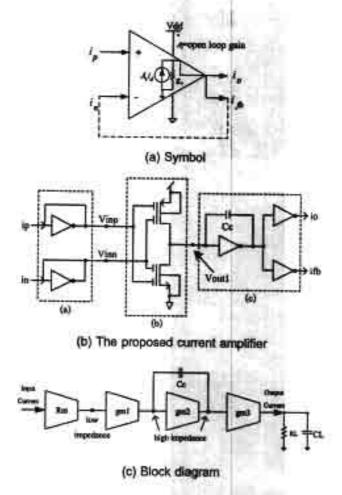

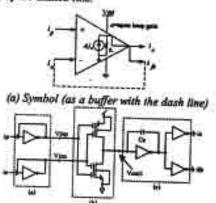

# 7.1. THE PROPOSED CURRENT AMPLIFIER

The proposed current amplifier, as symbolically shown in Fig.7.2(a), has two identical input terminals denoted as i<sub>p</sub> and i<sub>n</sub>, and two output terminals delivering the same phase of the signal denoted as i<sub>p</sub> and i<sub>p</sub>, which are used as the output and the feedback port respectively. At the input terminals, it is noted that the input i<sub>n</sub> can only be symbolized as an inverting terminal when the amplifier is connected in the negative feedback configuration as shown by the dashed line. This will be discussed later in this section.

Figure 7.2 The proposed current amplifier

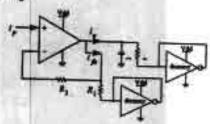

In Fig.7.2(b), the amplifier comprises three circuit blocks as shown in the dashed boxes.

The transimpedance amplifier is shown in box (a) and written as

$$Rm = \frac{1}{(gm_n + gm_p)} \tag{7.1}$$

where gm<sub>n</sub> and gm<sub>e</sub> are respectively the transconductance of NMOS and PMOS of the inverter. The additive analog inverter in box (b) is basically a two-input CMOS inverter elegantly built from the floating-gate MOSFETs and proposed in [41]. It is employed in this circuit together with the other Rm and gm blocks to work as a differential amplifier because the polarity of i<sub>th</sub> is inversed to those of i<sub>p</sub> causing the voltage at node V<sub>inn</sub> to be inversed to those at node V<sub>inp</sub>. Considering only the NMOS, a large signal current equation can be written as in (7.2) where the coefficient of V<sub>inn</sub> is now negative.

$$I_{D} = \frac{1}{2} \mu C_{ac} \frac{W}{L} \left[ \left( k_{1} V_{asp} - k_{2} |V_{bas}| \right) - V_{S} - V_{TH} \right]^{2}$$

(7.2)

Here k1 and k2 are the capacitive division factors [27, 48]  $C_1/C_T$  and  $C_2/C_T$ , where  $C_1$  and  $C_2$  are the effective coupling capacitances between the input gates and the floating gate and  $C_T$  is the total capacitance seen from the floating gate. All capacitances correspond directly to the sizes of the input gates and the floating gate areas obtained from the layout of the circuit. In this case, the equal input gate areas of  $I_p$  and  $I_n$  are set and result in equal values of  $C_1$  and  $C_2$  of 50fF and k1 and k2 of 0.5. The two-inputs CMOS inverter works as if a differential amplifier for which the small signal voltage gain between the output  $V_{out1}$  and the differential inputs can be derived as

$$\frac{V_{out}}{(V_{sqs} - V_{sns})} = -(gm_{in} + gm_{ip})(r_{ots} // r_{otp})$$

(7.3)

Here r<sub>oin</sub> and r<sub>oip</sub> are the respective output resistances to the floating-gate NMOS and PMOS in the dashed box (b). With further analysis using the diagram in Fig.7.2(c), the open-loop current gain of the whole circuit can be derived as

$$A_i = Rm \cdot gm_1 r_{o1} gm_2 r_{o2} gm_3 \tag{7.4}$$

and the dominant pole frequency(Od) is

$$\omega_d = \frac{1}{r_{cl}gm_2r_{cl}C_c}$$

(7.5)

while the GBW is

$$GBW = \frac{Rm \cdot gm_1gm_3}{C_c}$$

(7.6)

## 7.2. DESIGN AND SIMULATION RESULTS

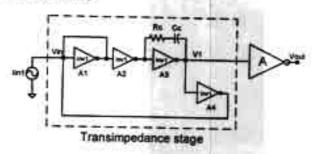

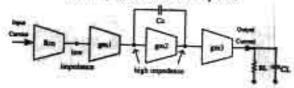

Based on the proposed concept, the design schematic can be simplified as shown in Fig.7.3, where it is seen that the circuit can be designed in a modular fashion

where all inverters including the additive analog inverter have the same dimensions of NMOS and PMOS correspondingly. If a higher gain of the gm<sub>2</sub> and gm<sub>3</sub> blocks is required, we simply add more cells of the identical inverters in parallel. R<sub>C</sub> and C<sub>C</sub> are employed for the frequency compensation.

Figure 7.3 The design Schematic

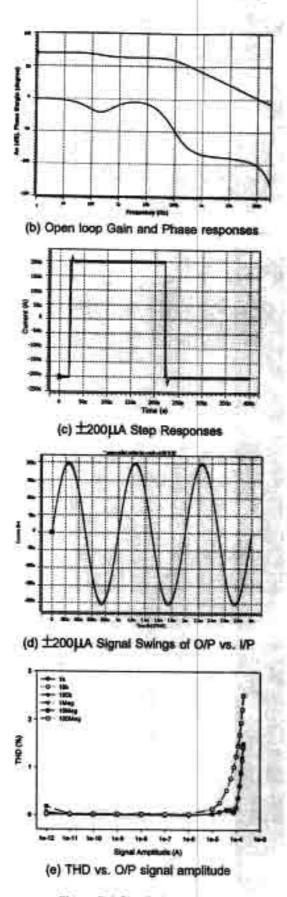

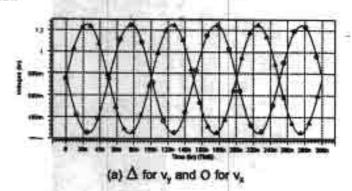

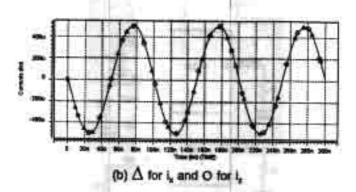

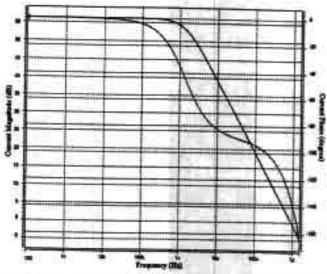

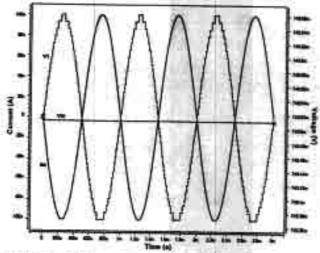

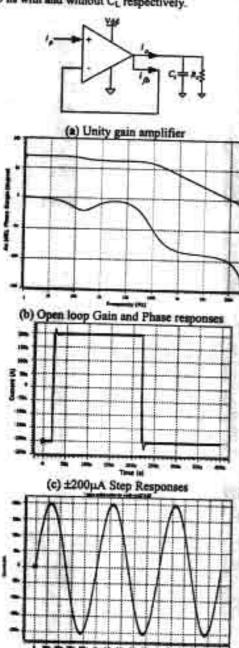

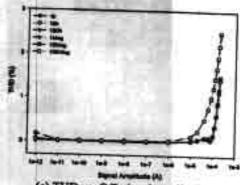

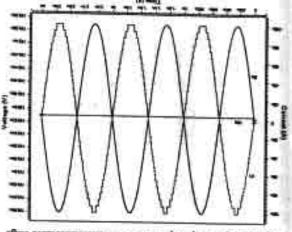

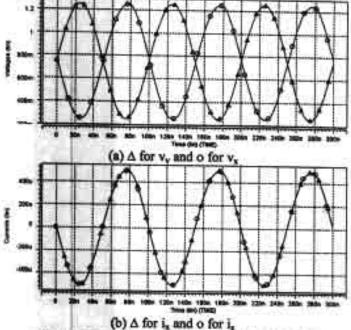

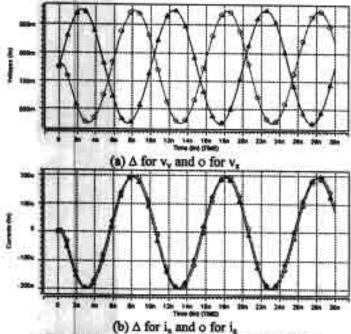

On the Alcatel 0.5 µm CMOS process, two amplifiers have been designed for Vop of 1.5V and 1V to demonstrate high frequency operations and low power respectively. With V<sub>DD</sub> of 1.5V, all NMOS and PMOS are designed with the dimensions of 6.9/0.5 and 23.6/0.5 respectively resulting in the idle currents of 30µA for each inverter. As seen in Fig.7.3, only one CMOS inverter is employed for each Rm and gm1 block but extra input gates on Poly2 are connected to the inverter of the gm1 block. Then four and three inverters connected in parallel are employed for the gm2 block and the gm3 block respectively. The amplifier is loaded with  $C_L$  of 10pF and  $R_L$  of 1.69k  $\Omega$  that is the same value as Rm or its input resistance. To improve the phase margin, Rc of 1k Ohms and C<sub>C</sub> of 0.8pF are also included in the compensation scheme. The circuit was simulated on HSPICE with the performances shown in Fig.7.4 where 69.6d8 Open-loop gain, 127MHz GBW and 74° Phase margin were achieved with a supply voltage of 1.5Volts and 635µW of power consumption. As a unity gain buffer, step response and linearity were measured at the maximum signal amplitude of ±200 µA and are shown in Fig.7.4(d) and (e) where the 1% settling times are measured as 9.4 and 34.5 ns with and without C<sub>L</sub> respectively.

Figure 7.4 Simulation results

Another amplifier with a 1V power supply was designed including all NMOS and PMOS with the dimensions of 8/0.5 and 19.9/0.5 respectively operated in the weak

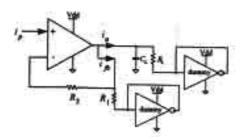

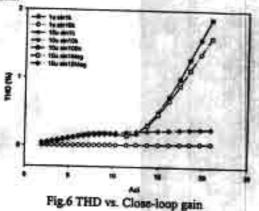

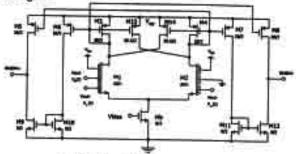

inversion region. As in Fig.7.3, only one CMOS inverter is employed for each Rm and gm1 block. Then five and two inverters connected in parallel are employed for the gm2 block and the gm3 block respectively. The amplifier is loaded with  $C_L$  of 10pF and  $R_L$  of  $47.86 k\Omega$ . From simulations, an open-loop gain of 68.3 dB, with 2.68 MHz GBW and  $68^{\circ}$  phase margin is achieved with 6 $\mu$ W power consumption. Due to space restrictions, not all performance graphs could be included here. However, in Table 7.1 all performances are compared with those of some earlier designs. The 1.5V  $V_{DD}$  version amplifier is also tested in negative feedback structure with passive networks to set the closed loop gains higher than 1 as shown in Fig.7.5.

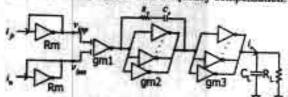

Figure 7.5 The amplifier in negative feedback

Fig.7.5 displays a non-inverting amplifier with a resistive negative feedback network. We arbitrarily put the dummy shorted input-output inverters to work as resistive loads and also to set the DC offset voltage to half of the V<sub>DD</sub> which is the same DC voltage at all input and output nodes. Then the closed loop gain can be derived as

$$A_{CI} = 1 + \frac{R_2 + Rm}{R_1 + Rm} \tag{7.7}$$

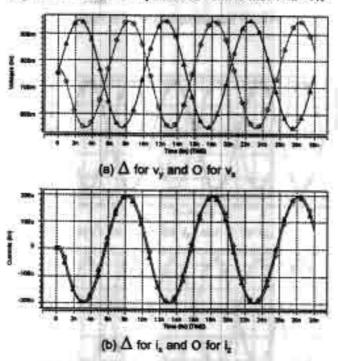

where  $R_1$  and  $R_2$  are the resistances in the range of 0~10k $\Omega$  which are integrable value on a chip. The dummy inverter load is used to settle a proper dc level in order to avoid DC offset of the feedback current. From (7.7), Rm with  $R_1$  is the transimpedance of the dummy inverter while Rm with  $R_2$  is the input resistance of the  $i_n$  terminal. Hence all Rms are the same value, With  $V_{DD}$  of 1.5V, by setting  $R_1$  at  $10\Omega$  and adjusting  $R_2$  for various close-loop gains, the THD of the O/P signal were measured and shown in Fig.7.6 where the labels in the plot show details of the input signals.

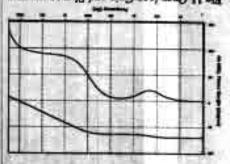

Figure 7.6 THD vs. Close-loop gain