factor. To avoid the negative value of  $L_m$  and to guarantee a smooth change in  $L_m$ ,  $V_{DS}$  in equation (19) is replaced by a smoothing function  $V_{DSX}$  [12]

$$V_{DSV} = V_{DSAT}' \left[ 1 + \frac{\ln\left(1 + e^{A(V_{DS}/V_{DSAT} - 1)}\right)}{\ln\left(1 + e^{A}\right)} \right]$$

(14)

The expression  $V_{DSX}$  in equation (14) gives  $V_{DS}$  and  $V_{DSAT}'$  when  $V_{DS} \sqcup V_{DSAT}'$  and  $V_{DS} \subseteq V_{DSAT}'$  respectively. Parameter A in equation (20) is used to control the smoothness of the curve.

#### III. RESULTS AND DISCUSSION

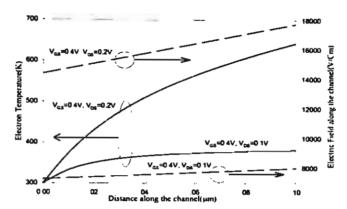

To verify the validity of the model, the model results have been compared with The devices were experimental data[2]. fabricated with several gate lengths ranging from 0.07µm to 0.25µm with the oxide thickness of 4.5nm. Fig. 1 shows the electric field from \( \beta \) (3)(dash line) and the electron temperature from \( \beta \) (4)(solid line) of the 0.1 µm MOSFET for two different drain source voltages ( $V_{DS}$ =0.1V and 0.2V) respectively. As seen, higher drain source voltage results in higher electric field and thus higher electron temperature. It can be noticed that carriers take longer distance before they are in equilibrium with the lattice.

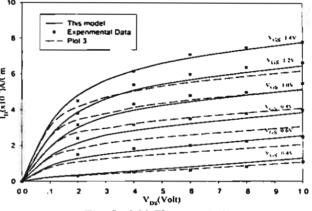

Figure 2 shows the comparison between the theoretical predictions of current voltage theoretical characteristic(solid line), the predictions without velocity overshoot[7](dash line) and the experimental data(dot)[2]. an effective channel concentration  $(N_4)$ , low field mobility  $(\mu_0)$ , saturation velocity (v<sub>sat</sub>), parasitic drain source resistance (R), smoothing factor (A) and  $\chi$  are  $7x10^{17}$  cm<sup>-3</sup>, 480 cm<sup>2</sup>/V<sub>•</sub>s,  $9x10^{\circ}$  V/cm, 55  $\Omega$ , 10 and 0.12 respectively. As seen, the predictions show increasing differences in the drain current with and without velocity overshoot especially for larger applied drain source voltages  $V_{DS}$ . This is attributed to the increasing electric field. For example, for the device biased at  $V_{GS}$ = 0.8V and  $V_{DS}$ = 0.6V, the drain current including velocity overshoot effect can be 29% larger than the current without velocity overshoot. agreements between the theoretical predictions and the experimental data are well obtained over a wide range of applied gate and drain voltages.

Fig. 1 Electric field and electron temperature along the channel

Fig. 2 I-V Characteristics

#### IV. CONCLUSION

A physics-based modeling of short channel MOSFET including velocity overshoot is presented. The model is developed based on the solution of energy balance equation. Electron temperature is analytically obtained along the channel and the thermoelectric and drift current are calculated. The model includes the effects of the mobility degradation, channel length modulation, drain induced barrier lowering and parasitic drain source resistance. The theoretical predictions of the model are compared with the experimental data and shown to be in good agreement over a wide range of biasing conditions.

#### **ACKNOWLEDGEMENT**

This work is supported by a grant from "The Thailand Research Fund (TRF)" under the grant number PDF/74/2544.

#### REFERENCES

- [1] M. Ono, M. Saito, T. Yoshitomi, C. Fiegna, T. Ohguro, and H. Iwai, "A 40 nm gate length n-MOSFET," *IEEE Trans. Electron Devices*, vol. 42, pp.1822-1830, 1995.

- [2] G.A. Sai-Halaz, M.R. Wordeman and E. Ganin, "High transconductance and velocity overshoot in NMOS (0.1μm) gate length," *IEEE Electron Device Lett.*, vol. 9, pp.464-466, 1988.

- [3] E. C. Kan, U. Ravaioli and D. Chen, "Multidi--mensional augmented current equation including velocity overshoot," *IEEE Electron Devices Lett.*, vol. 12, pp.419-421, 1991.

- [4] T.W. Tang, S. Ramaswamy, and J. Nam, "An improved hydrodynamic transport model for silicon," *IEEE Trans. Electron Devices*, vol. 40 No. 8, pp.1469-1477, 1993.

- [5] D. Sinitsky, F. Assderagi, "Velocity Overshoot of Electrons and Holes in Si Inversion Layers, Solid State Electronic, vol. 41, pp.1119-1125, 1997.

- [6] R.S. Huang and P.H. Ladbrooke, "The Physics of Excess Electron Velocity in Submicron Channel FET's", J. Apply. Phys. Vol. 48, pp. 4791-4797, 1977

- [7] V. Kasemsuwan, "An Analytical Transit Time Model for Short Channel MOSFET's," IEEE Inter. Conf. on Semiconductor Electronics (ICSE-2000), pp. 72-75, 2000.

- [8] M.El. Banna and M.El. Nokali, "A Pseudotwodimensional Analysis of Short Channel MOSFETs', Solid State Electronic., vol. 31, pp. 269-274, 1988.

- [9] M. Lundstrom, Fundamentals of Carrier Transp--ort, X Modular Series on Solid State Devices, Addison Wesley Co., 1990.

- [10] H.B.Dwight, 1961, Table of Integrals and others mathematical data (Macmillan Publishing)

- [11] P. K. Ko. "Approaches to scaling in Advanced MOS Device Physics," N.G. Einspruch and G. Gildenblat, eds. VLSI Electronics; Microstructure Science, vol. 18, New York: Academic, pp. 1-37, 1989.

- [12] A. Klos and A. Kostka, "PREDICTMOS a predictive compact model of small geometry MOSFETs for circuit simulation and device scaling calculations", Solid State Electronics, pp. 1145-1156, 2000.

### A 3Volt High Frequency and Low Input Impedance CMOS Current-Mode Precision Full-Wave Rectifier

Surachet Khucharoensin and Varakorn Kasemsuwan, Member, IEEE

Department of Electronics, Faculty of Engineering,

King Mongkut's Institute of Technology Ladkrabang (KMITL)

Tel. +66-2-326-4222 Ext. 102, Fax: +66-2-739-2398 E-mail: kkyarako: kmitl.ac.th

Abstract This paper presents a 3Volt high frequency and low input impedance CMOS current mode precision full-wave rectifier. The circuit is designed based on an improved Wilson current miller. All MOS transistors are biased at low current resulting in small power dissipation. Negative feedback has been employed to reduce the input impedance HSPICE is used to of the circuit (236 $\Omega$ ). perform the simulation and the result shows the frequency of operation as high as 100 with a standard 0.5µm CMOS technology. The mismatch obtained from the input and rectifier's output is 0.21% for an input current of ±150µA. The DC transfer characteristic shows good linearity, very sharp corner at zero crossing point and good symmetry during positive and negative input cycle while power dissipation is 5.8µW.

#### I. INTRODUCTION

PRECISION Full-Wave Rectifiers (PFWRs) are one among very important circuit building blocks analog and digital signal processing, conditioning and instrumentation especially for low level signals. Applications include RMS to DC conversions and peak detectors. approaches have been proposed[1-5] to build Conventionally, precision precision rectifiers. rectifiers are based on diodes and opamps[1-2]. The rectifier however has a problem with a high distortion during the zero crossing of the input signal due to that the opamps have to recover transition non-conduction/conduction with a finite small signal dV/dt(slew rate). The rectifiers are thus limited to a frequency performance well below the gain bandwidth product  $f_T$  of the amplifier. An improvement of the rectifier design was to use current conveyors The resulting circuits can and diodes[3-4]. operate at high frequency. However, the circuits are power hungry and quite large making them unsuitable for implementing in the large scale integrated circuit. Recently, a high performance precision rectifier has been proposed[5]. The circuit consists of only three transistors and are biased with low current resulting in low total power dissipation(4.8 $\mu$ W). The circuit can also operate at high frequency(100 MHz). However, the input impedance of the circuit is quite high(7.2 $k\Omega$ -47 $k\Omega$ ) posing a problem in the current mode circuit design. In addition, the output signal is not symmetry during positive and negative input cycle.

In this paper, a high frequency low input impedance CMOS current mode precision full-wave rectifier is proposed. The circuit is designed based on an improved Wilson current miller. All MOS transistors are biased at low current resulting in small power dissipation. Negative feedback has been employed to reduce the input impedance of the circuit. The DC transfer characteristic shows good linearity, very sharp corner at zero crossing point and good symmetry during positive and negative input cycle.

#### II. PRECISION FULL-WAVE RECTIFIER (PFWR)

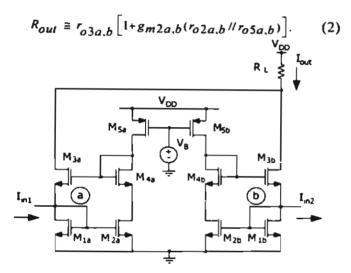

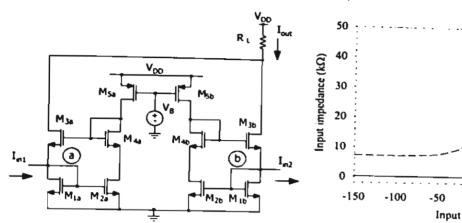

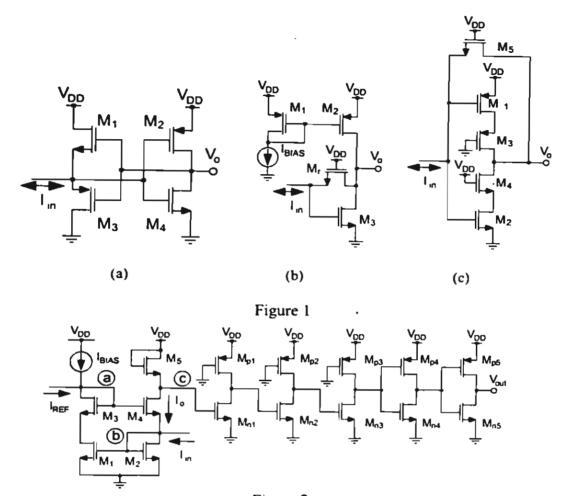

Fig. 1 shows the proposed precision rectifier. The circuit is designed based on two precision half wave rectifiers(M<sub>1a</sub>-M<sub>5a</sub> and M<sub>1b</sub>-M<sub>5b</sub>) operating alternatively during positive and negative input cycle. Im1 and Im2 are the input currents with the same magnitude but 180 degree out of phase. Msa,b are used to biased M1a,b-M4a,b on the edge of conduction. When  $I_{\rm in1}$  and  $I_{\rm in2}$ flows into node a and out of node b respectively. M<sub>3</sub>, cuts off while M<sub>3b</sub>, which is connected as a common gate, allows the input current In2 to flows through the load R<sub>L</sub>. Same explanation is applied when I<sub>m1</sub> and I<sub>m2</sub> flows out of node a and into node b respectively. As a result, the circuit works as a full-wave rectifier. The input impedance of the circuit(node a and b) are very low due to the negative feedback(shunt input) with in the loop M<sub>12,b</sub>-M<sub>42,b</sub>. To demonstrate this fact, when  $I_{in1}$  flows into node a, Voltage at node a,  $V_a$ , is pulled high. The signal  $V_a$  is amplified via  $M_{2a}$ (common source) causing voltage at the drain of  $M_{2a}$  and at the gate of  $M_{4a}$  to go low. As a result, the source voltage of  $M_{3a}$  is forced to be low. Straight forward circuit analysis shows the input impedance of the circuit given by

$$R_{in} = \frac{1}{g_{m1a,b} + g_{m3a,b} + g_{m2a,b} g_{m3a,b}(r_{o2a,b} // r_{o5a,b})}$$

(1)

while the output impedance is given as

Fig. 1 Schematic diagram of the proposed precision full-wave rectifier(PFWR).

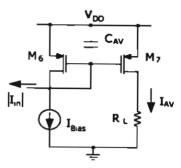

#### III. APPLICATION

There are many applications of the precision full-wave rectifier circuit such as RMS-to-DC converters and averaging circuits [6]. In this section, averaging current circuit is presented based on our proposed full-wave rectifier. This can be done by passing the output current after rectified to the first order low pass filter. Fig. 2 shows a simple first order low pass filter which consists of a current miller(M<sub>6</sub> and M<sub>7</sub>) and a capacitor C<sub>AV</sub> to control the ripple of the output current signal.

The averaging output current signal  $I_{AP}$  of the first order low-pass filter in Fig. 2 is given by

$$I_{Ai'} = \frac{\left|I_{in}\right|}{1 + s\left(C_{Ai'}/g_{m6}\right)} \tag{3}$$

$$I_{AV} = \frac{|I_{in}|}{1 + s\left(C_{AV}/g_{m6}\right)} \tag{4}$$

Fig 2. First order Low-pass filter

If  $sC_{Al'}/g_{m6} \gg 1$ , then  $I_{Al'}$  in the s-domain and time-domain are

$$I_{AV} = \left| I_{in} \right| \frac{g_{m6}}{sC_{AV}} \tag{5}$$

$$I_{AV} = \frac{1}{T} \int_0^T \left| I_{m} \right| dt \tag{6}$$

respectively and T is the RC time constant equal to  $C_{AV} / g_{m6}$ .

The criterion for selecting the value of  $C_{AV}$  is that the capacitor has to be large enough to keep the residual output ripple within specified limits [6] or

$$C_{AV} >> \frac{g_{m_{6(\text{max})}}}{4\pi f_{(\text{min})}} \tag{7}$$

where  $f_{(\min)}$  is the low end of input frequency range of interest. Because  $g_{m6}$  varies as a function of the drain current  $I_D$ ,  $g_{m6(\max)}$  or  $\sqrt{2\mu C_{ox}(W/L)_6 |I_{in(\max)}|}$  should be employed.  $C_{AV}$  should exceed the right-hand term by the inverse of the fractional ripple error that can be tolerated at the output current.

#### IV. PERFORMANCE OF THE PROPOSED PFWR

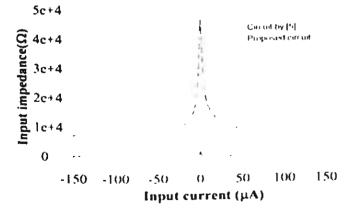

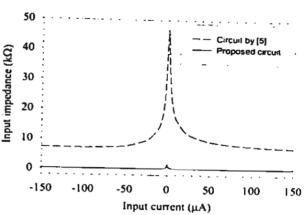

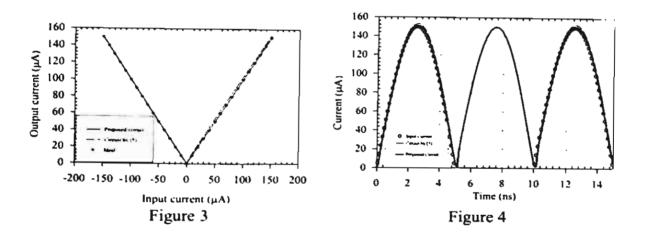

To verify the circuits performance, HSPICE is used to simulate the proposed circuit using a standard  $0.5\mu m$  CMOS process. In this work, the bias voltage  $V_B$  is used to bias  $M_{5a}$  and  $M_{5b}$  to have the drain currents of  $0.5\mu A$ . Table 1 shows all transistors' aspect ratio. Fig. 3 shows input impedance of the proposed PFWR(solid line) and that by[5](dash line). As seen, our proposed circuit has relatively much lower input impedance. To the best of authors' knowledge,

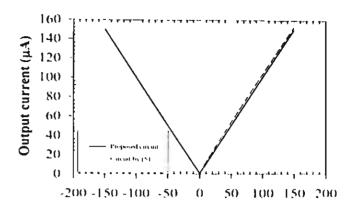

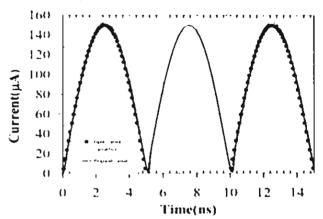

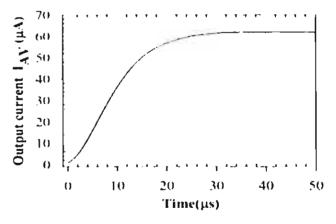

our circuit offers lowest input impedance(236Q). Fig. 4 shows the comparison of the DC transfer characteristic of our circuit (solid line) and As seen, the proposed circuit [5](dash\_line). shows a sharp corner at zero crossing point and good symmetry during positive and negative input cycle while the circuit by [5] shows mismatch during positive input cycle as a result of channel length modulation of the transistor. The mismatch obtained from the input and rectifier's output in this PFWR are 0.21% for an input current of ±150µA. Fig. 5 shows transient simulation of input signal(dot), our circuit(solid line) and [5](dash line) for the input frequency of 100MHz. The results show that our circuit gives a good symmetry for both positive and negative input cycle at high frequency. The total power dissipation is 5.8µW. Fig. 6 shows averaging current as a function of time. As seen, at steady state, our output current shows 64.75µA while the theoretical output current should read 63.66µA or 1.7% error. This error is a direct result of the drain source voltage mismatch between  $M_n$  and  $M_n$  and can be solved by increasing the channel length of the transistors M<sub>b</sub> and M<sub>c</sub> or using cascode technique to enhance the output impedance at the output node.

Table 1 Transistor's geometrical dimensions

| Device                          | W(µm) | L(µm) |

|---------------------------------|-------|-------|

| $M_{4a,b} = M_{4a,b} \ $        | 0.5   | 0.5   |

| M <sub>5a,h</sub>               | 7     | 2     |

| M <sub>6</sub> , M <sub>7</sub> | 10    | 2     |

Fig. 3 Input Impedance.

Fig. 4 DC Transfer Characteristics.

Fig. 5 Transient response (100 MHz)

Fig. 6 Averaging current (input frequency of full-wave rectifier at 4 MHz with amplitude  $\pm 100 \mu A_{\odot}$  using  $C_{43}$  TnF)

#### V. CONCLUSION

A high performance current mode precision full-wave rectifier based on an improved Wilson current miller is proposed. All transistors are biased at low current resulting in small power dissipation (5.8 $\mu$ W). The input impedance of the circuit is small(236 $\Omega$ ) and the circuit can operate at 100 MHz with only 0.21% mismatch between input and output signals for  $\pm 150\mu$ A input current.

#### **ACKNOWLEDGEMENT**

This work is supported by Thailand Research Fund(TRF)(grant no. PDF/74/2544).

#### REFERENCES

- [1] C. Toumazou and F.J. Lidgey, F.J, "Wideband precision rectification", *IEEE Proc.* G., vol. 134, no.1, pp. 7-15, 1987.

- [2] F.J. Lidgey, K. Hayatleh and C. Toumazou, "New current mode precision rectifiers", *IEEE Inter. Symposium on Circuits and Systems*, pp. 1322-1325, 1993

- [3] C. Toumazou, F.J. Lidgey and S. Chattong, "High Frequency Current Conveyor Precision Full-Wave Rectifier", *Electron. Lett*, vol. 30, no. 10, pp. 745-746, 1994.

- [4] K. Hayatleh, S. Porta, and F.J. Lidgey, "Temperature Independent Current Conveyor Precision Rectifier", Electron. Lett, vol. 30, no. 25, pp. 2091-2093, 1994.

- [5] C.C. Chang and S.I. Liu, "Current-Mode Full-Wave Rectifier and Vector Summation Circuit", *Electron. Lett.*, vol. 36, no. 19, pp. 1599-1600, 2000.

- [6] Z. Wang, "Novel Pseudo RMS Current Converter for Sinusoidal Signals using a CMOS Precision Current Rectifier," IEEE Transactions on Instrumentation and Measurement, vol. 39, Issue: 4, pp. 670-671, Aug. 1990.

## ±1.5V HIGH PERFORMANCE CMOS RAIL TO RAIL VOLTAGE FOLLOWER

Varakorn Kasemsuwan, Patt Boonyaporn and Apinunt Thanachayanont

Department of Electronics, Faculty of Engineering King Mongkut's Institute of Technology Ladkrabang (KMITL) Tel. +66-2-326-4222 Ext. 102, Fax.: +66-2-739-2398 Email: kkvarako@kmitl.ac.th

#### **ABSTRACT**

$\pm 1.5 V$  high performance CMOS rail to rail voltage follower is presented. The circuit is based on the symmetrical class AB voltage follower and can operate under supply voltages of  $\pm 1.5 V$ . The proposed circuit has power dissipation of 5.2mW under quiescent condition and can drive  $\pm 1.25 V$  to  $250 \Omega$  load with a total harmonic distortion of less than 0.5 percent and cut off frequency of 237 MHz. Although simple, the proposed circuit enables the output transistors to drive load efficiently.

#### 1. INTRODUCTION

An integrated voltage follower is one of the indispensable blocks in many analog VLSI systems. At present, most system requirements make it necessary for the follower to be able to drive low-resistance loads while, at the same time, handle large output voltage swing and maintain low harmonic distortion. Several approaches have been proposed to achieve this goal [1-6] One among the most popular approaches for realizing such follower is to employ a pseudo source follower which has a pair of complementary common-source MOS transistors. pseudo source follower has a key advantage in that it offers small output impedance. Moreover, the pseudo source follower offers a larger output voltage swing compared to a simple common drain type source follower. However, this approach suffers from the difficulty in the control of the quiescent current as a result of the random threshold voltage and high transconductance of pullup and pulldown parts. Therefore, any practical circuit using such approach needs to incorporate an additional mechanism to control the quiescent current. In addition, compensation capacitors are required to improve the stability and the transient response and thus requiring large chip area. Kadanka et al.[7] has proposed wild swing voltage follower without feedback. The circuit contains both BJTs and MOS transistors and is based on a double buffer implemented in the class AB emitter follower configuration. BJTs are employed as a core part and connected as an emitter follower due to two main reasons: 1) BJT has higher transconductance over MOS transistor, and 2) the mismatch in base-emitter voltage( $\Delta V_{BE}$ ) of npn and pnp is much less than the mismatch in the gate-source voltage( $\Delta V_{GS}$ ) of NMOS and The circuit shows good dynamic performance, good stability and low power dissipation. The circuit

implementation however requires BiCMOS process which has lower level of integration and higher power dissipation compared to the well known CMOS technology.

This paper presents  $\pm 1.5 \text{V}$  high performance CMOS rail to rail voltage follower which is capable of handling large output voltage swing and maintaining low harmonic distortion. The circuit is based on the symmetrical voltage follower with additional circuit to enhance transconductance and, at the same time, reduce gate-source voltage mismatch. The circuit can operate under  $\pm 1.5 \text{V}$  supplies and can drive  $\pm 1.25 \text{V}$  to 250  $\Omega$  load with a total harmonic distortion of less than 0.5 percent and cut off frequency of 237 MHz. The power dissipation under quiescent condition is 5.2 mW.

#### 2. CIRCUIT DESCRIPTION

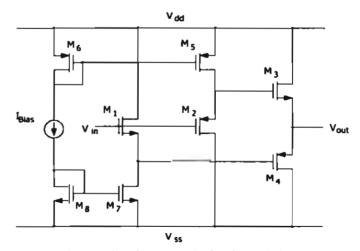

A conventional symmetrical voltage follower is shown in Fig. 1. The circuit consists of four transistors (M1-M4) connecting in the two stage common drain (double buffer) using class AB configuration. This configuration however has three main drawbacks: 1) a large offset voltage due to the mismatch between the gate-source voltage of NMOS and PMOS, 2) a high output impedance due to a reduced transconductance  $(g_m)$  of the MOS transistor compared to BJT's counterpart, and 3) a significant limitation in the linear output swing. All these problems can be alleviated using the proposed circuit shown in Fig. 2.

Figure 1. Conventional symmetrical voltage follower.

The proposed circuit in Fig. 2 is based on the symmetrical voltage follower described in Fig. 1. The four

This work was supported by Thailand Research Fund(TRF)"(grant no. PDF/74/2544).

transistors (M1, M3, M5 and M7) work as two stage common drain stage and are biased by current mirrors implemented by both NMOS and PMOS transistors (M2-M4 and M6-M8) with a transfer current ratio of  $\alpha$ (see Fig.2). Since M1 has the same drain current as M2 and M3 has the same drain current as M4, the gate-source voltages of M1 and M3 are then nearly equal provided that all NMOS have the same dimensions and all PMOS have the same dimensions. This gate-source voltage matching approach is also applied to the upper follower (M5-M8). As a result, the offset voltage of the voltage follower has been minimized[8]

The transconductance of the output MOS transistors can be increased by using two compound transistors as suggested in [8] consisting of M1-M4 and M5-M8. The transconductance of the lower follower (M1-M4) and upper follower (M5-M8) are given by Eqs (1a) and (1b) as

$$g_{m(LOWER)} = \frac{g_{m1} \cdot g_{m3}}{g_{m1} - \alpha \cdot g_{m3}}$$

(1a)

$$g_{m(\ell'PPER)} = \frac{g_{m5} \cdot g_{m7}}{g_{m5} - \alpha \cdot g_{m}}$$

(1b)

respectively.

From Eqs.(1a) and (1b), the transconductance of output transistors can be adjusted through the transfer current ratio  $\alpha$ . The simulation shows that proper value of  $\alpha$  can result in very high transconductance

For the input voltage with the amplitude in between  $V_{LOW}$  and  $V_{HIGH}$ , the circuit will operate as a conventional voltage follower with an enhanced transconductance and the reduced gate-source voltage

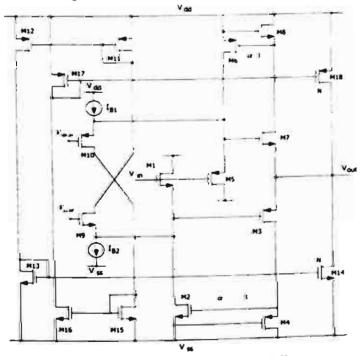

Figure 2. Proposed rail to rail voltage follower

mismatch. By using Eqs.(1a) and (1b), the output impedance of the circuit is given by

$$R_{o} = \left(\frac{1}{g_{m3}} - \frac{\alpha}{g_{m1}}\right) \left[\left(\frac{1}{g_{m7}} - \frac{\alpha}{g_{m5}}\right)\right]$$

(2)

If the input voltage is lower than  $V_{LOW}$ , the bias current IB2 for both transistors M1 and M9, which are connected as a differential amplifier, mostly becomes the drain current of M9 and is mirrored by two current mirrors M11-M12 and M13-M14. M14, which has its width N-times that of M13, now acts as bias current for the upper voltage follower(M5-M8). The output is capable to swing within one overdrive (VDSAT14) of the negative supply with the output impedance  $R_{O(LOW)}$  given by  $1/g_{m_1} - \alpha/g_{m_2}$ . Similarly, if the input voltage is higher than  $V_{HIGH}$ , the bias current  $I_{B1}$  for transistors M5 and M10, which are connected as a differential amplifier, mostly becomes the drain current of M10 and is mirrored by two current mirrors M15-M16 and M17-M18. M18, which has its width N-times that of M17, now acts as bias current for the lower voltage follower (M1-M4). The output in this case is capable to swing within one overdrive (VDSATIS) of the positive supply with the output impedance  $R_{O(HIGH)}$  given by  $1/g_{m3} - \alpha/g_{m1}$

A low quiescent current of the circuit are obtained by properly selecting biasing currents  $I_{B1}$  and  $I_{B2}$  and two bias voltages  $V_{HIGH}$  and  $V_{LOH}$ . We have chosen the  $V_{HIGH}$  and  $V_{LOH}$  to be 0.5 V and -0.5 V and  $I_{B1}$  and  $I_{B2}$  to be 10  $\mu$ A respectively. The quiescent current as a result is found to be 550  $\mu$ A.

#### 3. EXPERIMENTAL RESULTS

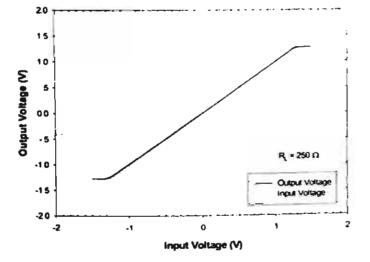

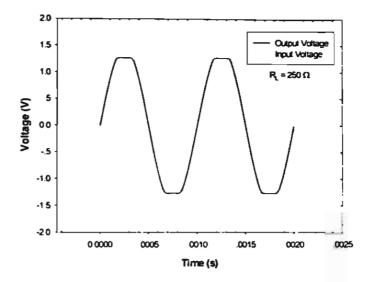

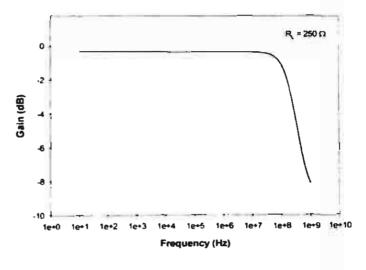

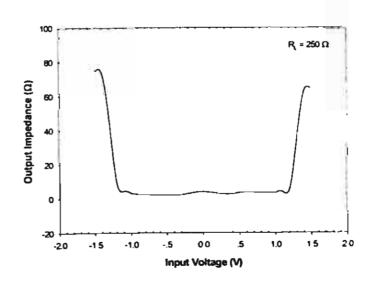

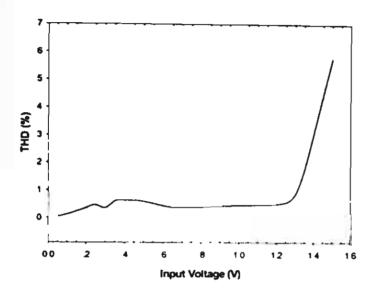

To evaluate the performance of the proposed circuit, the simulation is performed using HSPICE with a standard twin well 0.6 µm CMOS technology. All W/L values of the transistors used in the circuit are summarized in Table I. It is noted that the mobility of the electron in this process is approximately four times that of hole and the transfer current ratio  $\alpha$  used in this work is around 1/8. simulations results show high performance characteristics. namely low output impedance, low harmonic distortion. large linear output voltage swing, wide bandwidth and low The proposed voltage follower is power dissipation. connected to drive  $\pm 1.25$  V to 250  $\Omega$  load and the highest output impedance of the circuit is found to be less than 3.8  $\Omega$  while the harmonic distortion is less than 0.5 percent, ors Figure 3 shows DC transfer characteristics of the circuit with the same load. Dotted and solid lines represent input and output waveform respectively. As seen, the output can trace the input over a wide range linearly. Figure 4 show output waveform of the circuit with the input signal is 1kHz at 1.5V<sub>P.P.</sub> Figure 5 shows a frequency response of the circuit. The cut off frequency is found to be 237MHz. Figure 6 shows the output impedance of the proposed follower. It can be seen that low output impedance can be obtained, in the range of operation (±1.25V) with maximum value of 3.8Ω. Figure 7 show the THD versus the input voltage for 1kHz sinusoidal signal. The power dissipation is 5.2mW under quiescent condition.

#### 4. CONCLUSIONS

$\pm 1.5 V$  high performance CMOS rail to rail voltage follower is presented. The circuit is based on the symmetrical class AB voltage follower and can operate under supply voltages of  $\pm 1.5 V$ . The proposed circuit has power dissipation of 5.2mW under quiescent condition and can drive  $\pm 1.25 V$  to  $250 \Omega$  load with a total harmonic distortion of less than 0.5 percent and cut off frequency of 237 MHz. The maximum output impedance is less than 3.8  $\Omega$ . Although simple, the proposed circuit enables the output transistors to drive load efficiently.

Table 1. Aspect ratio of transistors

| Transistors | Aspect Ratios |

|-------------|---------------|

| M1,M2,M9    | 55/1          |

| M3,M4       | 750/0.6       |

| M5,M6,M10   | 220/1         |

| M7,M8       | 450/0.6       |

| M11,M12,M17 | 4.6/1         |

| M13,M15,M16 | 1.2/1         |

| M14         | 380/0.6       |

| MI8         | 1305/0.6      |

Figure 3. DC transfer characteristics

Figure 4. Output waveform

Figure 5. Frequency response of the proposed follower

Figure 6. Output impedance

Figure 7. Total harmonic distortion (THD)

#### REFERENCES

- Ahuja, B.K., Gray, P.R., Baxter, W.M., and Uchara, G.T., "A programmable CMOS dual channel interface processor for telecommunications applications," IEEE J. Solid-State Circ., Vol. SC-19, pp. 892-899, Dec. 1984.

- [2] Brehmer, K.E., and Wieser J.B., "Large swing CMOS power amplifier," IEEE J. Solid-State Circ., Vol. SC-18, pp. 624-629, Dec. 1983.

- [3] Fisher J.A., "A high performance CMOS power amplifier," IEEE J. Solid-State Circ. Vol. SC-20, pp. 1200-1205, Dec. 1985.

- [4] Nagaraj, K., "Large-swing CMOS buffer amplifier," IEEE J. Solid-State Circ., Vol. SC-24, pp.181-183, Feb. 1989.

- [5] Mistlberger, F., and Kock, R., "Class AB High swing CMOS power amplifier," IEEE J. Solid-State Circ., Vol. SC-27, pp. 1089-1092, July 1992.

- [6] Sekerkiran, B., "A compact rail-to-rail output stage for CMOS operation amplifiers," IEEE J. Solid-State Circ., Vol. SC-34, pp. 107-110, Jan. 1999.

- [7] Kadanka, P., and Rozsypal, A., "Rail-to rail voltage follower without feedback", Electronics Letters, Vol. 36, pp. 104-105, Jan. 2000.

- [8] Manetakis, K., and Toumazou, C., "A new high-frequency very low output-impedance CMOS buffer," IEEE International Symposium on Circuits and Systems, Vol. 1, pp. 485-488, 1996.

# A Physics-Based Bidirectional Model of Hot-Carrier-Induced nMOSFET Degradation Based on Exponential Interface State Profile

Weerayoot Chaisirithavornkul and Varakorn Kasemsuwan

Department of Electronics, Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang,

Ladkrabang Dist., Bangkok, 10520, Thailand

Phone: 66-2-326-4222 Ext.102, Fax: 66-2-739-2398, e-mail: kkvarako@kmitl.ac.th

Abstract-- A bidirectional DC model of n-MOSFET using exponential interface state profile is proposed. The model employs single physically based exponential expression to describe localized distribution of the interface states along the channel. The saturation voltage as a function of a position along the channel due to localized interface states is taken into account. Several short-channel effects including vertical and lateral field degradations, saturation velocity, parasitic source-drain resistances, channel length modulation are included. The predictions of the model agree well with the experimental data.

#### I. INTRODUCTION

At present, MOS device size has been scaled down without proportional reduction of supply voltages resulting in very high electric field especially near the drain end. Such high electric field creates hot carriers causing long term reliability concerns of the device operation. One of the main concerns is the injection of high energy electrons resulting in localized interface trap generation.

Several attempts [1-5] have been proposed to model the device degradation due to interface trapping  $N_{tr}$ . Hsu et al. [2] employed uniform distribution of  $N_n$  throughout the channel while Chung et al [3] used uniform distribution of  $N_{ii}$  only in the high field region(near the drain). The model accuracies are questionable as the interface trapping generation is a direct result of hot carriers which is caused by high electric field. It is well known that the electric field is not constant but increasing in the cosine hyperbolic trend [7] near the drain and thus uniform distribution is questionable. Chen et al. [1] and Leblebici et al. [4] proposed spatial dependent  $N_{ii}(y)$  in the linear form in damaged region and assumed zero elsewhere. In their model, such spatial dependent  $N_a(y)$  has been however averaged to simplify the drain current expression and therefore the localized effects of  $N_n(v)$  are not properly accounted for. In addition, two expressions are used to describe interface state profile causing a discontinuity in the model. Quader et al.[5] proposed the bidirectional model based on a uniform interface state in the high field regions. The uniform distribution is questionable as stated previously. The mobility as a function of  $N_n(y)$  is again assumed average value. In addition, the current deviation from the pre-stressed device is calculated using superposition principle which is invalid since effects of the interface states from source and drain ends are not completely uncorrelated.

In this paper, a bidirectional DC model of n-MOSFET using exponential interface state profile is proposed. The model employs single exponential expression to describe localized distribution of  $N_n(y)$  making the prediction results continuous. The model does not assume any average value and thus fully

accounts for localized effects of  $N_u(y)$ . The saturation voltage as a function of a position in the channel due to localized  $N_u(y)$  is taken into account. The resulting model provides physical explanation of the drain current degradation.

#### II. MODEL

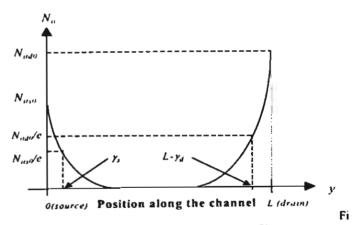

In this work, single expression of the interface state profile is employed and given as

$$N_{u}(y) = N_{us0} \cdot e^{(-y/\gamma_s)} + N_{ud0} \cdot e^{(y-L)/\gamma_d}$$

(1)

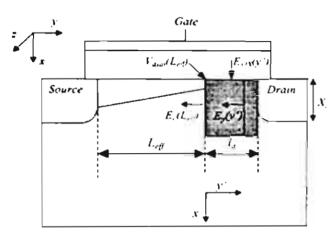

where y, L,  $N_{iii0}$  and  $N_{iid0}$  are location along the channel, channel length, interface state densities at the source and drain ends respectively.  $y_s$  and  $y_d$  are fitting parameters used to determine the shape of the interface state profile as shown in Fig. 1. As seen, the interface state at drain and source ends are described using single physically based exponential expression and thus the problem of the discontinuity in the current voltage characteristic created by interface state profile has been avoided. Eq. (1) will be used in developing DC model instead of employing an average value as conventionally done in other research works[1-5] and therefore the localization of interface state is taken into account properly.

g. 1 Interface state distribution profile.

The drain current of the hot-carrier-induced MOSFET is

$$I_p = WQ_*(y)v(y) \tag{2}$$

where W,  $Q_m(y)$  and v(y) are channel width, charge density and drift velocity given by

$$v(y) = \frac{\mu_{ell}}{(1 + KN_{ell}(y))(1 + \frac{E_{ell}}{E_{ell}(y)})} \cdot E_{ell}$$

and

$$\mu_{ell} = \frac{\mu_{ol}}{1 + \theta(V_{ell} - V_{pll})}$$

$\mu_0$ ,  $E_{co}$ ,  $\theta$  and K are low field mobility, lateral electric field, vertical mobility degradation factor and fitting parameter accounting for the mobility degradation due to interface state.  $E_c(y)$  is critical electric field given by  $E_{co}(I + K N_u(y))$  and  $E_{co}$  is critical electric field of the pre-stressed devices[1].

The charge density  $Q_m(v)$  is[1]

$$Q_{\pi}(y) = C_{xx}(V_{gy} - V_{DH} - 2a_0V(y) - \Delta V_{FB}(y))$$

(3)

where  $C_{oi}$ ,  $V_{TH}$ ,  $a_o$ , V(y) and  $\Delta V_{FB}(y)$  are capacitance, threshold voltage, a Taylor's series correction factor, channel potential and localized flat band voltage variation as a result of interface state given by  $qN_o(y)/C_{oi}$  respectively

Substituting (1) into  $q \nabla_x(y) C_{sx}$  for  $\Delta V_{FS}(y)$  and  $Q_{\omega}(y)$  and Wy into (2) and integrating the result from the source to the drain ends yield the drain current in the linear region,  $I_{DL}$ , as

$$I_{2d} = \frac{W \mu_{ab} C_{ijk} \left[ (k_{ab} - k_{ij}) + k_{ab} (k_{ab}) - k_{ab}^{2} (-q k_{ab}) (k_{ab}) C_{ij} \right]}{k + KA (k_{ab}) + k_{ab} E_{ij}}$$

(4)

where

$$\begin{split} A_{i}(L_{eff}) &= -\gamma_{i}N_{exp}(k_{i}-1) + \nu_{j}N_{ex}\left[k_{i} - \exp(L/\gamma_{i}) - \exp(-L/\gamma_{i})\right] \\ A_{i}(L_{eff}) &= \gamma_{i}^{-1}N_{exp}\left[1 - (\frac{L_{eff}}{\gamma_{i}} + 1)k_{i} + \gamma_{e}^{-1}N_{exp}\left[1 + (\frac{L_{eff}}{\gamma_{i}} + 1)/k_{i}\right] \exp(-L/\gamma_{i}) \right] \\ A_{i}(L_{eff}) &= \frac{\eta_{i}}{L_{eff}}A_{i}(L_{eff}) + 2\frac{(1 - \eta_{i})}{L_{eff}}A_{i}(L_{eff}) \\ k &= \exp(-L_{eff}/\gamma_{i}), \quad k_{i} = \exp(-L_{eff}/\gamma_{i}) \end{split}$$

and  $L_{eff}$  is the channel length L. The value of  $L_{eff}$  (see Fig. 2) will be modified to L- $l_{eff}$  when device operates in the saturation region(discussed later). As seen, the current expression in (4) is a simple analytical expression and derived based local interface state in (1) without using an average value,  $\overline{N}$ .

The drain current in (4) assumes zero parasitic drain  $R_d$  and source resistances  $R_t$ . Such assumption is invalid especially for very short channel devices. To account for this effects, one can use the fact that  $V_{gs} = V_{GS} - R_t I_{DL}$ ,  $V_J = V_D - R_J I_{DL}$  and  $V_t = V_S + R_t I_{DL}$  where  $V_{GS}$ ,  $V_D$  and  $V_S$  are actual applied voltages.

The drain current in (4) including  $R_d$  and  $R_s$  is therefore given by

$$I_{OL} = \frac{-B_1 - \sqrt{B_2}^2 - 4 B_3 B_3}{2B_2}$$

(5)

where

$$\begin{split} B_1 &= (R_s + R_d) \left\{ \frac{1}{E_{c0}} + W \mu_{eff} C_{OX} \left( R_s - a_n (R_d - R_s) \right) \right\} \\ B_2 &= W \mu_{eff} C_{OX} \left\{ \frac{q}{C_{OX}} \left( R_s + R_d \right) A_2 (L_{eff}) + 2 a_n (R_s \cdot V_s + R_d \cdot V_D) \right\} \\ &- R_s (V_{OS}) + (V_{GS} - V_{DH}) (R_s + R_d) \\ &- (L + K \cdot A_0 (L_{eff}) + \frac{V_{OS}}{E_{c0}}) \\ B_1 &= W \mu_{eff} C_{OX} \left\{ (V_{GS} - V_{DH}) (V_{OS}) - a_0 (V_D^2 - V_S^2) - \frac{q}{C_{OX}} (V_{OS}) A_2 (L_{eff}) \right\} \end{split}$$

When the drain voltage  $V_{ds}$  is increased upto the onset of saturation voltage,  $V_{dsaro}$ , electron at the drain end moves with the saturation velocity,  $v_{sat}$ , and the device is known to operate at the onset of the saturation region. If  $V_{ds}$  is greater than  $V_{dsaro}$ , the point where electron moves with saturation velocity moves toward the source end and known as channel length modulation. In this case, device can be divided into two sections. The first section extends from the source end to the velocity saturation point,  $L_{eff}$ , which has channel potential of  $V_{dsar}/L_{eff}$ . The second section extends from the velocity saturation point to the drain end and is given by modulation length  $l_d$ .

One can find the drain current in the saturation region by substituting (3) into (2) with v(y) replaced by  $v_{yat}$  as

$$I_{DS} = WC_{QA}(V_{gS} - V_{TH} - 2a_0 \cdot V_{dsat}(L_{eff}) - \Delta V_{FB}(L_{eff}))v_{sat}$$

(6)

To compute  $V_{dsat}(L_{eff})$ , one has to replace  $V_{ds}$ ,  $V_d$ ,  $V_s$  in (4) by  $V_{dsat}(L_{eff})$ ,  $V_{dsat}+I_{DS}R_s+V_S$  and  $V_S+I_{DS}R_s$  respectively and equating the result to (6) to yield

$$V_{nor}(L_{eff}) = (-H_1 - \sqrt{H_1^2 - 4/H_1/H_1})/(2H_1)$$

(7)

where

$$\begin{split} H_{1} &= -2a_{\alpha}\rho\bigg(\frac{1}{E_{,0}} + W\mu_{,cl}C_{OA}R_{+}(1+2a_{o})\bigg) + W\mu_{,cl}C_{OA}a_{\alpha}, \\ H_{2} &= \rho\bigg[V_{ob} - V_{ml} - q\frac{N_{n}(L_{cl})}{C_{OA}}\bigg]\bigg[\frac{1}{E_{co}} + W\mu_{,cl}C_{OA}R_{+}(1+2a_{a})\bigg] \\ &= 2a_{o}\rho\big[L_{cl} + K \cdot A_{a}(L_{cl})\bigg] \\ &= -W\mu_{,cl}C_{OA}\bigg[V_{ob} - V_{ml} - 2a_{a} \cdot V_{s} - \frac{q}{C_{OA}}A_{2}(L_{cl})\bigg], \\ H_{A} &= \rho\bigg[V_{ob} - V_{ml} - \frac{qN_{a}(L_{cl})}{C_{OA}}\bigg]\bigg[L_{cll} + K \cdot A_{a}(L_{cll})\bigg], \\ \rho &= \frac{WV_{ob}C_{OA}}{1+WV_{ob}C_{OA}R_{s}}. \end{split}$$

To evaluate (6) and (7), one needs to know the value of  $L_{eff}$ . This  $L_{eff}$  can be obtained by applying a quasi two dimensional approximation (QTDA) to rectangular Gaussian box (shaded area in Fig. 2) in the second section including interface state given in (1) yields

$$\varepsilon_{n} \int_{0}^{w} \int_{0}^{x_{0}-1} E_{\varepsilon}(L_{eff}) dx dz - \varepsilon_{OA} \int_{0}^{A} \int_{0}^{M} E_{OA}(y^{\varepsilon}) dy dz \\

- \varepsilon_{n} \int_{0}^{w} \int_{0}^{x_{0}-1} E_{\varepsilon}(y^{\varepsilon}) dx dz = \int_{0}^{w} \int_{0}^{M} \int_{0}^{x_{0}-1} (Q_{-n}^{\varepsilon} + Q_{-n}^{\varepsilon} + Q_{-n}^{\varepsilon}) dx dy dz$$

(8)

$$V_{ds} = V_{dsac}(L_{eff}) + \frac{q}{C_{sc}} \left( \frac{N_{sc}(L_{eff}) + \left\{ \frac{\exp(l_{d}/l - l_{d}/\gamma_{d})}{(\gamma_{d} - l)} - \frac{\exp(l_{d}/\gamma_{d} - l_{d}/l)}{(\gamma_{d} + l)} \right\} \cdot \frac{l \cdot N_{sd0}}{2} + \frac{N_{sd0} \cdot \gamma_{d}^{2}}{(l^{2} - \gamma_{d}^{2})}}{l^{2} + \frac{(l^{2} - \gamma_{d}^{2})}{(l^{2} - \gamma_{d}^{2})} - \left\{ \frac{\exp(-l_{d}/l - L_{eff}/\gamma_{d})}{(l - \gamma_{d})} + \frac{\exp(l_{d}/l - L_{eff}/\gamma_{d})}{(l + \gamma_{d})} \right\} \cdot \frac{l \cdot N_{es0}}{2}}{l^{2}} + E_{c} \cdot l \cdot \sinh(\frac{l_{d}/l}{l}) \quad where \quad l = \sqrt{\frac{E_{ss}X_{l}}{\lambda C_{OB}}}$$

(9)

where  $X_j$  is junction depth and  $\lambda$  is a fitting parameter. Differentiating (8) with respect to y' and z gives a second order differential equation which can be solved subjected to proper boundary conditions,  $E_x(y'=0) = E_c$  and  $V(y'=l_d) = V_{ds}$ , to give (9).

Fig. 2 Cross section of MOSFET and Gaussian box

As seen, (9) has one unknown, i.e.  $l_d$ , and can be found using Newton-Raphson method. We found that  $l_d$  is obtained after a few iterations (less than 12 iterations with initial guessed  $l_d$  computed without interface states). It is instructive to note that the potential at the point of saturation velocity,  $V_{dial}(L_{eff})$ , is not a constant. This is partly due to the fact that the interface state is changing along the channel

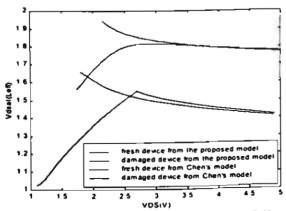

Fig. 3 shows  $V_{diat}(L_{eff})$  as a function of  $V_{DS}$  from the proposed model. The fitting parameters  $N_{idO}$ , K and  $\chi_d$  are  $4.5 \times 10^{11}$  cm<sup>-2</sup>,  $4.9 \times 10^{12}$ cm and  $5.1 \times 10^{16}$ cm respectively. As seen, our model gives continuous curve while it was shown discontinuous in Chen et al.[1]. Such discontinuity in  $V_{diat}(L_{eff})$  can cause discontinuity of the final drain current.

Fig. 3 Saturation voltages  $V_{dsat}(L_{eff})$  as a function of  $V_{DS}$  from the proposed model compared to Chen et al.[1], at  $V_{GS} = 5$  V.

#### III. RESULTS AND DISCUSSION

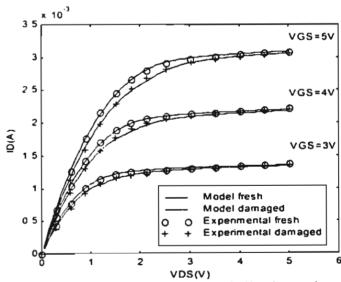

The model results have been compared with the experimental data[4]. The device has the channel length L and width W of 1  $\mu$ m and 10 $\mu$ m. Gate oxide thickness  $t_{ox}$  is 20nm. Effective substrate doping concentration  $N_a$  is  $5.0 \times 10^{16} \text{cm}^{-3}$ .  $\mu_0$ ,  $v_{sai}$ ,  $\theta$ ,  $a_0$ ,  $\lambda$ ,  $R_s$  and  $R_d$  are  $633 \text{cm}^2/\text{Vs}$ ,  $8.4 \times 10^{6}$  cm/s,  $0.11 \text{ V}^{-1}$ , 0.58, 3.35 and  $35\Omega$  respectively. Because the post-stress device is performed in one direction,  $N_{us0}$  is therefore zero while  $N_{ud0}$  is  $4.5 \times 10^{11}$  cm<sup>-2</sup>. K and  $\gamma_d$  are  $4.9 \times 10^{12}$  cm and  $5.1 \times 10^{6}$  cm. Fig. 4 shows a comparison of pre- and post-stress current-voltage characteristic. As seen, a good agreement between the predictions from this model and the experimental data [4] over a wide range of biasing conditions is obtained. It is noticed that the effect of the interface state is obvious in the linear region while it is negligible in the saturation region. This is because the modulation length  $l_d$  increases for an increasing  $V_{DS}$  making the effect of the interface state, mostly located near the drain, less pronounced.

Fig. 4 Comparison of pre- and post- stress  $I_D$ - $V_{DS}$  characteristic. Degraded device ( $W=10~\mu\text{m}, L=1~\mu\text{m}, t_{ox}=20~\text{nm}$ ) was stressed at  $V_{DS}=6.5V$ ,  $V_{GS}=2.6~V$  for 423 hours [4].

Our model can be extended to include the effect of time dependent degradation (age). To calculate generation of interface state, one can use  $\Delta N_{ii}$  generation expression [6]

$$\Delta N_{u} = C \left[ t \frac{I_{d}}{W} e^{-\frac{\Phi_{n}}{Q} M E_{n}} \right]^{n} \tag{10}$$

where C and n are fitting parameters.  $\lambda$ ,  $\phi_n$ ,  $E_m$  and t are electron mean free path, critical energy that electron possess to create interface state(3.7 eV), maximum lateral electric field in the channel and time for this stressing respectively. The generated  $\Delta N_n$  is then used in the purposed model to predict the drain current for a given stressing time.

#### IV. CONCLUSIONS

A physics-based bidirectional model of n-MOSFET including interface state effects is proposed. The model does not use an average value of  $N_n(y)$  and thus localized effects are accounted for properly. Single physically exponential interface state expression is used in developing model making model continuous over a wide range of biasing conditions. The predictions of the model agree well with the experimental data[4]

#### V. ACKNOWLEDGEMENT

This work is supported by Thailand Research Fund (TRF)(grant no PDF 74 2544)

#### REFERENCES

- [1] Y.S. Chen, T.H. Tang and S.L. Jang, "Modeling of hot-carrier-stressed characteristics of nMOSFETs," Solid-State Electronics, V.39, pp. 75-81, 1996.

- [2] F.-C. Hsu and S. Tam, "Relationship between MOSFET degradation and hot-electron-induced interface-state generation," IEEE Electron Devices Lett., Vol. 5, pp.50-52, Feb. 1984.

- [3] J.E. Chung, P.K. Ko and C. Hu, "A model for hot-electroninduced MOSFET linear current degradation based on mobility reduction due to interface-state generation," IEEE Trans. Electron Devices, Vol. 38, No. 6, pp.1362-1370, Jun. 1991.

- [4] Y. Leblebici and S.M. Kang, "Modeling of nMOS transistors for simulation of hot-carrier-induced device and circuit degradation," IEEE Trans. Comp-Aided Design, Vol. 11, pp. 235-246, Feb. 1992.

- [5] K.N. Quader, C.C. Li, R. Tu, E. Rosenbaum, P. Ko and C. Hu., "A bidirectional NMOSFET current reduction model for simulation of hot-carrier-induced circuit degradation," IEEE Trans Electron Devices, Vol.40, pp. 2245-2254, Jun. 1993.

- [6] C. Hsu, S.C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan and K. W. Terrill, "Hot-Electron-Induced MOSGET Degradation-Model, Monitor, and Improvement," IEEE Trans. Electron Devices, Vol. 32, No. 2, pp. 375-385, Fcb. 1985.

- [7] W. Li, J. S. Yuan, S. Chetlur, J. Zhou and A. S. Oates, "An improved substrate current model for deep submicron MOSFETs," Solid State Electronics, Vol. 44, pp. 1985–1988.

ภาคผนวก ข สำเนาบทความงานวิจัยที่ยังคงต้องรอผลการพิจารณาตอบรับ

| ลำดับที่ | ชื่อบทความ                                                                                                                                                                        | หน้า  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 1.       | An Analytical Model of Short Channel MOSFET Including Velocity Overshoot (מומור International Journal of Electronics)                                                             | 45-53 |

| 2.       | A 3Volt High Frequency and Low Input Impedance CMOS  Current-Mode Precision Full-Wave Rectifier  (212 813 The Institute of Electronics, Information and  Communication Engineers) | 54-57 |

| 3.       | High-Speed Low Input Impedance CMOS Current Comparator (115 013 IEEE Transactions on Very Large Scale Integration Systems)                                                        | 58-64 |

# AN ANALYTICAL MODEL OF SHORT CHANNEL MOSFET INCLUDING VELOCITY OVERSHOOT

#### Varakorn Kasemsuwan

Department of Electronics, Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang(KMITL), Chalongkrung Road, Bangkok 10520, THAILAND

Tel: 662 326-4222 Ext. 102, Fax: 662 739-2398 Email: kkvarako@kmitl.ac.th

Index Terms MOSFET devices, velocity overshoot.

Abstract In this paper, an analytical model for short channel MOSFET including velocity overshoot is proposed. The model is developed based on the solution of energy balance equation under the assumption of displaced Maxwellian distribution. The resulting mobility model is an augmented version of a conventional mobility model and all parameters involved are physical parameters. The model also includes the effects of the mobility degradation, channel length modulation, drain induced barrier lowering(DIBL) and parasitic drain source resistance. The theoretical predictions of the model are compared with the experimental data and shown to be in good agreement over a wide range of bias conditions.

#### I. INTRODUCTION

Velocity overshoot is becoming more prominent as MOSFET dimension reduced to the deep submicron regime(Ono et al. 1995, Sai-Halasz et al. 1988). This non local effect is a result of the carrier transit time that becomes comparable with the energy relaxation time. As a result, the field dependent mobility model assuming equilibrium with the lattice is not suitable for modeling the deep submicron devices. Several approaches(Kan et al. 1991, Tang et al. 1993, Sim 1995, Roldan et al. 1997, Kolhatkar and Dutta, 2000) have been proposed to take into account this nonlocal effects. The work by Kan et al. (1991) included the thermoelectric current to account for the velocity overshoot. The model is developed based on perturbation analysis on the carrier temperature using the energy balance equation. Tang et al. (1993) developed an improved hydrodynamic transport model. Both models however require numerical calculation making the models unsuitable for circuit simulator due to Sim (1995) has solved the energy balance equation inefficient computation time. incorporated with the drift-diffusion equation analytically. However the linear approximation is made on the integration of the thermoelectric current limiting the model validity. In addition, the current voltage characteristic has to be computed iteratively to include the effect of the parasitic drain and source resistance. Roldan et al. (1997) proposed the analytical model using augmented drift-diffusion velocity model. The model does not take into account parasitic drain source resistance. The transconductance has also been calculated but the model assumed no channel length modulation. Kolhatkar and Dutta et al. (2000) has proposed the analytical model including velocity overshoot effect using augmented drift-diffusion equation similar to that proposed by Roldan et al. (1997). The model however is valid for drain voltage less than the saturation voltage limiting the validity of the model. The derived transconductance is therefore limited to small drain voltages.

In this paper, an analytical model for short channel MOSFET including velocity overshoot is proposed. The model is developed based on the solution of energy balance equation under the assumption of displaced Maxwellian distribution. The resulting mobility model is an augmented version of a conventional mobility model and all parameters involved are physical parameters. The model also includes the effects of the mobility degradation, channel length modulation, drain induced barrier lowering and parasitic drain source resistance. The theoretical predictions of the model are compared with the experimental data with several gate lengths ranging from 0.07µm to 0.25µm and shown to be in good agreement over a wide range of bias conditions

#### II ANALYTICAL MODEL

The energy balance equation is written as(Lundstrom 1990)

$$J_n E = \nabla F_w + \frac{3}{2} nk \frac{T_e - T_O}{\tau_e} \tag{1}$$

where  $J_n$  and  $F_w$  are device current density and energy flux and given by

$$J_n = nq\mu E + qD_n \nabla n + \mu k n \nabla T_e \tag{2}$$

$$F_{w} = -\frac{5}{2} \frac{kT_{e}}{q} J - \frac{k^{2}}{q} n \mu T_{e} \nabla T_{e}, \tag{3}$$

k,  $T_e$ ,  $T_O$ ,  $\tau_e$ ,  $\mu = (\mu_O T_O)/(\theta T_e)$ ,  $\mu_O$  and  $\theta$  are Boltzmann constant, electron temperature, lattice temperature, energy relaxation time, temperature dependent electron mobility, low field mobility, vertical mobility degradation coefficient given by  $\theta = 1 + \theta_A (V_{GS} - V_T) + \theta_B V_{SB}$  where  $\theta_A$  and  $\theta_B$  account for degradation due to gate and body voltages respectively. Note that the first term on the right hand side(RHS) of equation (1) represents the gradient of energy flux while the second term represents the energy transferred from electrons to the lattice.

By substituting equations (2) and (3) into equation (1) and assuming that the gradients of energy flux and electron temperature are small (i.e., all the energy given to the electrons can transfer to the lattice simultaneously), one can solve for the electron temperature as

$$T_e^{Eq} = \frac{T_O}{2} + \left(\frac{T_O^2}{4} + \frac{2q\tau_e E^2 \mu_O T_O}{3k\theta}\right)^{1/2}.$$

(4)

However, if the gradient of the energy flux is taken into account, one can solve for the electron temperature as

$$T_e^{Non-Eq} = \frac{T_O}{2} + \left(\frac{T_O^2}{4} + \frac{2q\tau_e E^2 \mu_O T_O}{3k\theta}\right)^{1/2} - \frac{5}{6}\tau_e \frac{\mu_O}{\theta} T_O \frac{dE}{dy}.$$

(5)

It is instructive to note that  $T_e^{Eq}$  in equation (4) represents the electron temperature in equilibrium with the lattice while  $T_e^{Non-Eq}$  in equation (5) represents electron temperature in non-equilibrium with the lattice which is the case for submicron devices.

The temperature dependent electron temperature is related to electron and lattice temperatures(Baccarani and Wordeman 1985) as

$$\mu = \frac{\mu_O}{\theta} \frac{T_O}{T_c}.$$

(6)

If  $T_e$  in equation (6) is replaced with  $T_e$  in equations (4) and (5), the temperature dependent mobility in the equilibrium  $\mu^{Eq}$  and non-equilibrium  $\mu^{Non-Eq}$  become

$$\mu^{E_{d}} = \frac{\mu_{O}}{\theta} \frac{T_{O}}{\frac{T_{O}}{2} + \left(\frac{T_{O}^{2}}{4} + \frac{2q\tau_{e}E^{2}\mu_{O}T_{O}}{3k\theta}\right)^{1/2}},$$

(7)

$$\mu^{Non-Eq} = \frac{\mu_O}{\theta} \frac{T_O}{\frac{T_O}{2} + \left(\frac{T_O^2}{4} + \frac{2q\tau_c E^2 \mu_O T_O}{3k\theta}\right)^{1/2} - \frac{5}{6}\tau_c \frac{\mu_O}{\theta} T_O \frac{dE}{dy}}$$

(8)

Using the fact that  $(2q\tau_e E^2 \mu_o T_o)/(3k\theta) = (T_o^2/4)$  and 1/(1-x) = 1+x,  $\mu^{Non-Eq}$  in equation (8) can be rearranged as

$$\mu^{Non-Eq} = \frac{\mu_O}{\theta} \left( 1 + \frac{\alpha}{E} \frac{dE}{dy} \right) \frac{T_O}{\frac{T_O}{2} + \left( \frac{T_O^2}{4} + \frac{2q\tau_c E^2 \mu_O T_O}{3k\theta} \right)^{1/2}}$$

(9)

where  $\alpha = \sqrt{\frac{25}{24} \frac{k \tau_e \mu_o T_o}{q \theta}}$ .

From equations (7) and (8), it is obvious that the temperature dependent mobility in equilibrium can be modified to account for the case when electron and lattice are in non-

equilibrium by modifying the low field mobility term,  $\mu_0$ , in equation (7) with the effective mobility,  $\mu_0^{\it Eff}$

$$\mu_O^{Eff} = \frac{\mu_O}{\theta} \left( 1 + \frac{\alpha}{E} \frac{dE}{dv} \right) \tag{10}$$

As seen, the effective mobility  $\mu_0^{Eff}$  is augmented by the term which is responsible for the non-equilibrium condition and is a function of electric field. In this work, the electric field along the channel is given by [See (A-3) in the Appendix]

$$E = \frac{-m_2}{2\sqrt{m_1 - m_2 y}}. (11)$$

where

$$m_1 = \left(\frac{1}{2a_{\parallel}} \left[ (V_{GS} - V_T) - I_{DL} \left( \frac{1}{WC_{ov}\mu_o E_C} + R \right) \right] + I_{DL} R \right)^2$$

,  $m_2 = \frac{I_{DL}'}{a_o WC_{OX}\mu_o}$  and  $I_{DL}'$  is

the drain current without velocity overshoot(to be derived shortly).

The electric field in equation (11) includes several second order effects such as parasitic drain sources resistance, vertical and horizontal mobility degradations but not velocity overshoot which is the main objective of this work. The electric field along the channel including velocity overshoot effect can be obtained but it requires numerical approach making the model inefficient in term of time computation. As will be shown next, the electric field in equation (11) results in a simple analytical expression of the drain current which can predict the results well over a wide range of biasing conditions.

Using a piecewise model (Hoefflinger et al. 1979), the drift velocity in a low field near the source region is given by

$$v_d^{\Lambda o n - Eq} = \frac{\mu_O^{Eff} E}{1 + \left( E / E_C \right)} \tag{12}$$

where  $E_C$  is the critical electric field for velocity saturation,  $v_{sat}$ .

By combining equations (10), (11) and (12), one obtains

$$v_{d}^{\text{Non-Eq}} = \mu_{O} \left( 1 + \frac{\alpha m_{2}}{2 \left( m_{1} - m_{2} y \right)} \right) \frac{E}{1 + \left( E / E_{C} \right)}$$

(13)

As seen,  $v_d^{Non-Ed}$  in equation (13) reduces to conventional field dependent velocity model if electron energy can be transferred to the lattice immediately (i.e., energy relaxation time and thus  $\alpha$  is zero.). It is also instructive to note that the electric field expression given in equation (11) is valid only in the region where the gradual channel approximation is applied. For device operating in the saturation region, equations (11) and (13) are valid from the source terminal to the point where the channel potential is equal to saturation voltage.

The drain current including parasitic drain source resistance( $R_S = R_D = R$ ) is given by modifying the drain current in (Arora et al. 1994) as

$$I_D = WC_{ox} \left[ V_{GS} - V_T - 2a_o V(y) \right] v_d^{Non-Eq}$$

(14)

where W,  $C_{ox}$ ,  $V_{GS} = V_{GS} - I_D R$ ,  $V_T = 2\psi_B + V_{FB} + \gamma_e \sqrt{2\psi_B + V_{SB}} - \sigma V_{DS}$ , V(y),  $\sigma$  and  $a_o$  are the width of the channel, gate oxide capacitance per unit area, gate source voltage, threshold voltage, channel potential, drain induced barrier lowing(DIBL) factor and Taylor series correction factor respectively.

By combining equations (13) and (14), the drain current is

$$I_{D} = \mu_{O}WC_{ox} \left[ V_{GS}^{i} - V_{T} - 2a_{o}V(y) \right] \left( 1 + \frac{\alpha m_{2}}{2(m_{1} - m_{2}y)} \right) \frac{E}{1 + (E/E_{C})}$$

(15)

Integrating equation (15) over the whole channel length yields the drain current as(Dwight 1961)

$$I_{DL} = \frac{-k_{3} + \sqrt{4k_{1}k_{2} + k_{3}^{2}}}{2k_{1}} + \frac{\alpha\eta_{1}m_{2}}{4\eta_{2}} \left\{ 2 \left[ V_{GS} - V_{T} - \frac{1}{2a_{o}} \left( V_{GS} - V_{T} - \frac{I_{DL}'}{WC_{ox}\mu_{o}E_{C}} - I_{DL}'R \right) \right] \times \left[ \frac{1}{\sqrt{m_{1} - m_{2}L}} - \frac{1}{\sqrt{m_{1}}} \right) - \ln \left( 1 - \frac{m_{2}L}{m_{1}} \right) \right]$$

$$(16)$$

where  $\eta_1 = WC_{av}\mu_O$ ,  $\eta_2 = L + V_{DS}/E_C$ ,  $k_1 = (2/\eta_2)(\eta_1 R^2(2a_0 - 1) - R/E_C)$ ,  $k_2 = (\eta_1/\eta_2)(V_{GS} - V_T - a_0 V_{DS})V_{DS}$  and  $k_3 = (2k_2 R/V_{DS}) - (\eta_1/\eta_2)(2a_0 - 1)V_{DS}R + 1$ .

As seen, equation (16) consists of two current components: 1) the first term on the RHS which is the drain current contributed by the conventional mobility model or the drain current without velocity overshoot  $I_{DL}$ , and 2) the second term on the RHS caused by the augmented portion of velocity overshoot model in equation (13).

As the drain voltage increases, the lateral electric field at the drain terminal reaches the critical field  $E_C$ . The drain voltage responsible for that critical electric field is saturation voltage  $V_{DSAT}$  and can be found using similar approach to Chaisirithavornkul and Kasemsuwan (2000) as

$$V_{DSAT} = V_{DSAT}' + 2RI_{DSAT} \tag{17}$$

where  $V'_{DSAT} = (-k_4 + \sqrt{k_4^2 + \eta_1 k_5})/(2a_o R E_C \eta_1)$ ,  $k_4 = V_{GS} - V_T - 2a_o L E_C$ ,  $k_5 = 4a_o R E_C^2 L (V_{GS} - V_T)$  and  $I_{DSAT}$  is the drain current at the onset of saturation given by equation (16) with  $V_{DS}$  replaced by  $V'_{DSAT}$ .

For device operating in the saturation region, the validity of the gradual channel approximation region is reduced from L to  $L-L_m$  where  $L_m$  is the channel shortening due to the channel length modulation. The drain current in this region can be found by integrating equation (15) from the source end to the point of the saturation  $(L-L_m)$  and is given by

$$I_{DS} = \frac{I_{DSAT}}{1 - \frac{L_m}{\eta_2' + \eta_1 R V_{DSAT}'}}$$

(18)

where  $\eta_2'$  is  $\eta_2|_{V_{DS}=V_{DSAT}}$ .

In this work,  $L_m$  is found by using quasi-two dimensional approximation and retaining the first three terms after the Taylor series expansion of  $L_m$  in Ko (1989) as

$$L_{m} = l \ln \left( (1 + \chi) + \frac{\gamma}{l E_{C}} + \frac{\gamma^{2}}{2(l E_{C})^{2}} \right)$$

(19)

where  $\gamma = V_{DS} - V_{DSAT}$ ,  $l = \sqrt{\varepsilon_{SI}t_{OX}X_J/\varepsilon_{OX}}$  and  $\chi$  represents the Taylor series expansion correction factor. To avoid the negative value of  $L_m$  and to guarantee a smooth change in  $L_m$ .  $V_{DS}$  in equation (19) is replaced by a smoothing function  $V_{DSX}$  (Klos and Kostka 2000)

$$V_{DSX} = V_{DSAT}^{\prime} \left[ 1 + \frac{\ln\left(1 + e^{A(1 v_{DS}/v_{DSAT} - 1)}\right)}{\ln\left(1 + e^{A}\right)} \right]$$

(20)

The expression  $V_{DSX}$  in equation (20) gives  $V_{DS}$  and  $V'_{DSAT}$  when  $V_{DS} \square V'_{DSAT}$  and  $V_{DS} \square V'_{DSAT}$  respectively. Parameter A in equation (20) is used to control the smoothness of the curve.

#### III. RESULTS AND DISCUSSION

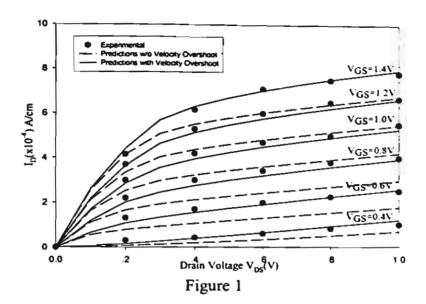

To verify the validity of the model, the model results have been compared with the experimental data(Sai-Halasz et al. 1988). The devices were fabricated with several gate lengths ranging from 0.07µm to 0.25µm with the oxide thickness of 4.5nm. Figure 1 shows the comparison between the theoretical predictions of current voltage characteristic(solid line), the theoretical predictions without velocity overshoot i.e., equation (16) with  $\tau_e$ =0ps(dash line) and the experimental data(dot)(Sai-Halasz et al. 1988). In the simulation, an effective doping concentration  $(N_4)$ , low field mobility  $(\mu_0)$ , energy relaxation time  $(\tau_e)$ , saturation velocity ( $v_{sat}$ ), parasitic drain source resistance (R), smoothing factor (A) and  $\chi$  are  $7 \times 10^{17}$  cm<sup>-3</sup>, 420 cm<sup>2</sup>/V·s, 0.3 ps,  $9 \times 10^6$  V/cm, 32  $\Omega$ , 10 and 0.12 respectively. As seen, the predictions show increasing differences in the drain current for larger applied drain source voltage  $V_{DS}$  due to the larger channel electric field and its gradient. For the device biased at  $V_{GS} = 0.8 \text{ V}$  and  $V_{DS} = 0.6 \text{ V}$ , the drain current including velocity overshoot effect can be 29% larger than the current without velocity overshoot. The agreements between the theoretical predictions and the experimental data are well obtained over a wide range of applied gate and drain voltages. Figure 2 shows the comparison between the theoretical predictions of the device transconductance  $g_m(solid line)$ , theoretical predictions without velocity overshoot(dash line) and the experimental data(dot)(Sai-Halasz et al. 1988) for different gate lengths(0.07μm-0.275μm) under 300K. The device transconductance in the linear and saturation regions can be calculated by taking derivative the drain currents in equation (16) and equation (18) with respect to  $V_{GS}$  respectively. As seen, there is a sharp increase in the transconductrance as the channel length decreases. The difference in the transconductance from the theoretical predictions with and without velocity overshoot is 10% for channel length of  $0.21\mu m$  and can go up to 20% when the channel length goes down to  $0.08\mu m$ . Reasonable agreements between the experimental data and the predictions from this model are obtained.

#### V. CONCLUSION

In this paper, an analytical model for short channel MOSFET including velocity overshoot is presented. The model is developed based on the velocity overshoot model obtained from the solution of energy balance equation under the assumption of displaced Maxwellian distribution. The mobility model is found to be an augmented model and all parameters involved are physical parameters. The model also includes the effects of the mobility degradation, channel length modulation, drain induced barrier lowering(DIBL) and parasitic drain source resistance. The theoretical predictions of the model are verified by comparing its predictions with the experimental data and shown to be in good agreement over a wide range of bias conditions.

# APPENDIX ELECTRIC FIELD EXPRESSION

Combining equations (12) and (14) and taking into account parasitic drain source resistance i.e.,  $V'_{GS} = V_{GS} - I'_{DL}R$ , yields the drain current in term of channel potential V(y) after some algebraic manipulation as

$$I'_{DL} = WC_{ax}\mu_{o} \left[ V_{GS} - V_{T} - 2a_{o}V(y) - I'_{DL} \left( R + \frac{1}{W\mu_{eff}C_{ax}E_{C}} \right) \frac{dV(y)}{dy} \right].$$

(A-1)

The channel potential V(y) can be obtained by integrating equation (A-1) from the source end to any position along the channel, y, subject to boundary condition  $V(y)|_{y=0} = I'_{DL}R$  as

$$V(y) = \sqrt{m_1} + I'_{DL}R - \sqrt{m_1 - m_2 y}$$

(A-2)

where

$$m_1 = \left\{ \frac{1}{2a_o} \left[ (V_{GS} - V_T) - I_{DL}' \left( \frac{1}{WC_{ax}\mu_O E_C} + R \right) \right] - I_{DL}'R \right\}^2$$

and  $m_2 = \frac{I_{DL}'}{a_o WC_{ax}\mu_O}$ .

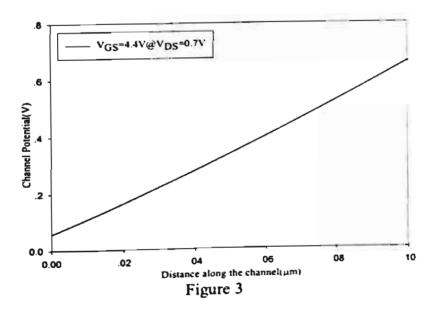

Figure 3 shows channel potential along the channel of the MOS transistor with channel length of  $0.1 \mu m$ . The gate and drain voltages are 4.4V and 0.7V respectively. The potential at the source( $\nu$ =0 in equation (A-2)) and the drain terminals( $\nu$ =0.1 $\mu m$  in equation (A-2)) are 0.056V and 0.644V respectively. The voltage at the source and the drain terminals are not zero and  $V_{DS}$  due to the voltage drop across parasitic drain and source resistances respectively. The electric field along the channel is given by the negative of the gradient of channel potential in equation (A-2) as

$$E = \frac{-m_2}{2\sqrt{m_1 - m_2 y}}. (A-3)$$

#### **ACKNOWLEDGEMENT**

This work is supported by a grant from "The THAILAND RESEARCH FUND(TRF)" under the grant number PDF/74/2544.

#### REFERENCES

- Arora, N. D., Rios, R., Huang, C. L. and Raol, K., 1994, PCIM: A physically based continuous short-channel IGFET model for circuit simulation. *IEEE Trans. Electron Devices*, 41, 988-997.

- Baccarani, G. and Wordeman, M. R., 1985. An investigation of steady-state velocity overshoot in silicon. *Solid-State Electron.*, 28, 407-416.

- Chaisirithavornkul, W., and Kasemsuwan, V. 2000. A physical model of short channel MOS transistor using trapezoidal Gaussian surface. *Proc. ICSE*, 2000, 24-28.

- Dwight, H.B., 1961, Table of Integrals and others mathematical data(Macmillan Publishing)

- Hoefflinger, B., Sibbert, H., and Zimmer, G., 1979. Model and performance of hot-electron MOS transistors for VLSI. *IEEE Trans. Electron Devices*, 26, 513-520.

- Kan, E. C., Ravaioli, U., and Chen, D., 1991. Multidimensional augmented current equation including velocity overshoot. *IEEE Electron Devices Lett.*, 12, 419-421.

- Klos, A., and Kostka, A., 2000. PREDICTMOS a predictive compact model of small geometry MOSFETs for circuit simulation and device scaling calculations. Solid State Electronics, 1145-1156

- Ko, P. K., 1989, Approaches to scaling in Advanced MOS Device Physics," N.G. Einspruch and G. Gildenblat, eds. VLSI Electronics; *Microstructure Science*, vol. 18, New York: Academic, pp. 1-37.

- Kolhatkar, J. S., and Dutta, A. K., 2000. A new mobility model to explain the transconductance overshoot effect observed in ultra short channel length MOSFETs. *Solid State Electron.*, 44, 691-696.

- Ono, M., Saito, M., Yoshitomi, T., Fiegna, C., Ohguro, T., and Iwai, H., 1995. A 40 nm gate length n-MOSFET. *IEEE Trans. Electron Devices*, vol. 42, 1822-1830.

- Sai-Halasz, G. A., Wordeman, M. R., Kern, D. P., Rishton S., and Ganin, E., 1988. High transconductance and velocity overshoot in NMOS devices at the 0.1 µm gate length level. *IEEE Electron Device Lett.*, 9, 464-466.

- Sim, J. H., 1995. An analytical deep submicron MOS device model considering velocity overshoot behavior using energy balance equation. *IEEE Trans. Electron Devices*, 42, 864-869.

- Tang, T. W., Ramaswamy, S., and Nam, J., 1993. An improved hydrodynamic transport model for silicon. *IEEE Trans. Electron Devices*, 40, 1469-1477.

- Roldan, J. B., Gamiz, F., Lopez, J. A. and Carceller, J.E., 1997. Modeling effects of electron velocity overshoot in a MOSFET. *IEEE Trans. Electron Devices*, 44, 841-846.

- Lundstrom, M., 1990, Fundamentals of Carrier Transport(X Modular Series on Solid State Devices, Addison Wesley Co.)

#### FIGURE CAPTIONS

- Figure 1. I-V Characteristic. Measured data(dot)[2], this model with velocity overshoot(solid line) and without velocity overshoot(dash line)

- Figure 2. Device Transconductance. Measured data(dot)[2], the model with velocity overshoot(solid line) and without velocity overshoot(dash line)

- Figure 3. Channel potential  $(V_{GS} = 4.4 \text{ V} @ V_{DS} = 0.7 \text{ V})$

800 - -- Model w/o Velocity Overshoot Proposed Model Expenmental

200 --- Model w/o Velocity Overshoot Proposed Model Expenmental

200 ---- Standard Length(µm) Figure 2

# 3Volt High Frequency and Low Input Impedance CMOS Current-Mode Precision Full-Wave Rectifier(PFWR)

#### Varakorn Kasemsuwan and Surachet Khucharoensin

#### Correspondence author:

Varakorn Kasemsuwan

Department of Electronics, Faculty of Engineering,

King Mongkut's Institute of Technology Ladkrabang (KMITL)

Chalongkrung Road, Bangkok 10520, THAILAND

Tel: 662 326-4222 ext. 102

Fax: 662 739-2398

E-mail: kkvarako@kmitl.ac.th

Subject categories: Analogue Electronics

Index Terms by subject categories: Analogue Processing Circuits

Keywords: Current-mode, Rectifier

# 3Volt High Frequency and Low Input Impedance CMOS Current-Mode Precision Full-Wave Rectifier(PFWR)

#### Varakorn Kasemsuwan and Surachet Khucharoensin

A high performance current-mode precision full-wave rectifier based on an improved Wilson current miller is proposed. All transistors are biased at low current resulting in small power dissipation(5.8 $\mu$ W). The input impedance of the circuit is very small(236 $\Omega$ ) and the circuit can operate at 100 MHz with only 0.21% mismatch between input and output signal currents for an input current of  $\pm 150\mu$ A.

Introduction: Precision rectifiers are one among very important circuit building blocks for analogue and digital signal processing, conditioning and instrumentation especially for low level signals. Applications include RMS to DC conversions and peak detectors. approaches have been proposed[1-5] to build precision rectifiers. Conventionally, precision rectifiers are based on diodes and opamps[1-2]. The rectifier however has a problem with a high distortion during the zero crossing of the input signal due to that the opamps have to recover during non-conduction/conduction transition with a finite small signal dV/dt (slew rate). The rectifiers are thus limited to a frequency performance well below the gain bandwidth product  $f_T$  of the amplifier. An improvement of the rectifier design was to use current conveyors and diodes[3-4]. The resulting circuits can operate at high frequency. However, the circuits are power hungry and quite large making them unsuitable for implementing in the large-scale integrated circuit. Recently, a high performance precision rectifier has been proposed[5]. The circuit consists of only three transistors and are biased with low current resulting in low The circuit can also total power dissipation(4.8µW). frequency(100MHz). However, the input impedance of the circuit is quite high(7.2k $\Omega$ - $47k\Omega$ ) posing a problem in the current-mode circuit design. In addition, the output signal is not symmetry during positive and negative input cycle.

Proposed precision full-wave rectifier(PFWR): Fig. 1 shows the proposed precision rectifier. The circuit is designed based on two precision half-wave rectifiers(M<sub>1a</sub>-M<sub>5a</sub> and M<sub>1b</sub>-M<sub>5b</sub>) operating alternatively during positive and negative input cycle. I<sub>in1</sub> and I<sub>in2</sub> are the input currents with the same magnitude but 180 degree out of phase. M<sub>5a,b</sub> are used to biased M<sub>1a,b</sub>-M<sub>4a,b</sub> on the edge of conduction. When I<sub>in1</sub> and I<sub>in2</sub> flows into node a and out of node b respectively, M<sub>3a</sub> cuts off while M<sub>3b</sub>, which is connected as a common gate, allows the input current I<sub>in2</sub> to flows through the load R<sub>L</sub>. Same explanation is applied when I<sub>in1</sub> and I<sub>in2</sub> flows out of node a and into node b respectively. As a result, the circuit works as a full-wave rectifier. The input impedance of the circuit(node a and b) are very low due to the negative feedback(shunt input) with in the loop M<sub>1a,b</sub>-M<sub>4a,b</sub>. To demonstrate this fact, when I<sub>in1</sub> flows into node a, voltage at node a, V<sub>a</sub>, is pulled high. The signal V<sub>a</sub> is amplified via M<sub>2a</sub>(common source) causing voltage at the drain of M<sub>2a</sub> and at the gate of M<sub>4a</sub> to go low. As a result, the source voltage of M<sub>3a</sub> is forced to be low. Straightforward circuit analysis shows the input impedance of the circuit given by

$$R_{in} = \frac{1}{g_{m1a,b} + g_{m3a,b} + g_{m2a,b}g_{m3a,b}(r_{o2a,b} / r_{o5a,b})}$$

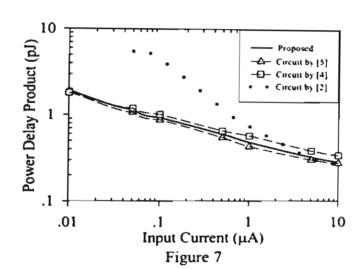

Performance of proposed precision full-wave rectifier (PFWR): To verify the circuit performance, HSPICE is used to simulate the proposed circuit using a standard  $0.5\mu m$  CMOS process. Fig. 2 shows input impedance of the proposed circuit (solid line) and that by [5] (dash line). As seen, our proposed circuit has relatively much lower input impedance. To the best of authors' knowledge, our circuit offers lowest input impedance (236 $\Omega$ ). Fig. 3 shows the comparison of the DC transfer characteristic of proposed circuit (solid line), circuit in [5] (dash line) and ideal output curve (triangle). A sharp corner at zero crossing point and good symmetry during positive and negative input cycle are well obtained. The mismatch obtained from the input and rectifier's output are 0.21% for an input current of  $\pm 150\mu A$ . Fig. 4 shows transient simulation of input signal (dot), our circuit (solid line) and [5] (dash line) for the input frequency of 100MHz. The results show that our circuit gives a good symmetry for both positive and negative input cycle at high frequency. Lastly, the total power dissipation is  $5.8\mu W$

Acknowledgement: This work is supported by Thailand Research Fund(TRF)(grant no. PDF. 74 2544).

#### References

- [1] Toumazou, C., and Lidgey, F.J.: 'Wide-band precision rectification', *IEEE Proc.* G., vol. 134, no.1, pp. 7-15, 1987.

- [2] Lidgey, F.J., Hayatleh, K. and Toumazou, C.: 'New current-mode precision rectifiers', *IEEE Inter. Symposium on Circuits and Systems*, pp. 1322-1325, 1993.

- [3] Tournazou, C., Lidgey, F.J., and Chattong, S.: 'High Frequency Current Conveyor Precision Full-Wave Rectifier', *Electron. Lett.*, vol. 30, no. 10, pp. 745-746, 1994.

- [4] Hayatleh, K., Porta, S., and Lidgey, F.J.: 'Temperature Independent Current Conveyor Precision Rectifier', Electron. Lett., vol. 30, no. 25, pp. 2091-2093, 1994.

- [5] Chang, C.C., and Liu, S.I.: 'Current-Mode Full-Wave Rectifier and Vector Summation Circuit', *Electron. Lett.*, vol. 36, no. 19, pp. 1599-1600, 2000.

Figure captions:

Fig. 1 Schematic diagram of the proposed precision full-wave rectifier(PFWR)

Fig. 2 Input impedance

— proposed circuit

— circuit by [5]

Fig. 3 DC Transfer Characteristic

∇ Ideal

— proposed circuit

---- circuit by [5]

Fig. 4 Transient response (100MHz input current)

O input current

--- proposed circuit

--- circuit by [5]

#### Table caption:

Table 1. Transistor's geometrical dimensions

Figure 1

Figure 2

Table 1

| Device                | W(µm) | L(µm) |

|-----------------------|-------|-------|

| $M_{1a,b} - M_{4a,b}$ | 0.5   | 0.5   |

| $M_{5a,b}$            | 7     | 2     |

| $M_6, \overline{M_7}$ | 10    | 2     |

## **High-Speed Low Input Impedance CMOS Current Comparator**

### Varakorn Kasemsuwan and Surachet Khucharoensin

#### Correspondence author:

Varakorn Kasemsuwan Department of Electronics, Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang (KMITL) Chalongkrung Road, Bangkok 10520, THAILAND

Tel: 662 326-4222 ext. 102

Fax: 662 739-2398

E-mail: kkvarako@kmitl.ac.th

Subject categories: Analogue Electronics

Index Terms by subject categories: Analogue Processing Circuits

Keywords: Current mode, Comparator

## High-Speed Low Input Impedance CMOS Current Comparator

### Varakorn Kasemsuwan and Surachet Khucharoensin

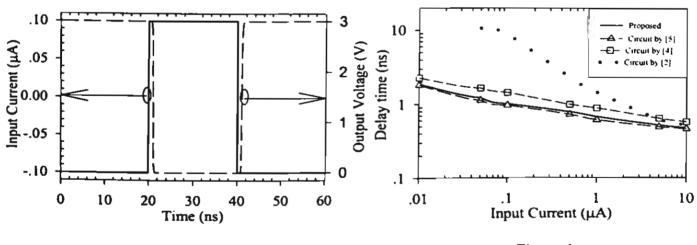

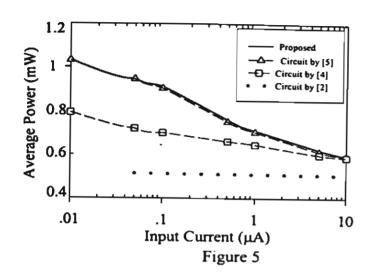

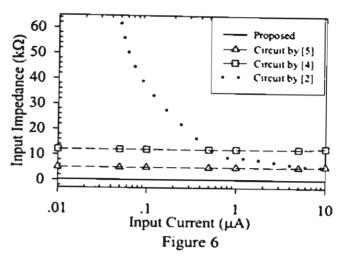

A simple high-speed low input impedance CMOS current comparator is proposed. The circuit uses improved Wilson current-mirror to perform a subtraction. Negative feedback is employed to reduce the input impedance of the circuit. HSPICE is used to verify the circuit performance with a standard 0.5 $\mu$ m CMOS technology. Simulation results demonstrate the propagation delay of 1.02 ns, average power consumption of 0.911 mW and input impedance of 137  $\Omega$  for  $\pm 0.1 \mu$ A input current at the supply voltage of 3V.

Introduction: In recent years, current-mode circuits become increasingly popular among analog circuit designers. This is mainly attributed to higher speed, larger bandwidth and lower supply voltage requirement compared to the voltage mode circuit counterpart. Current comparator is widely used as a building block of analog systems including A/D converters, oscillator, VLSI neural network and other signal processing applications. Several approaches have been proposed to implement current comparator [1-5]. Current mirror current comparator has been firstly proposed by [1]. The circuit consists of two cascode current mirrors. The circuit can not operate at high frequency due to high impedance at the output node. To increase frequency of the operation and, at the same time, to reduce the input impedance of the circuit, source follower input stage current comparator as shown in Fig. 1a) is then proposed[2]. The input part of the circuit consists of two transistors(M<sub>1</sub> and M<sub>3</sub>) connected as source follower to lower the input impedance while two transistors at the output (M2 and M<sub>4</sub>) are connected as complementary common source. The circuit however shows deadband region where the input impedance is quite high during input transition and thus limiting the speed of operation. A biasing method using current source[3] is proposed to alleviate this deadband problem. The circuit needs very well controlled current sources in addition to the requirement of a twin well process as the substrate of two diode connected transistors have to be tied to their sources. The input and output impedances of current comparator are further reduced by using a negative feedback approach[4-5]. The front end preamplifier circuit by[4] shown in Fig. 1b) is current source inverting amplifier with M<sub>r</sub> operating as a resistive feedback element while the front end preamplifier circuit by[5] shown in Fig. 1c) is a cascode current source inverting amplifier with M5 serving as a resistive feedback element. Their circuits exhibit low input and output impedances and the delay time is less than 1.5 ns for  $\pm 0.1 \mu A$  input current.

Up to present, most proposed current comparators[2-5] assumed input current I<sub>in</sub> as a subtraction(or difference) of the reference current(I<sub>REF</sub>) and the actual input current(to be compared with I<sub>REF</sub>). None of them shows the circuit that performs such subtraction. It is instructive to note that the subtraction circuit is also part of the current comparator and therefore previously reported simulation results, i.e., power dissipation, speed of operation and power delay product, are too optimistic as the subtraction circuit also consumes certain amount of power and exhibits certain delay time.