## รายงานวิจัยฉบับสมบูรณ์

โครงการ เทคนิควงจรแอนะลอกที่แรงดันไฟเลี้ยงและกำลังงานต่ำ<sup>†</sup>

สำหรับการประมวลผลสัญญาณชีวภาพแบบพกพาและปลูกฝัง

โดย อภิศักดิ์ วรพิเชฐ

10 สิงหาคม 2554

## รายงานวิจัยฉบับสมบูรณ์

โครงการ เทคนิควงจรแอนะลอกที่แรงดันไฟเลี้ยงและกำลังงานต่ำ

สำหรับการประมวลผลสัญญาณชีวภาพแบบพกพาและปลูกฝัง

อภิสัคดี วรพิเชฐ

มหาวิทยาลัยเทคโนโลยีมหานคร

สนับสนุนโดยสำนักงานกองทุนสนับสนุนงานวิจัย

และสำนักงานคณะกรรมการอุดมศึกษา

(ความเห็นของรายงานนี้เป็นของผู้วิจัย สกอ.ไม่จำเป็นต้องเห็นด้วยเสมอไป)

## Abstract

**Project Code:** RMU5180033

**Project Title:** **Very Low Voltage Low Power Analogue Techniques for Portable and Implantable Biomedical Signal Processing**

**Investigator:** **Apisak Worapishet**

**Mahanakorn University of Technology**

**E-mail Address:** [apisak@mut.ac.th](mailto:apisak@mut.ac.th)

**Project Period:** **15 May 2008 to 15 August 2011**

Today's advancement of state-of-the-art fine-line CMOS processing has made feasible the implementation of portable and implantable bio-medical integrated circuits and systems for ubiquitous healthcare applications. Crucial parameters for such devices include low power consumption and low supply voltage with adequate dynamic range. In this research project, we have developed analogue CMOS techniques in sub-threshold inversion operation for very low voltage and low power circuits. In particular, a sampled-data switch-current analogue signal processing based on CMOS memory transistors operating in sub-threshold operation has been introduced and analyzed in details. Also developed are the sub-threshold R-MOSFET tunable resistors and mixers for continuous-time analogue signal processing. These techniques show good promise for future implementation of low voltage low power bio-medical integrated filters which are indispensable building elements for portable and implantable bio-medical signal processing.

**Keywords:** **Low voltage circuits, low power circuits, sub-threshold CMOS circuits, bio-medical CMOS circuits**

## บทคัดย่อ

รหัสโครงการ: **RMU5180033**

ชื่อโครงการ: เทคนิควงจรแอนะลอกที่แรงดันไฟเลี้ยงและกำลังงานต่ำสำหรับ

การประมวลผลสัญญาณชีวภาพแบบพกพาและปลูกฝัง

ชื่อนักวิจัย: อภิศักดิ์ วรพิเชฐ

มหาวิทยาลัยเทคโนโลยีมหานคร

E-mail Address: [apisak@mut.ac.th](mailto:apisak@mut.ac.th)

ระยะเวลาโครงการ: 15 พฤษภาคม 2551 ถึง 10 สิงหาคม 2554

ปัจจุบัน ความก้าวหน้าด้านเทคโนโลยีการผลิตวงจรรวมซึ่งมีอัตราการเติบโตสูงมาก ได้ส่งผลให้ความสามารถสร้างระบบวงจรอิเล็กทรอนิกส์สำหรับอุปกรณ์พกพาและปลูกฝังได้ ทั้งนี้ สมรรถนะที่จำเป็นสำหรับอุปกรณ์เหล่านี้ที่สำคัญอย่างยิ่งคือการกินกำลังงานที่ต่ำ รวมถึงระดับแรงดันไฟเลี้ยงที่ต่ำ โดยที่ยังต้องคงไว้ซึ่งระดับของพิสัยพลวัตที่เพียงพอ สำหรับโครงการวิจัยนี้ได้ทำการพัฒนาเทคโนโลยีการแอนะลอกกำลังงานต่ำและแรงดันไฟเลี้ยงต่ำ ที่อาศัยมอสทรานชิสเตอร์ซึ่งทำงานในย่านต่ำๆ โดยเราได้ทำการพัฒนาและวิเคราะห์เทคนิคสวิทช์กระแสที่อาศัยหน่วยความจำมอสทรานชิสเตอร์ในย่านต่ำๆ ได้เริ่มสำหรับการประมวลผลสัญญาณเชิงสุ่ม นอกจากนี้ ยังได้พัฒนาตัวต้านทานปรับค่าได้และวงจรสมดุลสัญญาณที่อาศัยโครงสร้างตัวต้านทานและมอสทรานชิสเตอร์ ย่านต่ำๆ ได้เริ่มสำหรับการประมวลผลสัญญาณเชิงต่อเนื่อง เทคนิคที่นำเสนอเหล่านี้ ได้มีการพิสูจน์ให้เห็นว่าเหมาะสมกับการสร้างระบบวงจรกรองที่มีการกินกำลังงานต่ำ และมีความต้องการระดับไฟเลี้ยงที่ต่ำ ซึ่งเป็นองค์ประกอบที่มีความสำคัญต่อการประมวลผลสัญญาณชีวภาพยังในอุปกรณ์พกพาและปลูกฝังเป็นอย่างยิ่ง

คำหลัก: **Low voltage circuits, low power circuits, sub-threshold CMOS circuits bio-medical CMOS circuits**

# **Very Low Voltage Low Power Analogue Techniques for Portable and Implantable Biomedical Signal Processing**

## **1. Introduction**

Since its invention in 1958, integrated circuits technology has revolutionized electronic devices, which help transform the world into the so-called information age. This is made possible by its computing capability, inexpensive production, and tiny physical size. While the dominance of integrated circuits in data processing, communication and multi-media will continue into the foreseeable future, there has been considerable research effort in pushing the silicon technology into the realm of biology and medicine.

Today's advancement of state-of-the-art fine-line CMOS processing has made feasible the implementation of bio-medical integrated circuits and systems for ubiquitous healthcare applications, such as wearable health and wellness monitoring, as well as portable and implantable molecular detection platform for disease diagnosis, DNA sequencing etc [1]. Crucial parameters for such devices include low power consumption and low supply voltage with adequate dynamic range.

In this research project, we have developed analogue CMOS techniques in sub-threshold inversion operation for very low voltage and low power circuits and systems. Particular emphasis is given on techniques for implementations of integrated filters – one of the indispensable building blocks for bio-medical signal processing. A list of the technical contributions resulting from this project, along with their summary is given as follows:

- 1) Circuit development and performance analysis of very low supply voltage, low power sampled-data switch-current analogue signal processing based on CMOS transistors in sub-threshold operation :

The general performance of class AB switched currents (SI) is analysed using the general MOS equations, valid for all regions of operation. Using a figure-of-merit combining speed, dynamic range and power consumption, the overall performance is shown to improve progressively as the SI memory transistors' operating region is moved from strong inversion to moderate and then weak inversion. The analysis is validated firstly by experiment using transistor arrays and then by simulation using 0.35 $\mu$ m, 0.18 $\mu$ m and 90nm CMOS process data. After discussing non-ideal behaviour of the weak inversion memory cell, two practical designs are described: a cascoded class AB memory at 1.25V supply in the 3.3V, 0.35 $\mu$ m process and a two-step sampling class AB memory at 0.6V supply in the 1.8V, 0.18 $\mu$ m process, and each demonstrates good performance.

- 2) Circuit development and detailed analysis/design of sub-threshold R-MOSFET tunable resistors for very low supply voltage :

The sub-threshold R-MOSFET resistor structure which enables tuning range extension below the threshold voltage in the MOSFET with moderate to weak inversion operation is analyzed in detail. The principal operation of the sub-threshold resistor is briefly described. The analysis of its characteristic based on approximations of a general MOS equation valid for all regions is given along with discussion on design implication and consideration. Experiments and simulations are provided to validate the theoretical analysis and design, and to verify the feasibility at a supply voltage as low as 0.5V using a low-threshold devices in a 1.8-V 0.18  $\mu$ m CMOS process.

- 3) Circuit development and detailed analysis/design of sub-threshold R-MOSFET mixers for very low supply voltage :

An enhanced mixer topology suitable for very low supply voltage applications is developed. The circuit introduces a linear resistor network to the conventional mixer based on cross-coupled triode MOS transistors to render extended transistors' operation and linearity improvement at a low supply. Detailed analysis that leads to a systematic design is outlined. The feasibility of the mixer for baseband wireless sensor applications is demonstrated through simulation of a 0.5-V demodulator for IEEE 802.15.4 radio using regular transistors in a 1.8V 0.18 $\mu$ m CMOS process with  $V_{T0} = 0.4V$  which is as large as 80% of the supply voltage. Also provided to verify its practicality is the experimental demodulator at a reduced data rate based upon a breadboard implementation using array transistors.

- 4) Analysis, design and silicon implementation of a very low voltage and low power R-MOSFET-C filters :

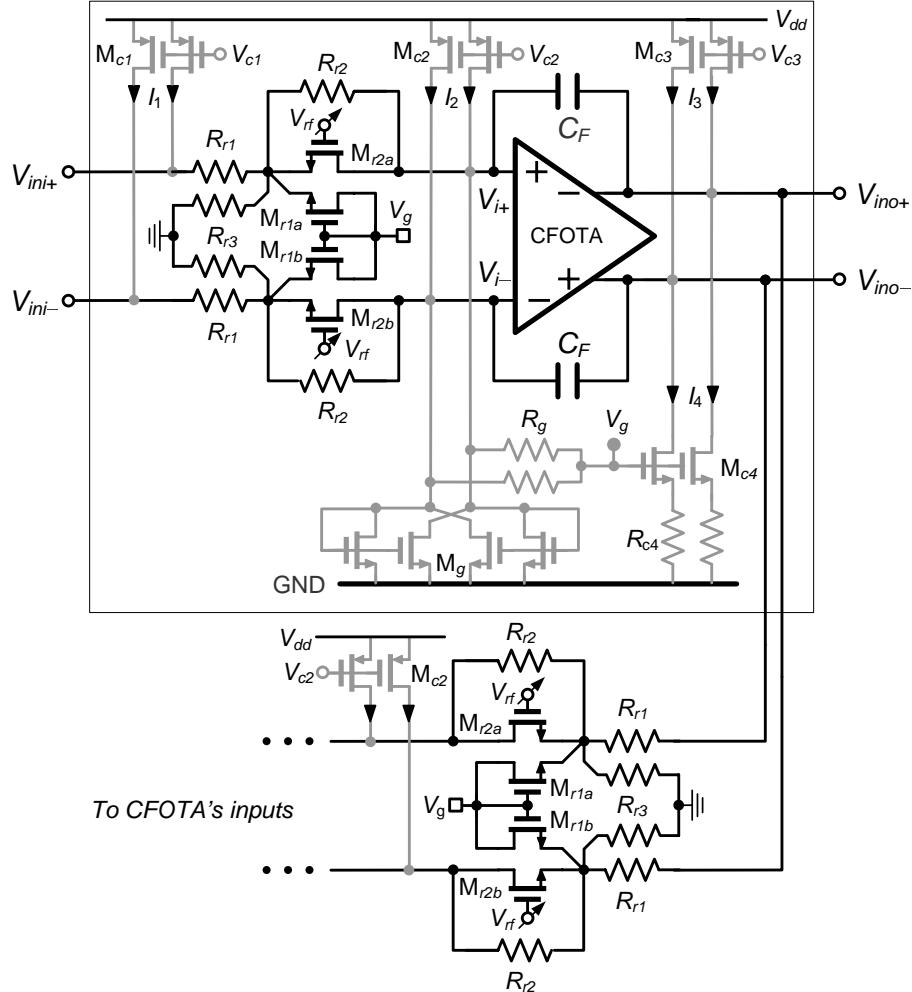

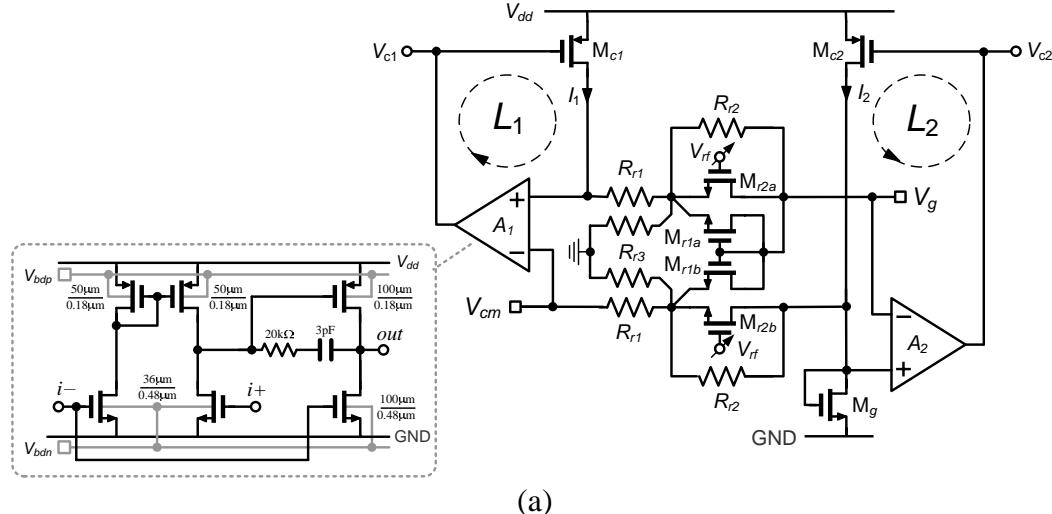

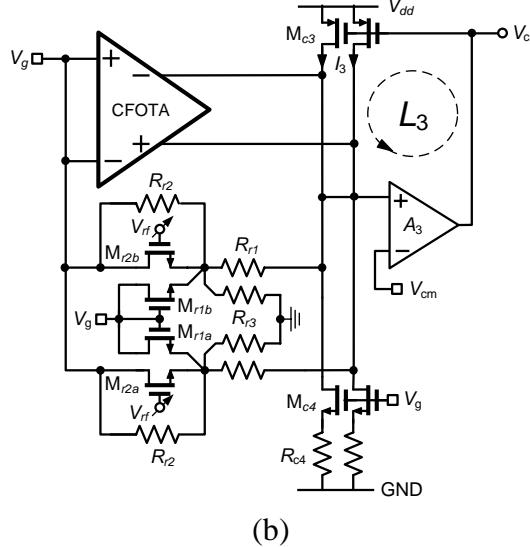

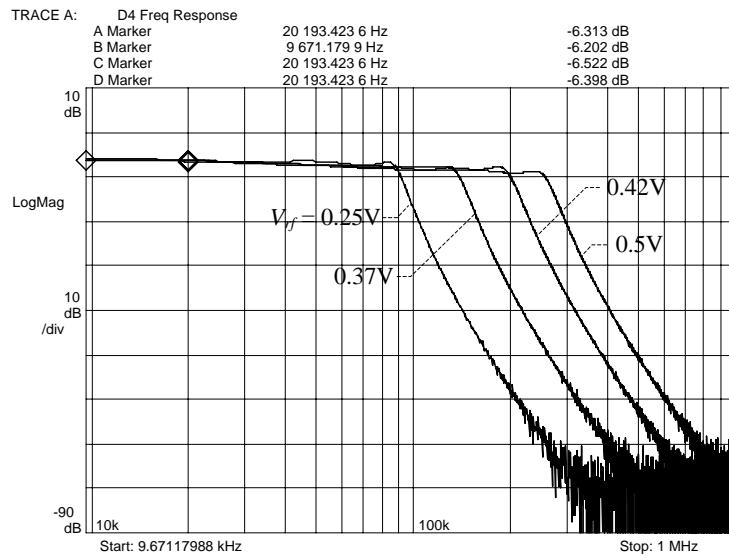

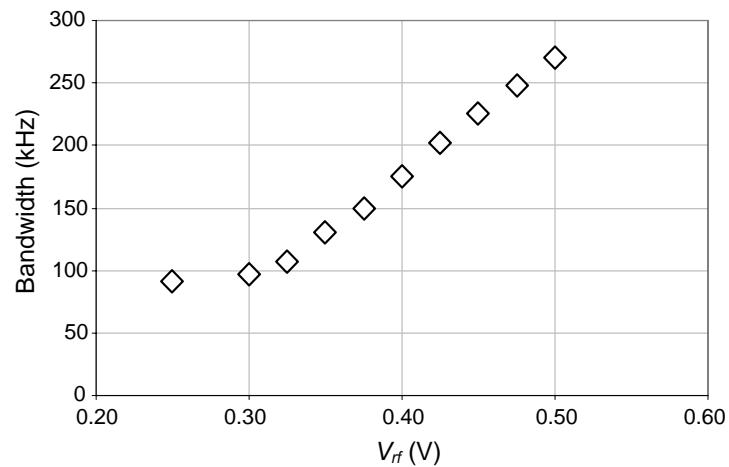

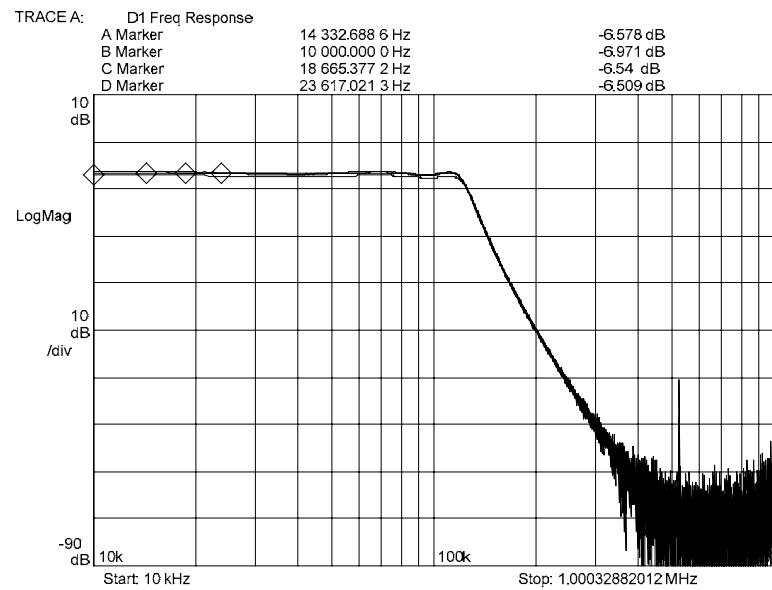

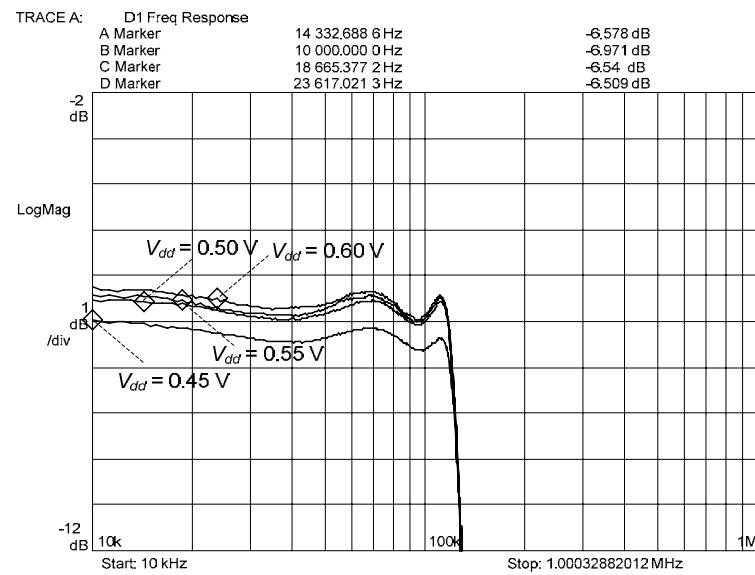

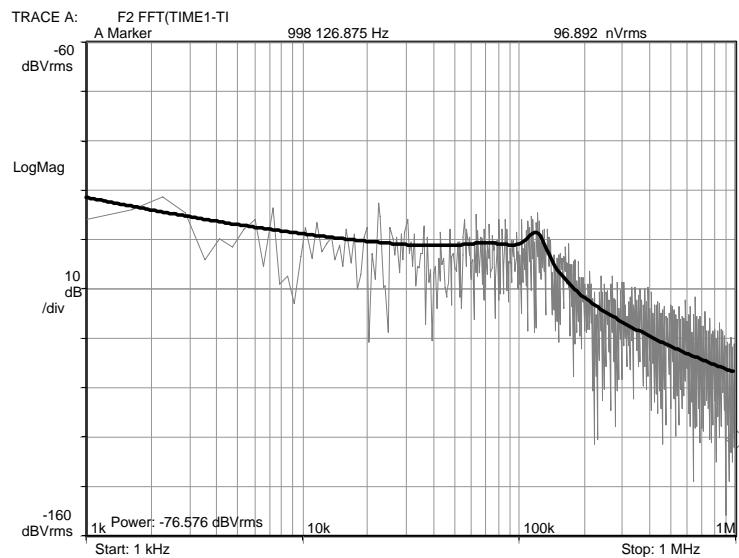

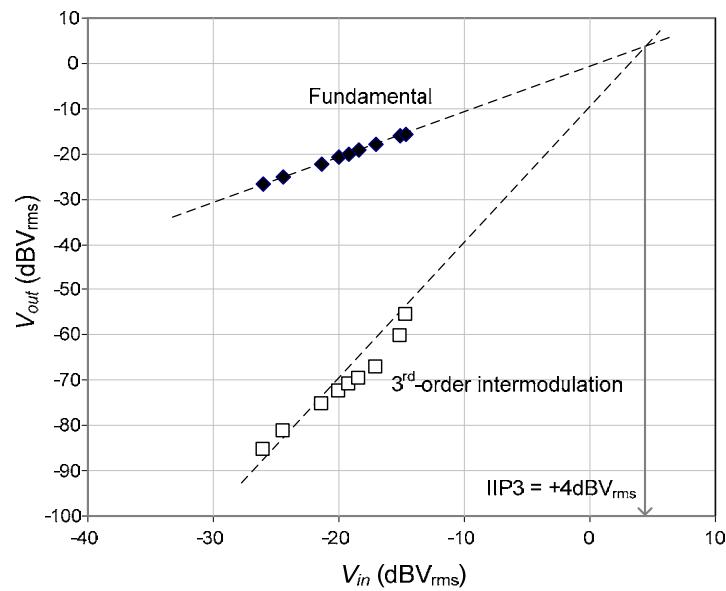

A 0.5-V fully-integrated R-MOSFET-C filter suitable for use in wearable and portable biomedical devices is demonstrated. Such a very low supply voltage and low power is made possible through the sub-threshold inversion operation of the MOS transistors in both the operational transconductance amplifiers (OTA) and the tunable resistors. A fully-integrated 5<sup>th</sup>-order Chebychev low-pass filter in a 0.18- $\mu$ m triple-well CMOS technology with  $V_T = 0.42$  V is implemented for a 0.5 V supply voltage. The measured tuning frequency is from 91 kHz to 268 kHz which is more than one octave where the nominal cut-off frequency automatically set by the on-chip PLL circuit is at 130-kHz. The spurious-free dynamic range (SFDR) is better than 53.7 dB. The total current and power consumption (including the bias control circuits) are 1.2 mA and 600  $\mu$ W respectively.

The details of each topic will be covered from Section 2 to 5 of this report.

## 2. Subthreshold SI Techniques for Low Power Biomedical Electronics

### 2.1 Introduction

Since its inception over a decade ago, the switched-current (SI) technique has claimed two main advantages over switched-capacitors (SC): because it operated in the current domain, it should be less impacted by lowering supply voltage, and because it did not use explicit capacitors, it should be better suited to “digital” CMOS. The SI technique has been found useful in many analogue applications where a compatibility with standard digital CMOS and low supply voltage, as well as a small chip area are of main concern [1-13]. However, despite numerous circuit developments, all using transistors operated in strong inversion (i.e. square law characteristics), performance never competed with that of SC. Theoretical comparisons of SI and SC [14-15] established that competitive performance could be achieved using class AB techniques but very low voltage operation was hindered by the use of strong inversion operation. As CMOS processes have headed towards smaller feature sizes and lower supply voltage, designs have been forced towards operating their transistors in moderate or even weak inversion, i.e. in the sub-threshold region, and the earlier theoretical comparison is no longer sufficiently general.

With this in mind, it has become necessary to extend the theoretical study by using the general saturated MOS model, valid for all regions of inversion. In Section II, the overall performance, expressed in terms of a figure-of-merit (FoM) embracing speed ( $F_C$ ), dynamic range ( $DR$ ) and power consumption ( $P$ ), is derived. Section III discusses how SI performance is affected by the operating region of its transistors and Section IV provides a practical validation of the theory established in Section II. Section V describes some important non-ideal effects. Two practical sub-threshold designs are then demonstrated in Section VI and finally conclusions are given in Section VII.

### 2.2 Theoretical Performance Analysis

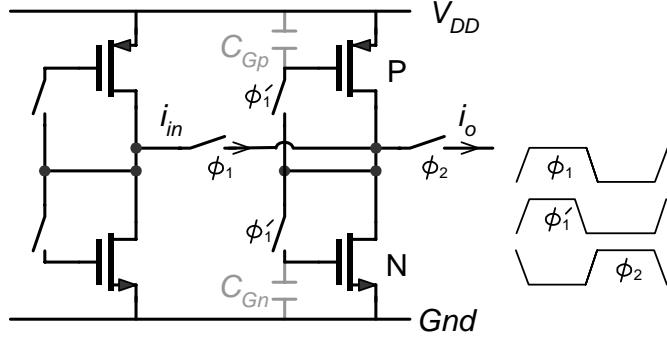

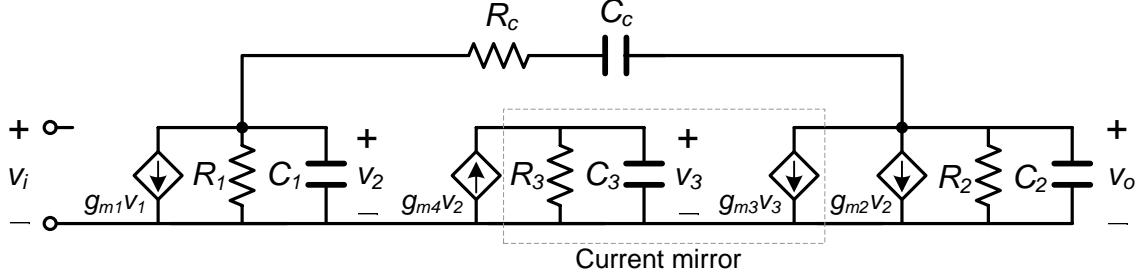

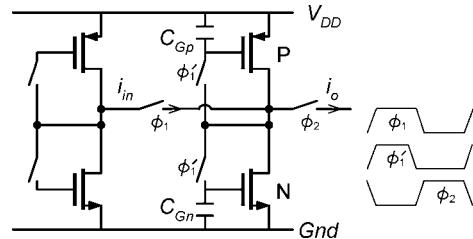

The general performance analysis presented in this section follows along similar lines to that presented earlier [14-15] for strong inversion. Thus, a cascade of the basic class AB memories shown in Fig. 2.1 is chosen since these form the basic configuration used by SI filters and ADCs. The SI memory has a sampling phase  $\phi_1$  during which an amplifier, made up from p- and n-MOS complementary transistors, is in a closed loop due to the closure of the switches  $\phi_1$ . The voltage on its memory capacitors settles to a value determined by the input current  $i_{in}$  and the transconductance of the memory transistors. On the hold phase  $\phi_2$ , the amplifier is open loop and the voltage held on the memory capacitors, together with the same transconductance, produces the output current  $i_o$  which is close to  $i_{in}$ . To promote analysis simplicity without loss of generality, it is assumed that the n- and p-MOS memory transistors are symmetrical, i.e. with identical transconductance parameter ( $\beta$ ), threshold voltage ( $V_T$ ) and memory capacitance ( $C_{Gn} = C_{Gp} = C_G$ ) etc. All the parasitic capacitances are neglected leaving only the gate-to-source capacitance ( $C_{GS}$ ) and gate-to-body capacitances ( $C_{GB}$ ) to form the total memory capacitance

$C_{tot} = 2C_G = 2(C_{GS} + C_{GB})$ . Note that  $C_{tot}$  is dominated by  $C_{GS}$  in strong inversion and by  $C_{GB}$  in weak inversion memory operation. Also, all the switches are assumed to have zero on-resistance and only thermal noise from transistors is included. Unless stated otherwise, saturation operation in the memory transistors is assumed throughout and signals are sinusoidal.

**Fig. 2.1** Basic class AB SI memory configuration for FoM performance analysis

The following analysis is based on the approximate “single piece” saturation model equations for MOS transistors [16], valid for all regions of inversion. It should be noted that although a compromise of the accuracy over the entire operating range is anticipated, the simple model can achieve a balanced compromise between simplicity and accuracy. In the model, the  $I_D - V_{GS}$  characteristic, the small-signal transconductance  $g_m$ , the gate capacitance  $C_G$ , and the thermal noise power spectral density  $S_n(f)$  of a MOS transistor are given by

$$I_D = I_S \cdot \left[ \ln \left( 1 + e^{\frac{V_{GS} - V_T}{2n\phi_t}} \right) \right]^2 \quad (1a)$$

$$g_m = \frac{I_D}{n\phi_t f(x)} \quad (1b)$$

$$S_n(f) = 4kT_j \left( \frac{1}{2} + \frac{1}{6} \cdot \frac{x}{f(x)^2} \right) n g_m \quad (1c)$$

$$C_G = WLC_{ox} \left[ 1 - \frac{1}{n} \cdot \left( 1 - \left( \frac{3}{2} + \frac{f(x)}{x} \right)^{-1} \right) \right] \quad (1d)$$

with  $I_S = 2\beta n\phi_t^2$ ,  $x = I_D / I_S$  and  $f(x) = (\sqrt{1+4x} + 1) / 2$ . In the equations,  $\phi_t = kT/q$  is the thermal voltage,  $n$  is the slope factor ( $1 < n < 2$ ),  $k$  is the Boltzmann’s constant,  $T_j$  is the absolute temperature,  $C_{ox}$  is the oxide capacitance,  $W$  is the channel width,  $L$  is the channel length, and  $\beta = \mu_{eff}C_{ox}W/L$  is the transconductance parameter where  $\mu_{eff}$  is the effective mobility. The mobility reduction effect is modeled as  $\mu_{eff} = \mu_0 / (1 + \theta \cdot V_{GT})$  where  $V_{GT} = V_{GS} - V_T$ ,  $\mu_0$  is the low field mobility and  $\theta$  is the mobility reduction parameter [16].

### A. Figure-of-Merit Formulation

We now develop the figure-of-merit,  $\text{FoM} = F_C \cdot DR / P$ , from expressions for the memory clock frequency  $F_C$ , the power consumption  $P$ , and the dynamic range  $DR$ .

The memory's clock frequency,  $F_C$ , is related to the composite memory time-constant,  $C_{tot}/(2g_m)$ . Using (1a)-(1b), this gives

$$F_C = \frac{2g_m}{NC_{tot}} = \frac{2I_D}{NC_{tot}n\phi_f f(x)} \quad (2)$$

where  $N$  is a constant which depends on the desired settling accuracy (e.g.  $N \approx 9$  for 0.1% settling accuracy [15]).

The average power consumption  $P$  for a maximum sinusoidal signal current is given by

$$P = \rho I_D V_{DD} \quad (3)$$

where  $I_D$  is the memory cell's quiescent current. The factor  $\rho$  needs further explanation. Under large signal conditions, the current flowing into the supply rail depends on both the circuit operation and the region of operation of its transistors. The factor  $\rho$  is the ratio of the average power supply current under maximum signal conditions to the cell's quiescent current  $I_D$ . For a class A SI memory,  $\rho$  is unity. In a class AB memory, since it can handle input signals larger than  $I_D$ ,  $\rho > 1$  and is dependent on the inversion region of the memory transistors. The supply voltage  $V_{DD}$ , is determined by the threshold voltage  $V_T$  and also the operating region of the memory transistors.

Similar to continuous-time translinear MOS circuits with class AB operation where input currents can be much larger than the quiescent bias current, the output noise of class AB SI is dependent on the input current level, particularly at sub-threshold operation [17,18]. With such a noise characteristic, the signal-to-noise ratio (SNR) employed in [14-15] is not applicable and dynamic range ( $DR$ ) is adopted as the performance measure to define the usable input range [18]. For the  $DR$  calculation, whereas the minimum input signal is limited by the total sampled noise current  $\sqrt{\hat{i}_n^2}$  from the memory transistors, the maximum signal  $\hat{i}_n$  is limited by the linearity performance. However, for the sake of simplicity it is assumed here that  $\hat{i}_n$  is determined at a point where substantially all of the input current flows into one or other of the SI memory's composite transistors. This is in turn set by the quiescent bias current  $I_D$  and the region of inversion of the memory transistors. By using (1a) - (1c), the  $DR$  can be expressed as

$$DR = \frac{\hat{i}_n^2}{2\hat{i}_n^2} = \frac{(\alpha I_D)^2}{8 \cdot S_n(f) \cdot BW_n} = \frac{n(\alpha\phi_f f(x))^2}{\frac{8kT_j}{C_{tot}} \left(1 + \frac{1}{3} \cdot \frac{x}{f(x)^2}\right)} \quad (4)$$

where  $BW_n = g_m/2C_{tot}$  is the equivalent noise bandwidth of the composite memory. The factor  $\alpha$  is the ratio of the peak value of the maximum signal current to the quiescent current  $I_D$ . Similar to the factor  $\rho$ ,  $\alpha=1$  for a class A memory and  $\alpha>1$  for a class AB memory and is dependent on the operating region of the memory transistors.

From the derived expressions (2)-(4), the general FoM of an SI memory is thus expressed as

$$\text{FoM} = \frac{F_C \cdot DR}{P} = \frac{\alpha^2}{\rho} \cdot \frac{\phi_t}{NV_{DD}} \cdot \frac{f(x)}{4kT_j \left( 1 + \frac{1}{3} \cdot \frac{x}{f(x)^2} \right)} \quad (5)$$

The analysis of the factors,  $\rho$  and  $\alpha$ , is the subject of the next sub-section.

### B. Calculation of Dependent Factors $\rho$ and $\alpha$

For SI memories using transistors operating in strong inversion, (1a) converges to the square-law relation,  $I_D = (\beta/2n) \cdot V_{GT}^2$ , and the function  $f(x) \approx \sqrt{x} = \sqrt{I_D/I_S}$  since  $I_D \gg I_S$ . For weak inversion, (1a) becomes the exponential relation,  $I_D = I_S \cdot \exp(V_{GT}/n\phi_t)$ , and  $f(x) \approx 1$  as  $I_D \ll I_S$ . Note that, for the calculation of  $I_D$  and  $f(x)$  in (1a)-(1d) in moderate inversion, one must resort to numerical computation.

For a class AB SI memory, the factor  $\alpha$  is determined by considering how an input current  $i_{in}$  is shared between the memory transistors N and P in Fig. 2.1. The peak value of the maximum signal  $\hat{i}_{in}$  is that which forces substantially all the current to flow in one transistor while substantially cutting-off the other. Following this, we have  $\alpha = 4$  in the strong-inversion memory [11]. For the sub-threshold memory operation, it can be shown numerically using (1a) that, for the same quiescent current  $I_D$ ,  $\hat{i}_{in}$  increases further, i.e.  $\alpha > 4$ . This is primarily attributed to a heavier companding characteristic in a MOS transistor, i.e. from square-root companding [19] in strong inversion to natural log-exponential companding in weak inversion. For this,  $\alpha$  can be determined analytically from the relation between the input current  $i_{in}$  and the variation in the gate overdrive voltage  $v_{GT}$  as follows

$$i_{in} = I_S e^{\frac{V_{GT} + v_{GT}}{n\phi_t}} - I_S e^{\frac{V_{GT} - v_{GT}}{n\phi_t}} = 2I_S \cdot \sinh\left(\frac{v_{GT}}{n\phi_t}\right) \quad (6)$$

**Table I** Summary of Analytical Performance Expressions

| Performance | Strong Inversion                              | Weak Inversion                                   |

|-------------|-----------------------------------------------|--------------------------------------------------|

|             | SI                                            | SI                                               |

| $F_C$       | $\frac{4I_D}{NC_{tot}V_{GT}}$                 | $\frac{2I_D}{NC_{tot}n\phi_t}$                   |

| $P$         | $\frac{3I_D V_{DD}}{2}$                       | $3.37 \cdot I_D V_{DD}$                          |

| $DR$        | $\frac{3C_{tot}V_{GT}^2}{8nkT_j}$             | $\frac{49C_{tot}n\phi_t^2}{4kT_j}$               |

| $FoM$       | $\frac{1}{nKT_j} \cdot \frac{V_{GT}}{V_{DD}}$ | $\frac{7.28}{NKT_j} \cdot \frac{\phi_t}{V_{DD}}$ |

If the memory transistors' current ratio is assumed to be 100:1 for the maximum signal condition, it can be shown that we have the peak overdrive at  $\hat{v}_{GT} \approx 2.3 \cdot n\phi_t$ . From (6), this subsequently yields the peak current factor  $\alpha = \hat{i}_{in}/I_D = 2\sinh(2.3) \approx 9.9$  in the class AB weak inversion memory.

Next, we consider the factor  $\rho$ . This is determined by calculating the average power supply current for the same maximum sinusoidal input current used in the determination of the factor  $\alpha$ . For a class AB strong inversion memory with a balanced structure,  $\rho = 3/2$  [15]. As the memory operation moves to moderate inversion,  $\rho$  gradually increases due to a larger peak input current handling capacity as described above. At weak inversion, the instantaneous supply current  $I_{DD}(t)$  under a sinusoidal input current that gives an instantaneous memory transistor gate-overdrive  $v_{GT}(t)$  is given by

$$I_{DD}(t) = I_S e^{\frac{(V_{GT} + v_{GT}(t))}{n\phi_t}} + I_S e^{\frac{(V_{GT} - v_{GT}(t))}{n\phi_t}} = 2I_D \cosh\left(\text{arc sinh}\left(\frac{i_{in}}{2I_D}\right)\right) \quad (7)$$

With the peak gate-overdrive voltage at  $\hat{v}_{GT} = 2.3 \cdot n\phi_t$  due to the peak input current  $\hat{i}_{in} = 9.9 \cdot I_D$ , the average supply current for half of the balanced memory can be computed and this yields  $\rho$  in the weak inversion class AB SI memory as

$$\rho = \frac{\frac{1}{2\pi} \int_0^{2\pi} \hat{I}_{DD}(t) d\omega t}{2I_D} = \frac{1}{2\pi} \int_0^{2\pi} \cosh\left(\text{arc sinh}\left(\frac{9.9}{2} \cdot \sin(\omega t)\right)\right) d\omega t \approx 3.37 \quad (8)$$

Using the foregoing analysis, the analytical expressions for a class AB SI memory under strong and weak inversion operation were derived and these are summarized in Table I. The expressions will be particularly useful for performance discussion in the next section. In the table, due to inter-stage transmission constraints between two identical class AB SI memories, the maximum quiescent gate-overdrive for strong inversion is limited to  $V_{GT} = V_T/2$  and hence we have  $V_{DD} = 3 \cdot V_T$  [14]. At weak inversion,  $V_{DD}$  can be below  $2 \cdot V_T$  when  $I_D < I_S$ . However, even though  $V_{DD}$  is inherently small, it must be made large enough to ensure saturated operation during inter-stage transmission. Since the peak gate-overdrive voltage is at  $\hat{v}_{GT} \approx 2.3 \cdot n\phi_t$  and the weak inversion memory transistors require  $V_{DS,min} \geq \sim 5\phi_t$  to keep saturated operation [16], the minimum supply voltage for the basic sub-threshold SI memory becomes

$$V_{DD,min} \approx 2 \cdot (2.3 \cdot n + 5) \cdot \phi_t \quad (9)$$

For a typical value of the slope factor,  $n = 1.2$  and  $\phi_t = 26\text{mV}$  at 300K, we have  $V_{DD,min} = 0.38\text{V}$ .

As the improvement in sub-threshold class AB SI performance relies heavily on the ability to handle large input current, it is also instructive to discuss the effects that may influence the peak current handling. At strong inversion, mobility reduction results in less than square-law  $I_D - V_{GS}$  characteristic in the memory transistors and this tends to increase the

voltage swing for the same drain current variation. Since there is a limit to the maximum voltage signal, a reduction in peak input current results. At weak inversion, a similar effect occurs due to the slope factor  $n$ , i.e. a larger  $n$  in the exponential  $I_D - V_{GS}$  characteristic necessitates a larger voltage swing. In effect, the memory transistors' operation may be moved into moderate inversion over the intervals near the peak voltage swing and this results in a lower peak current handling. Another important effect can result from the asymmetry between the composite memory transistors. This makes one of the devices cut off more quickly than the other, unbalancing the drain current handling, and reducing the peak input current. In the general model equation in (1a), differences in any of the parameters except the threshold voltages contributes to a reduction in the peak input current handling but the most pronounced effect is the mismatch in the slope factors at weak inversion. The parameters  $\alpha$  for the maximum input signal current and  $\rho$  for the average supply current including the aforementioned effects can be obtained numerically.

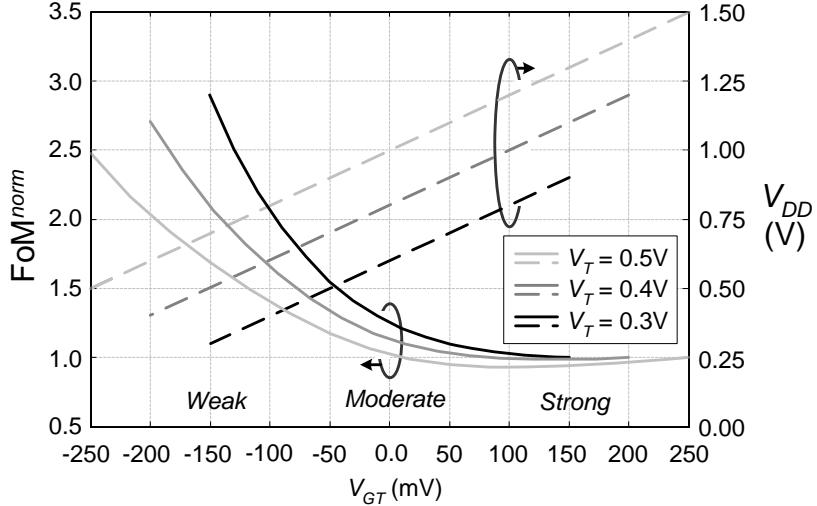

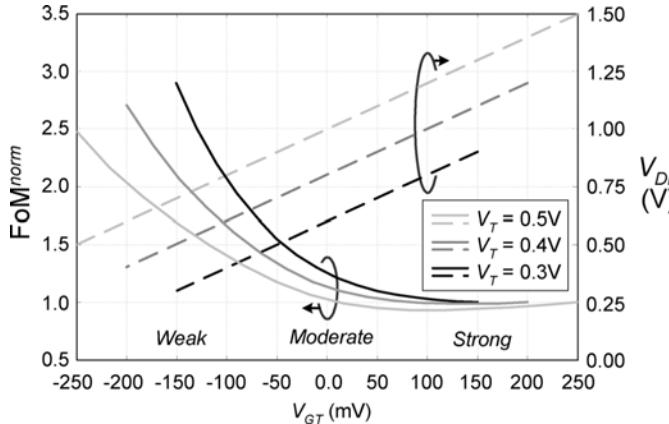

**Fig. 2.2** Normalised basic class AB FoM performance and operating supply voltage  $V_{DD}$  versus  $V_{GT}$  at different memory transistor's threshold voltages.

### 2.3 Performance Discussions

The FoMs were calculated from (5), with  $\alpha$  and  $\rho$  being numerically determined as outlined in Section II-B and with the transistor slope factor set to  $n=1$  and mobility degradation set to  $\theta = 0$ . Fig. 2.2 shows the FoMs versus  $V_{GT}$  for the class AB SI at different threshold voltages  $V_T = 0.5V$ ,  $0.4V$  and  $0.3V$ . This corresponds to CMOS process generations spanning from  $0.35\mu\text{m}$  down to  $90\text{nm}$  according to the SIA roadmap. The range of  $V_{GT}$  is from  $-V_T/2$  to  $+V_T/2$  and all the plots are normalised to their corresponding strong inversion FoMs at the maximum  $\hat{V}_{GT} = V_T/2$ . Also included in Fig. 2.2 is the variation of  $V_{DD}$  for the same range of  $V_{GT}$  and  $V_T$ .

With the memory transistors in strong inversion, the FoM plots indicate that the performance of class AB SI remains almost constant with falling  $V_{GT}$ . This is also predicted by the analytical FoM expression for strong inversion operation in Table I (with  $V_{GT} = V_T/2$  and  $V_{DD} = 3 \cdot V_T$ ) and was already reported in detail in [16]. When entering moderate to weak

inversion, the FoM performance starts to rise and  $V_{DD}$  falls with falling  $V_{GT}$  and  $V_T$  indicating that class AB SI should offer better performance in modern CMOS processing. Interestingly, such a trend is in stark contrast to SC where performance is known to fall steadily with falling  $V_{DD}$ . Also note that the supply voltage level falls significantly when operating in weak inversion.

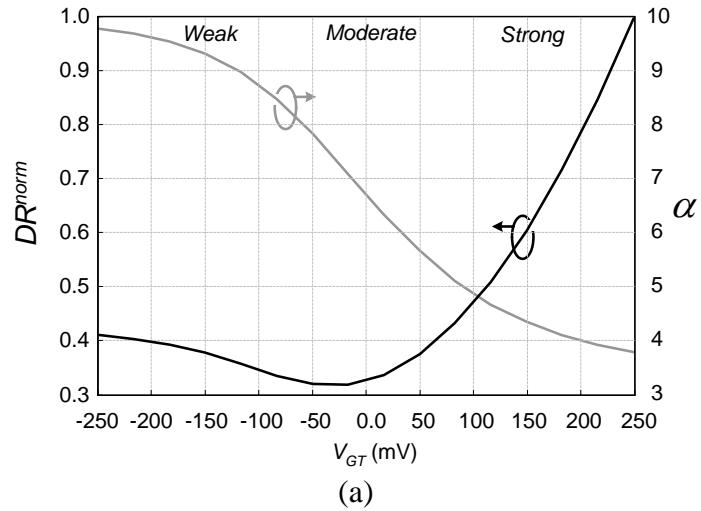

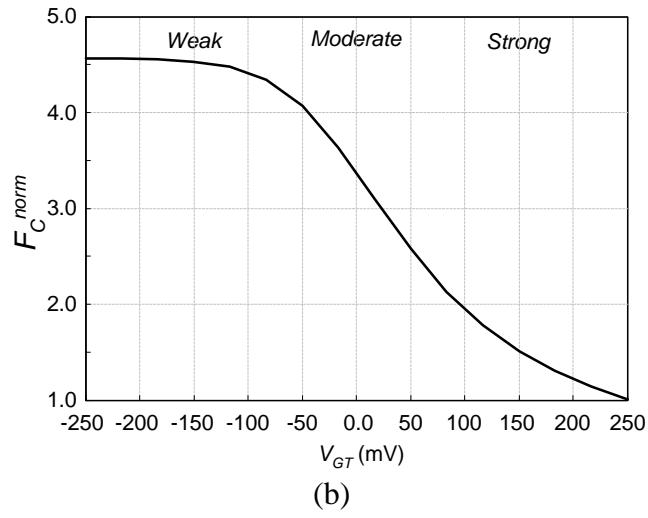

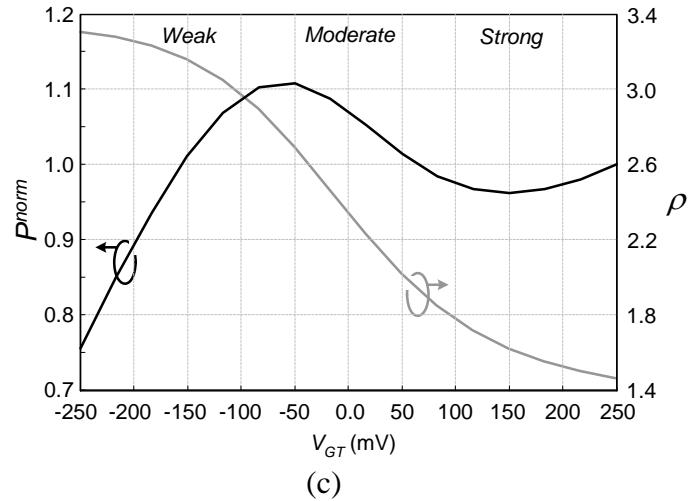

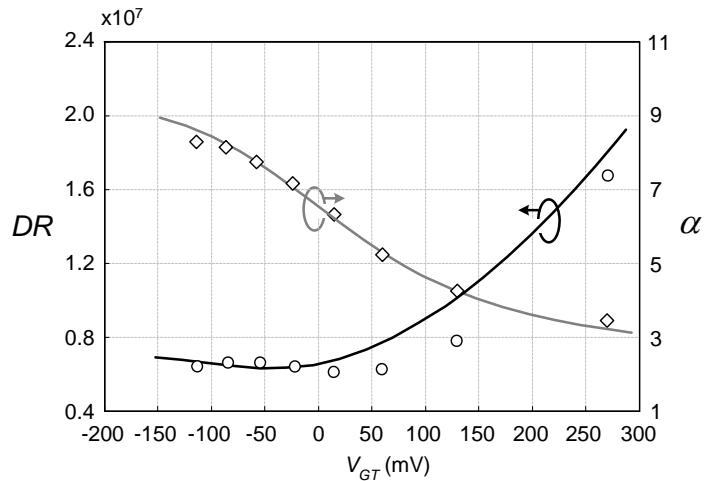

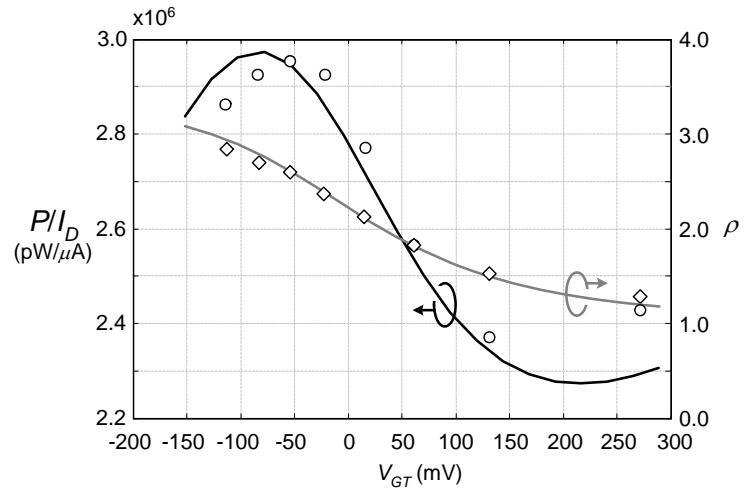

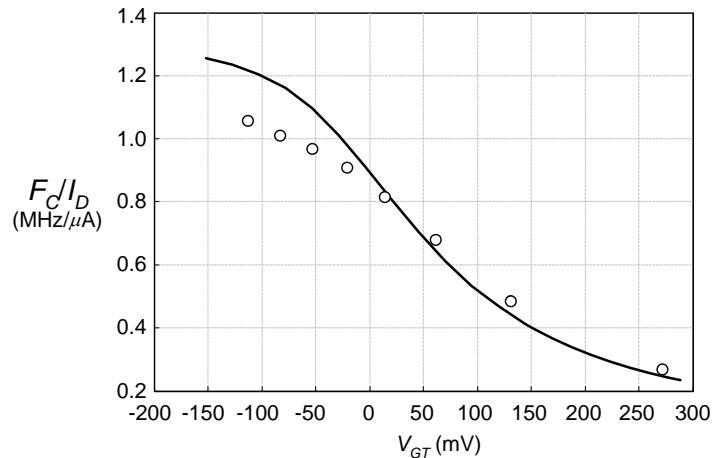

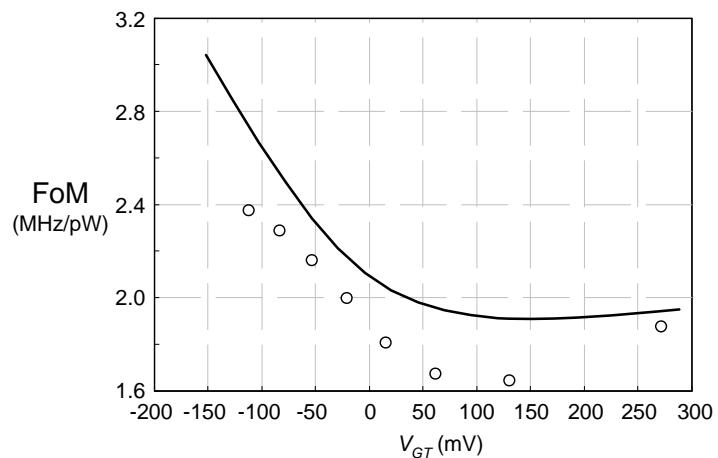

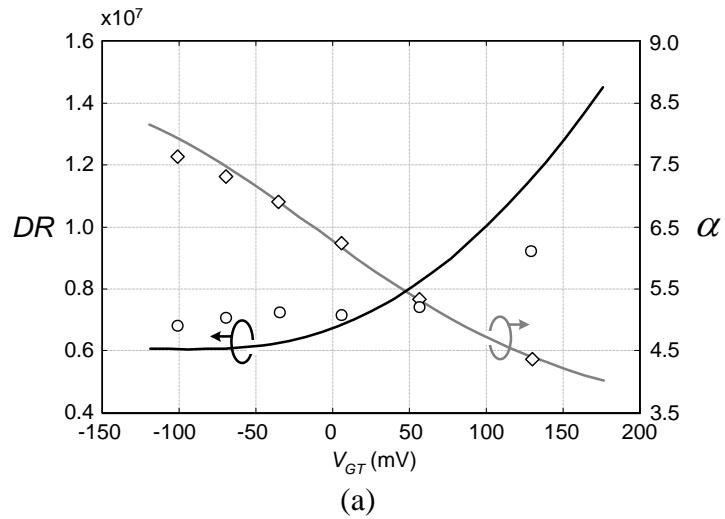

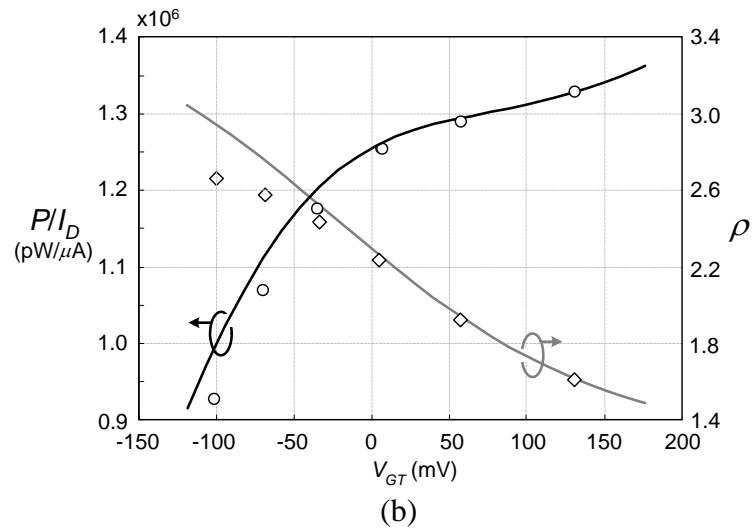

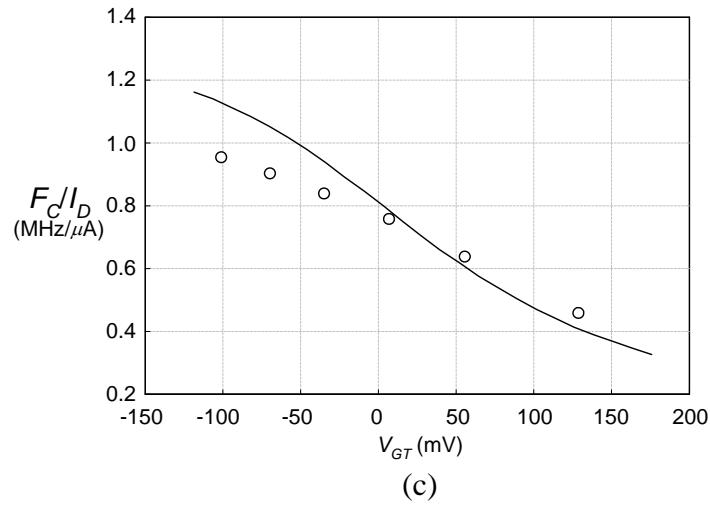

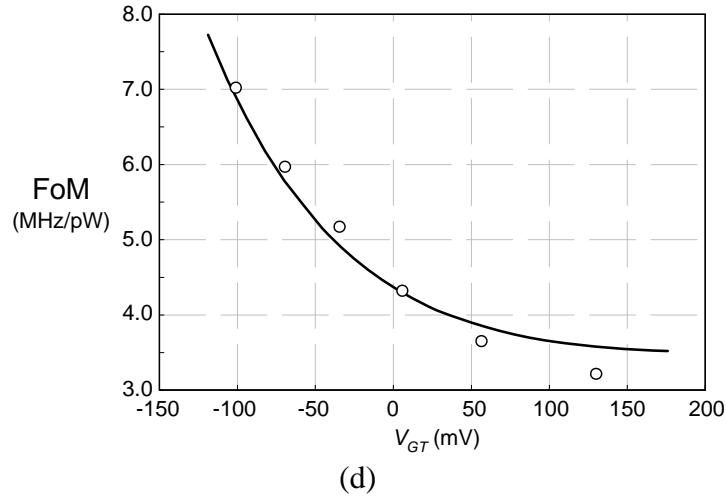

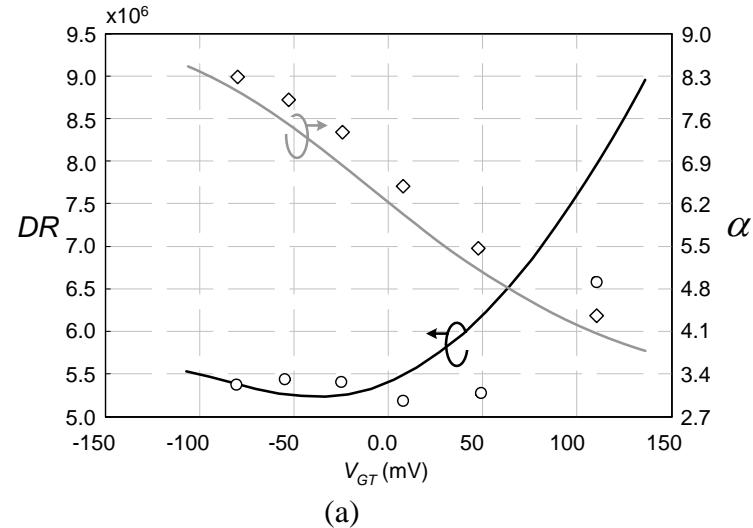

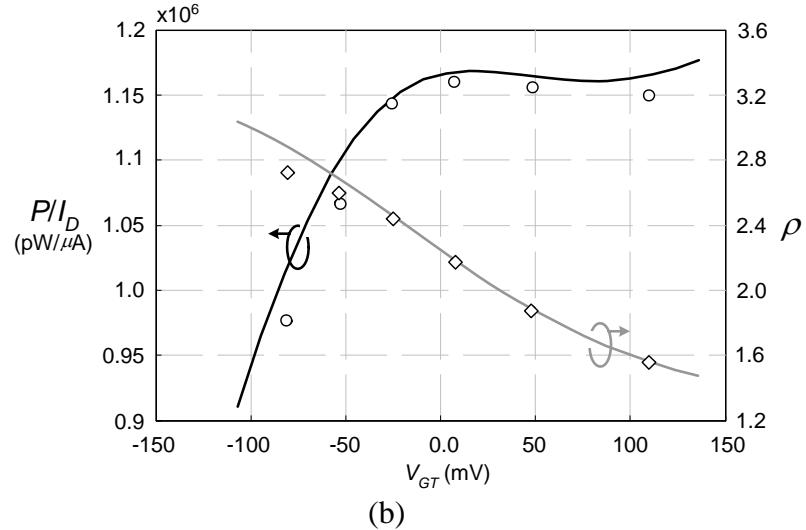

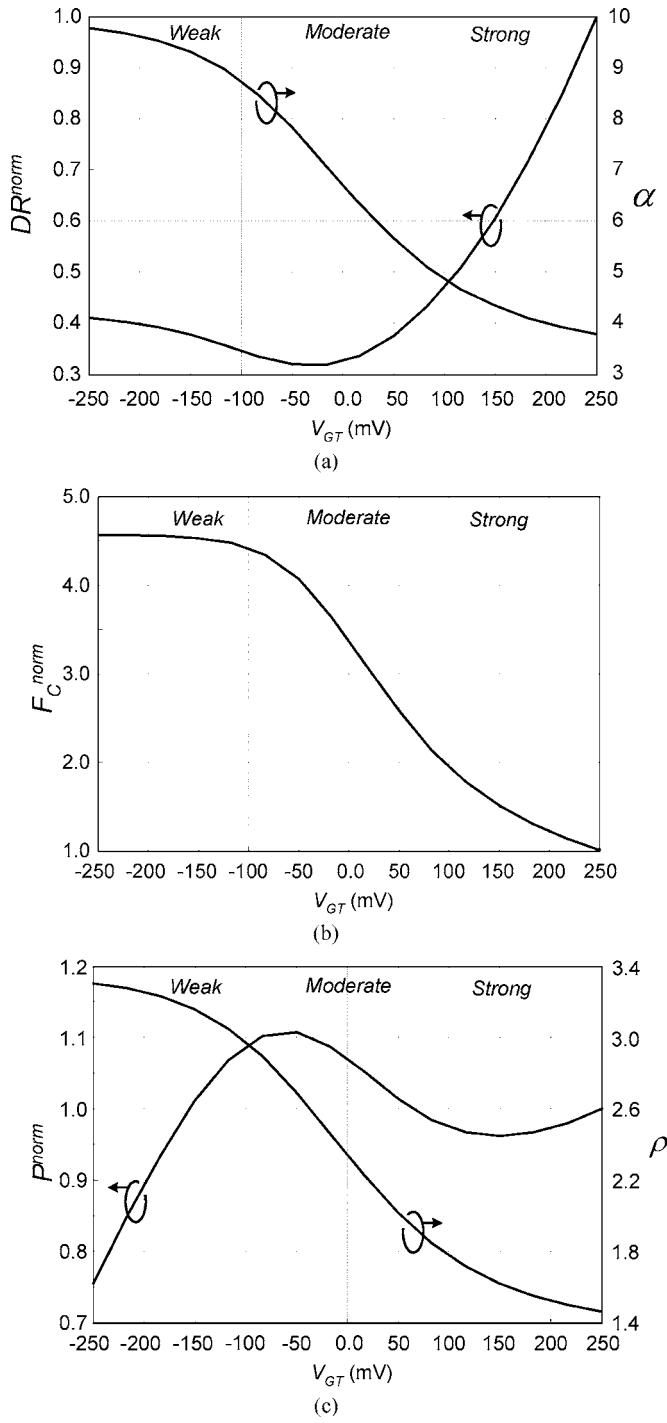

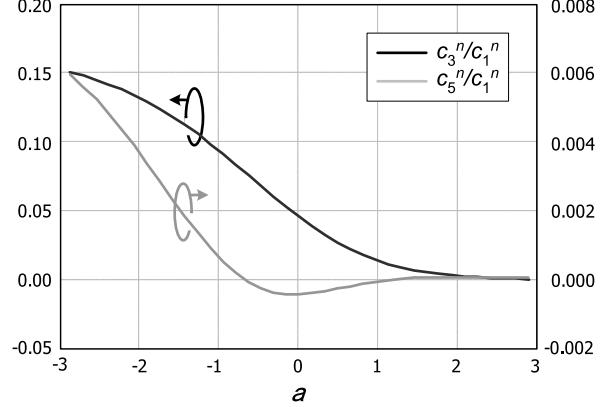

The FoM improvement at smaller gate overdrives can be explained by investigating how each of the performance vectors,  $DR$ ,  $F_C$  and  $P$ , changes with  $V_{GT}$ . Consider, without loss of generality, a scenario in which  $V_{GT}$  falls but the quiescent drain current  $I_D$  in the memory transistors and the total capacitance  $C_{tot}$  remain *constant*. Based on the analysis in Section II, the plots of the performance vectors versus  $V_{GT}$ , *all normalised* to their corresponding values at  $\hat{V}_{GT} = V_T/2$  are given in Fig. 2.3(a)-(c) for  $V_T = 0.5V$  as a case example. It should be noted that, at strong and weak inversion operations, the performance dependencies in the figures follow the expressions summarized in Table I.

With strong inversion, the maximum signal current swings and signal power are almost constant [ $\alpha \sim 4$  at strong inversion in Fig. 2.3(a)]. However, the reduced  $V_{GT}$  at a constant  $I_D$  necessitates the use of transistors with a proportionally higher transconductance  $g_m$ . It also produces a quadratically increased noise power since both the noise PSD and  $BW_n$  increase. This results in a quadratic reduction of the  $DR$  against  $V_{GT}$  ( $DR \propto V_{GT}^2$  for strong inversion SI). Since we have kept  $C_{tot}$  constant, there is a proportional increase in memory speed  $F_C$  due to a higher  $g_m$ ,  $F_C \propto 1/V_{GT}$ , [Fig. 2.3(b)]. The power consumption  $P$  falls with  $V_{GT}$  because of the reduced  $V_{DD}$  and almost constant average peak supply current [ $\rho \sim 1.5$  at strong inversion in Fig. 2.3(c)]. Therefore, the net result is an almost constant FoM for SI with strong inversion, as evident in Fig. 2.2 and Table I, despite falling  $V_{GT}$ .

With moderate to weak inversion, as  $V_{GT}$  falls, the memory transistors' characteristics are gradually changed from a square-law to an exponential relationship. This yields an increasing maximum signal current swing and hence signal power, even though  $I_D$  is constant [see  $\alpha$  rising to  $\sim 9.9$  from the moderate to the weak inversion region in Fig. 2.3(a)]. Similarly, the transconductance  $g_m$ , and hence noise power, must increase to accommodate the reduced  $V_{GT}$ . However, the increases are slower than with strong inversion and so the  $DR$  drops more gradually and eventually stays almost constant [see  $DR^{\text{norm}}$  at moderate to weak region in Fig. 2.3(a)]. Similarly, the increase in the memory speed  $F_C$  is also less [see  $F_C$  at moderate to weak region in Fig. 2.3(b)]. The power consumption  $P$  rises slowly in moderate inversion because  $V_{DD}$  falls slowly while the average supply current falls more quickly due to the increased signal swing [see  $\rho$  rising to  $\sim 3.37$  from moderate to weak region in Fig. 2.3(c)]. Eventually in weak inversion, the

(a)

(b)

(c)

**Fig. 2.3** Theoretical variations of basic class AB SI performances against  $V_{GT}$ .

**Table II** Extracted MOS Model Parameters for CD4007 Transistor Arrays

| Parameter                   | pMOS                 | nMOS                 |

|-----------------------------|----------------------|----------------------|

| $I_S$ (A)                   | $2.2 \times 10^{-3}$ | $7.2 \times 10^{-3}$ |

| $ V_T(V) $                  | 1.322                | 1.518                |

| $n$                         | 1.415                | 2.284                |

| $\theta$ (V <sup>-1</sup> ) | 0.1839               | 0.1755               |

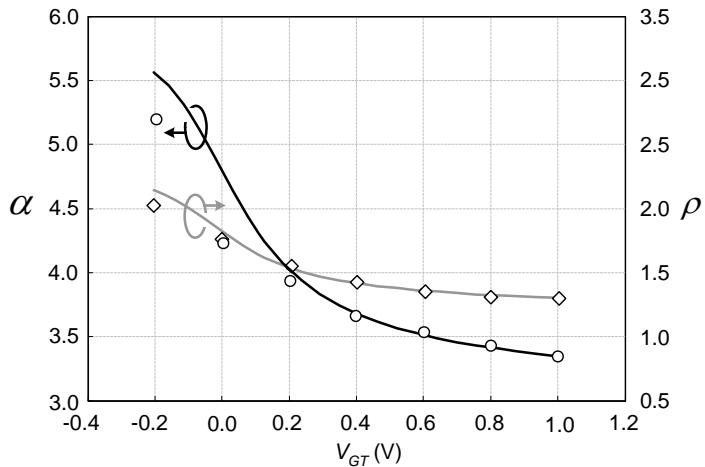

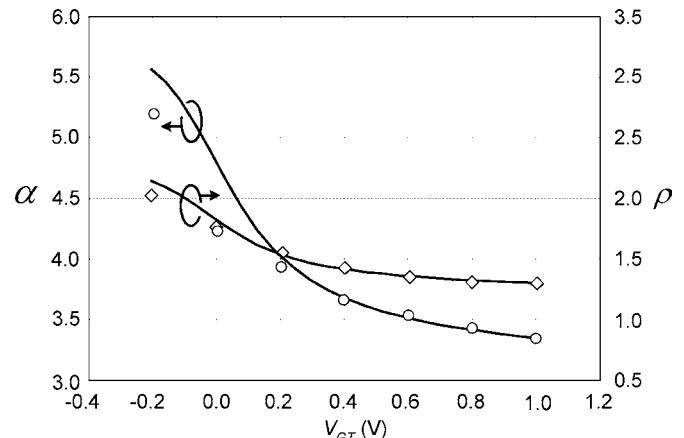

**Fig. 2.4** Measured (markers) and simulated (solid) plots of  $\alpha$  and  $\rho$  versus  $V_{GT}$ .

average supply current stays almost constant and thus  $P$  falls proportionally with  $V_{DD}$  [see  $P$  falling at weak inversion in Fig. 2.3(c)].

With these performance dependencies, the overall effect is that FoM is improved for class AB SI operating in moderate to weak inversion as depicted in Fig. 2.2. As  $V_{GT}$  falls in weak inversion  $V_{DD}$  falls proportionally and FoM rises inversely as indicated in Table I.

## 2.4 Analysis and Performance Verifications

### A. Experimental Performance

The analysis results obtained in Section II, particularly the input signal handling and signal-dependent supply current, are first verified by a breadboard implementation of the basic balanced class AB SI memory, using CD4007 transistor arrays as CMOS memory transistors and CD4016 as memory switches. Listed in Table II are the parameters of the MOS equation in (1a) for both the p- and n- MOS transistor arrays extracted to obtain best overall fit to their

measured characteristics in saturation over the operating range from strong to weak inversion with the help of MATLAB optimization tools. The maximum clock frequency  $F_C$  was set at 1kHz, and the sinusoidal input at 100Hz. The input V-to- $I$  and output  $I$ -V converters were implemented by AD844 operational current amplifiers and linear resistors to facilitate voltage-domain measurement. For this measurement, the gate-overdrive voltages  $V_{GT}$  were adjusted via the supply voltage  $V_{DD}$  to set the operating region of the memory transistors. Since this also affected the transconductance, the memory bandwidth was maintained by adding external memory capacitors which could be tuned for memories operating in strong or weak inversion.

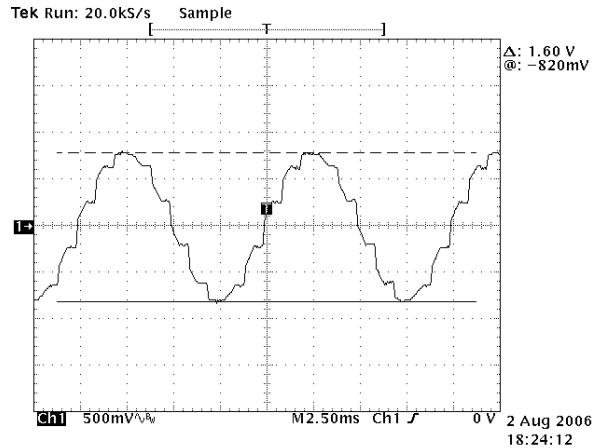

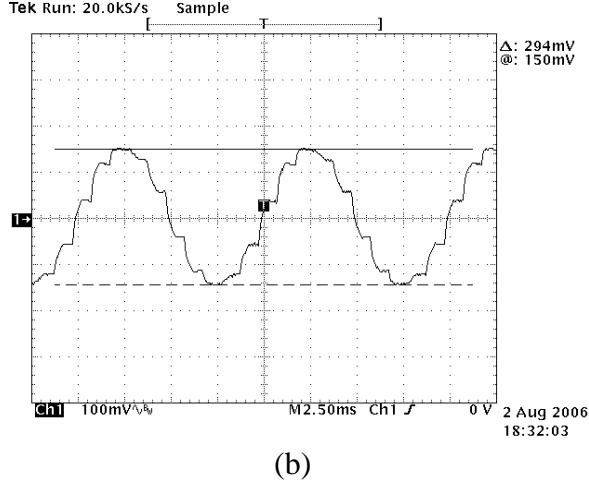

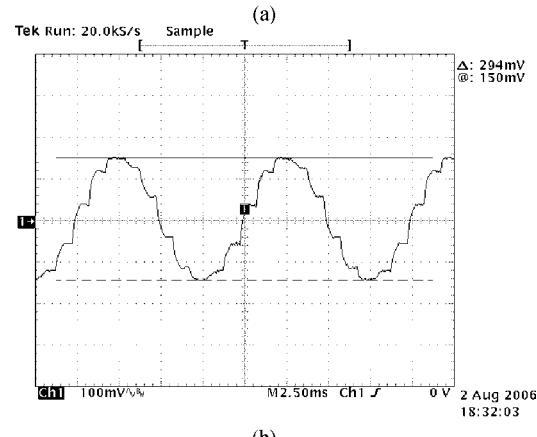

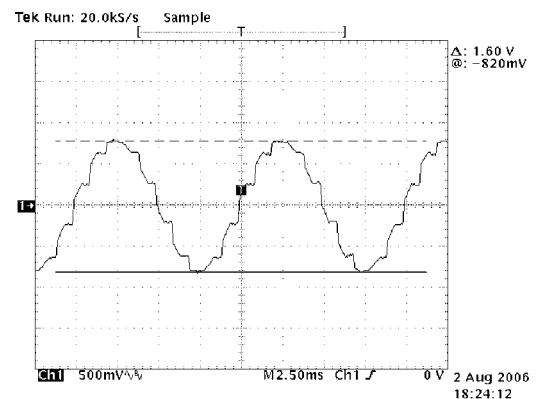

Fig. 2.4 shows both the measured peak signal current factor  $\alpha$  and the measured peak average supply current factor  $\rho$  versus  $V_{GT}$ . Also given are the plots of  $\alpha$  and  $\rho$  obtained from numerical calculation based on the theoretical analysis where the maximum errors as compared with the measured results are about 6.7% for  $\alpha$ , and 4% for  $\rho$ . From the figures, it can be noticed that both  $\alpha$  and  $\rho$  at  $V_{GT} = -0.2V$ , i.e. weak inversion memory operation, are somewhat smaller than the theoretical predictions in (6) and (7). This is because the slope factor  $n$  and the parameter  $I_S$  of the p- and n-MOS memory transistors are considerably different as evident in Table II. In order to illustrate the voltage *compression* characteristic in the weak inversion SI, the transient gate-source voltage waveforms of the class AB memories with strong inversion ( $V_{GT} = 0.8V$ ) and weak inversion ( $V_{GT} = -0.2V$ ) at their corresponding *peak* input currents were measured, and these are given in Fig. 2.5(a) and 5(b) respectively. Whereas the signal voltage swing in strong inversion is of the order of the threshold voltage  $V_{TP}$  or  $V_{TN}$  in Table II, that of the weak inversion memory is compressed to only a few hundred millivolts.

(a) [Continued]

(b)

**Fig. 2.5** Voltage waveforms at the basic class AB SI memory's gate under maximum sinusoidal input (a) at strong inversion and b) at weak inversion operating conditions.

### B. Simulated FoM Performance

Following the breadboard experimental verification, the theoretical performance of sub-threshold class AB SI in IC implementation is demonstrated via simulation using 3.3V, 0.35 $\mu$ m CMOS process data. The simulation models for MOS transistors are BSIM3v3. The extracted model parameters for the selected unit transistor dimensions, i.e.  $(W/L)_p = 4.6\mu\text{m}/2.5\mu\text{m}$  and  $(W/L)_n = 3.0\mu\text{m}/4.0\mu\text{m}$ , are summarised in Table III. Notice from the table that the p- and n-MOS transistors of the process exhibit good symmetrical characteristics (except  $V_T$  but this has no impact on the performance). Similar to the experimental test, the operating condition of the memory transistors was set by varying  $V_{GT}$  through  $V_{DD}$ . Although there was flexibility to simultaneously maintain the memory's transconductance and capacitance at different  $V_{GTS}$  by adjusting both  $W$  and  $L$  of the memory transistors, we chose to maintain the transconductance by only modifying the width  $W$ , which enabled us to use *multiples* of the unit transistor. This however did not maintain the memory speed ( $F_C = 1\text{MHz}$ ) and so we compensated this by adding a sufficient number of unit capacitors. The total composite memory's transconductance and capacitance were held at  $g_{mp} + g_{mn} = 50\mu\text{S}$  and  $C_{tot} = 3.5\text{pF}$ . In simulation, the cascade configuration of class AB memories in Fig. 2.1 was driven by an ideal input current source and was loaded by an identical 'diode-connected' memory cell.

**Table III** Extracted MOS Model Parameters for 0.35 $\mu$  Unit Transistors

| Parameter             | pMOS                   | nMOS                   |

|-----------------------|------------------------|------------------------|

| $I_S$ (A)             | $255 \times 10^{-9}$   | $231 \times 10^{-9}$   |

| $ V_T$ (V)            | 0.71                   | 0.50                   |

| $n$                   | 1.28                   | 1.26                   |

| $\theta$ (V $^{-1}$ ) | 0.805                  | 0.285                  |

| $WLC_{ox}$ (F)        | $44.8 \times 10^{-15}$ | $56.4 \times 10^{-15}$ |

**Table IV-A** Extracted MOS Model Parameters for  $0.18\mu$  Unit Transistors

| Parameter        | pMOS                    | nMOS                    |

|------------------|-------------------------|-------------------------|

| $I_S$ (A)        | $643 \times 10^{-9}$    | $585 \times 10^{-9}$    |

| $ V_T(V) $       | 0.22                    | 0.33                    |

| $n$              | 1.44                    | 1.35                    |

| $\theta(V^{-1})$ | 0.531                   | 0.656                   |

| $WLC_{ox}$ (F)   | $245.3 \times 10^{-15}$ | $205.6 \times 10^{-15}$ |

**Table IV-B** Extracted MOS Model Parameters for 90nm Unit Transistors

| Parameter        | pMOS                    | nMOS                    |

|------------------|-------------------------|-------------------------|

| $I_S$ (A)        | $480 \times 10^{-9}$    | $487 \times 10^{-9}$    |

| $ V_T(V) $       | 0.29                    | 0.23                    |

| $n$              | 1.16                    | 1.14                    |

| $\theta(V^{-1})$ | 0.943                   | 0.488                   |

| $WLC_{ox}$ (F)   | $171.2 \times 10^{-15}$ | $184.5 \times 10^{-15}$ |

(a) [Continued]

(b)

(c)

(d)

**Fig. 2.6** Simulated (markers) and theoretical (solid) plots of basic class AB SI performances in  $0.35\mu\text{m}$  CMOS process.

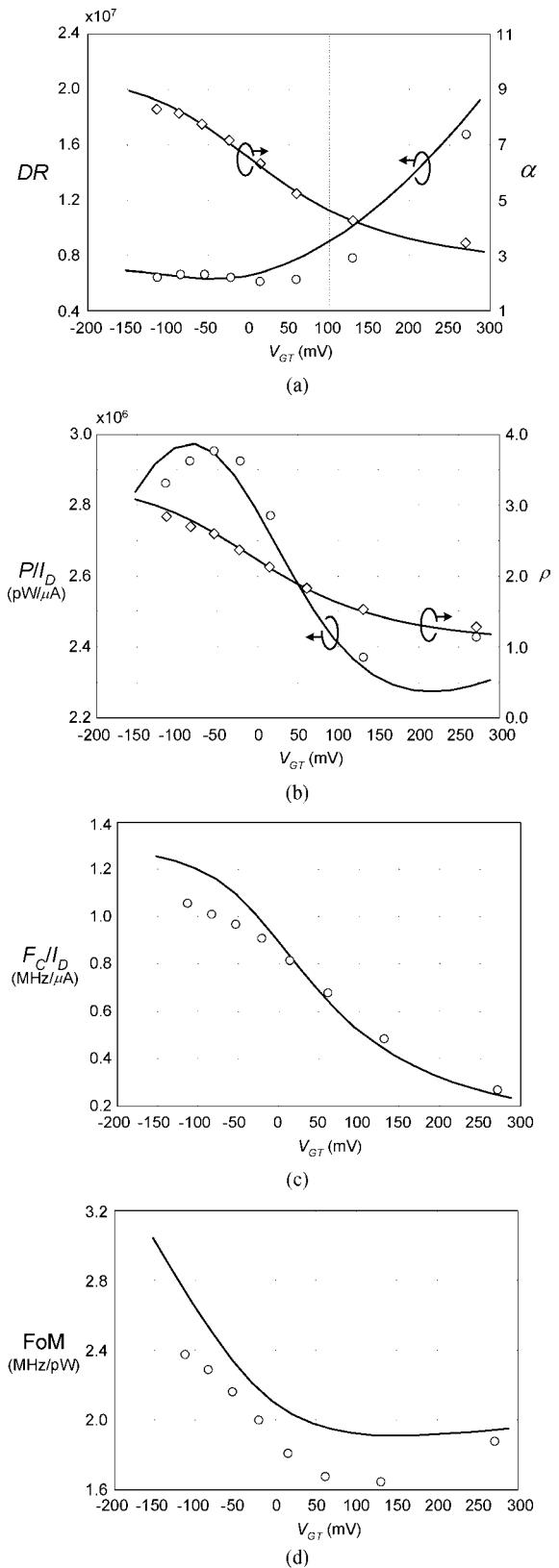

Fig. 2.6(a)-(d) show the simulated results of  $DR$ ,  $P/I_D$ ,  $F_C/I_D$  and FoM versus  $V_{GT}$  respectively, along with the plots of  $\alpha$  in Fig. 2.6(a) and  $\rho$  in Fig. 2.6(b). Normalising the operating speed and power for  $I_D$  removes the variation of  $I_D$  with  $V_{GT}$  and this enables easier comparison with the theoretical plots of Fig. 2.2 and Fig. 2.3. The calculated performances are also included in the figures where the maximum error percentages for each plot is about 8.6% for  $\alpha$ , 4.0% for  $\rho$ , 32.5% for  $DR$ , 5.1% for  $P/I_D$ , 15.7% for  $F_C/I_D$  and 17.3% for FoM. Some of the errors are quite significant due to an accuracy compromise of the extracted parameters needed to obtain good overall fit of the approximate model equation in (1a). However, a close relationship is observed in Fig. 2.6(a) to (d) between the calculated and simulated characteristics as the memory operation moves from strong to weak inversion. In this  $0.35\mu\text{m}$  CMOS process with the average  $V_T = (V_{TP} + V_{TN})/2 \approx 0.6\text{V}$  (see Table III), the FoMs of weak inversion SI are better than those of the strong inversion counterpart by a factor of 1.27 from simulation and a factor of 1.5 from calculation [Fig. 2.6(d)]. Although the improvement factor is modest (because the process has large  $V_T$ ), it should be noted that the strong inversion memory requires  $V_{DD} = 1.75\text{V}$  whereas the weak inversion SI operates at about  $V_{DD} = 1.0\text{V}$  which is a reduction by more than 40%.

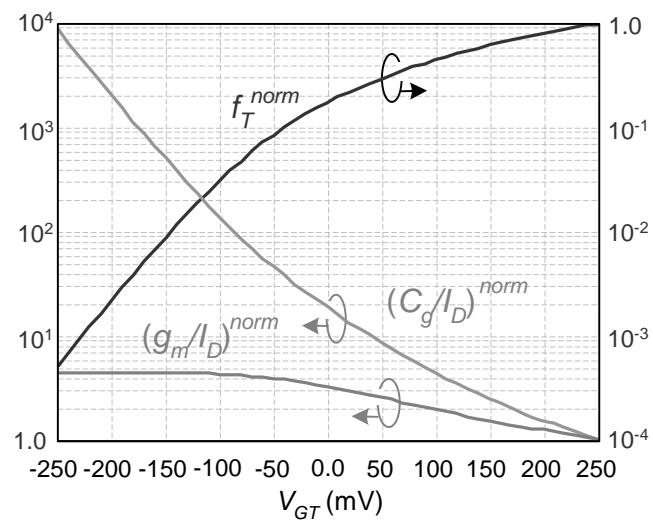

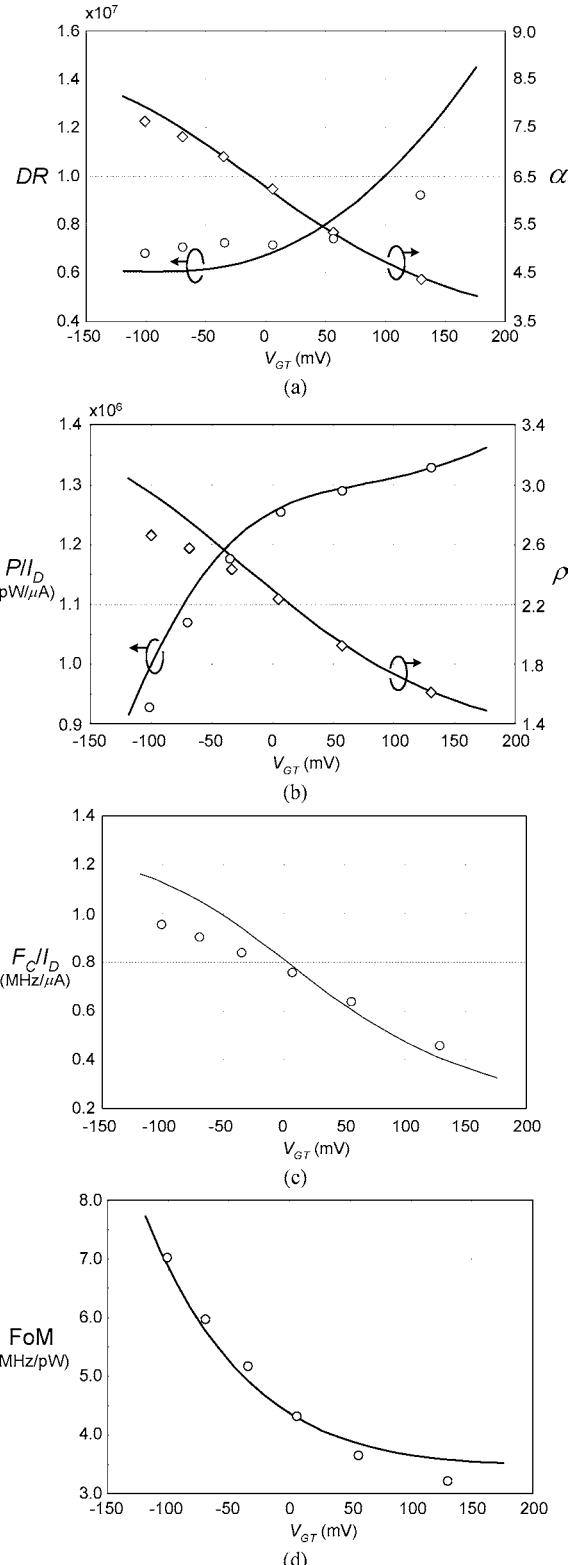

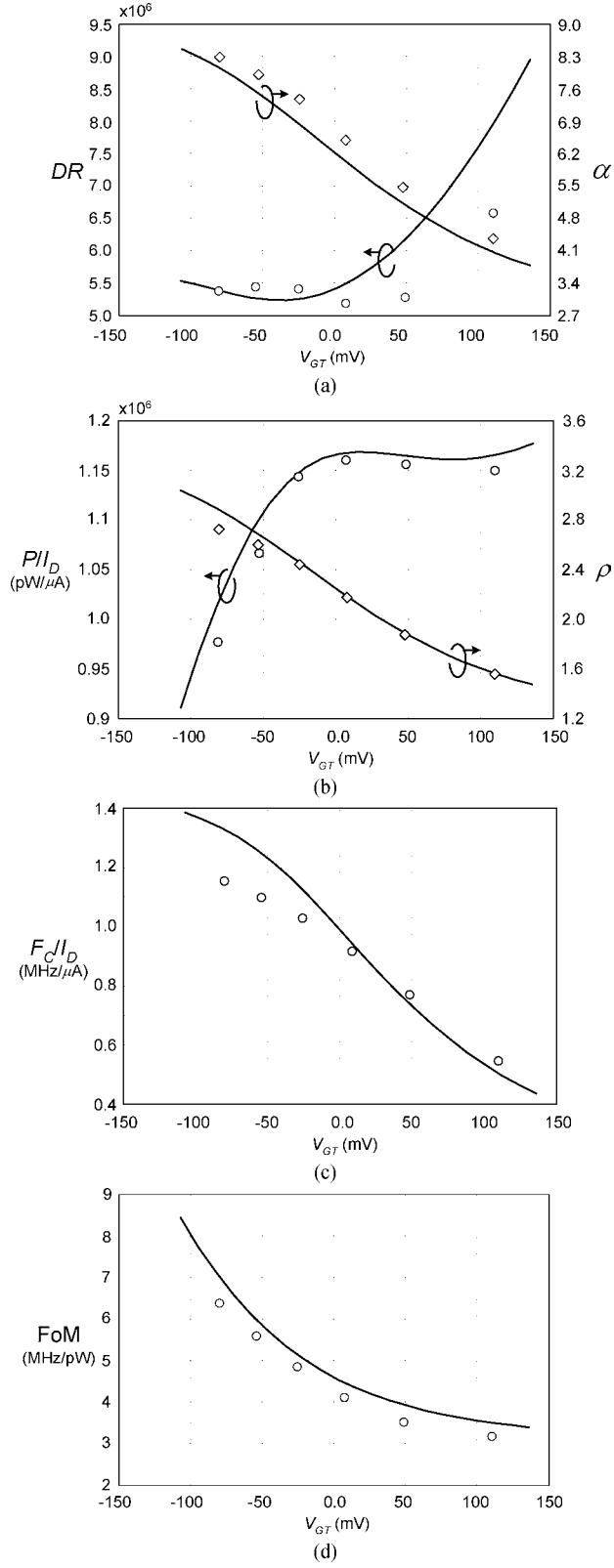

To show further the performance trend of the sub-threshold class AB SI memory, the same memory test as above was also conducted using low-threshold transistors of more advanced  $1.8\text{V } 0.18\mu\text{m}$  and regular transistors of  $1.2\text{V } 90\text{nm}$  CMOS processes with BSIM 3v3 MOS models. For the  $0.18\mu\text{m}$  process, the unit transistor dimensions were chosen at  $(W/L)_p = 9.5\mu\text{m}/3.0\mu\text{m}$  and  $(W/L)_n = 6.5\mu\text{m}/6.0\mu\text{m}$ . For the  $90\text{nm}$  process, the unit transistor dimensions were at  $(W/L)_p = 5.0\mu\text{m}/2.5\mu\text{m}$  and  $(W/L)_n = 3.0\mu\text{m}/5.5\mu\text{m}$ . From the simulated transistors' characteristics, the MOS parameters were extracted for theoretical computation and are summarized in Table IV-A for the  $0.18\mu\text{m}$  process, and Table IV-B for the  $90\text{nm}$  process. With similar total memory transconductance and capacitance to those of the  $0.35\mu\text{m}$  CMOS design, the simulated performance vectors versus  $V_{GT}$  are plotted in Fig. 2.7(a)-(d) and Fig. 2.8(a)-(d), along with the calculated results. For the  $0.18\mu\text{m}$  process, the maximum error percentages for each plot are about 4.9% for  $\alpha$ , 9.8% for  $\rho$ , 25% for  $DR$ , 8.1% for  $P/I_D$ , 18% for  $F_C/I_D$  and 12.8% for FoM. For the  $90\text{nm}$  process, the maximum error percentages for each plot are about 7.8% for  $\alpha$ , 7.4% for  $\rho$ , 21.2% for  $DR$ , 2.6% for  $P/I_D$ , 12.1% for  $F_C/I_D$  and 12.9% for FoM. Despite these errors, similar dependencies between the calculated and simulated characteristics are observed in all the performance metrics and for both processes. For the  $0.18\mu\text{m}$  process, it is noticed from the  $\alpha$  and  $\rho$  plots at weak inversion that both the peak current handling and supply current are reduced compared to those obtained from  $0.35\mu\text{m}$  and  $90\text{nm}$  CMOS. This is primarily due to the effect of asymmetrical slope factors  $n$  between the employed CMOS devices [see Table IV-A]. With such low threshold voltage processes, it is shown in Fig. 2.7(d) and 8(d) that the weak inversion SI has a FoM improvement of more than two for both simulations and calculations. The required supply voltage of the weak inversion SI is at  $V_{DD} = 0.35\text{V}$  for the  $0.18\mu\text{m}$  process, and  $V_{DD} = 0.36\text{V}$  for the  $90\text{nm}$  process. These are less than half of the supply voltage used for the strong inversion memories in the  $0.18\mu\text{m}$  and  $90\text{nm}$  processes ( $V_{DD} = 0.81\text{V}$  and  $0.74\text{V}$  respectively).

(a)

(b)

(c)

(d)

**Fig. 2.7** Simulated (markers) and theoretical (solid) plots of basic class AB SI performances in  $0.18\mu\text{m}$  CMOS process.

(a)

(b)

**Fig. 2.8** Simulated (markers) and theoretical (solid) plots of basic class AB SI performances in 90nm CMOS process.

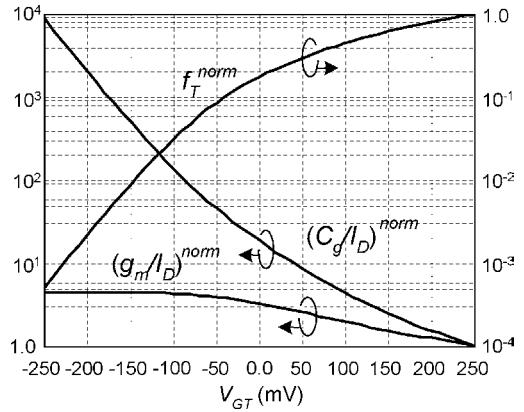

**Fig. 2.9** Normalised  $g_m/I_D$  and  $C_g/I_D$  and  $f_T$  characteristics versus  $V_{GT}$ .

## 2.5 Non-ideal Behaviours

This section describes important second-order non-idealities that affect SI performances in the sub-threshold operating region, specifically in terms of speed and transmission accuracy. These considerations are useful in designing and optimising sub-threshold SI circuits in practice.

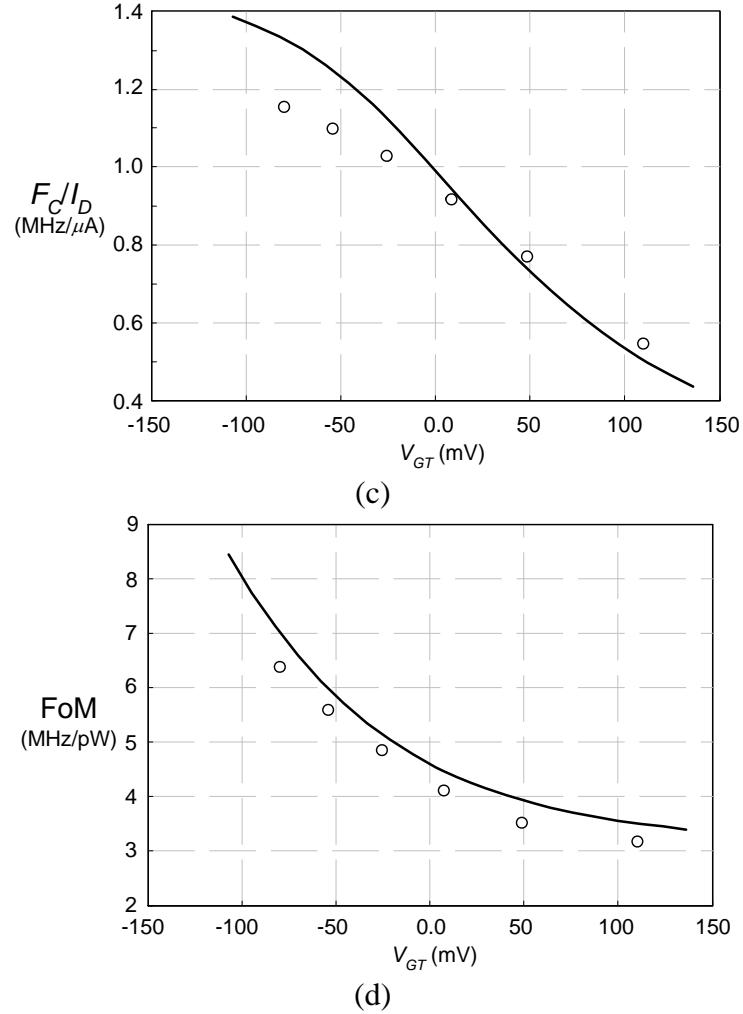

### A. Speed Limitation

It is generally known that the transition frequency  $f_T$ , which indicates the intrinsic maximum usable frequency in a MOS transistor at a given channel length  $L$ , is reduced with decreasing gate-overdrive voltage  $V_{GT}$ . In particular, it has been shown in [16] that, at strong inversion,  $f_T$  is proportional to  $V_{GT}$ . Eventually at weak inversion, it becomes dependent on the drain current  $I_D$  which is now related to  $V_{GT}$  exponentially, making  $f_T$  fall faster with  $V_{GT}$  than with strong inversion operation.

To investigate how this impacts speed performance, we have plotted the transition frequency  $f_T = g_m/2\pi C_G$  and the  $g_m/I_D$  and  $C_G/I_D$  ratios versus  $V_{GT}$  under a *constant* channel length  $L$ , by using (1a)-(1b) and (1c), and these are shown in Fig. 2.9. To facilitate the discussion, all the plots are normalized to their corresponding values in strong inversion operation with  $V_{GT} = 0.25V$ . From the normalised  $f_T$  characteristic in Fig. 2.9, when the transistor operation moves from the strong inversion to weak inversion, with  $V_{GT} = -0.1V$  as an example,  $f_T$  drops by more than thirty times. As indicated from the normalised  $g_m/I_D$  and  $C_G/I_D$  plots, such a significant  $f_T$  degradation is mainly attributed to a sharp increase in  $C_G/I_D$ , because a small  $V_{GT}$  in a sub-threshold MOS transistor requires a larger aspect ratio  $W/L$  for the same  $g_m$  and/or  $I_D$  when compared with strong inversion operation. At a constant channel length  $L$ , this results in a larger width  $W$  and hence a larger gate capacitance  $C_G (\propto W \cdot L)$ .

While design for sub-threshold operation has dramatically worsened the transistor's  $f_T$ , this does not imply a worsening of the SI memory's operating speed. This is because the memory capacitance  $C_G$  of a particular design, whether in strong or weak inversion, is chosen to meet a noise specification. So a sub-threshold design having the same speed as a strong inversion design can be achieved simply by choosing transistors with a larger  $W$  and smaller  $L$  (but with the same area  $W \cdot L$ ).

In SC, the situation is in absolute contrast. Unlike its SI counterpart, the gate capacitance  $C_G$  appears as a parasitic component. This creates non-dominant poles which may give rise to under-damped settling and even circuit instability. As a result, the considerably larger  $C_G$  of a sub-threshold MOS transistor adversely affects the SC speed performance.

### B. Transmission Accuracy

In SI, there are three major non-idealities that affect the memory's transmission accuracy: signal-dependent settling, charge injection of the memory's switches and finite output-input conductance ratio [1]. Since a class AB sub-threshold SI must handle input current which is much larger than its quiescent bias current, the transconductance  $g_m$  of the composite memory is heavily signal-dependent. This makes the memory's settling time considerably signal-dependent. However, since larger input current gives a larger  $g_m$  and hence a faster settling time, proper design of the memory's settling at a small input automatically

guarantees the required accuracy for the entire input range. As a result, the signal-dependent settling should not have a significant effect on the memory accuracy.

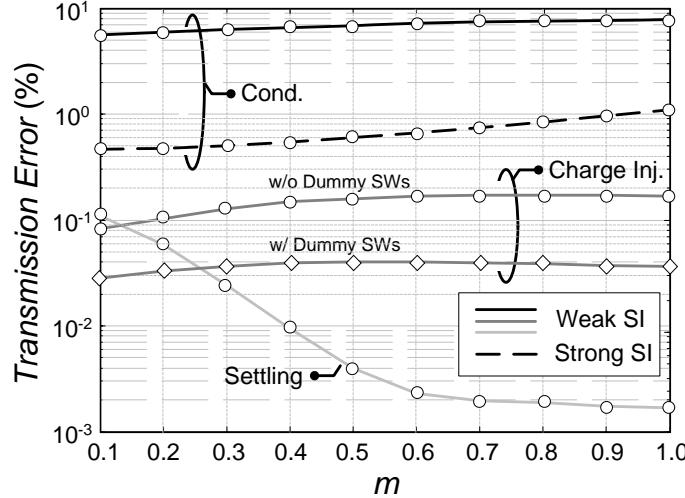

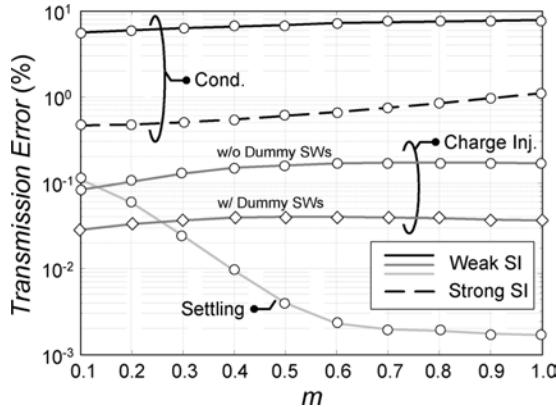

**Fig. 2.10** Simulated error performances of basic class AB SI from individual error source under strong and weak operations.

Due to inherently small signal voltage swings in sub-threshold SI, the signal-dependent component from charge injection is also small. A more critical issue is the absolute charge of the memory switches as this can give rise to signal-dependent error through the signal-dependent  $g_m$  of the composite memory. Nevertheless, this can be effectively reduced by the use of a balanced SI structure and the dummy switch technique [20].

As explained earlier, the small  $V_{GT}$  associated with sub-threshold operation results in transistors with larger width  $W$  and smaller length  $L$  compared to their strong inversion counterpart. The transmission error resulting from finite output-input conductance ratio arises because of channel length modulation ( $\propto 1/L$ ) and feedback to the gate capacitance  $C_G$  via the drain-gate overlap capacitance  $C_{DG}$  ( $C_{DG}/C_G \propto 1/L$ ). So, output-input conductance ratio transmission errors are correspondingly higher in sub-threshold operation and must be accommodated by the chosen circuit technique.

The contribution of each non-ideal effect for each region of operation, including signal-dependent settling, charge injection and finite conductance ratio, was examined via simulation of the individual transmission errors. To enable the study, certain components or parameters were made ideal in the memory under test so that only the non-ideality under consideration became the major error source: to eliminate charge injection errors, ideal memory switches were employed; to suppress conductance errors, the memory was equipped with an ideal active feedback amplifier; to minimize the signal-dependent settling, considerable extension of the sampling period was allowed.

The resulting individual memory transmission error for the balanced weak inversion memory using  $0.18\mu\text{m}$  CMOS process data with  $V_{GT} = -0.10\text{V}$  are depicted in Fig. 2.10. The errors are plotted versus the input current modulation index  $m$ , defined as the ratio of the signal current to its maximum value,  $i_{in}/\hat{i}_{in}$ . It is seen that the settling error is small and improves with larger  $m$  due to a higher  $g_m$ . The charge injection error is practically independent of the input

signal level due to the balanced structure and it is effectively reduced by using dummy switches. Contributing most to the memory's overall error is that resulting from the finite output-input conductance ratio. Compared with a similar strong inversion design ( $V_{GT} = -0.13V$ ) the error is about ten times worse.

In summary, the basic class AB memory has higher transmission error when operated in weak inversion. To achieve good performance, these errors must be controlled by more sophisticated circuit techniques and two such examples are described in the next section.

## 2.6 Practical Designs

### A. Cascode Design

To demonstrate the feasibility of the sub-threshold SI technique in practice, we have designed and simulated a balanced weak inversion class AB SI memory in  $0.35\mu\text{m}$  CMOS. The design was based on the memory cell tested in Section IV-B at  $V_{DD} = 1.0\text{V}$  with the cascaded memory arrangement for accuracy enhancement [10]. For the test configuration, the memory cell was driven by a differential current source and the load was formed by an identical diode-connected memory. The operating clock frequency was at 1MHz and the total quiescent drain current was  $I_D = 2\mu\text{A}$ . The supply regulation scheme in [10] was also adopted to regulate the quiescent current and this increased the operating supply voltage to  $V_{DD} = 1.25\text{V}$  to accommodate the additional voltage headroom. The designed transistor dimensions are as follows: for memory transistors,  $(W/L)_p = 588\mu\text{m}/2.5\mu\text{m}$  and  $(W/L)_n = 384\mu\text{m}/4.0\mu\text{m}$ , for cascaded transistors,  $(W/L)_{Cp} = 588\mu\text{m}/0.35\mu\text{m}$  and  $(W/L)_{Cn} = 384\mu\text{m}/0.35\mu\text{m}$ .

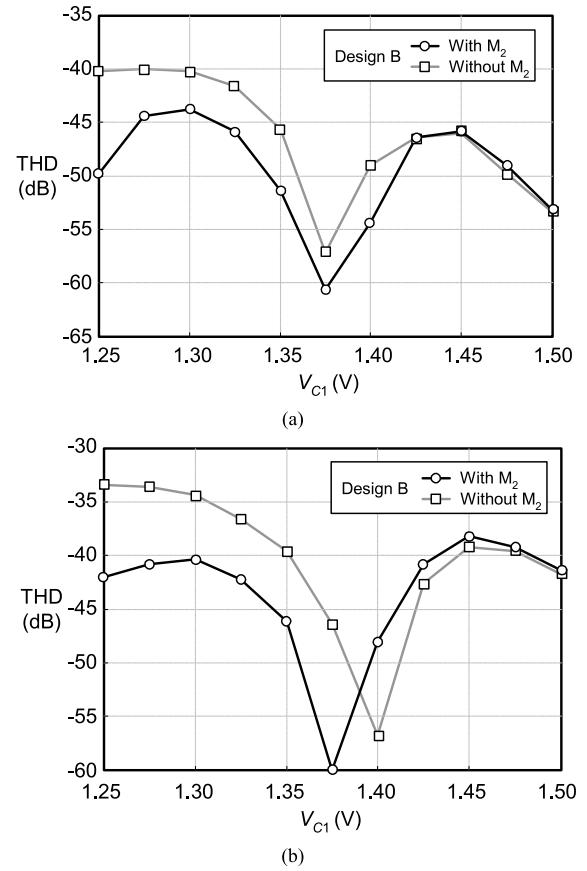

The simulated accuracy performance of the weak inversion memory cell versus modulation index,  $m$  is summarised in Table V-A for extreme process and temperature conditions. The table indicates that a memory error of less than 0.8% can be achieved over the entire input range. Also, at  $m = 1$ , the simulated THD is less than  $-40\text{dB}$  even under extreme conditions. Table VI summarises the practical performances. It should be noted that as compared to the simulated plots of Fig. 2.6(a) to 6(c), due to the balanced structure,  $F_C/I_D$  is reduced by half whereas  $DR$  is increased by slightly less than twice (because of the additional noise from cascaded devices and switches). This yields the FoM of the balanced cascaded SI memory slightly less than the simulated plots at weak inversion of the basic class AB memory (Fig. 2.6(d)).

**Table V-A** Transmission Performance of Weak Inversion Cascoded Class AB SI

| Modulation Index ( $m$ ) | Transmission Error (%) |                  |             |

|--------------------------|------------------------|------------------|-------------|

|                          | Slow<br>100°C          | Typical<br>40 °C | Fast<br>0°C |

| 0.2                      | 0.14                   | 0.15             | 0.25        |

| 0.4                      | 0.15                   | 0.11             | 0.28        |

| 0.6                      | 0.18                   | 0.15             | 0.25        |

| 0.8                      | 0.19                   | 0.19             | 0.54        |

| 1.0                      | 0.35                   | 0.25             | 0.78        |

**Table V-B** Transmission Performance of Weak Inversion Class AB S2I

| Modulation Index ( $m$ ) | Transmission Error (%) |                 |             |

|--------------------------|------------------------|-----------------|-------------|

|                          | Slow<br>100°C          | Typical<br>40°C | Fast<br>0°C |

| 0.2                      | 0.20                   | 0.08            | 0.17        |

| 0.4                      | 0.31                   | 0.15            | 0.27        |

| 0.6                      | 0.51                   | 0.33            | 0.50        |

| 0.8                      | 0.77                   | 0.55            | 0.78        |

| 1.0                      | 0.98                   | 0.78            | 0.96        |

**Table VI** Typical Performance Summary of Practical Balanced SI Memories

| Memory design                                  | 0.35 $\mu$ Cascoded<br>SI | 0.18 $\mu$ S <sup>2</sup> I |

|------------------------------------------------|---------------------------|-----------------------------|

| pMOS memory size                               | 588 $\mu$ /2.5 $\mu$      | 304 $\mu$ /3.0 $\mu$        |

| nMOS memory size                               | 384 $\mu$ /4.0 $\mu$      | 208 $\mu$ /6.0 $\mu$        |

| Analog voltage                                 | 1.0V                      | 0.35V                       |

| Total quiescent<br>drain current               | 2 $\mu$ A                 | 4 $\mu$ A                   |

| $F_C$                                          | 1MHz                      | 1MHz                        |

| $P$                                            | 5.8 $\mu$ W               | 2.6 $\mu$ W                 |

| $DR$                                           | 1.24x10 <sup>7</sup>      | 0.66x10 <sup>7</sup>        |

| FoM <sup>*</sup>                               | 2.14MHz/pW                | 2.54MHz/pW                  |

| Transmission Error <sup>**</sup> (@<br>$m=1$ ) | 0.78%                     | 0.96%                       |

| THD <sup>**</sup> (@ $m=1$ )                   | -40.9dB                   | -38.6dB                     |

| Supply voltage                                 | 1.25V                     | 0.6V                        |

<sup>\*</sup> Calculated from analog voltages

<sup>\*\*</sup> Worst case performances under fast processes and 0°C

## B. Two-Step Design

Due to insufficient voltage headroom, the cascaded memory enhancement becomes ineffective for the weak inversion SI in the 0.18 $\mu$ m CMOS using low-voltage transistors. One of the existing techniques readily applicable at very low supply voltages is the class AB two-step sampling SI, S<sup>2</sup>I [9]. Due to the use of a coarse and fine parallel memory configuration, some FoM degradation is expected in the weak inversion S<sup>2</sup>I memory. Since the settling of input signal is continued from coarse to fine phases, the S<sup>2</sup>I memory exhibits identical speed to its basic counterpart. In terms of power, as the fine memory only needs to handle the small residue input current left from the coarse phase, additional dynamic current close to the memory quiescent bias is required. Due to a high average drain current over the quiescent bias ( $\rho \sim 3.37$ ) in the weak inversion memory cell, this only slightly increases the total power consumption. For the noise performance, the inclusion of the fine memory doubles the total noise power compared to that of the basic cell. By taking these considerations into the general FoM expression of the basic class AB SI in (5), the FoM of class AB S<sup>2</sup>I in weak operation can be given as

$$\text{FoM}_{S^2I}^{weak} = \frac{2.8}{NkT_j} \cdot \frac{\phi_t}{V_{DD}} \quad (10)$$

Comparing this with the FoM of the basic weak inversion SI in Table I, overall performance degradation by about a factor of 2.6 is expected from the use of the S<sup>2</sup>I technique. For the 0.18 $\mu\text{m}$  process employed in Section V-B, this makes the FoM performance of the S<sup>2</sup>I memory slightly less than its basic counterpart in strong inversion. Although the enhancement technique seems to undo the FoM benefit of weak inversion SI, such a drawback should be outweighed by the ability to operate at a very low supply voltage with good accuracy.

The balanced class AB weak inversion S<sup>2</sup>I memory using low voltage transistors in the 1.8V 0.18 $\mu\text{m}$  process was designed at  $F_C = 1\text{MHz}$  where the transistor dimensions for both coarse and fine memories are given at  $(W/L)_p = 304\mu\text{m}/3.0\mu\text{m}$  and  $(W/L)_n = 208\mu\text{m}/6.0\mu\text{m}$ . The supply voltage was 0.35V and the total quiescent bias current was 4 $\mu\text{A}$ . With the regulation circuitry, the supply was increased to 0.6V. As summarized in Table V-B, simulation indicates an accuracy of better than 1.0% under extreme processing and temperature. Also from the performance summary in Table VI, the simulated THD at  $m = 1$  is  $-38.6\text{dB}$  and the THD at  $m = 0.86$  is  $-40\text{dB}$ . It should be noted that the simulated FoM of the balanced S<sup>2</sup>I memory is about 20% less than the simulated FoM of the basic memory at strong inversion operation as indicated in Fig. 2.7(d).

## 2.7 Conclusions

The behaviour of the basic class AB SI memory with transistors operating in their sub-threshold region has been studied through the theoretical assessment of its overall performance using the general MOS equations valid for all regions of operation. Thanks to its ability to handle larger input signal current levels, basic sub-threshold SI operation has better performance with lower supply voltage than its strong inversion counterpart and this performance improves with the reducing threshold voltages which come with successive CMOS generations.

The theoretical performance analysis used a figure-of merit which embraced dynamic range, speed and power consumption and the results were extensively verified by both experiment and simulation using actual CMOS process data. It was found that while the theory was a little optimistic, it demonstrated similar behaviour and confirmed that sub-threshold operation gives worthwhile performance gains.

However, it was also found that sub-threshold design produced transistors with a large aspect ratio. This gave the basic class AB memory poor accuracy because the high output conductance produced large transmission errors. Enhanced circuit design was needed to overcome this shortcoming of the basic memory.

Two enhanced circuit styles were investigated: cascoding using a 0.35 $\mu\text{m}$  CMOS process, and two-step sampling using a 0.18  $\mu\text{m}$  CMOS process. These designs were successful in restoring the accuracy but at some further cost to performance. Nevertheless, these designs demonstrated in a practical way that sub-threshold SI can produce much lower voltage operation without loss of performance when compared with strong inversion design. While the achievement of accurate low voltage operation and the realization of the full promise of performance improvement remain a challenging research goal, this work has nevertheless

demonstrated that sub-threshold SI is a viable analogue technique for the implementation of very low voltage CMOS circuits and systems, such as emerging implantable biomedical electronic devices.

## References

- [1] C. Toumazou, J. B. Hughes, and N. C. Battersby (eds), *Switched-Currents: An Analogue Technique for Digital Technology* Peter Perigrinus Ltd, 1993.

- [2] J. B. Hughes, K. Moulding, J. R. Richardson, J. Bennett, and W. Redman-White, “Automated Design of Switched-Current Filters”, *IEEE J. Solid-State Circuits*, vol. 28, pp. 314-322, 1993.

- [3] N. C. Battersby and C. Toumazou, “High-Frequency Fifth-Order Switched-Current Bilinear Elliptic Low-Pass Filter”, *IEEE J. Solid-State Circuits*, vol. 29, pp. 737-740, June 1994.

- [4] N. Moeneclaey, and A. Kaiser, “Design Technique for High Resolution Current-Mode Delta-Sigma Modulator”, *IEEE J. Solid-State Circuits*, vol. 32, pp. 953-958, July 1997.

- [5] K. Koli and K. Halonen, “A Fully Differential Class AB Switched-Current Integrator for Signal Processing”, *IEEE J. Solid-State Circuits*, vol. 32, pp. 238-244, Feb. 1997.

- [6] B. Stefanelli, I. O. Connor, L. Quiquerez, A. Kaiser, D. Billet, “An Analog Beam-Forming Circuit for Ultrasound Imaging Using Switched-Current Delay Lines”, *IEEE J. Solid-State Circuits*, vol. 35, pp. 202 – 211, Feb. 2000.

- [7] J. M. de la Rosa, B. Perez-Verdu, R. del Rio, A. Rodriguez-Vazquez, “A CMOS 0.8- $\mu$ m Transistor-only 1.63-MHz Switched-current Bandpass  $\Sigma\Delta$  Modulator for AM Signal A/D Conversion”, *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1220-1226, Apr. 2000

- [8] G. K. Balachandran, P. E. Allen, “Switched-Current Circuits in Digital CMOS Technology with Low-Charge Injection Errors”, *IEEE J. Solid-State Circuits*, vol. 37, pp. 1271– 1281, Oct. 2002.

- [9] A. Worapishet, J. B. Hughes and C. Toumazou, “Low Power High-Frequency Class AB Two-Step Sampling Switched-Current Techniques”, *IEEE Trans. Circuits .Syst. II*, vol. 50, pp 649-653, Sept. 2003.

- [10] A. Worapishet, R. Situdhikorn, A. Spencer and J. B. Hughes, “A Multi-rate Switched-Current Filter Using Class AB Cascoded Memory”, *IEEE Trans. Circuits .Syst. II*, vol. 53, No. 11, pp 1323-1328, Nov. 2006.

- [11] C. C. Tsai, C. H. Lai, W. T. Lee and J. O. Wu, “10-bit switched-current digital-to-analogue converter”, *IEE Proc.-Circuits Devices Syst.*, Vol. 152, No. 3, pp. 287-290 , June 2005.

- [12] T. Yamasaki, T. Nakayama, and T. Shibata, “A Low-Power and Compact CDMA Matched Filter Based on Switched-Current Technology”, *IEEE J. Solid-State Circuits*, vol. 40, no. 4, pp. 926-932, Apr. 2005

- [13] S. Y. Lee, and C. J. Cheng, “A Low-Voltage and Low-Power Adaptive Switched-Current Sigma-Delta ADC for Bio-Acquisition Micro-systems”, *IEEE Trans. Circuits .Syst. I* , vol. 53, no. 12 pp 2628-2636, Dec. 2006.

- [14] J. B. Hughes, A. Worapishet and C. Toumazou, “Switched-Capacitors versus Switched-Current: A Theoretical Comparison”, *Proceedings of IEEE ISCAS*, vol. 2, pp 409-412, 2000.

- [15] J. B. Hughes and A. Worapishet, "Switched-Capacitors or Switched-Current, Which Will Succeed?," in C. Toumazou and G. Moschytz (Eds.): Understanding Trade-Offs in Analog Design, Kluwer Academic Publishers, 2001, Chap. 11, pp.491-515

- [16] Y. P. Tsividis, *Operation and Modeling of The MOS Transistor*, 2<sup>nd</sup> Edition, McGraw-Hill 1999.

- [17] Y. P. Tsividis, "Externally Linear, Time-Invariant Systems and Their Application to Companding Signal Processors", *IEEE Trans. Circuits .Syst. II*, vol. 44, pp. 65-85, Feb. 1997.

- [18] C. Enz, M. Punzenberger, and D. Python, "Low-Voltage Log-Domain Signal Processing in CMOS and BiCMOS", *IEEE Trans. Circuits .Syst. II*, vol. 46, pp 279-289, March 1999.

- [19] N. Kontogiannopoulos, C. Psychalinos, "Switched-Current Filters Revisited: Square-Root Domain Sampled-Data Filters", *IEEE Trans. Circuits .Syst. II*, vol. 53, no. 12, pp 279-289, Dec. 2006.

- [20] J. B. Hughes, A. Worapishet, R. Sitzhikorn, "Low Voltage Techniques for Switched-Current Filters", in Y.Sun (Ed.): Design of High Frequency Integrated Analogue Filters, IEE Circuits, Devices and Systems Series, 2002, Chap. 5, pp. 125-160.

### 3. Very Low Voltage Mixer Techniques for 0.5-V Operation

#### 3.1. Introduction

With potential applications in environmental monitoring, surveillance, health-care, security etc, wireless sensor networks have been envisaged as holding promise for future ubiquitous wireless computing systems [1]. Among the essentials to a full scale deployment of such sensor networks are analogue techniques that can enable efficient operation at a very restricted supply voltage level. In response to this demand, various innovative circuits fully compatible with an ultra-low supply voltage in nanoscale CMOS have been demonstrated. These include an OTA for filter applications [2], passive analogue sampling circuits [3], [4], and an active track-and-hold circuit [5] for ADC applications — all operating at a 0.5-V supply voltage using *standard* transistors. Also developed were techniques for time-constant tuning based upon variable capacitors [2] and sub-threshold MOSFET operation [6,7]. To complement the ultra-low supply scenario, a circuit arrangement for a mixer with a commensurate supply voltage requirement is introduced in this letter, with the targeted application for baseband demodulators of wireless sensor transceivers.

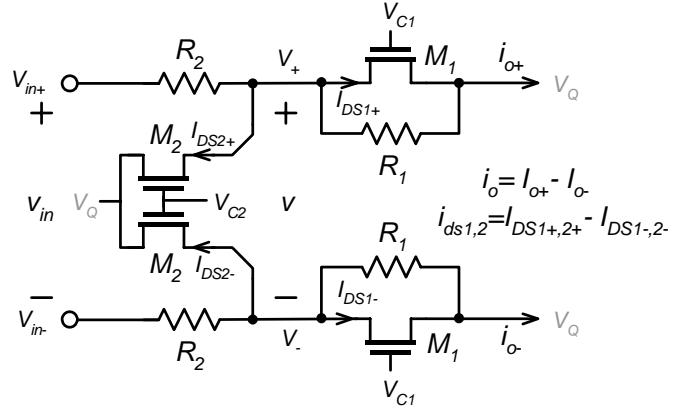

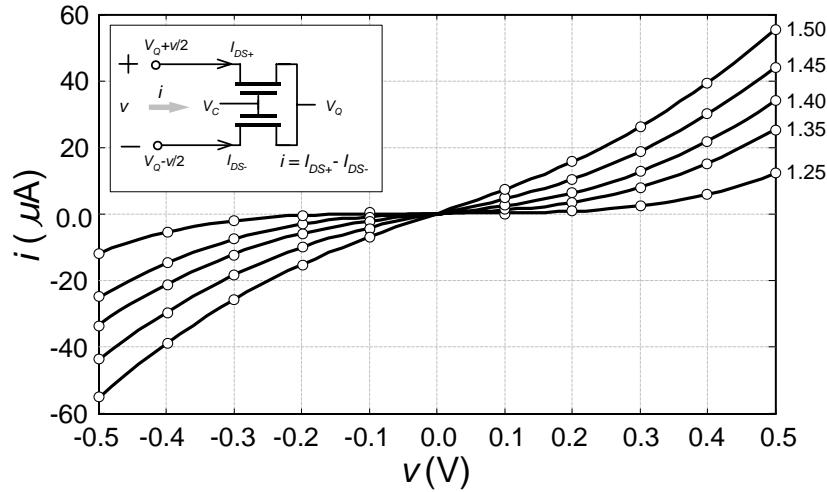

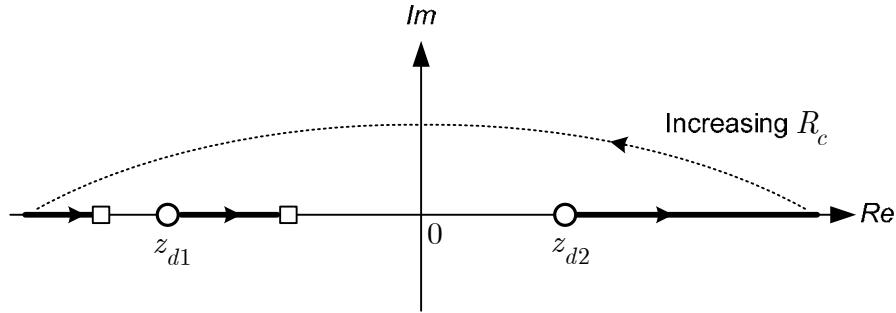

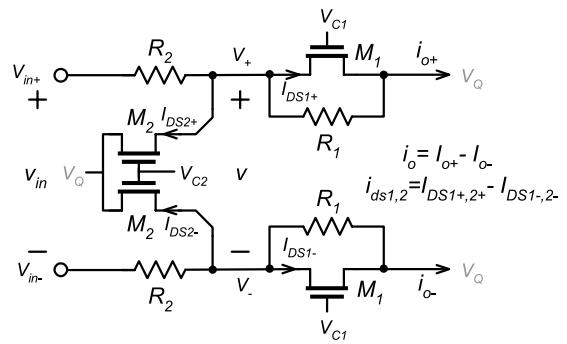

#### 3.2 Circuit Structure

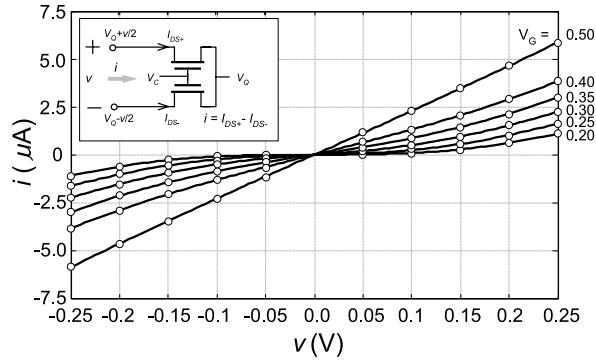

Traditionally, a mixer topology for down-conversion and baseband applications makes use of four cross-coupled MOS transistors operated in *strong* inversion and triode region, with one of their drain/source terminals connected to a virtual ground [8], [9]. At a reduced supply voltage however, such a topology shares a similar difficulty to conventional tunable MOS resistors for integrated continuous-time filters [2]. Both require excessive headroom, particularly for the input voltages at the gate terminals, so as to keep the transistors in their strong triode operation at all times. Thus, without the use of a charge pump which may entail a reliability issue, the quad MOS transistors can be pushed into sub-threshold conduction, especially at the negative swing of the gate inputs. In effect, the mixer is turned to operate in a current commutation manner, where each of the transistor pairs takes turn to conduct during each half of the input cycle. This in turn degrades the linearity since the dependence of  $g_{DS}$  on  $V_{DS}$  is now highly nonlinear and can no longer be suppressed by virtue of the double-balanced structure [7]. Moreover, the conversion gain of the mixer is degraded due to a significant reduction of  $g_{DS}$  at sub-threshold conduction. With a continued supply reduction to a very low voltage, the mixer may cease to operate entirely.

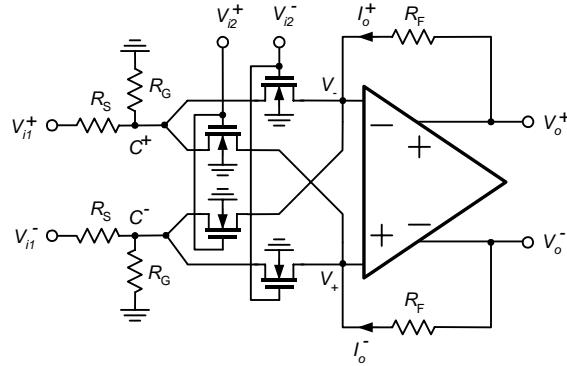

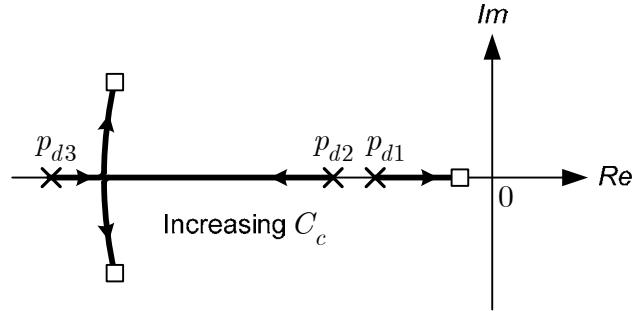

**Fig. 3.1** Very low voltage mixer topology

Fig. 3.1 shows an enhanced low-voltage mixer topology where it resembles the conventional triode-biased mixer, but with the incorporation of the linear resistors  $R_S$  and  $R_G$  at the drain/source terminals of the quad transistors. In the circuit, one of the differential input signals is applied at the resistors' terminals,  $v_{i1}^{+/-}$ , and the other at the transistors' gates,  $v_{i2}^{+/-}$ . The mixing output current  $I_o^{+/-}$  is converted to the differential voltage,  $v_o^{+/-}$ , by the feedback resistors  $R_F$ . The resistor network serves as a voltage division that essentially pulls down the drain/source terminals of the quad MOS transistors below the quiescent bias voltage of  $v_{i1}^{+/-}$  (typically at a mid-supply level), thereby enlarging the gate overdrives and pushing the devices' operation back towards strong inversion. In addition,  $R_S$  and  $R_G$  together form an equivalent linear resistor in series with the quad transistors, yielding a significant improvement in the linearity as it helps suppress the effect of the nonlinear  $g_{DS}$ - $V_{DS}$  characteristics contributed by the transistors, especially when they are in sub-threshold conduction. It is worth noting that the grounded resistors  $R_G$  in Fig. 3.1 can be replaced by a current source to produce a similar extended operation in the transistors, but this is not the choice here due to the associated flicker noise.

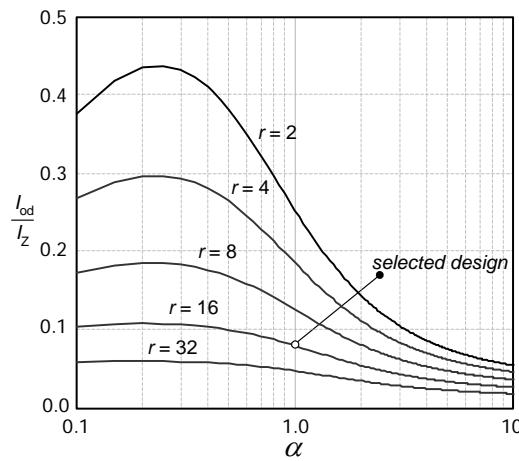

**Fig. 3.2** Plot of the normalized differential peak output current versus the design parameters  $r$  and  $\alpha$

### 3.3 Mixer Design

Of prime importance is a careful design methodology of the very low voltage mixer, due to a limited available signal swing at a low supply voltage. Also, due to such a wide coverage of the MOSFET's operation, it is obliged to employ a general current-voltage MOS equation valid for all regions in the analysis. This may be given by [9]:

$$I_{DS} = 2m\varphi_t^2 \beta \left( \ln 2 \left[ \frac{V_{GB} - V_{T0} - mV_{SB}}{1 + e^{\frac{V_{GB} - V_{T0} - mV_{SB}}{2m\varphi_t}}} \right] - \ln 2 \left[ \frac{V_{GB} - V_{T0} - mV_{DB}}{1 + e^{\frac{V_{GB} - V_{T0} - mV_{DB}}{2m\varphi_t}}} \right] \right) \quad (1)$$

with  $m = \left( 1 - \gamma/2 \sqrt{V_{GB} - V_{T0} + (\gamma/2 + \sqrt{\varphi_0})^2} \right)^{-1}$

where  $\beta = \mu C_{ox} W/L$  is the transconductance parameter,  $\varphi_t = kT/q$  is the thermal voltage,  $\mu$  is the carrier effective mobility in the channel,  $C_{ox}$  is the gate-oxide per unit area,  $W$  and  $L$  are the channel width and length,  $V_{T0}$  is the threshold voltage at  $V_{SB} = 0$ ,  $\gamma$  is the body effect coefficient,  $\varphi_0$  is a characteristic potential, and  $m$  is the slope factor. It is noted that the short-channel effects and the dependence of the mobility on the transversal field are not included in (1). By using (1), and applying KCL at the common node  $C^+$  or  $C$  ( $C^{+/-}$ ) of the circuit in Fig. 3.1, the following normalized equation can be obtained:

$$\begin{aligned} & \frac{v_{i1}^{+/-} - v_C^{+/-}}{r} \\ &= \frac{v_C^{+/-}}{\alpha r} - \left( \ln 2 \left[ 1 + e^{v_{i2}^+ - v_T - mv_C^{+/-}} \right] - \ln 2 \left[ 1 + e^{v_{i2}^+ - v_T - mv_{+/-}} \right] \right) \\ & \quad - \left( \ln 2 \left[ 1 + e^{v_{i2}^- - v_T - mv_C^{+/-}} \right] - \ln 2 \left[ 1 + e^{v_{i2}^- - v_T - mv_{-/+}} \right] \right) \end{aligned} \quad (2)$$

where the input voltages  $v_{i1,2}^{+/-}$ , the common node's voltages  $v_C^{+/-}$ , the threshold voltage  $V_{T0}$ , and the opamp's input voltages  $V_{+/-}$  [cf. Fig. 3.1] are all divided by  $2m\varphi_t$  to form the normalized variables  $v_{i1,2}^{+/-}$ ,  $v_C^{+/-}$ ,  $v_T$ , and  $v_{+/-}$  in (2), respectively. Also,  $\alpha = R_G/R_S$  and  $r = R_S\beta\varphi_t$ . Note that the normalization yields the closed-form equation in (2) which facilitates a systematic design as will be shortly described.

Given a set of dc bias and input signal levels, one can determine  $v_C^{+/-}$  based on numerical computation of (2). Subsequently, the normalized mixer's output currents  $I_o^{+/-}/I_Z$ , where  $I_Z = 2m\varphi_t^2 \beta$ , can be calculated as

$$\frac{I_o^{+-}}{I_Z} = \left( \ln 2 \left[ 1 + e^{v_{i2}^+ - v_T - mv_C^{+/+}} \right] - \ln 2 \left[ 1 + e^{v_{i2}^+ - v_T - mv_{-/+}} \right] \right) \\ + \left( \ln 2 \left[ 1 + e^{v_{i2}^- - v_T - mv_C^{+-/-}} \right] - \ln 2 \left[ 1 + e^{v_{i2}^- - v_T - mv_{-/+}} \right] \right) \quad (3)$$

For a particular set of conditions compatible with values assigned in the subsequent simulation, the numerical plot of the normalized *differential peak* output current,  $\hat{I}_{od}/I_Z = (\hat{I}_o^+ - \hat{I}_o^-)/I_Z$  can be determined using (3). This is given in Fig. 3.2 as a function of the design parameters  $r$  and  $\alpha$ . The plot indicates that, at a constant  $r$ , the output peak current increases with a successive reduction of  $\alpha$ . This trend holds until around  $\alpha = 0.2$  to  $0.3$  where only a marginal improvement or even a drop in the output is obtained. For a constant  $\alpha$ , a smaller  $r$  results in a larger output but this can not be reduced indefinitely since a smaller  $r$  results in smaller  $R_S$  and  $R_G$ , and there exists a limit determined by the driving capability of the preceding stage.

### 3.4 Design and Performance Verification

The mixer in Fig. 3.1 has been designed and simulated using a 1.8V 0.18 $\mu$ m CMOS process. The supply voltage was set at 0.5V and the dc bias for  $v_{il,2}^{+/-}$  were both at 0.25V. The differential peak inputs were at  $\hat{v}_{id1} = \hat{v}_{il}^+ - \hat{v}_{il}^- = 0.2V_p$ , and  $\hat{v}_{id2} = \hat{v}_{i2}^+ - \hat{v}_{i2}^- = 0.4V_p$ . The dc bias of

(a) [Continued]

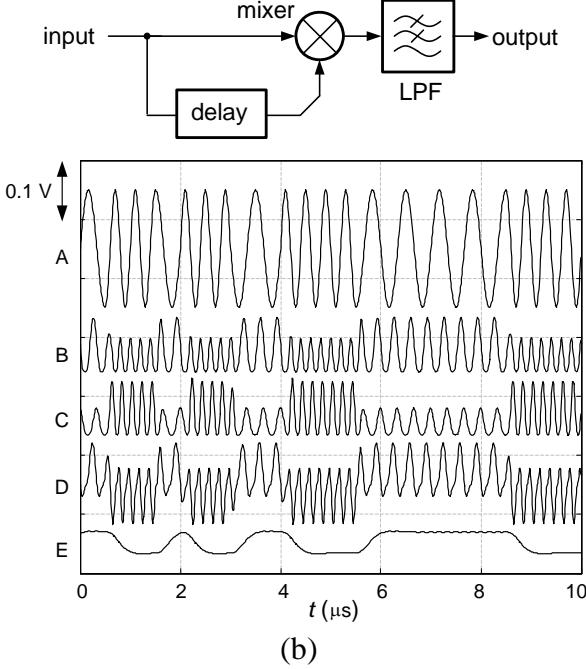

**Fig. 3.3** Simulated waveforms of (a) mixer with 50kHz and 2.0MHz inputs and (b) FSK demodulator.

its input terminals was set at  $V_+ = V_- = 0.4V$ . In order to demonstrate a very low voltage capability, the standard n-channel devices were used with  $W/L = 110\mu\text{m}/1.1\mu\text{m}$ . As extracted from simulation, this yields  $\beta = 25\text{mA/V}^2$  ( $I_Z = 45.6\mu\text{A}$  and  $1/\beta\varphi_t = 1.55\text{k}\Omega$ ) and  $V_{T0} \approx 0.4\text{V}$ . Based on Fig. 3.2, for the design case at  $r = 16$  and  $\alpha = 1.0$ ,  $R_S = R_G = 16/\beta\varphi_t \approx 25\text{k}\Omega$  were determined. This also results in the normalized differential peak output current at  $I_{od}/I_Z = 0.08$ . With  $R_F = 55\text{k}\Omega$ , the differential peak output voltage,  $\hat{V}_{od} = \hat{V}_o^+ - \hat{V}_o^-$ , is at  $|\hat{V}_{od}| = |\hat{I}_{od} \cdot R_F| \approx 0.2\text{V}_p$ . Since we have  $V_{ild} = 0.2\text{V}_p$ , the conversion gain is  $G = |\hat{V}_{od}/\hat{V}_{ild}| = \sim 1.0\text{V/V}$ .

Fig. 3.3(a) shows the simulated waveform (solid line) at the mixer's differential output for a 2MHz high frequency input at  $V_{i1}^{+/-}$  and a 50kHz low frequency input at  $V_{i2}^{+/-}$ . The resulting output differential peak voltage is at  $\sim 0.2\text{V}_p$ , yielding the down conversion gain at  $G = \sim 1.0\text{V/V}$ . Also given in the plot is the mixer's output with  $R_G$  in Fig. 3.1 removed (gray line), i.e.  $\alpha$  approaches infinity, where it is seen that the amplitude and hence the gain drops significantly by more than five folds. It should be noted that simulations of the mixer with other sets of the parameters, i.e.  $r$  ranging from 2 to 32, and  $\alpha$  from 0.5 to 2.0 [cf. Fig. 3.2], were also conducted and the resulting conversion gain exhibit good agreement with the theoretical analysis throughout.

The effectiveness of the designed mixer for use in a baseband application at a 0.5-V supply was also validated. It was employed as a mixer block in the differential delay demodulator for a low-IF IEEE 802.15.4 receiver (schematic as depicted in Fig. 3.3(b)), with the delay at  $-\pi/2$  phase shift for the low-IF of 2.0MHz. A 2-FSK modulated signal (a combination of I- and Q- O-QPSK signals compliant with IEEE 802.15.4 standard) was applied. Fig. 3.3 shows the simulated waveforms of the demodulator for the 1.5/2.5MHz FSK input at 2Mchip/s (trace A), the single-ended and differential outputs of the mixer (traces B, C, D, E).

C and D), and the filtered output (trace E). The filtered output matches well to that obtained from the ideal demodulator where the mixer was replaced by an ideal multiplier with the same conversion gain.

### 3.5. Conclusion

A very low voltage opamp-based mixer incorporating a linear resistor network to extend the operation of the cross-coupled triode transistors has been presented. Detailed analysis, design and verification have been provided. Its viability has been demonstrated via simulation and experiment where it has made possible an FSK demodulator's operation at a very restricted supply of 0.5V using standard transistors in a 1.8V 0.18 $\mu$ m CMOS. It should be noted that the technique is also readily applicable to extend the operation of the sub-threshold MOS resistor technique in [6], [7].

## References

- [1] Tsung-Hsien, L., Kaiser, W. J., Pottie, G. J., "Integrated Low-Power Communication System Design for Wireless Sensor Networks", *IEEE Communications Magazine*, vol. 42, no. 12, pp. 142-150, Dec. 2004.

- [2] Chatterjee, S., Tsividis, Y. P., and Kinget, P., "0.5-V Analog Circuit Techniques and Their Applications to OTA and Filter Design," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2373-2387, Dec. 2005.

- [3] Gambini S., and Rabaey, J., "A 1.5 MS/s 6-bit ADC with 0.5 V supply," in *Proc. Asian Solid State Circuits Conf. (ASCC)*, 2006, pp. 47-50.

- [4] Sauerbrey, J., Schmitt-Landsiedel, D., and Thewes, R., "A 0.5-V 1- $\mu$ w Successive Approximation ADC," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1261-1265, Jul. 2003.

- [4] Chatterjee, S., and Kinget, P., "A 0.5-V 1-MspS Track-and-Hold Circuit With 60-dB SNDR," *IEEE J. Solid-State Circuits*, vol. 42, no. 4, pp. 722-729, April 2007.

- [6] Worapishet, A., Khumsat, P., "Sub-threshold R-MOSFET tunable resistor technique", *Electronics Letters*, vol. 43, Issue 7, pp. 390 – 392, March 2007.

- [7] Worapishet, A., Khumsat, P., "Analysis and design of sub-threshold R-MOSFET tunable resistor", *IEICE Trans. Electronics*, Vol. EC92-C, No. 1, pp. 135-143, January, 2009.

- [8] Song, B. S., "CMOS RF Circuits for Data Communications Applications", *IEEE J. Solid-State Circuits*, vol. 21, no.2, pp. 310-317, April 1986.

- [9] Crols, J., and Steyaert, M. S., "A 1.5-GHz Highly Linear CMOS Downconversion Mixer", *IEEE J. Solid-State Circuits*, vol. 30, no. 7, pp. 736-742, July 1995.

- [10] Y. P. Tsividis, *Operation and Modeling of The MOS Transistor*, 2<sup>nd</sup> Edition, McGraw-Hill 1999.

- [11] A. Worapishet, and T. Demeechai, "Accurate Signal-to-Noise Analysis of Derivative and Quadrature Differential FM Discriminators Based on Multi-Sinusoidal AWGN Representation" to appear in *IEICE Trans. Fundamental Theory and Applications*, Vol.E93-A, No. 10, Oct. 2010.

## 4. Sub-threshold Resistor-MOSFET Tunable Resistor Technique

### 4.1 Introduction

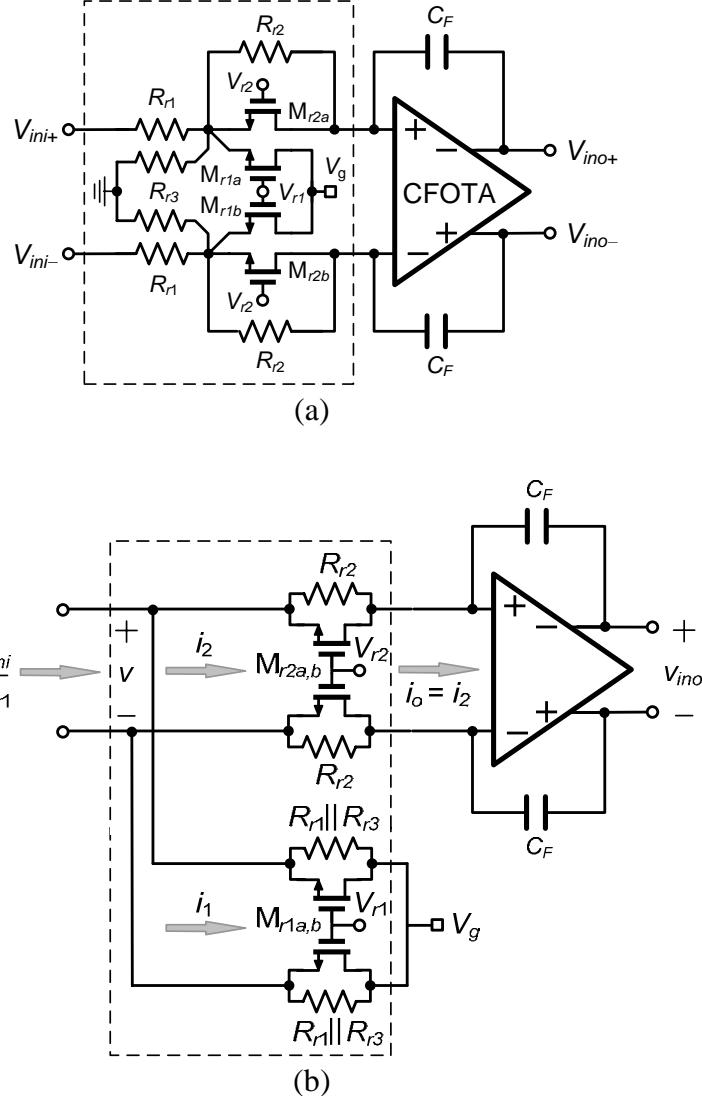

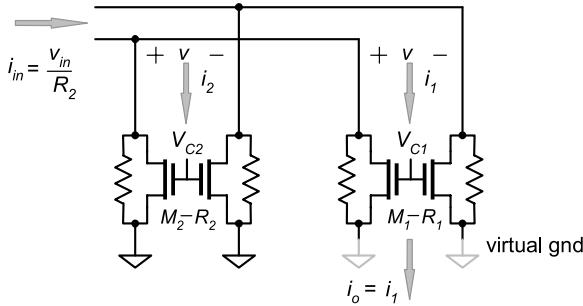

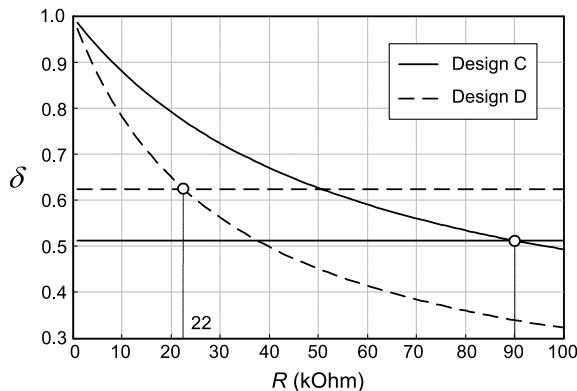

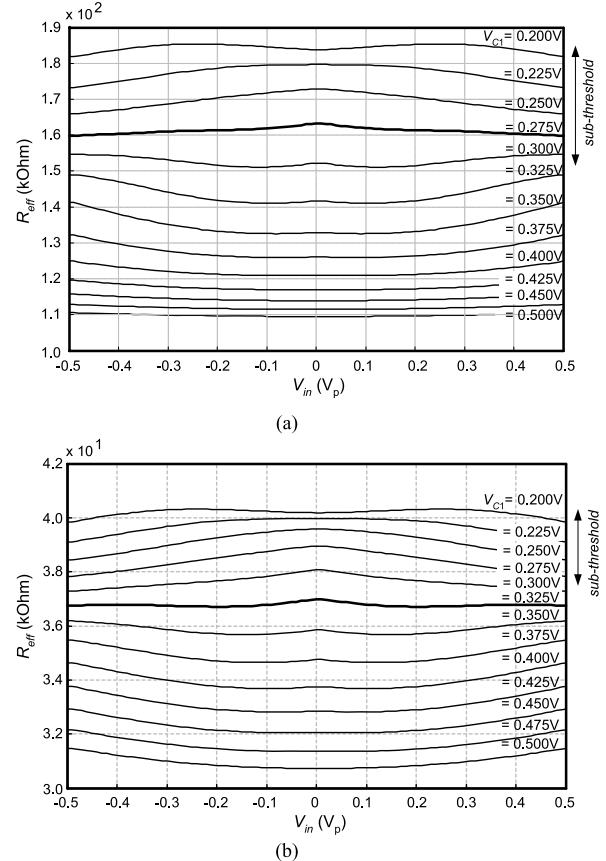

With the continued reduction of supply voltages due to aggressive downsizing of transistors in modern CMOS processes, the design of analog circuits that co-integrate with digital circuits on the same chip with sufficient performance promises to be increasingly challenging. For analog filtering applications, continuous-time (CT) MOSFET-C and linearity enhanced R-MOSFET-C techniques that employ no switches as well as no anti-aliasing and smoothing filters have been demonstrated as attractive alternatives to sampled-data switched-capacitor (SC) filters at low voltages [1-4]. One major issue however for the low-voltage CT filters is the limited range of the gate voltage available for tuning the corner frequency through the MOSFET resistance so as to cope with inevitable process and temperature variations. Although this may be circumvented either by using native transistors, low threshold transistors or thick oxide transistors, a control voltage larger than the supply is often necessary, thereby necessitating a clock boosting circuitry which invariably poses reliability concerns on the devices. Another means is to employ the variable MOS capacitors [1], but a switched array of parallel *linear* capacitors for coarse tuning must be included to achieve a good linearity and adequate overall tuning range.

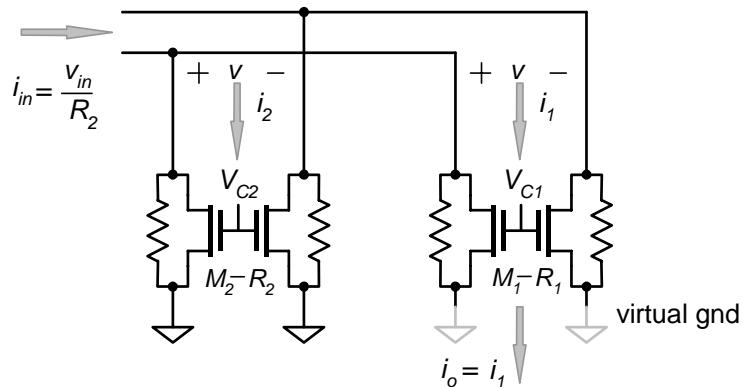

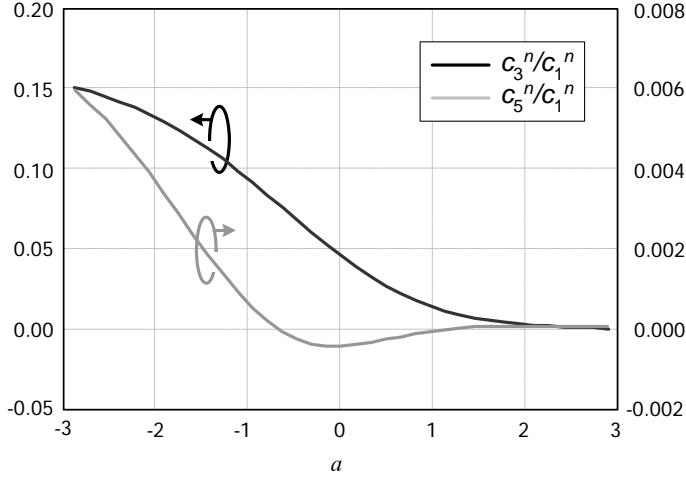

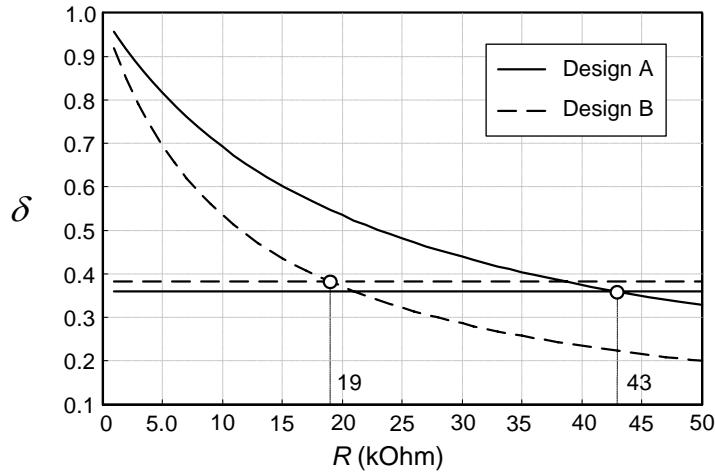

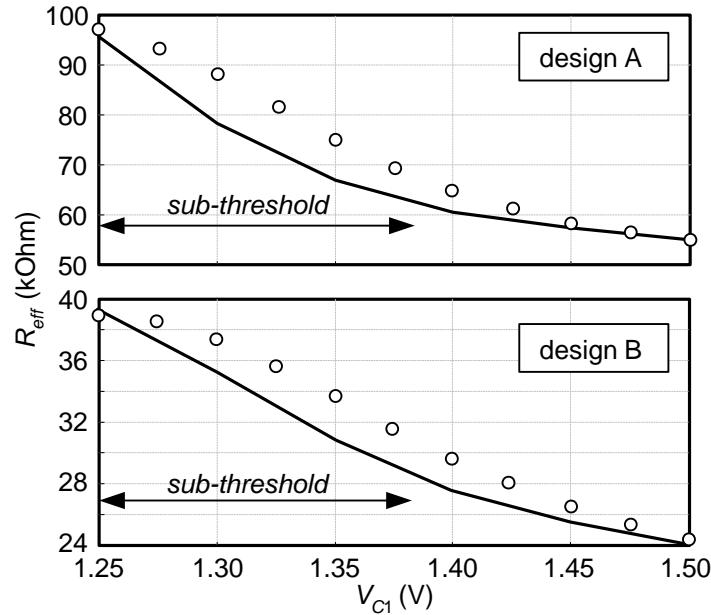

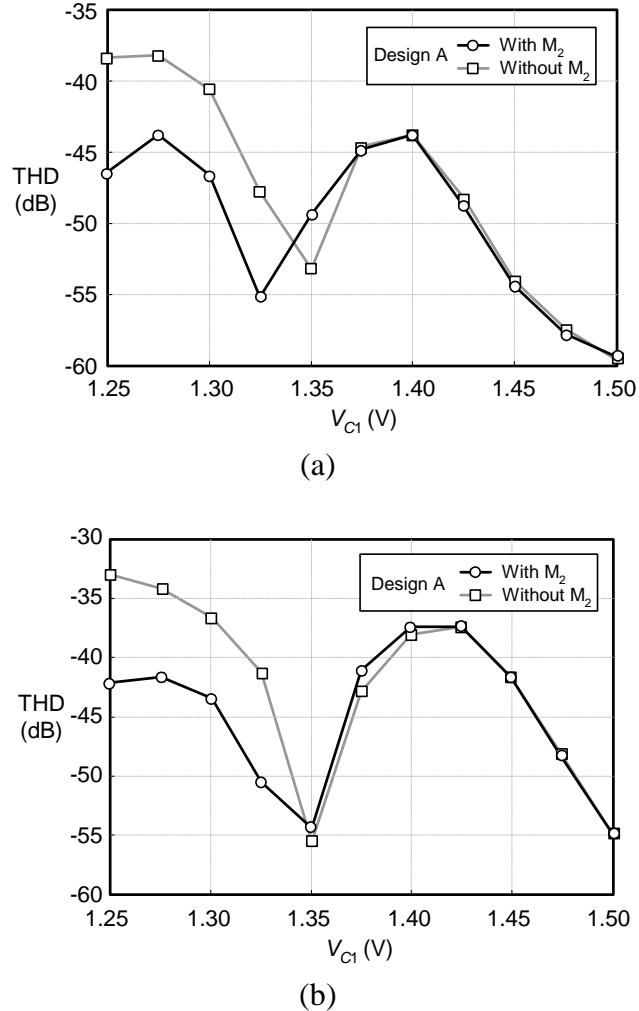

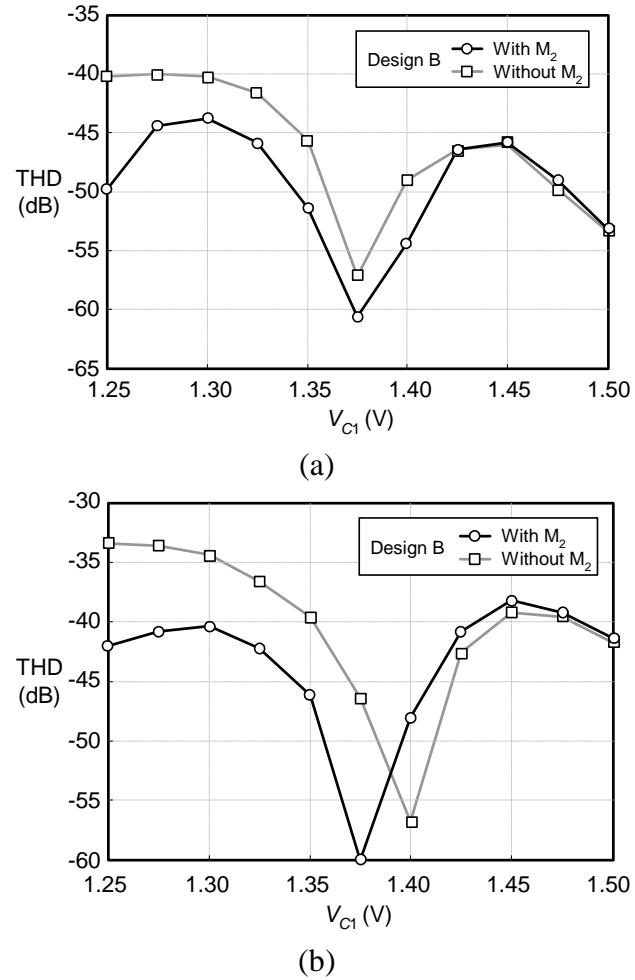

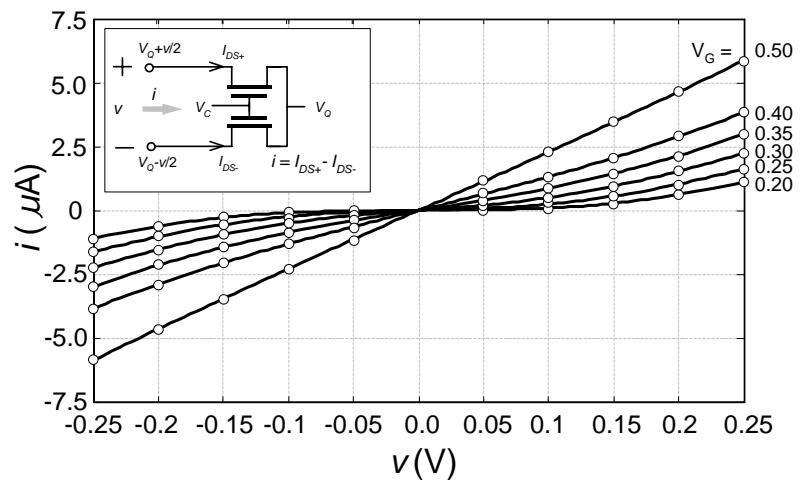

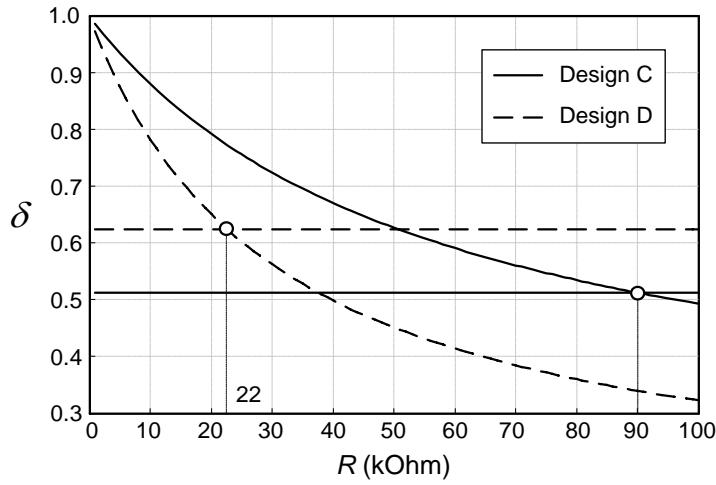

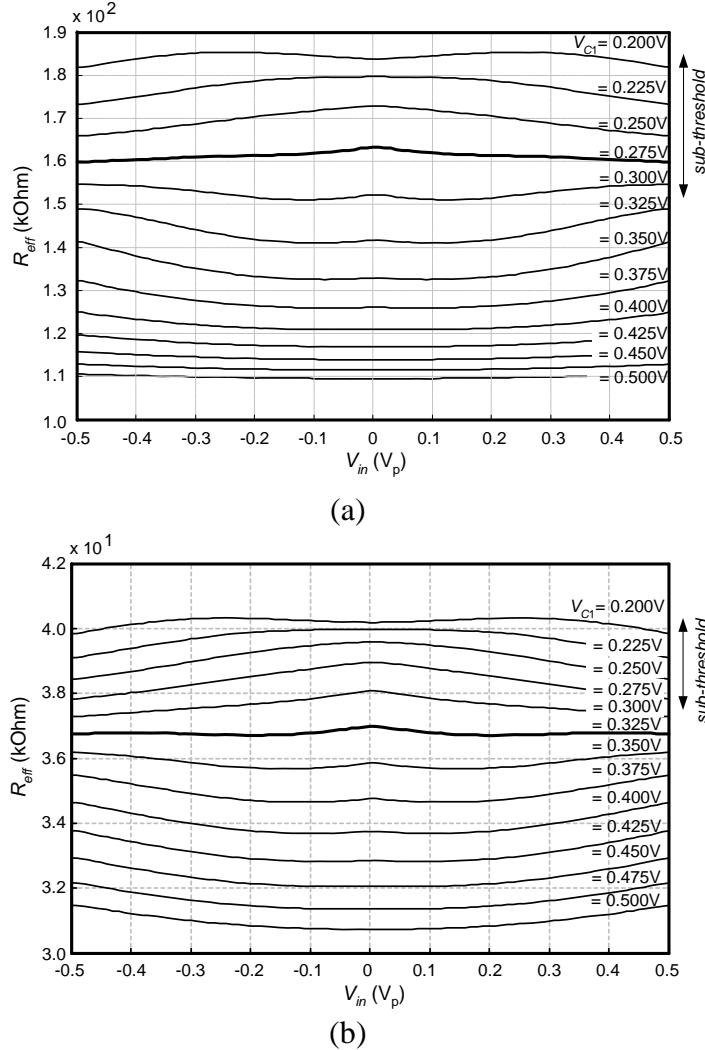

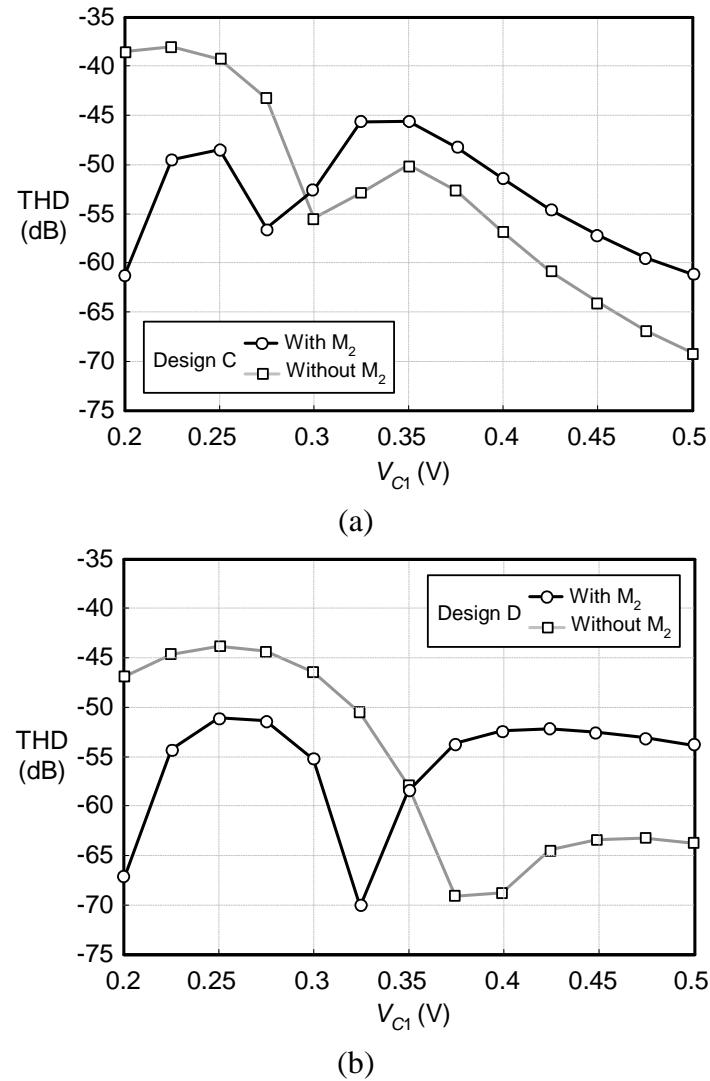

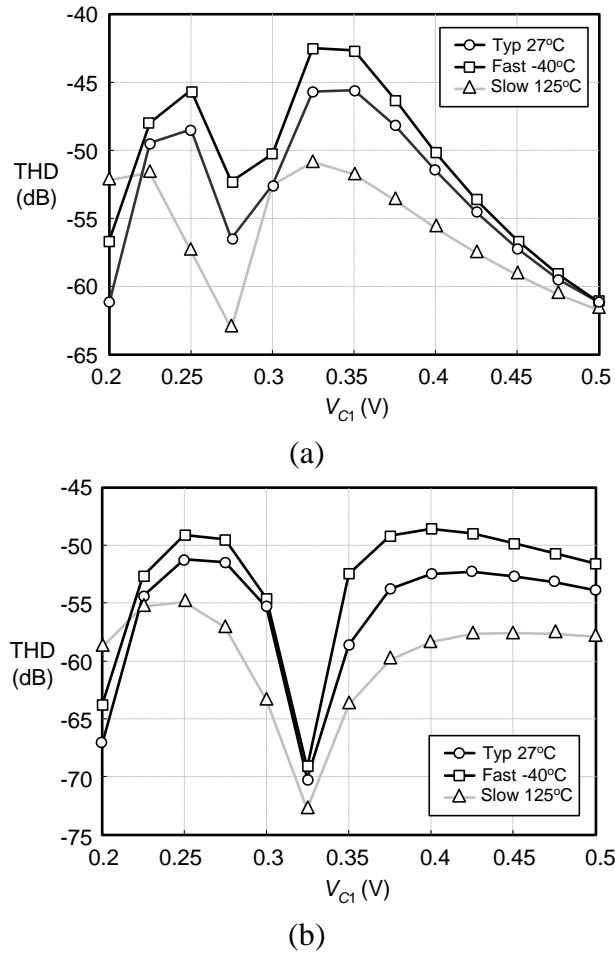

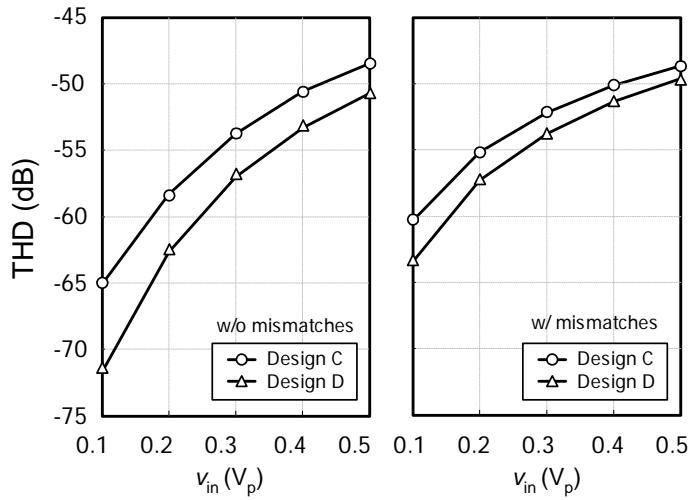

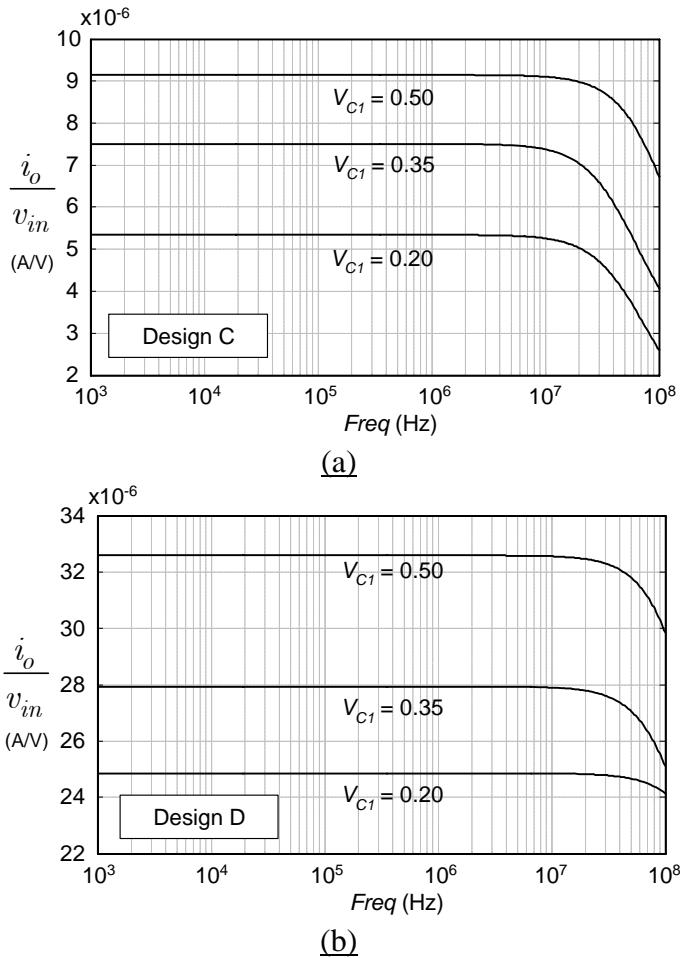

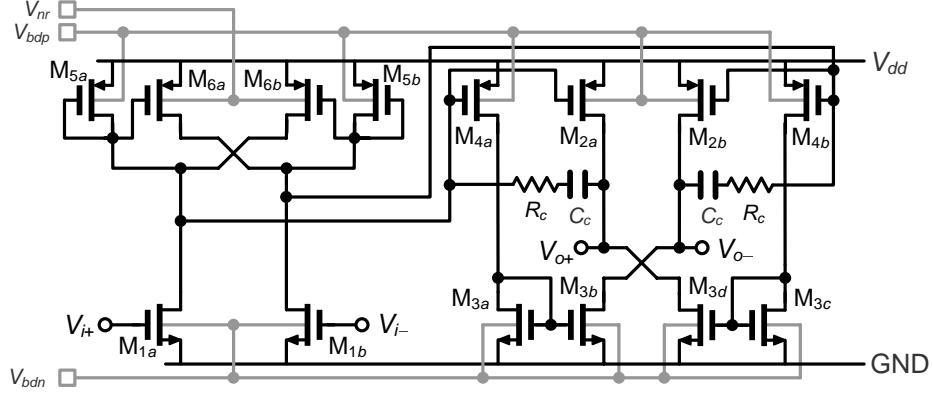

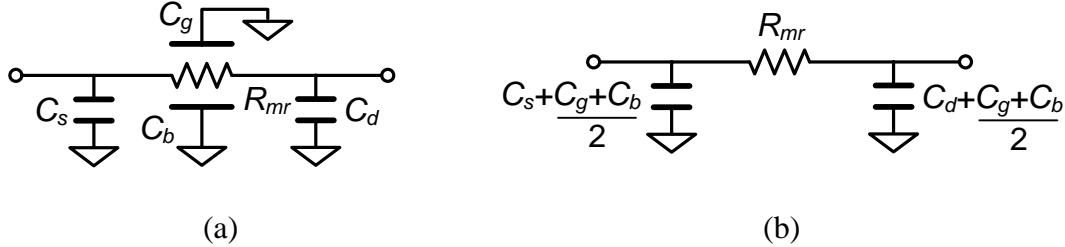

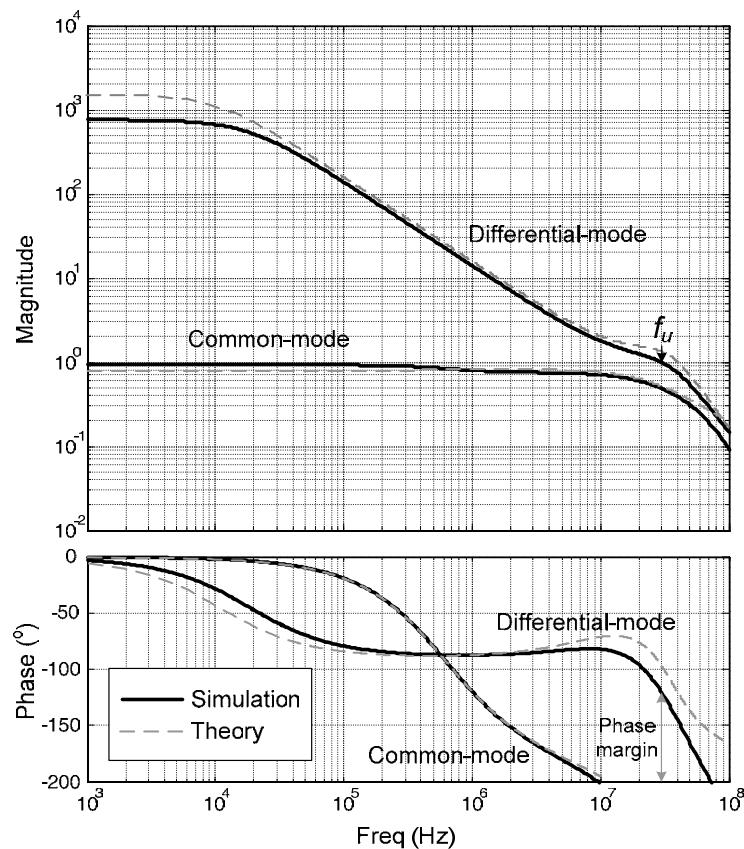

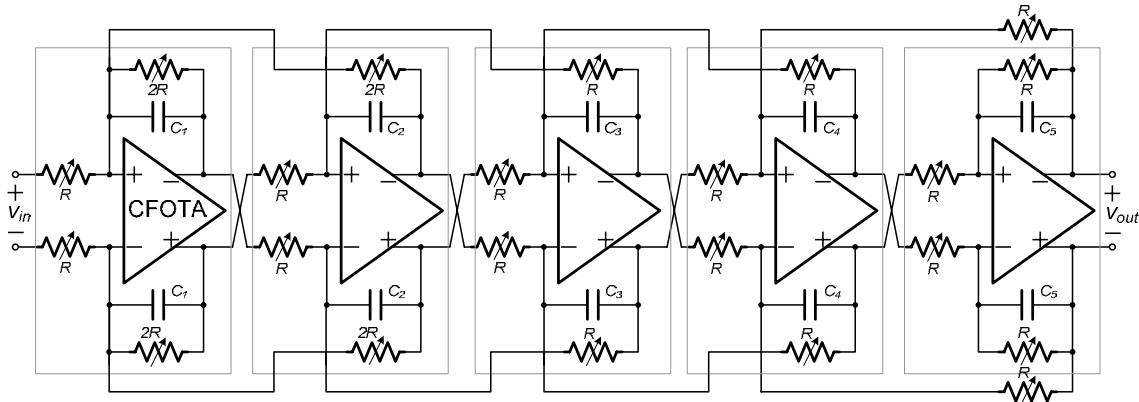

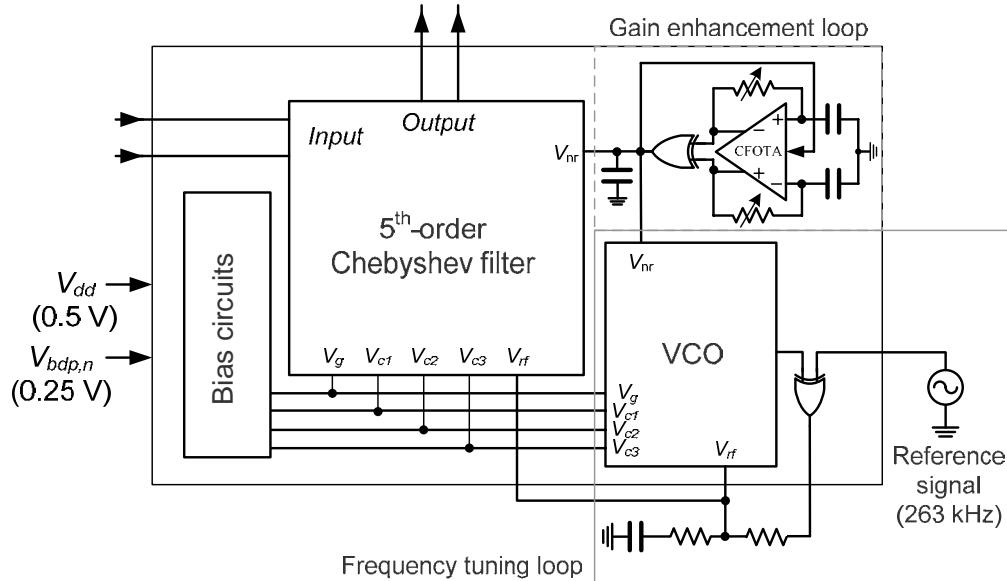

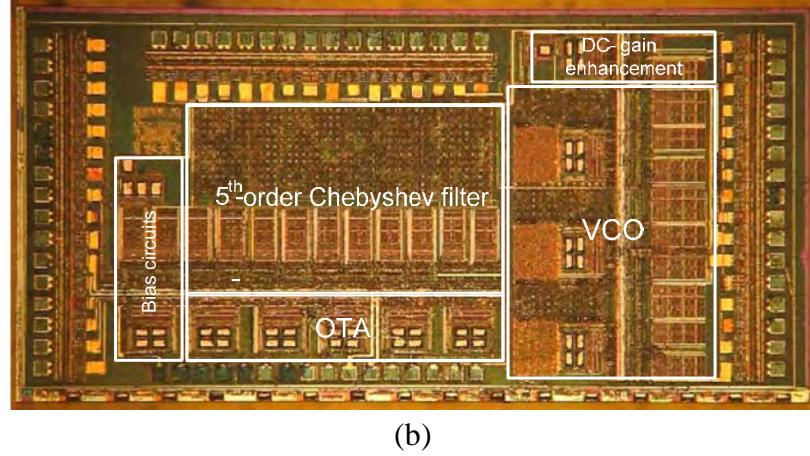

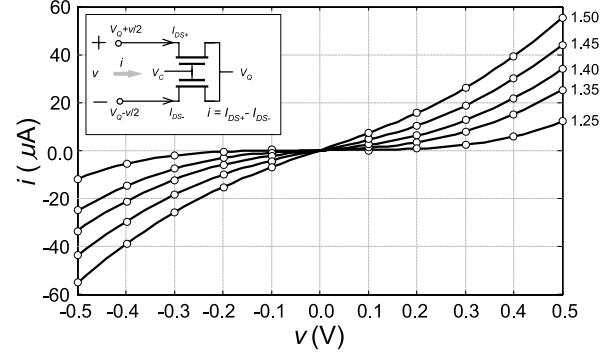

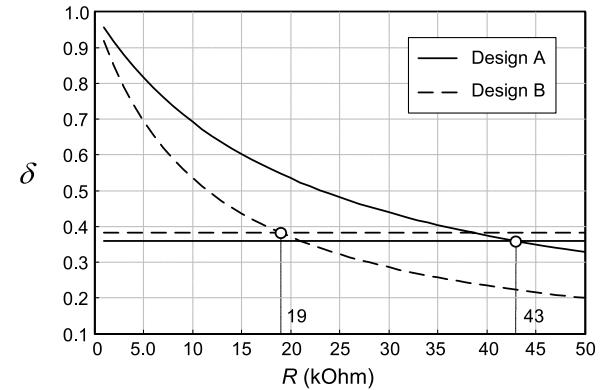

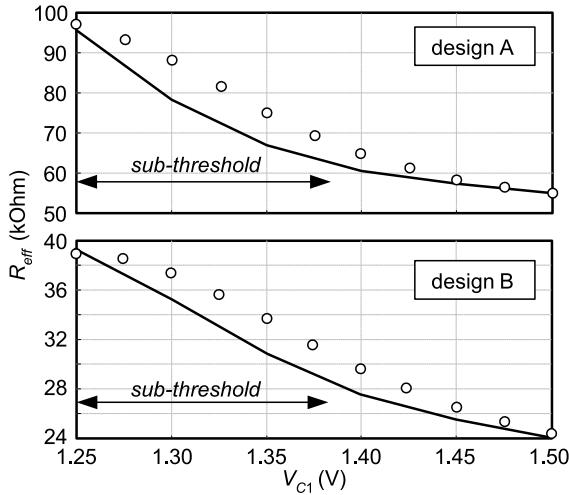

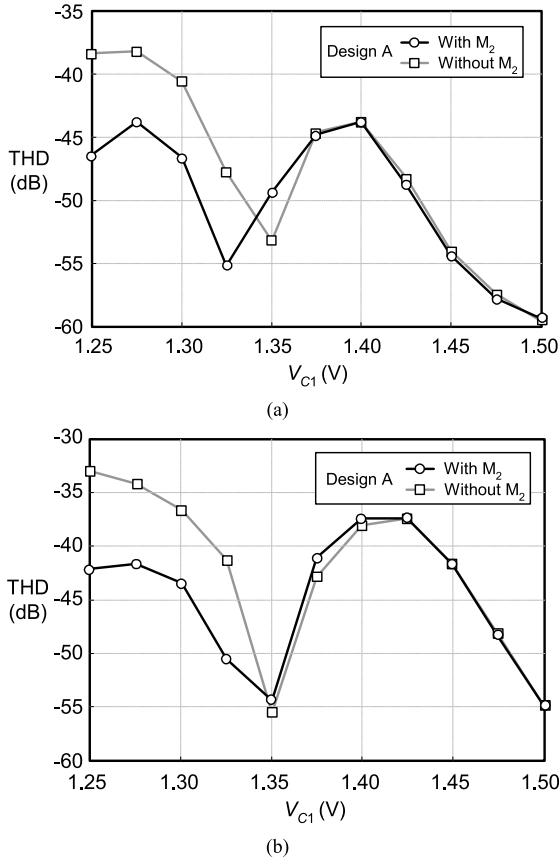

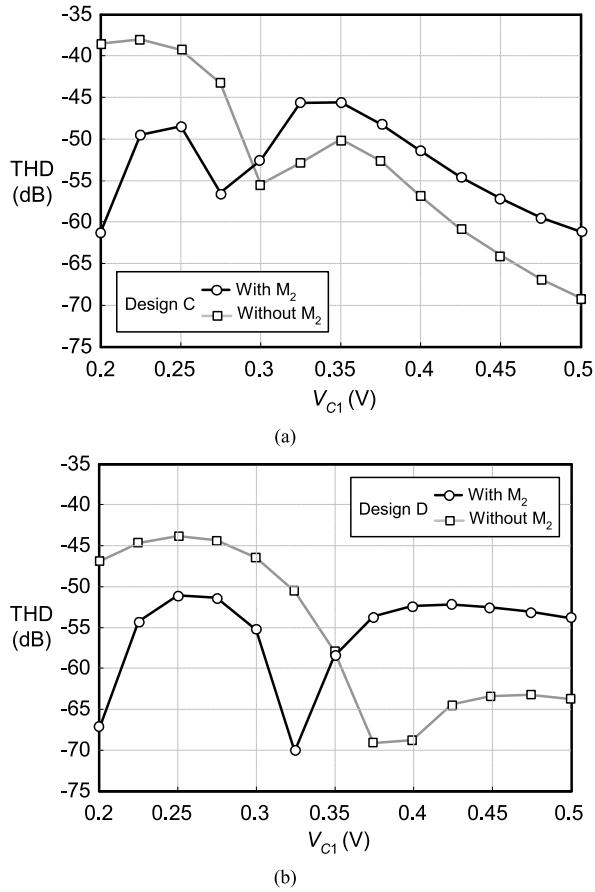

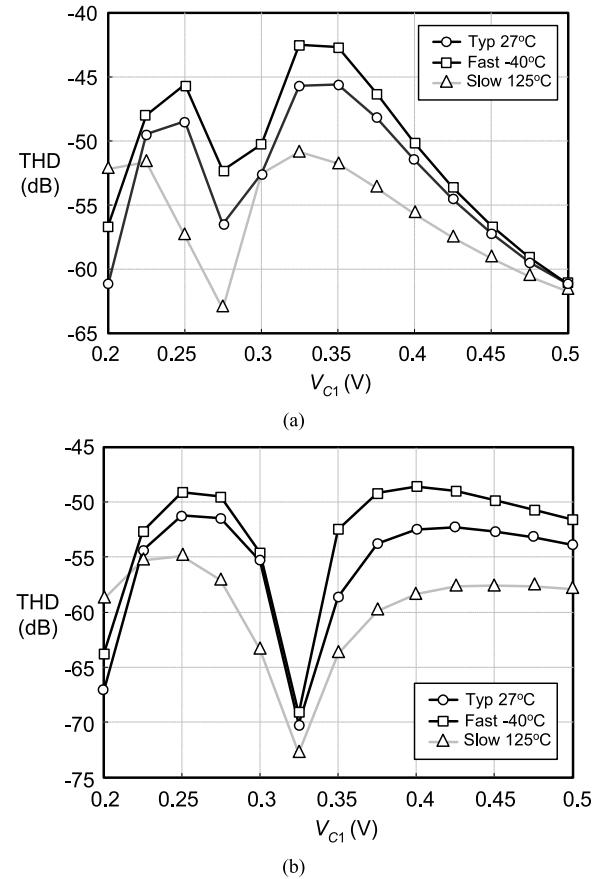

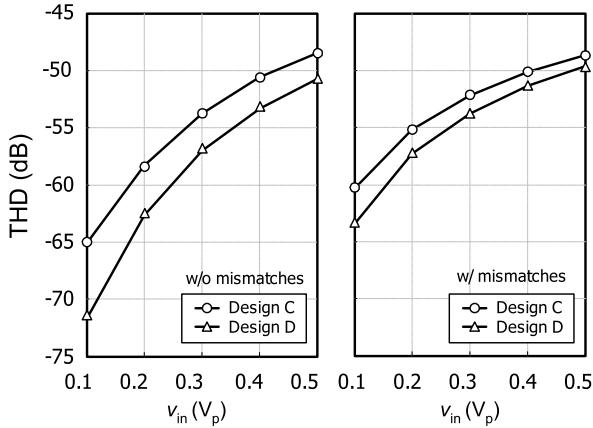

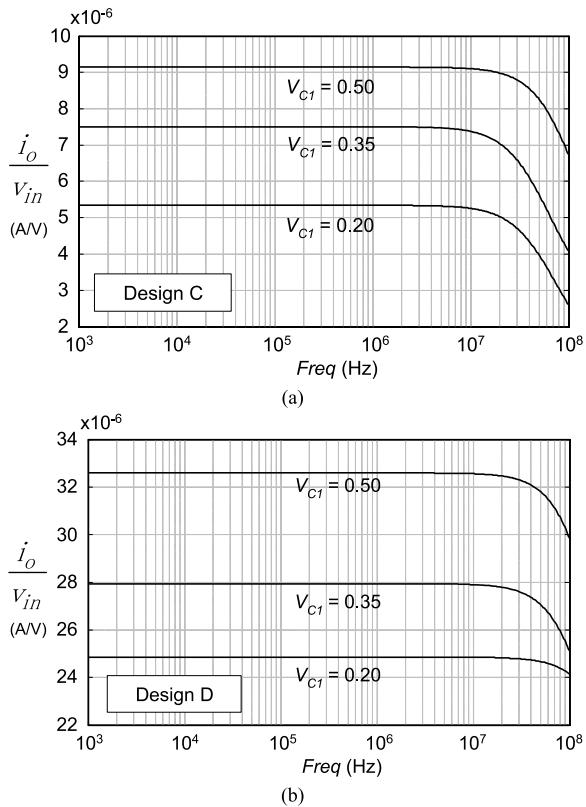

**Fig. 4.1** Sub-threshold R-MOSFET tunable resistor structure