### รายงานวิจัยฉบับสมบูรณ์

#### โครงการ

วงจรรวมแอนะล็อกและผสมสัญญาณแบบซีมอสที่ใช้กำลังไฟต่ำมาก สำหรับการประยุกต์ใช้งาน ด้านชีวการแพทย์และการดูแลสุขภาพรอบตัว

Ultra Low-Power CMOS Analog and Mixed-Signal Integrated Circuits for Biomedical Applications and Pervasive Healthcare

โดย

รศ. ดร. อภินันท์ ธนชยานนท์

สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

กันยายน 2554

### รายงานวิจัยฉบับสมบูรณ์

#### โครงการ

วงจรรวมแอนะล็อกและผสมสัญญาณแบบซีมอสที่ใช้กำลังไฟต่ำมาก สำหรับการประยุกต์ใช้งาน ด้านชีวการแพทย์และการดูแลสุขภาพรอบตัว

Ultra Low-Power CMOS Analog and Mixed-Signal Integrated Circuits for Biomedical Applications and Pervasive Healthcare

> รศ. ดร. อภินันท์ ธนชยานนท์ สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

สนับสนุนโดยสำนักงานกองทุนสนับสนุนการวิจัย

(ความเห็นในรายงานนี้เป็นของผู้วิจัย สกว.ไม่จำเป็นต้องเห็นด้วยเสมอไป)

#### บทคัดย่อ

รหัสโครงการ: RSA5180015

ชื่อโครงการ: วงจรรวมแอนะล็อกและผสมสัญญาณแบบซีมอสที่ใช้กำลังไฟต่ำมากสำหรับการประยุกต์ใช้

งาน ด้านชีวการแพทย์และการดูแลสุขภาพรอบตัว

ชื่อนักวิจัย : รศ. ดร. อภินันท์ ธนชยานนท์

สถาบัน: สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

E-mail Address: ktapinun@kmitl.ac.th

ระยะเวลาโครงการ : 15 กันยายน 2551 – 14 กันยายน 2554

รายงานนี้นำเสนอผลงานวิจัยด้านการออกแบบวงจรรวมแอนะล็อกและผสมสัญญาณแบบซีมอสที่ใช้ กำลังไฟต่ำมากสำหรับการประยุกต์ใช้งานด้านชีวการแพทย์และการดูแลสุขภาพรอบตัว โดยอธิบายถึง วงจรที่ได้ออกแบบและพัฒนาขึ้นใหม่ในเทคโนโลยีซีมอสสมัยใหม่ที่มีขนาดเล็กกว่า 1 ไมโครเมตร ซึ่งใช้ กำลังไฟต่ำและแรงดันไฟเลี้ยงต่ำโดยอาศัยวิธีการและเทคนิควงจรต่างๆ เช่น มอสเฟตในย่านต่ำกว่าขีดเริ่ม เทคนิคทรานส์ลิเนียร์โหมดกระแส เทคนิคการขับอินพุตที่ขาบอดี้ ประกอบด้วยวงจรดังต่อไปนี้

วงจรอ่านค่าสัญญาณจากอีสเฟตที่ไวต่อค่า pH ใช้โครงสร้างวงจรขยายสัญญาณผลต่างที่ใช้อีสเฟตและ รีเฟตในย่านผันกลับอย่างอ่อน และหลักการทรานส์ลิเนียร์โหมดกระแสเพื่อให้ได้ความเป็นเชิงเส้นที่ดีและ สามารถกำจัดสัญญาณรบกวนโหมดร่วมได้ดี มีขนาดเล็กและใช้กำลังไฟฟ้าต่ำมาก (4 nW)

วงจรแปลงสัญญาณแอนะล็อกเป็นดิจิตอลแบบล็อกการิทึมโหมดกระแสที่ใช้โครงสร้างแบบไพพ์ไลน์ และแบบอัลกอริทึม มีความละเอียด 8 บิต ใช้เทคนิคการทำงานในย่านผันกลับอย่างอ่อนของมอสเฟต และ หลักการทรานส์ลิเนียร์ วงจรสามารถทำงานภายใต้แรงดันไฟเลี้ยง 1-1.8 V และใช้กำลังงาน 0.2-4  $\mu$ W

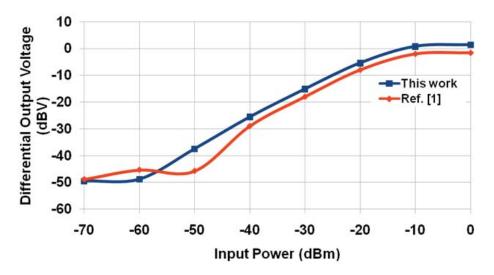

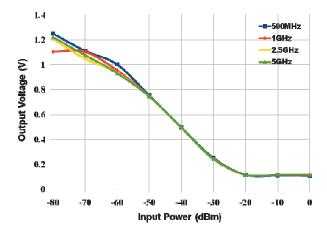

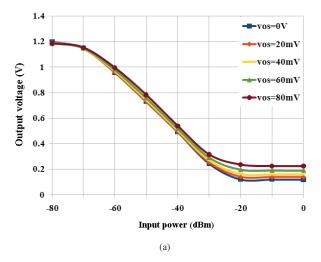

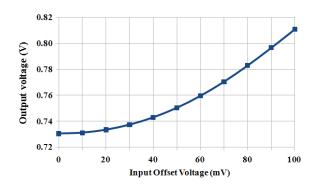

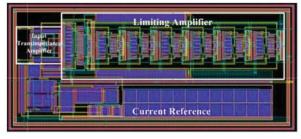

วงจรตรวจวัดกำลังงานสัญญาณคลื่นความถี่วิทยุใช้คุณลักษณะความไม่เป็นเชิงเส้นของมอสเฟตในย่าน อื่มตัวและโหลดแอกทีฟเพื่อเพิ่มอัตราขยายแปลงทำให้ไม่ต้องการแบนด์วิดท์สูงและไม่ต้องใช้วงจรเรียง กระแสและวงจรกรอง วงจรสามารถตรวจวัดกำลังงานอินพุตได้ตั้งแต่ -70 dBm ถึง -20 dBm ในย่าน ความถี่ 500 MHz ถึง 5 GHz และใช้กำลังงาน 0.9 mW

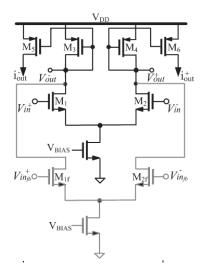

วงจรขยายทรานส์คอนดักแตนซ์เชิงเส้นที่ใช้เทคนิคการขับสัญญาณอินพุตที่ขาบอดี้ของมอสเฟต ร่วม กับการใช้ตัวต้านทานถดถอยที่ขาซอร์สร่วมและโครงสร้างวงจรตามสัญญาณแบบกลับแรงดัน วงจรใช้กำลัง งาน 0.8 µW จากแรงดันไฟเลี้ยง 0.8 V และมีความเป็นเชิงเส้นที่ดี

วงจรที่นำเสนอใหม่ทั้งหมดสามารถทำงานได้ที่แรงดันไฟเลี้ยงต่ำและใช้กำลังงานต่ำ ทำให้มีศักยภาพ เหมาะสมสำหรับการประยุกต์ใช้งานในส่วนประมวลสัญญาณของระบบวงจรรวมสำหรับทางชีวการแพทย์ หรือระบบโครงข่ายเซนเซอร์ไร้สายรอบร่างกาย

#### **Abstract**

Project Code: RSA5180015

Project Title: Ultra Low-Power CMOS Analog and Mixed-Signal Integrated Circuits for

Biomedical Applications and Pervasive Healthcare

Investigator: Associate Professor Dr. Apinunt Thanachayanont Institution: King Mongkut's Institute of Technology Ladkrabang

E-mail Address: ktapinun@kmitl.ac.th

Project Period: 15 September 2008 - 14 September 2011

This report is concerned with the design and implementation ultra low power CMOS analog and mixed-signal integrated circuits for biomedical application and pervasive health-care. Novel low-voltage low-power circuits have been proposed and realized in modern sub-micron CMOS technologies, using innovative circuit techniques including subthreshold MOSFETs, current-mode translinear circuits, and body-driven technique. The newly proposed circuits include the followings.

Ultra low-power read-out circuit for pH Ion-sensitive FET (ISFET) which exploits the ISFET-REFET differential amplifier and the Translinear principle to achieve good linearity and common-mode rejection ability. The circuit is compact and consumes nanoWatts of power.

Current-mode logarithmic analog-to-digital converters using the pipeline and algorithmic structures have been realized with 6-8 bits of resolution. The circuits exploits subthreshold MOSFETs and the Translinear principle and operates with 0.2-4  $\mu W$  under 1-1.8 V power supply voltage.

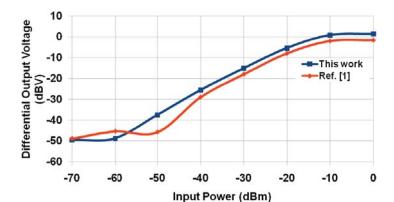

Low-power RF power detector exploits the non-linearity of MOSFET and active load to increase the conversion gain, which allows low operating bandwidth and alleviates the need for rectifier and filter circuits. The circuit can detect input power in the range of -70 to -20 dBm and input frequencies from 0.5 to 5 GHz, with 0.9-mW power dissipation.

Linear operational transconductance amplifier which uses the body-driven technique with resistive source degeneration and flipped-voltage follower topology to achieve good linearity with 0.8- $\mu W$  power dissipation under a 0.8-V power supply voltage.

All circuits proposed in this report can operate under low power supply voltage and low power dissipation. They exhibit strong potential for applications in the areas of biomedical electronic signal processing systems and wireless body area and sensor network.

## สารบัญ

| 1 | บทน้ำ  | (Introdu    | ction)                                                            | 1  |

|---|--------|-------------|-------------------------------------------------------------------|----|

| 2 | วงจร   | อ่านค่าสัญเ | ญาณโหมดกระแสจากตัวเซ็นเซอร์อีสเฟตที่ใช้กำลังไฟต่ำยิ่ง (Ultra low- |    |

|   | powe   | er current  | -mode readout circuit)                                            | 5  |

|   | 2.1    | บทนำ .      |                                                                   | 5  |

|   | 2.2    | หลักการ     | ทำงานของอีสเฟต                                                    | 6  |

|   | 2.3    | อีสเฟตใง    | นย่านการทำงานผันกลับอย่างอ่อน                                     | 7  |

|   | 2.4    | วงจรอ่าเ    | มค่าสัญญาณจากอีสเฟตที่นำเสนอ                                      | 11 |

|   | 2.5    |             |                                                                   | 15 |

| 3 | วงจร   | แปลงสัญญ    | าณแอนะล็อกเป็นดิจิตอลโหมดกระแสแบบล็อกการิทึมที่ใช้กำลังไฟต่ำ      |    |

|   | (Ultra | a low-pov   | ver current-mode logarithmic analog-to-digital converter)         | 16 |

|   | 3.1    | บทนำ .      |                                                                   | 16 |

|   | 3.2    | การแปล      | งสัญญาณแอนะล็อกเป็นดิจิตอลแบบล็อกการิทึม                          | 17 |

|   | 3.3    | วงจร Lo     | gADC โหมดกระแสแบบไพพ์ไลน์ (Current-mode Logarithmic Pipeline      |    |

|   |        | ADC) .      |                                                                   | 17 |

|   |        | 3.3.1       | โครงสร้างวงจร                                                     | 17 |

|   |        | 3.3.2       | การออกแบบวงจร LogADC โหมดกระแสแบบไพพ์ไลน์                         | 20 |

|   |        | 3.3.3       | ผลจำลองการทำงาน                                                   | 23 |

|   |        | 3.3.4       | การจำลองการทำงานของวงจร LogADC ที่เชื่อมต่อกับวงจรอ่านค่า         |    |

|   |        |             | สัญญาณจากอีสเฟต                                                   | 25 |

|   | 3.4    | วงจร Lo     | gADC โหมดกระแสแบบอัลกอริทีม (Current-mode Algorithmic Log-        |    |

|   |        | arithmic    | a ADC)                                                            | 30 |

|   |        | 3.4.1       | โครงสร้างวงจร                                                     | 30 |

สารบัญ

|     |         | 3.4.2                      | การออกแบ      | บวงจร LogADC โหมดกระแสแบบอัลกอริทึม                  | 32 |

|-----|---------|----------------------------|---------------|------------------------------------------------------|----|

|     |         |                            | 3.4.2.1       | วงจรสุ่มและคงค่าสัญญาณ (Sample-and-hold)             | 33 |

|     |         |                            | 3.4.2.2       | วงจรเปรียบเทียบสัญญาณโหมดกระแส                       | 35 |

|     |         |                            | 3.4.2.3       | วงจรคูณสัญญาณและวงจรสะท้อนกระแส                      | 37 |

|     |         |                            | 3.4.2.4       | วงจรยกกำลังสองสัญญาณกระแส                            | 37 |

|     |         | 3.4.3                      | ผลจำลองกา     | ารทำงาน                                              | 37 |

|     | 3.5     | สรุป                       |               |                                                      | 38 |

| 4   | วงจรต   | <b>ตรวจวัดกำ</b> ล         | ลังงานสัญญาถ  | เคลี่นความถี่วิทยุ (RF power detector)               | 42 |

|     | 4.1     | บทนำ .                     |               |                                                      | 42 |

|     | 4.2     | โครงสร้า                   | งวงจรตรวจวัดก | ำำลังงานสัญญาณคลื่นความถี่วิทยุ                      | 44 |

|     | 4.3     | การออกเ                    | แบบวงจร       |                                                      | 45 |

|     |         | 4.3.1                      | วงจรตรวจว     | ัดกำลังงาน rms                                       | 45 |

|     |         | 4.3.2                      | วงจรขยายส่    | รัญญาณแบบล็อกการิทีม (Logarithmic amplifier)         | 46 |

|     | 4.4     | สรุป                       |               |                                                      | 48 |

| 5   | วงจรา   | ขยายทรานเ                  | ส์คอนดักแตนซ์ | ์ที่ใช้กำลังไฟต่ำ (Low power Bulk-driven Operational |    |

|     | Trans   | sconducta                  | ance Amplifi  | er)                                                  | 54 |

|     | 5.1     | บทนำ .                     |               |                                                      | 54 |

|     | 5.2     | การออกเ                    | แบบวงจร OTA   |                                                      | 55 |

|     | 5.3     | ผลจำลอ                     | งการทำงานวงจ  | 75                                                   | 56 |

|     | 5.4     | สรุป                       |               |                                                      | 60 |

| 6   | สรุปผ   | ลดำเนินงา                  | น             |                                                      | 63 |

| บรร | ัณานุกร | ฆ                          |               |                                                      | 65 |

| ภาค | เผนวก   |                            |               |                                                      | 70 |

|     | ผลงาน   | มที่ตีพิมพ์ใน <sup>:</sup> | วารสารวิชาการ | รระดับนานาชาติ                                       | 70 |

|     | ผลงาน   | มที่ตีพิมพ์ใน              | การประชมวิชา  | การระดับนานาชาติ                                     | 70 |

# สารขัญรูป

| 1.1  | โครงสร้างทั่วไปของอุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการ<br>แพทย์ [1]     | 2  |

|------|-------------------------------------------------------------------------------------------|----|

|      | PPMNO [1]                                                                                 | 2  |

| 2.1  | โครงสร้างกายภาพของอีสเฟตกับมอสเฟต                                                         | 7  |

| 2.2  | แบบจำลองเชิงพฤติกรรมของอีสเฟต                                                             | 7  |

| 2.3  | สัญลักษณ์ของอีสเฟต                                                                        | 9  |

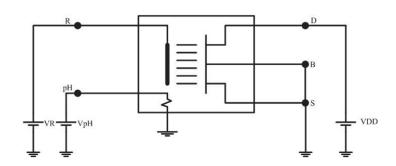

| 2.4  | วงจรทดสอบคุณลักษณะทางไฟฟ้าของอีสเฟต                                                       | 9  |

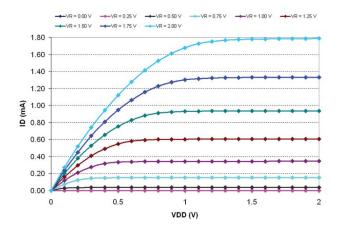

| 2.5  | คุณสมบัติกระแสเดรนและแรงดันเดรนซอสของอีสเฟตที่ค่า pH=7                                    | 9  |

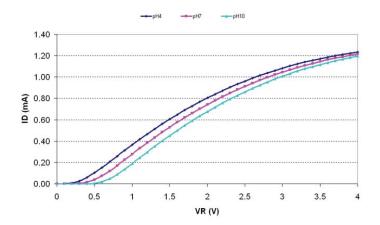

| 2.6  | คุณสมบัติกระแสเดรนและแรงดันเกตซอสของอีสเฟตที่ค่า pH=4, 7 และ 10                           | 10 |

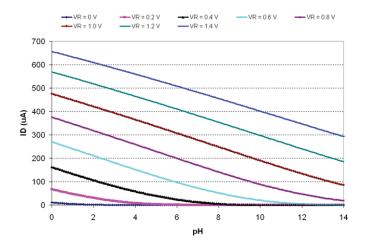

| 2.7  | คุณสมบัติกระแสเดรนและค่า pH                                                               | 10 |

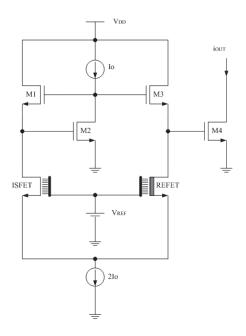

| 2.8  | วงจรอ่านค่าสัญญาณผลต่างจากอีสเฟตที่ได้นำเสนอขึ้นใหม่                                      | 11 |

| 2.9  | วงจรขยายสัญญาณผลต่าง (Differential Pair) ที่ประกอบด้วยอีสเฟตและรีเฟต                      | 12 |

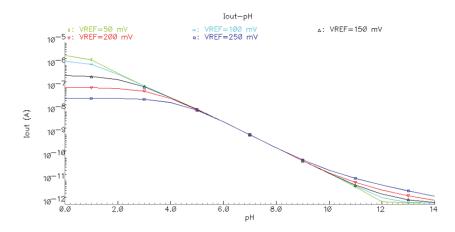

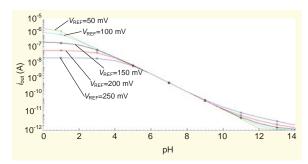

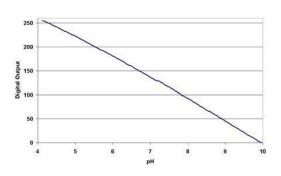

| 2.10 | คุณลักษณะกระแส $I_{out}$ กับค่า pH ที่ค่าแรงดัน $V_{REF}$ ระหว่าง 50 mV ถึง 250 mV        | 14 |

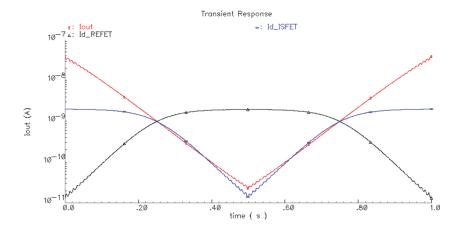

| 2.11 | ผลการจำลองทางเวลาของกระแส $I_{out}$ ต่อการเปลี่ยนแปลงของค่า pH $\  \   . \   . \   . \  $ | 14 |

| 2.12 | กระแสเอาท์พุตที่ค่า pH=7 ในกรณีที่วงจรใช้ (With) และไม่ใช้ (Without) แหล่ง                |    |

|      | จ่ายกระแสไบอัส $(2I_O)$                                                                   | 15 |

| 3.1  | คุณลักษณะอินพุตและเอาท์พุตของวงจร LogADC ขนาด 5 บิต                                       | 18 |

| 3.2  | โครงสร้างวงจร ADC ไพพ์ไลน์แบบเชิงเส้น                                                     | 19 |

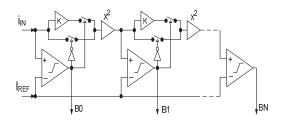

| 3.3  | โครงสร้างวงจร LogADC แบบไพพ์โลน์                                                          | 20 |

| 3.4  | วงจร LogADC ไพฟ์ไลน์โหมดกระแส                                                             | 21 |

| 3.5  | วงจรในแต่ละภาค (Bit cell) ของ LogADC                                                      | 22 |

| 3.6  | วงจรในภาคสุดท้ายของวงจร LogADC ไพฟ์โลน์โหมดกระแส                                          | 22 |

| 3.7  | วงจรสร้างกระแสอ้างอิง                                                                     | 23 |

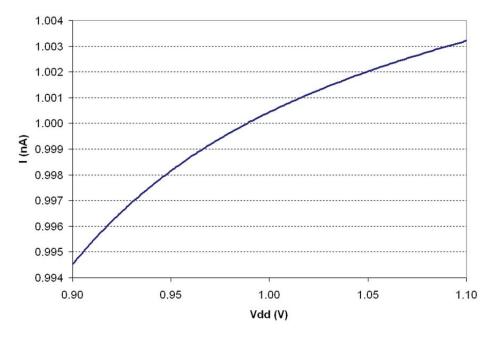

| 3.8  | ผลจำลองค่ากระแสอ้างอิงปกติกับการผันแปรของแรงดันไฟเลี้ยง                                   | 24 |

สารบัญรูป viii

| 3.9  | ผลจำลองการทำงานค่ากระแสอ้างอิงปกติกับการผันแปรอุณหภูมิ                       | 25 |

|------|------------------------------------------------------------------------------|----|

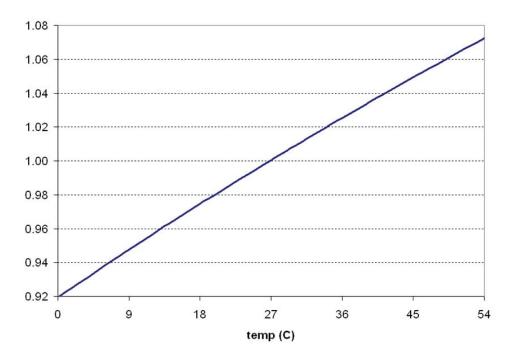

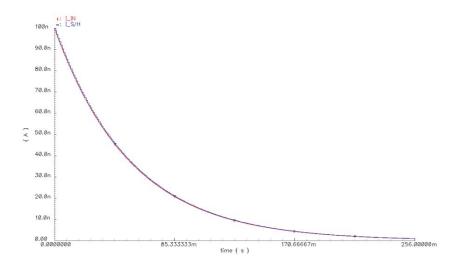

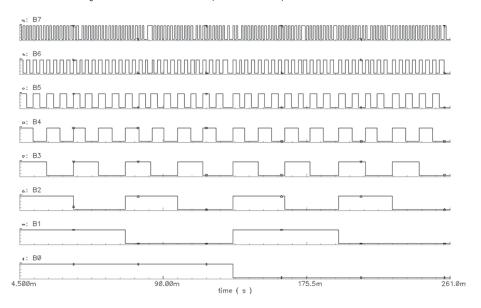

| 3.10 | กระแสอินพุตที่ผ่านการสุ่มและคงค่าสัญญาณ                                      | 26 |

| 3.11 | สัญญาณดิจิตอลเอาท์พุต 8 บิตของวงจร LogADC                                    | 26 |

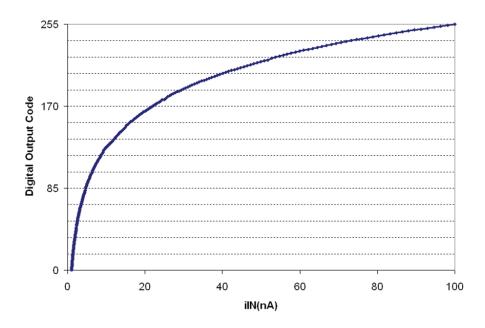

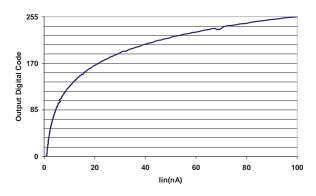

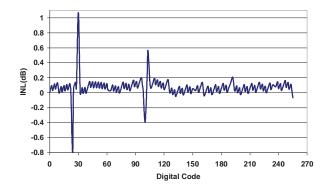

| 3.12 | ผลการจำลองคุณลักษณะสัญญาณดิจิตอลเอาท์พุตกับกระแสอินพุต                       | 27 |

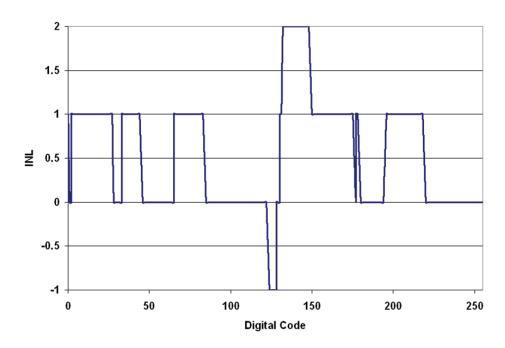

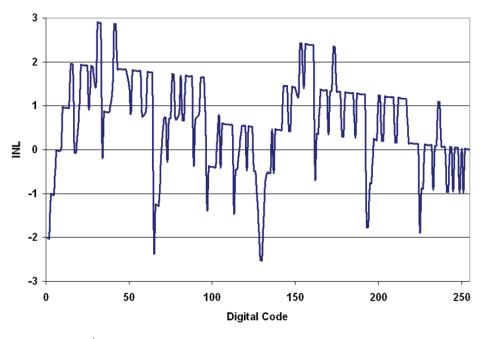

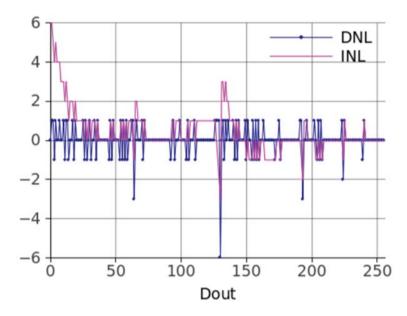

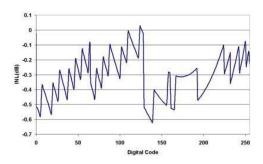

| 3.13 | ผลจำลองความไม่เป็นเชิงเส้นผลรวม (INL) ของวงจร LogADC 8 บิต                   | 27 |

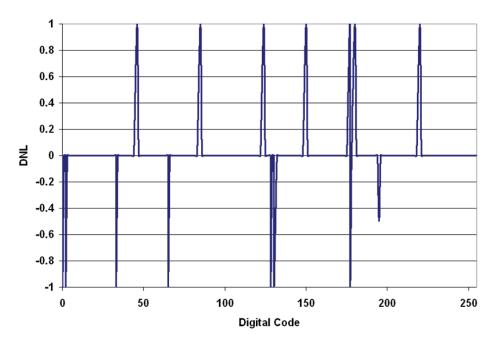

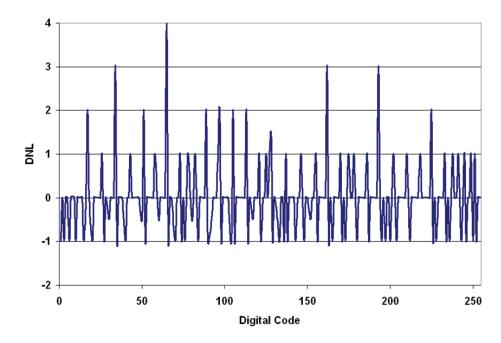

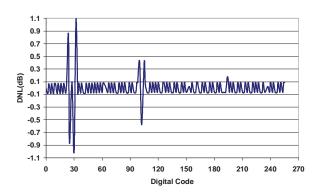

| 3.14 | ผลจำลองความไม่เป็นเชิงเส้นผลต่าง (DNL) ของวงจร LogADC 8 บิต                  | 28 |

| 3.15 | การเชื่อมต่อระหว่างวงจร LogADC กับวงจรอ่านค่าสัญญาณจากอีสเฟต                 | 28 |

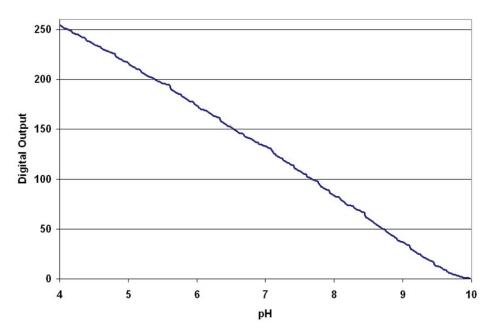

| 3.16 | ผลจำลองการทำงานสัญญาณดิจิตอลเอาท์พุตกับค่า pH                                | 29 |

| 3.17 | ผลจำลองการทำงานความไม่เป็นเชิงเส้นผลรวม (INL)                                | 29 |

| 3.18 | ผลจำลองการทำงานความไม่เป็นเชิงเส้นผลต่าง (DNL)                               | 30 |

| 3.19 | โครงสร้างวงจร ADC เชิงเส้นแบบอัลกอริทึมโหมดกระแส                             | 31 |

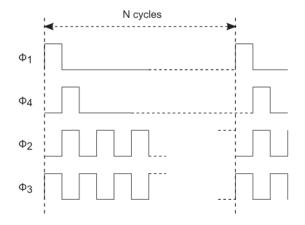

| 3.20 | สัญญาณนาฬิกาสำหรับควบคุมการทำงานของวงจร ADC เชิงเส้นแบบอัลกอริทึม .          | 31 |

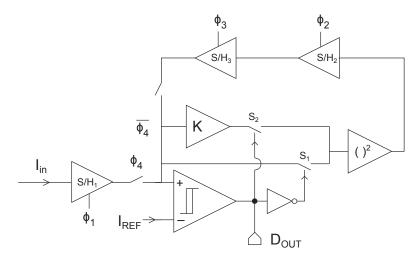

| 3.21 | โครงสร้างวงจร LogADC แบบอัลกอริทึม                                           | 32 |

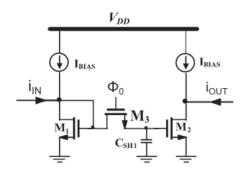

| 3.22 | วงจรสุ่มและคงค่ากระแสพื้นฐาน                                                 | 33 |

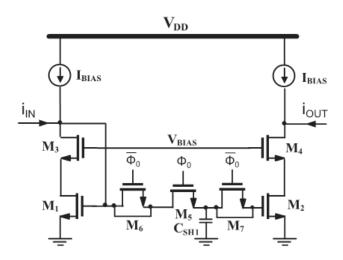

| 3.23 | วงจรสุ่มและคงค่ากระแสคาสโคดแบบแกว่งสัญญาณกว้าง                               | 34 |

| 3.24 | วงจรสุ่มและคงค่ากระแสโดยใช้วงจรหน่วยความจำสุ่มกระแส                          | 34 |

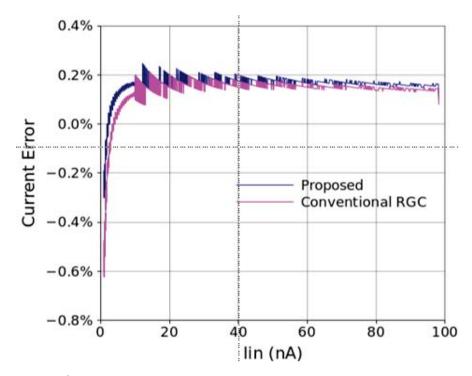

| 3.25 | วงจรสุ่มและคงค่าสัญญาณที่ใช้วงจรสวิทช์ความจำกระแสคาสโคดแบบคงค่า              | 35 |

| 3.26 | ผลจำลองค่าความผิดพลาดการสุ่มและคงค่ากระแสของวงจร                             | 36 |

| 3.27 | วงจรเปรียบเทียบกระแสแบบพื้นฐานที่ใช้วงจรซีมอสอินเวอร์เตอร์                   | 36 |

| 3.28 | วงจรเปรียบเทียบกระแสที่ใช้โครงสร้างแบบสวิทช์กระแสป้อนกลับ                    | 36 |

| 3.29 | วงจรคูณสัญญาณกระแสและวงจรสะท้อนกระแสคาสโคดแบบแกว่งสัญญาณกว้าง                | 37 |

| 3.30 | วงจรยกกำลังสองสัญญาณกระแส                                                    | 38 |

| 3.31 | ผลจำลองความไม่เป็นเชิงเส้น INL และ DNL ของวงจร LogADC แบบอัลกอริทึม          |    |

|      | ในการทำงานแบบ 6 บิต                                                          | 39 |

| 3.32 | ผลจำลองความไม่เป็นเชิงเส้น INL และ DNL ของวงจร LogADC แบบอัลกอริทึม          |    |

|      | ในการทำงานแบบ 8 บิต                                                          | 39 |

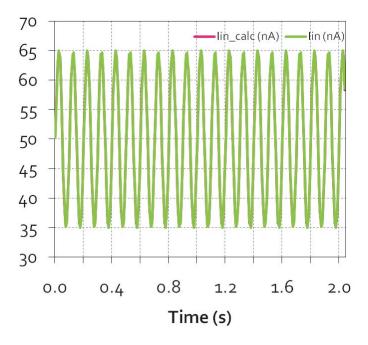

| 3.33 | กระแสที่ได้จากการแปลงสัญญาณดิจิตอลเอาท์พุต ( $I_{in\_calc}$ ) ของวงจร LogADC |    |

|      | เทียบกับกระแสอินพุต $(I_{in})$                                               | 40 |

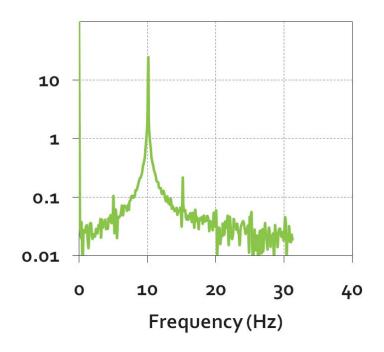

| 3.34 | สเปคตรัมของ $I_{in\_calc}$ ที่ได้จากการแปลงฟูริเยร์                          | 41 |

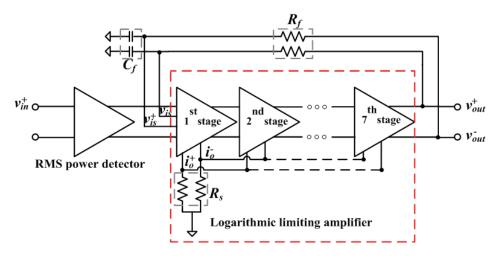

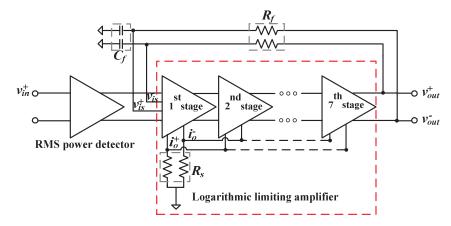

| 4.1  | โครงสร้างของวงจรตรวจวัดกำลังงานสัญญาณคลื่นความถี่วิทยุ                       | 44 |

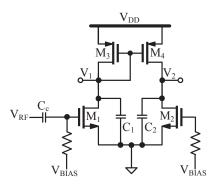

| 4.2  | วงจรตรวจวัดกำลังงาน rms                                                      | 46 |

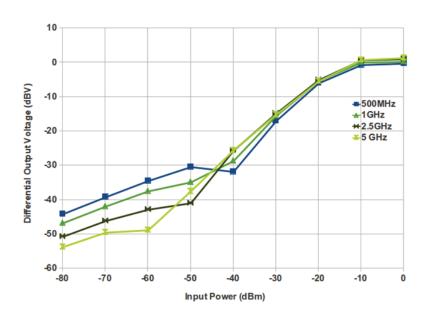

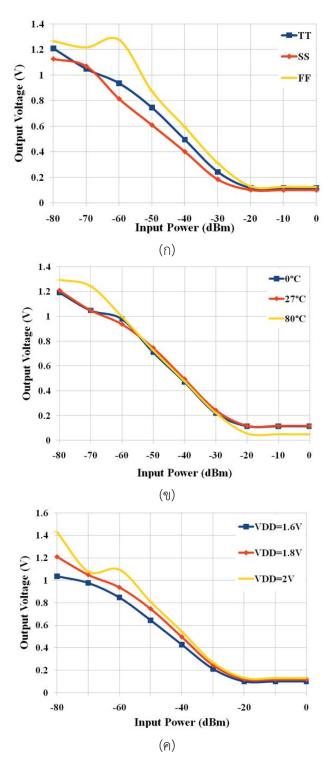

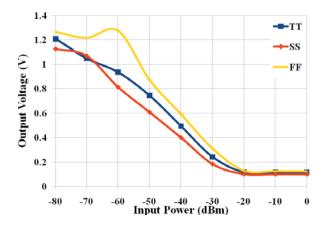

| 4.3  | คณสมบัติอินพตเอาท์พตของวงจรตรวจวัดกำลัง rms ที่ความถี่ 5 GHz                 | 46 |

สารบัญรูป

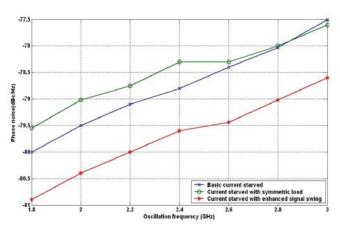

| 4.4  | วงจรขยายสัญญาณจำกัด                                                                        | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                            | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.6  |                                                                                            | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

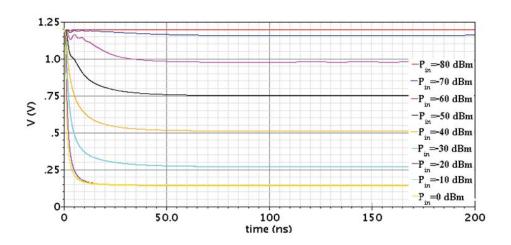

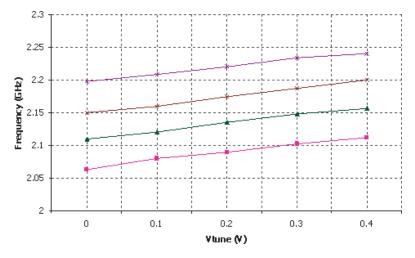

| 4.7  | 1                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

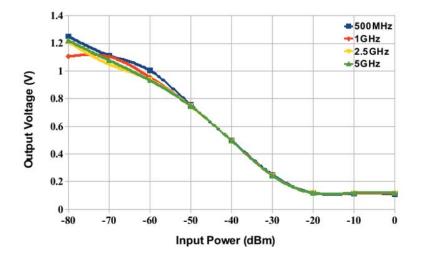

| 4.8  |                                                                                            | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

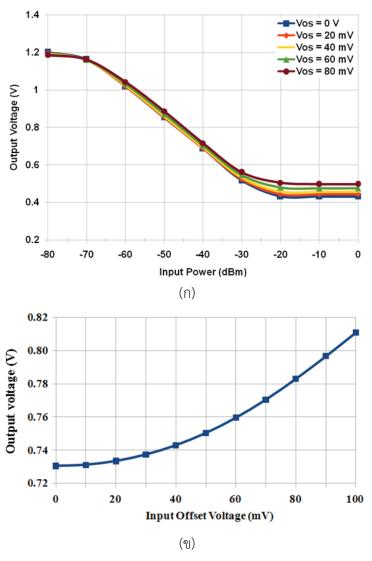

| 4.9  |                                                                                            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.10 |                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.11 | ้<br>ผลจำลองการทำงานวงจรที่ได้จากผังภูมิวงจร                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

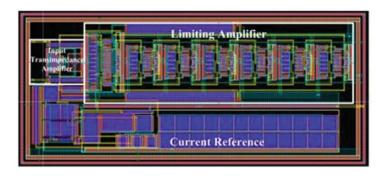

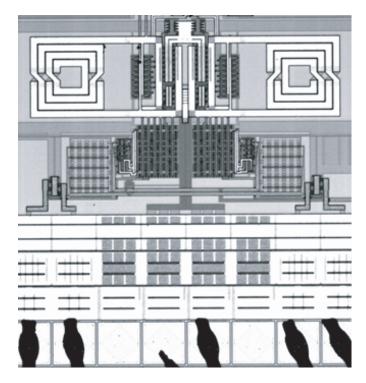

| 4.12 | ไมโครชิพต้นแบบ                                                                             | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

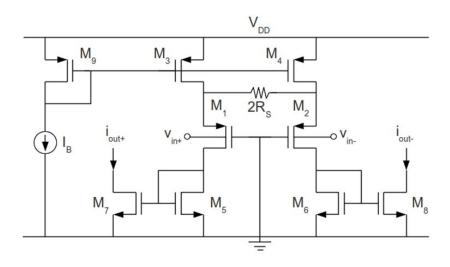

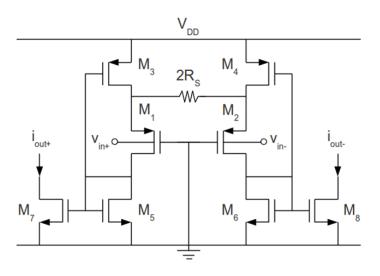

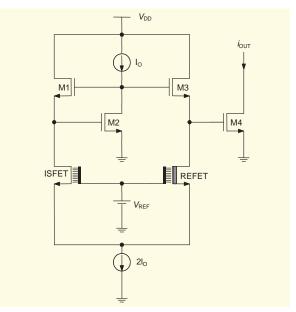

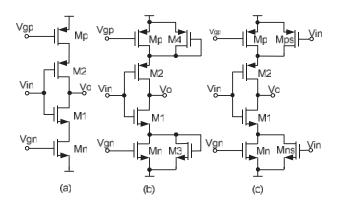

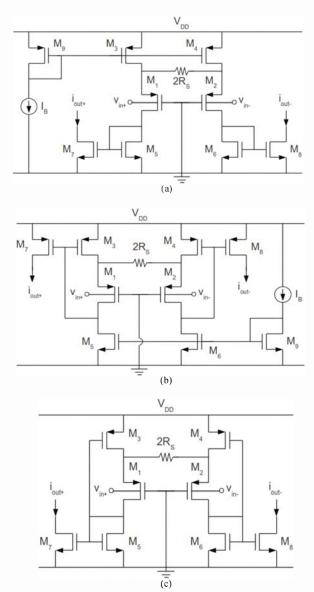

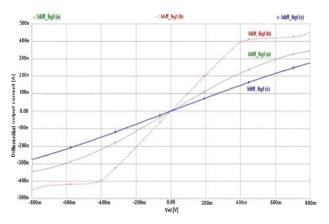

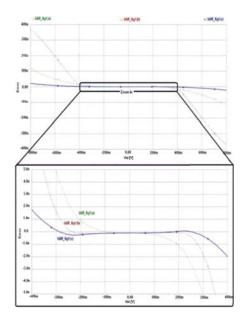

| 5 1  | วงจร OTA ที่ขับอิบพตที่ขาบอดี้และใช้เทคบิคถดถอยที่ขาซอร์ส                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                            | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

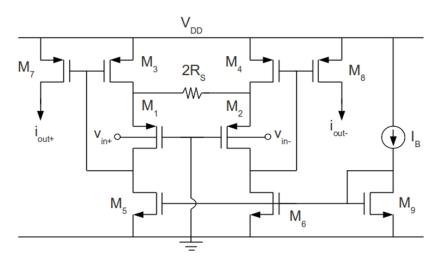

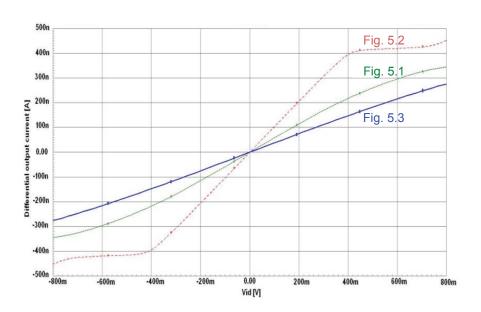

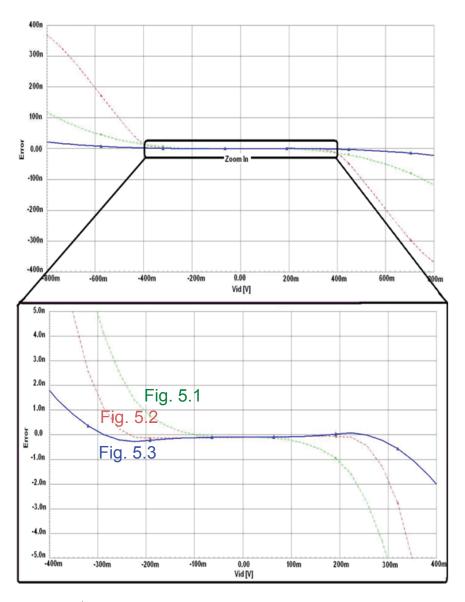

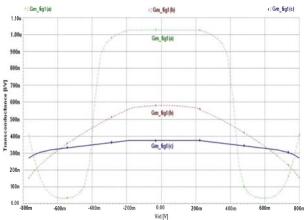

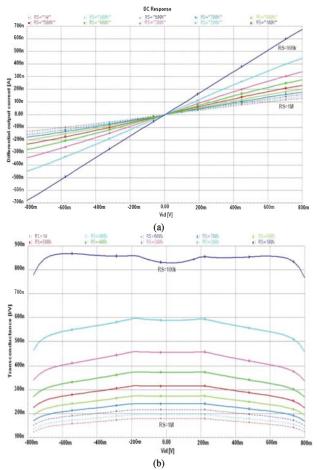

| 5.2  | 1                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5 3  |                                                                                            | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.3  |                                                                                            | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

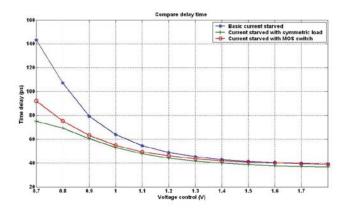

| 5.4  | 9                                                                                          | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

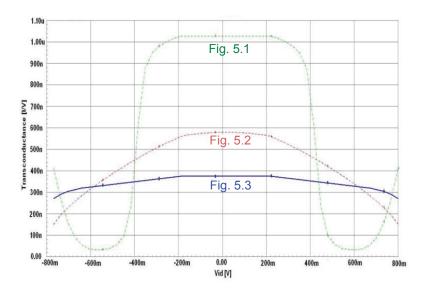

|      | 1                                                                                          | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | ,                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                                                                            | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

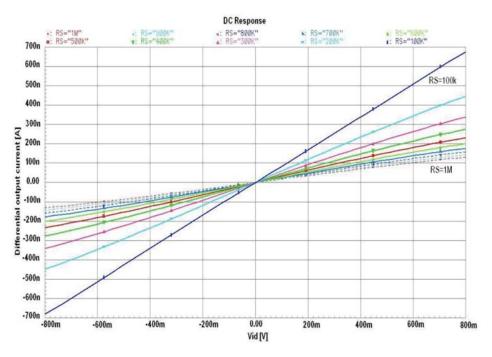

| 5.7  | กระแสเอาท์ผลต่างของวงจร OTA ในรูปที่ 5.3 เมื่อปรับค่า $R_S$ ระหว่าง 100 k $\Omega$         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | ถึง 1 M $\Omega$                                                                           | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

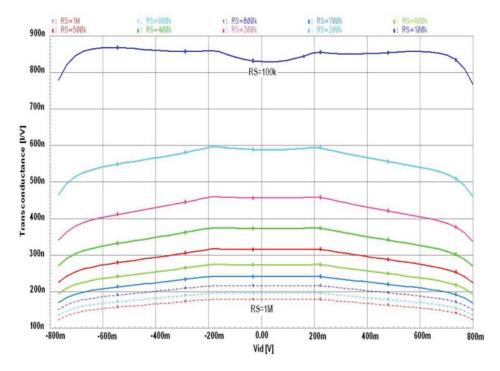

| 5.8  | ค่าทรานส์คอนดักแตนซ์ผลต่างของวงจร OTA ในรูปที่ 5.3 เมื่อปรับค่า $R_S$ ระหว่าง              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 100 kΩ                                                                                     | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

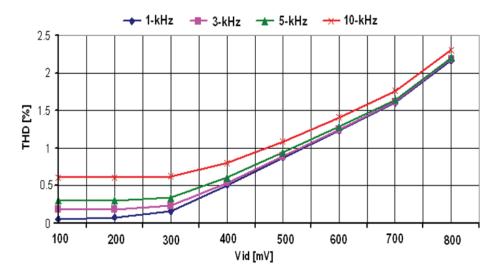

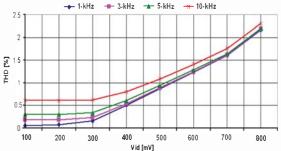

| 5.9  | ผลจำลองความผิดเพี้ยนของกระแสเอาท์พุตที่แรงดันและความถี่อินพุตต่างๆ                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | 4.5วงจรสร้างกระแสอ้างอิง4.6แรงดันเอาท์พุตผลต่างของวงจรตรวจวัดกำลัง rms ที่ความถี่อินพุตต่างๆ4.7แรงดันเอาท์พุตของวงจรตรวจวัดกำลังงานเมื่อป้อนสัญญาณอินพุต 2.5 GHz4.8คุณลักษณะแรงดันเอาท์พุดกับกำลังงานอินพุต4.9ผลของแรงดันออฟเซตอินพุต4.10ผังภูมิของวงจรตรวจวัดกำลังงานสัญญาณคลื่นความถี่วิทยุ4.11ผลจำลองการทำงานวงจรที่ได้จากผังภูมิวงจร4.12ไมโครซิพต้นแบบ5.1วงจร OTA ที่ขับอินพุตที่ขาบอดี้และใช้เทคนิคถดถอยที่ขาซอร์ส5.2วงจร OTA ที่ใช้โครงสร้างวงจรตามแรงดันแบบกลับและมีการขับอินพุตที่ขาบอดี้ และใช้เทคนิคถดถอยที่ขาซอร์ส5.3วงจร OTA วงจร OTA ที่ใช้โครงสร้างวงจรตามแรงดันแบบกลับและมีการขับอินพุตที่ขาบอดี้ที่นำเสนอใหม่5.4ผลจำลองการทำงานคุณลักษณะของกระแสเอาท์พุตและแรงดันอินพุตผลต่าง5.5ผลจำลองค่าความผิดพลาดเชิงเส้นของกระแสเอาท์พุต5.6ผลจำลองค่าทรานส์คอนดักแตนซ์ผลต่างกับแรงดันอินพุตผลต่าง5.7กระแสเอาท์ผลต่างของวงจร OTA ในรูปที่ 5.3 เมื่อปรับค่า $R_S$ ระหว่าง 100 k $\Omega$ ถึง 1 M $\Omega$ 5.8ค่าทรานส์คอนดักแตนซ์ผลต่างของวงจร OTA ในรูปที่ 5.3 เมื่อปรับค่า $R_S$ ระหว่าง100 k $\Omega$ ถึง 1 M $\Omega$ |

## สารบัญตาราง

| 1.1 | สรุปคุณลักษณะอุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการแพทย์ | 3  |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | ขนาดของมอสเฟตที่ใช้ในวงจรสร้างกระแสอ้างอิง                               | 24 |

| 3.2 | ขนาดของมอสเฟตที่ใช้ในวงจร LogADC                                         | 26 |

| 4.1 | สรุปผลจำลองการทำงานวงจร                                                  | 51 |

## บทที่ 1

## บทน้ำ (Introduction)

ตลอดช่วงทศวรรษที่ผ่านมา เทคโนโลยีสารสนเทศได้การพัฒนาและก้าวหน้าไปอย่างมากนำไปสู่การค้นพบ สิ่งใหม่ๆ และการนำไปใช้ด้านวิทยาศาสตร์และการแพทย์เพื่อปรับปรุงวิธีการตรวจและรักษาโรคและการ ดูแลสุขภาพต่างๆ การรวมกันของเทคโนโลยีสารสนเทศและวิทยาศาสตร์ชีวการแพทย์นั้น ทำให้เกิดสาขา วิชาการและวิจัยใหม่ที่มีความสำคัญยิ่ง เรียกได้ว่า "วิทยาศาสตร์การแพทย์บนฐานข้อมูลสารสนเทศ" หรือ "Information-based medicine" ซึ่งหมายถึงการนำเทคโนโลยีสารสนเทศมาประยุกต์ใช้ทางการแพทย์ เพื่อสร้างการดูแลสุขภาพส่วนตัว หรือ "Personalized healthcare" [2]

ความก้าวหน้าของเทคโนโลยีวงจรรวม (Integrated circuit หรือ IC) และเทคนิคใหม่และนวัตกรรมการ ออกแบบวงจรรวมเป็นปัจจัยสำคัญที่จะทำให้การนำเทคโนโลยีสารสนเทศไปใช้ทางด้านการแพทย์บนฐาน ข้อมูลสารสนเทศและการดูแลสุขภาพส่วนตัวประสพความสำเร็จได้ วงจรรวมที่มีขนาดเล็กและใช้กำลังไฟ ต่ำยิ่งยวดนั้นทำให้เราสามารถสร้างและพัฒนาอุปกรณ์และระบบอิเล็กทรอนิกส์ต่างๆ สำหรับการประยุกต์ ใช้ทางชีวการแพทย์ ตั้งแต่อุปกรณ์ที่ต้องฝังอยู่ในร่างกาย เช่น เครื่องช่วยการเต้นของหัวใจ (Pacemaker) และหูเทียม (Electronic cochclear) จนถึงโครงข่ายเซ็นเซอร์รอบร่างกาย (Body-area sensor network) เช่น การตรวจวัดคลื่น ECG และ EEG แบบไร้สาย โครงข่ายรอบร่างกาย หรือ Body-area network (BAN) นั้นมีความสำคัญมากเมื่อมีอุปกรณ์อิเล็กทรอนิกส์ต่างๆ สำหรับการประยุกต์ใช้ทางชีวการแพทย์ มากขึ้น การใช้โครงข่ายไร้สายจะทำให้เราสามารถรับส่งข้อมูลทางการแพทย์ได้อย่างถูกต้อง รวดเร็ว ที่ ใดและเวลาใดก็ได้ (anytime anywhere) หรือที่เรียกว่า "การดูแลสุขภาพรอบตัว" หรือ "pervasive healthcare"[3]

ระบบและวงจรรวมสำหรับชีวการแพทย์เป็นศาสตร์ใหม่ที่มีความสำคัญยิ่งและมีการพัฒนาก้าวหน้า อย่างรวดเร็ว และได้รับความสนใจจากนักวิจัยจำนวนมากทั่วโลก ซึ่งมีประเด็นปัญหาต่างๆที่ท้าทายอย่าง มากที่ต้องการการวิจัยทั้งในระดับระบบและวงจร โดยเฉพาะประเด็นที่สำคัญที่สุดน่าจะเป็นด้านเทคนิค การออกแบบวงจรแอนะล็อกและดิจิตอลที่ใช้กำลังไฟต่ำยิ่งยวด เพื่อให้ระบบและวงจรสามารถทำงานได้

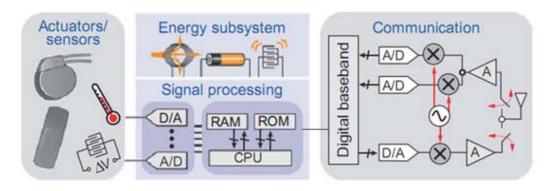

รูปที่ 1.1: โครงสร้างทั่วไปของอุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการแพทย์ [1]

ด้วยตนเองเป็นระยะเวลานาน โครงการวิจัยนี้มีวัตถุประสงค์เพื่อวิจัยและพัฒนานวัตกรรมและเทคนิคการ ออกแบบวงจรรวมแอนะล็อกและผสมสัญญาณที่ใช้กำลังไฟต่ำยิ่งยวดสำหรับการประยุกต์ใช้งานด้านชีว การแพทย์ โดยจะนำเทคนิคต่างๆ มาวิจัยและพัฒนาวงจร เช่น การใช้มอสเฟตในย่านต่ำกว่าขีดเริ่ม เทคนิค โหมดกระแส เทคนิคทรานส์ลิเนียร์โหมดกระแส เทคนิคการขับอินพุตที่ขาบอดี้ รวมทั้งการคิดค้นเทคนิค ใหม่ๆ

รูปที่ 1.1 แสดงโครงสร้างทั่วไปของอุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการแพทย์ [1] ซึ่งประกอบด้วย 4 ส่วนหลักได้แก่ ส่วนสื่อสาร ส่วนประมวลผลสัญญาณ ส่วนสร้างพลังงานและแหล่ง จ่ายไฟ และส่วนเซ็นเซอร์ โดยวงจรแอนะล็อกและผสมสัญญาณจะใช้สำหรับการเชื่อมต่อกับตัวเซ็นเซอร์ ประมวลผลสัญญาณ การสื่อสาร และการจัดการพลังงาน ซึ่งมีวงจรที่สำคัญได้แก่ วงจรแปลงสัญญาณแอ นะล็อกเป็นดิจิตอล วงจรแปลงสัญญาณดิจิตอลเป็นแอนะล็อก วงจรกรองสัญญาณ วงจรขยายสัญญาณ วงจรสังเคราะห์ความถี่ วงจรแปลงและรักษาระดับแรงดัน ตารางที่ 1.1 สรุปคุณลักษณะของตัวอย่าง อุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการแพทย์ ซึ่งงานวิจัยและพัฒนาอุปกรณ์และ ระบบต่างๆเหล่านี้เน้นไปที่วงจรอิเล็กทรอนิกส์ที่ใช้กำลังงานต่ำ สำหรับทำหน้าที่เชื่อมต่อกับตัวเซ็นเซอร์ ประมวลผลสัญญาณ การสื่อสาร และการจัดการพลังงาน

รายงานนี้นำเสนอผลงานวิจัยด้านการออกแบบวงจรรวมแอนะล็อกและผสมสัญญาณแบบซีมอสที่ใช้ กำลังไฟต่ำมากสำหรับการประยุกต์ใช้งาน ด้านชีวการแพทย์และการดูแลสุขภาพรอบตัว โดยอธิบายถึง การออกแบบวงจรที่ใช้กำลังไฟต่ำและแรงดันไฟเลี้ยงต่ำในเทคโนโลยีซีมอสสมัยใหม่ที่มีขนาดเล็กกว่า 1 ไมโครเมตร ด้วยวิธีการและเทคนิคต่างๆ เช่น การใช้มอสเฟตในย่านต่ำกว่าขีดเริ่ม เทคนิคทรานส์ลิเนียร์ โหมดกระแส เทคนิคการขับอินพุตที่ขาบอดี้ วงจรที่ได้นำเสนอใหม่ประกอบด้วย วงจรอ่านค่าสัญญาณ จากอีสเฟตที่ไวต่อค่า pH วงจรแปลงสัญญาณแอนะล็อกเป็นดิจิตอลแบบล็อกการิทึมโหมดกระแสที่ใช้ โครงสร้างแบบไพพ์ไลน์และแบบอัลกอริทึม วงจรตรวจวัดกำลังงานสัญญาณคลื่นความถี่วิทยุที่ใช้กำลังงาน ต่ำและมีพิสัยพลวัตสูง วงจรขยายทรานส์คอนดักแตนซ์เชิงเส้นที่ใช้แรงดันไฟเลี้ยงและกำลังงานต่ำ โดยใช้

ตารางที่ 1.1: สรุปคุณลักษณะอุปกรณ์อิเล็กทรอนิกส์สำหรับการประยุกต์ใช้งานด้านชีวการแพทย์

| Applications                                    | Performance specification |                                              |                          |                                        |                                                  |

|-------------------------------------------------|---------------------------|----------------------------------------------|--------------------------|----------------------------------------|--------------------------------------------------|

| Applications                                    | Power                     | ADC/DAC                                      | Processor                | Communi-                               | Energy                                           |

|                                                 |                           |                                              |                          | cation                                 | source                                           |

| Pacemakers<br>[4]                               | <10µW                     | 1ksps, 8b<br>ADC                             | 1kHz DSP                 | Inductive<br>link                      | 10-yr<br>lifetime<br>battery                     |

| Hearing aids [5]                                | 100-<br>2000μW            | 16ksps, 12b<br>ADC                           | 32<br>kHz-1MHz<br>DSP    | Telecoil                               | 1-wk<br>lifetime<br>recharge-<br>able<br>battery |

| Analog<br>cochlear [6],<br>[7]                  | <200μW                    | 16, 1ksps,<br>8b ADC                         | Analog DSP<br>(~16 MIPs) | Inductive<br>link                      | 1-wk<br>lifetime<br>recharge-<br>able<br>battery |

| Neural recording [8], [9]                       | 1-10mW                    | 1000s of<br>channels,<br>100 ksps,<br>8b ADC | n/a                      | High rate<br>inductive<br>link         | Inductive<br>power                               |

| Retinal<br>stimulator [10]                      | 250 mW                    | 10 ksps, 4b<br>ADC (per<br>electrode)        | No<br>embedded<br>DSP    | High rate<br>inductive<br>link         | Inductive<br>power                               |

| Bladder urine<br>pressure<br>Monitoring<br>[11] | 1.25 mW                   | 6b ADC                                       | No<br>embedded<br>DSP    | Off-chip<br>434MHz<br>wireless<br>link | 2-wk<br>lifetime<br>battery                      |

| Body-area<br>monitoring<br>[12]                 | 140 μW                    | 1 ksps, 12b<br>ADC (per<br>channel)          | < 10 MHz<br>DSP          | Far-field<br>Wireless<br>link          | Battery                                          |

เทคนิคการขับสัญญาณอินพุตที่ขาบอดี้ของมอสเฟต

รายงานนี้ได้จัดแบ่งเป็นบทต่างๆดังนี้ บทที่ 2 ได้กล่าวถึงการออกแบบและ จำลองการทำงานของ วงจรอ่านค่าสัญญาณจากอีสเฟตที่ไวต่อค่า pH ซึ่งมีขนาดเล็ก ง่ายต่อการออกแบบและใช้กำลังไฟฟ้าต่ำ มาก วงจรที่นำเสนอใช้โครงสร้างของวงจรขยายสัญญาณผลต่างที่ใช้อีสเฟตและรีเฟตในย่านผันกลับอย่าง อ่อน และใช้หลักการทรานส์ลิเนียร์โหมดกระแสเพื่อให้ได้ความเป็นเชิงเส้นที่ดีและสามารถกำจัดสัญญาณ รบกวนโหมดร่วมที่ขั้วอิเล็กโตรดอ้างอิง อีกทั้งยังสามารถชดเชยผลของตัวถัง (Body effects) ของเฟตได้ อีกด้วย วงจรที่นำเสนอมีศักยภาพเหมาะสมสำหรับใช้ในส่วนประมวลสัญญาณของระบบตรวจวัดชีวเคมี แบบฝังตัว (Implantable) และเวลาจริง (Real-time)

บทที่ 3 อธิบายการออกแบบและผลจำลองการทำงานของวงจรแปลงสัญญาณแอนะล็อกเป็นดิจิตอล แบบล็อกการิทึมโหมดกระแสที่ใช้โครงสร้างแบบไพพ์ไลน์และแบบอัลกอริทึม เพื่อใช้แปลงค่าสัญญาณ กระแสจากวงจรอ่านค่าสัญญาณอีสเฟตให้เป็นสัญญาณดิจิตอลที่มีความละเอียด 8 บิต โดยใช้เทคนิคการ ทำงานในย่านผันกลับอย่างอ่อนของมอสเฟต หลักการทรานส์ลิเนียร์ ผลการจำลองการทำงานวงจรด้วย เทคโนโลยีซีมอสขนาด  $0.18~\mu m$  แสดงให้เห็นว่าวงจรสามารถทำงานได้ดีที่แรงดันไฟเลี้ยงต่ำและใช้กำลัง ไฟต่ำเหมาะสมสำหรับการประยุกต์ใช้งานด้านชีวการแพทย์

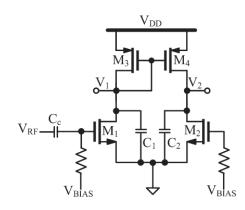

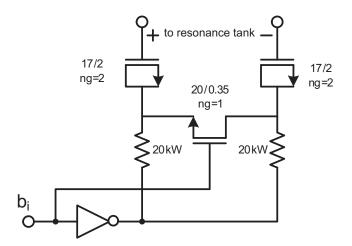

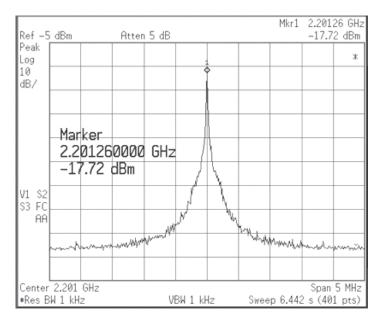

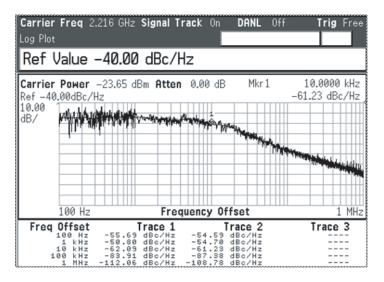

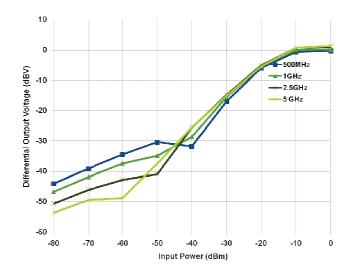

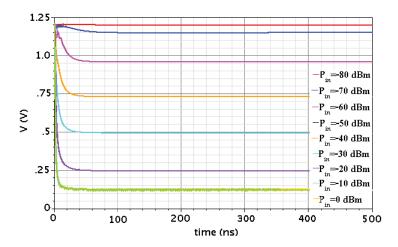

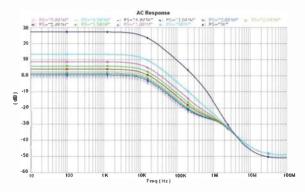

บทที่ 4 อธิบายการออกแบบวงจรตรวจวัดกำลังงานสัญญาณคลื่นความถี่วิทยุที่ใช้กำลังงานต่ำและมี พิสัยพลวัตสูง วงจรที่นำเสนอประกอบด้วยวงจรตรวจวัดกำลังงานค่ารากกำลังสองเฉลี่ย (Root mean square หรือ rms) และวงจรขยายล็อกการิทึม วงจรตรวจวัดกำลังงาน rms อาศัยคุณลักษณะความไม่เป็น เชิงเส้นของมอสเฟตในย่านอิ่มตัวและโหลดแอกทีฟเพื่อเพิ่มอัตราขยายแปลงที่กำลังงานต่ำสุด ทำให้ไม่ต้อง ใช้แบนด์วิดท์สูงและไม่ต้องใช้วงจรเรียงกระแสและวงจรกรอง ผลจำลองการทำงานที่ได้จากผังภูมิวงจรใน เทคโนโลยีซีมอสขนาด 0.18 ไมโครเมตร แสดงให้เห็นว่าวงจรสามารถตรวจวัดกำลังงานอินพุตได้ตั้งแต่ -70 dBm ถึง -20 dBm ในย่านความถี่ 500 MHz ถึง 5 GHz และใช้กำลังงาน 0.9 mW ดังนั้นวงจรจึงเหมาะ สมในการใช้งานสำหรับระบบโครงท่ายเซนเซอร์ไร้สาย

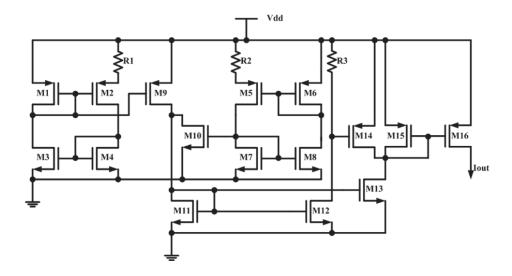

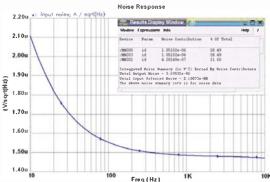

บทที่ 5 ได้กล่าวถึงการออกแบบวงจรขยายทรานส์คอนดักแตนซ์เชิงเส้นที่ใช้แรงดันไฟเลี้ยงและกำลังต่ำ โดยใช้เทคนิคการขับสัญญาณอินพุตที่ขาบอดี้ของมอสเฟต วงจรใช้โครงสร้างวงจรขยายสัญญาณผลต่าง อินพุตโดยขับสัญญาณอินพุตที่ขาบอดี้ร่วมกับการใช้ตัวต้านทานถดถอยที่ขาซอร์สร่วม (Resistive source degeneration) และโครงสร้างวงจรตามสัญญาณแบบกลับแรงดัน (Flipped-voltage follower) เพื่อให้ ได้ความเป็นเชิงเส้นที่สูงภายใต้การทำงานที่แรงดันไฟเลี้ยงต่ำ วงจรที่นำเสนอใช้กำลังไฟ 0.8  $\mu$ W จากแรง ดันไฟเลี้ยง 0.8 V และผลจำลองการทำงานของวงจรแสดงว่าวงจรมีความเป็นเชิงเส้นที่ดีโดยมีความผิด เพี้ยนฮาร์โมนิครวม (Total harmonic distortion) น้อยกว่า 1 % ในช่วงแรงดันอินพุต 470 mV วงจร ขยายทรานส์คอนดักแตนซ์เชิงเส้น ที่นำเสนอจึงมีศักยภาพเหมาะสมกับการประยุกต์ใช้งานสำหรับวงจร กรองความถี่และวงจรขยายในระบบวงจรรวมสำหรับทางชีวการแพทย์และโครงข่ายประสาท และบทที่ 6 สรุปผลการดำเนินงานของโครงการ

## บทที่ 2

วงจรอ่านค่าสัญญาณโหมดกระแสจาก ตัวเซ็นเซอร์อีสเฟตที่ใช้กำลังไฟต่ำยิ่ง (Ultra low-power current-mode readout circuit)

#### 2.1 บทน้ำ

จากความสำเร็จในการสร้างอีสเฟต หรือ Ion-sensitive field-effect transistor (ISFET) ด้วยเทคโนโลยีซี มอส [13] ทำให้เกิดความสนใจและพยายามอย่างมากในการวิจัยและพัฒนาเพื่อสร้างวงจรรวมที่ประกอบ ด้วยเซ็นเซอร์เคมีและชีวเคมีที่ใช้อีสเฟตและวงจรประมวลผลสัญญาณให้รวมอยู่ในชิพเดียวกัน [14] และ เมื่อไม่นานมานี้ได้มีการใช้อีสเฟตที่สร้างด้วยเทคโนโลยีซีมอสให้ทำงานในย่านต่ำกว่าแรงดันขีดเริ่ม ร่วม กันการใช้หลักการทรานส์ลิเนียร์ (Translinear principle) เพื่อสร้างวงจรอ่านค่าสัญญาณโหมดกระแสที่ ใช้กำลังไฟต่ำ [15] ซึ่งเป็นตัวอย่างหนึ่งของไมโครชิพเดี่ยวที่มีเซ็นเซอร์ฉลาดและมีกำลังไฟต่ำ มีศักยภาพสูง เหมาะสมกับการใช้ตรวจวัดทางชีวเคมีแบบเวลาจริง (real-time) สำหรับการใช้งานในระบบชีวการแพทย์ แบบฝังตัว (Implantable) บทนี้นำเสนองานวิจัยการออกแบบวงจรอ่านค่าสัญญาณผลต่างที่ใช้กำลังไฟต่ำ ยิ่งสำหรับอีสเฟตที่ไวต่อค่าพีเอช (pH)

2.2. หลักการทำงานของอีสเฟต

#### 2.2 หลักการทำงานของอีสเฟต

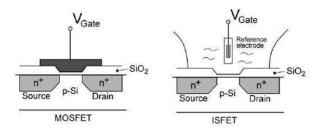

อีสเฟตหรือเฟตที่ไวต่อไอออนมีพื้นฐานโครงสร้างจากมอสเฟตดังแสดงในรูปที่ 2.1 โดยอีสเฟตมีขาเกตเป็น อิเล็กโตรดอ้างอิง (Reference Electrode) ที่สัมผัสกับสารละลาย (Solution) ผลของสนามไฟฟ้าจากปฏิ กริยาประจุไอออนที่พื้นผิวฉนวน (Insulator Surface) ของอีสเฟตทำให้เกิดการเปลี่ยนแปลงของคุณสมบัติ กระแสเดรน  $i_D$  และแรงดันเกตซอส  $v_{GS}$  ของอีสเฟต โดยการเลือกใช้วัสดุเป็นชั้นฉนวนของอีสเฟตที่เชื่อม ต่อกับอิเล็กโทรไลต์ (Electrolyte) ขึ้นอย่กับคณสมบัติทางเคมีและความไวต่อไอออนที่ต้องการวัด

แรงดันป้อนเข้าที่ขั้วไฟฟ้าอ้างอิงจะเชื่อมโยงแบบคาปาซิทีฟผ่านอิเล็กโทรไลต์ไปที่ผิวของชั้นฉนวน โดยที่ประจุจากไอออนที่พื้นผิวฉนวนจะมีการผันแปรตามค่า pH และทำให้กระแสเดรนและแรงดันขีดเริ่ม (Threshold voltage,  $V_{TH}$ ) ของอีสเฟตเปลี่ยนแปลงไป ซึ่งสามารถเขียนความสัมพันธ์ได้ดังสมการที่ 2.1 [16] โดยที่  $\phi_f$  คือคักย์ไฟฟ้าเฟอมิ (Fermi potential) ของสารกึ่งตัวนำ  $Q_{ss}$  คือความหนาแน่นประจุพื้น ผิวคงที่ต่อพื้นที่รอยต่อฉนวนและสารกึ่งตัวนำ  $Q_{ss}$  คือความหนาแน่นประจุบริเวณผิวของชั้นปลอดพาหะ ของสารกึ่งตัวนำต่อพื้นที่  $E_{ref}$  คือศักย์ไฟฟ้าของขั้วอิเล็กโตรดอ้างอิงเทียบกับอิเล็กโตรดของไฮโดรเจน  $\phi_{lj}$  คือความต่างศักย์ไฟฟ้าของรอยต่อเหลวระหว่างสารละลายอ้างอิงและอิเล็กโตรไลต์  $\chi_{eo}$  คือศักย์ไฟฟ้า โดโพลที่ผิวอิเล็กโตรไลต์และฉนวน  $\phi_s$  คือฟังก์ชั่นงาน (work function) ของสารกึ่งตัวนำ  $V_{chem}$  คือผล รวมของศักย์ไฟฟ้าเคมที่ผิวของชั้นฉนวน  $\varphi_{eo}$  คือศักย์ไฟฟ้าของรอยต่อระหว่างอิเล็กโตรไลต์และฉนวนที่ มีค่าผันแปรขึ้นอยู่กับค่า pH ของสารละลาย ดังแสดงในสมการที่ 2.3 และเป็นตัวแปรที่กำหนดความไว ของอีสเฟต  $U_T = {}^{kT}/q$  คือแรงดันอุณหภูมิ (Thermal voltage)  $pH_{pze}$  คือค่า pH ที่ทำให้ไม่มีประจุที่ผิว ฉนวน  $\alpha = {}^{S/S_{Nernst}}$  คือตัวแปรที่แสดงค่าความไวของอีสเฟต (S) ต่อความไวเนอสเตียนอุดมคติ (Ideal Nernstian sensitivity,  $S_{Nernst}$ ) (ไม่มีหน่วย)

$$V_{th(ISFET)} = (E_{ref} + \phi_{lj}) - (\varphi_{eo} - \chi_{eo}) - \frac{Q_{ss} + Q_{sc}}{C_{ox}} - 2\phi_f + \frac{\phi_s}{q} = V_{th(MOS)} + V_{chem}$$

(2.1)

$$V_{chem} = (E_{ref} + \phi_{lj}) - (\varphi_{eo} - \chi_{eo}) - \frac{\phi_m}{q}$$

(2.2)

$$\varphi_{eo} = 2.3U_T\alpha \left(pH_{pze} - pH\right) \tag{2.3}$$

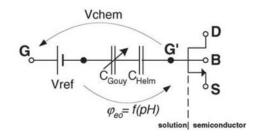

ความสัมพันธ์ของ  $V_{chem}$  กับค่า pH สามารถถูกจำลองได้โดยใช้ทฤษฎีไซท์-ไบดิ้ง (Site-Binding Theory) และแบบจำลองสองชั้นของโกย-แชพเมน-สเทอน (Gouy-Chapman-Stern Double-Layer Model) [16] ซึ่งสามารถแสดงด้วยแบบจำลองพฤติกรรมในรูปที่ 2.2 และเพื่อให้ง่ายต่อการวิเคราะห์ต่อไป  $V_{chem}$  สามารถถูกเขียนได้ใหม่ตามสมการที่ 2.4 โดยที่  $\gamma$  คือผลรวมของศักย์เคมีทั้งหมดที่เป็นอิสระจากค่า pH

รูปที่ 2.1: โครงสร้างกายภาพของอีสเฟตกับมอสเฟต

รูปที่ 2.2: แบบจำลองเชิงพฤติกรรมของอีสเฟต

และด้วยการประมาณอันดับที่หนึ่ง  $\alpha$  จะมีค่าคงที่ ทำให้  $V_{chem}$  และแรงดันขีดเริ่มของอีสเฟตจะมีค่า แปรผันโดยตรงกับค่า pH และอุณหภูมิ

$$V_{chem} = \gamma + 2.3U_T \alpha p H \tag{2.4}$$

#### 2.3 อีสเฟตในย่านการทำงานผันกลับอย่างอ่อน

อีสเฟตที่ทำงานในย่านผันกลับอย่างอ่อนจะมีแรงดันเกตซอส  $(v_{GS})$  น้อยกว่าแรงดันขีดเริ่ม  $(V_{th})$  และ การนำกระแสของอีสเฟตจะเกิดจากการเคลื่อนที่ของประจุพาหะภายใต้กระบวนการแพร่ (diffusion) โดยที่กระแสเดรนของมอสเฟตในย่านผันกลับอย่างอ่อนสามารถแสดงได้ดังสมการที่ 2.5 และ  $I_s=2n\mu_o C_{ox}\left(\frac{W}{L}\right)U_T^2e^{\left(\frac{-V_{T0}}{nU_T}\right)}e^{\left(\frac{(n-1)V_{BS}}{nU_T}\right)}$  เมื่อ  $V_{T0}$  คือแรงดันขีดเริ่มเมื่อ  $V_{BS}=0$  และ n คือปัจจัยความชัน ของการผันกลับอย่างอ่อน (Subthreshold slope factor) และมอสเฟตทำงานในย่านอิ่มตัวเมื่อ  $V_{DS}>4U_T$  โดยสมการที่ 2.5 สามารถใช้กับอีสเฟตที่ทำงานในย่านผันกลับอย่างอ่อนได้เนื่องจากการเปลี่ยนแปลง ทางเคมีต่างๆทำให้แรงดันขีดเริ่มเปลี่ยนแปลงเนื่องจากผลของ  $V_{chem}$  ที่ผันแปรตามค่า pH และเนื่องจากอีสเฟตที่ทำงานในย่านผันกลับอย่างอ่อนมีกระแสเดรนที่ผันแปรเป็นฟังก์ชั่นเอ็กโพเนนเชียลกับแรงดันขีด เริ่มซึ่งผันแปรตรงกับค่า pH และเนื่องจากค่า pH มีค่าผันแปรเป็นฟังก์ชั่นอีกการิทึมกับความเข้มข้นของ โอออนไฮโดรเจน ทำให้กระแสเดรนที่การผันแปรที่เป็นเชิงเส้นกับความเข้มข้นของไอออนไฮโดรเจน

$$I_D = I_s e^{\left(\frac{v_{GS}}{nU_T}\right)} \left(1 - e^{\left(\frac{-v_{DS}}{U_T}\right)}\right) \tag{2.5}$$

การผันแปรของค่า pH  $(\triangle pH)$  สามารถแสดงได้เป็นการผันแปรของ  $V_{chem}$   $(\triangle V_{chem})$  และ  $V_{th}$   $(\triangle V_{T0})$  ดังแสดงในสมการที่ 2.6 และหากสมมติให้  $V_{BS}=0$  และอีสเฟตทำงานในย่านอื่มตัว  $(V_{DS}>4U_T)$  ดังนั้น ค่ากระแสเดรนของอีสเฟตที่เปลี่ยนแปลงสามารถแสดงได้ดังสมการที่ 2.7 โดยที่  $I_{DQ}$  คือกระแสเดรนขอ งอีสเฟตในสภาวะสงบนิ่ง (quiescent)

$$\Delta V_{T0} = \Delta V_{chem} = 2.3 U_T \alpha \Delta p H \tag{2.6}$$

$$I_D\left(V_{T0} + \triangle V_{T0}\right) = 2n\mu_o C_{ox}\left(\frac{W}{L}\right) U_T^2 e^{\left(\frac{v_{GS}}{nU_T}\right)} e^{\left(\frac{-\triangle V_{T0}}{nU_T}\right)} = I_{DQ} e^{\left(\frac{-2.3U_T \alpha \triangle pH}{nU_T}\right)}$$

(2.7)

และ เนื่องจากค่า pH มีค่าผันแปรเป็นฟังก์ชั่นล็อกการิทึมกับความเข้มข้นของไอออนไฮโดรเจนดัง สมการที่ 2.8 ดังนั้นความสัมพันธ์ระหว่างกระแสเดรนของอีสเฟตและความเข้มข้นของไอออนไฮโดรเจน สามารถแสดงได้ดังสมการที่ 2.9 และค่า  $\alpha/n$  มีค่าอยู่ระหว่าง 0 กับ 1 เนื่องจาก  $0 < \alpha < 1$  และ n > 1

$$pH = -\log_{10}\left[H^{+}\right] \tag{2.8}$$

$$I_{D}\left(V_{T0} + \triangle V_{T0}\right) = I_{DQ}e^{\left(\frac{-2.3U_{T}\alpha\left(-\ln\left[H^{+}\right]/2.3\right)}{nU_{T}}\right)} = I_{DQ}\triangle\left[H^{+}\right]^{\alpha/n}$$

(2.9)

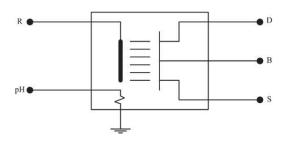

งานวิจัยนี้ใช้แบบจำลองอีสเฟตจาก [16] รูปที่ 2.3 และรูปที่ 2.4 แสดงสัญลักษณ์ของอีสเฟตและวงจร ที่ใช้ทดสอบคุณลักษณะของอีสเฟตตามลำดับ รูปที่ 2.5 แสดงผลจำลองคุณสมบัติ  $i_D$  vs.  $v_{DS}$  ของอีสเฟต ที่มีขนาด W/L =  $100\mu$ m/ $10\mu$ m ที่ค่า pH คงที่เท่ากับ 7 (i.e.  $V_{pH}=7$  V) โดยที่มีการเปลี่ยนแปลงแรงดัน ขั้วไฟฟ้าอ้างอิง ( $V_R$ ) ตั้งแต่ 0 - 2 V รูปที่ 2.6 แสดงผลจำลองคุณสมบัติ  $i_D$  vs.  $v_{GS}$  (i.e.  $V_R$ ) ของอีสเฟต ที่มีขนาด W/L =  $100\mu$ m/ $10\mu$ m ที่ค่า pH เท่ากับ 4, 7 และ 10 (i.e.  $V_{pH}=4$ , 7 และ 10 V) โดยที่มีการ เปลี่ยนแปลงแรงดันขั้วไฟฟ้าอ้างอิง ( $V_R$ ) ตั้งแต่ 0 - 4 V จะเห็นได้ว่าอีสเฟตมีคุณสมบัติคล้ายกับมอสเฟต รูปที่ 2.10 แสดงคุณสมบัติ  $i_D$  vs. pH (i.e.  $V_{pH}$ ) ของอีสเฟตที่มีขนาด W/L =  $100\mu$ m/ $10\mu$ m ที่ค่า pH ระหว่าง 0 ถึง 14 (i.e.  $V_{pH}=0$  - 14 V) โดยที่มีการเปลี่ยนแปลงแรงดันขั้วไฟฟ้าอ้างอิง ( $V_R$ ) ตั้งแต่ 0 - 1.4 V ซึ่งแสดงว่าช่วงความเป็นเชิงเส้นที่ดีที่สุดต้องมีค่าแรงดันที่ขั้วไฟฟ้าอ้างอิงไม่น้อยกว่า 1 V และอีสเฟ ตมีค่าความไวต่อค่า pH ประมาณ -28  $\mu A/pH$

รูปที่ 2.3: สัญลักษณ์ของอีสเฟต

รูปที่ 2.4: วงจรทดสอบคุณลักษณะทางไฟฟ้าของอีสเฟต

รูปที่ 2.5: คุณสมบัติกระแสเดรนและแรงดันเดรนซอสของอีสเฟตที่ค่า pH=7

รูปที่ 2.6: คุณสมบัติกระแสเดรนและแรงดันเกตซอสของอีสเฟตที่ค่า pH=4, 7 และ 10

รูปที่ 2.7: คุณสมบัติกระแสเดรนและค่า pH

รูปที่ 2.8: วงจรอ่านค่าสัญญาณผลต่างจากอีสเฟตที่ได้นำเสนอขึ้นใหม่

## 2.4 วงจรอ่านค่าสัญญาณจากอีสเฟตที่นำเสนอ

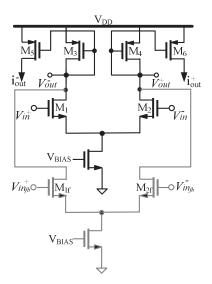

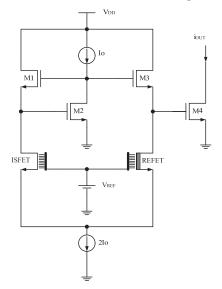

รูปที่ 2.8 แสดงวงจรอ่านค่าสัญญาณผลต่างจากอีสเฟตที่ใช้กำลังไฟต่ำยิ่งที่ได้นำเสนอขึ้นใหม่ โดยใช้ โครงสร้างของวงจรขยายสัญญาณผลต่างที่ใช้เฟตที่ไม่ไวต่อไอออน (Ion-insensitive FET) หรือที่เรียก ว่า Referenced ISFET (REFET) และอีสเฟตโดยใช้ขั้วโลหะอิเล็กโตรดต่อกับขาเกตของอีสเฟตและรีเฟต เข้ากับแรงดันไฟตรงอ้างอิง ( $V_{REF}$ ) ซึ่งจะทำให้เราสามารถกำจัดหรือลดการแปรผันของกระแสเอาท์พุตที่ เกิดจากการผันแปรของแรงดันไฟตรงอ้างอิงและทำให้สามารถใช้ขั้วอิเล็กโตรดแบบโซลิดสเตทได้ มอสเฟต อีสเฟตและรีเฟตทุกตัวทำงานในย่านผันกลับอย่างอ่อนแบบอิ่มตัว (Saturated weak-inversion region) (i.e.  $V_{GS} < V_{TH}$  และ  $V_{DS} > 4U_T$ ) โดยมีกระแสไฟตรงไบอัสเท่ากับ  $I_O$  เท่ากันทั้งหมด

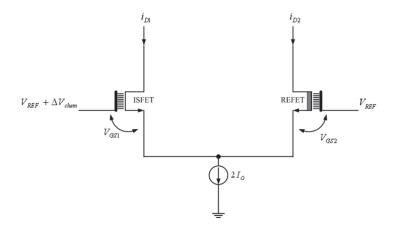

รูปที่ 2.9 แสดงวงจรขยายสัญญาณผลต่าง (Differential Pair) ที่ประกอบด้วยอีสเฟตและรีเฟตที่มี ขนาด (W/L) เท่ากันและทำงานในย่านการผันกลับอย่างอ่อน โดยถ้าสมมติว่า  $V_{BS}=0$  และ  $V_{DS}>4U_T$  กระแสเดรนของอีสเฟตและรีเฟตสามารถเขียนได้ดังสมการที่ 2.10 และ 2.11 และผลรวมของกระแส  $i_{D1}$  และ  $i_{D2}$  มีค่าเท่ากับกระแสไบอัส  $2I_O$  ดังแสดงในสมการที่ 2.12 และผลต่างแรงดัน  $v_{GS1}$  และ  $v_{GS2}$  มีค่า เท่ากับค่าผันแปรของศักย์ทางเคมี  $\Delta V_{chem}$  คือดังแสดงในสมการที่ 2.13 ดังนั้นเราสามารถเขียน  $i_{D1}$  และ  $i_{D2}$  ได้ดังสมการที่ 2.14 และ 2.15

$$i_{D1} = I_{s1}e^{V_{GS1}/nU_T} (2.10)$$

รูปที่ 2.9: วงจรขยายสัญญาณผลต่าง (Differential Pair) ที่ประกอบด้วยอีสเฟตและรีเฟต

$$i_{D2} = I_{s2}e^{V_{GS2/nU_T}} (2.11)$$

$$i_{D1} + i_{D2} = 2I_O (2.12)$$

$$v_{GS1} - v_{GS2} = \triangle V_{chem} \tag{2.13}$$

$$i_{D1} = 2I_O \cdot \frac{e^{-\left(\frac{\triangle V_{chem}}{nU_T}\right)}}{1 + e^{-\left(\frac{\triangle V_{chem}}{nU_T}\right)}} \tag{2.14}$$

$$i_{D2} = 2I_O \cdot \frac{1}{1 + e^{-\left(\frac{\triangle V_{Chem}}{nU_T}\right)}}$$

(2.15)

โดยที่  $I_O$  คือกระแสเดรนของอีสเฟตและรีเฟตที่ค่า pH อ้างอิง (เช่น pH = 7) ดังนั้นกระแสของอีสเฟตจะมีค่าเท่ากับ  $2I_O$  และกระแสรีเฟตมีค่าเป็นศูนย์สำหรับค่า  $\triangle pH$  ที่ค่าลบมากๆ และในทางตรงกันข้าม สำหรับค่า  $\triangle pH$  ที่มีค่าบวกมากๆ ซึ่งมีคุณลักษณะคล้ายกับการทำงานของวงจรขยายสัญญาณผลต่างที่ใช้ มอสเฟต (MOSFET Differential Pair)

จากรูปที่ 2.8 มอสเฟต  $(M_1-M_4)$  ทำงานในย่านผันกลับอย่างอ่อน และประกอบกันเป็นวงจรทรานส์ลิ เนียร์ซึ่งมีกระแสเอาท์พุต  $(I_{out})$  ดังสมการที่ 2.16 และ 2.17 และเนื่องจาก  $\triangle pH = -\log_{10} \triangle [H+]$  โดยที่  $\triangle [H+]$  คือความเข้มข้นของไฮโดรเจนไอออนที่เปลี่ยนแปลงไป และเนื่องจาก  $0<\alpha<1$  และ n>1 ดัง นั้นค่า  $\alpha/n$  มีค่าระหว่าง 0 กับ 1 ดังนั้นจะเห็นได้ว่าค่า pH ที่เปลี่ยนแปลงไปมีความสัมพันธ์ที่เป็นเชิงเส้น

กับค่าล็อกการิทึมของกระแสเอาท์พุตดังแสดงในสมการที่ 2.18

$$i_{out} = \frac{i_{D1}i_{D2}}{i_{D3}} = \frac{i_{D,ISFET}I_O}{i_{D,REFET}} = I_O e^{-\left(\frac{\triangle V_{chem}}{nU_T}\right)}$$

(2.16)

$$i_{out} = I_O \triangle \left[ H^+ \right]^{\alpha/n} \tag{2.17}$$

$$\log_{10} i_{out} = \log_{10} I_O - \left(\frac{\alpha}{n}\right) \triangle pH \tag{2.18}$$

ถ้าสมมติให้อุปกรณ์ทุกตัวอยู่ใกล้กันและมีสภาพแวดล้อมเชิงอุณหภูมิเหมือนกัน (Thermally matched) ความสัมพันธ์แบบอัตราส่วนของหลักการทรานลิเนียร์จะช่วยลดการผันแปรของวงจรที่เกิดจากกับอุณหภูมิ (Temperature dependence) และการใช้วงจรขยายสัญญาณผลต่างอีสเฟตและรีเฟตทำให้ผลกระทบ จากฐานรอง (Body effects) ของมอสเฟต อีสเฟตและรีเฟต หักล้างกันหมดไปในทางทฤษฏี และถ้าสร้าง แหล่งจ่ายกระแส  $I_O$  ที่เป็นอิสระกับอุณหภูมิและสมมติว่า  $\alpha$  และ n ไม่ขึ้นกับอุณหภูมิ เราจะได้กระแส เอาท์พุตของวงจรที่เป็นอิสระจากผลการเปลี่ยนแปลงอุณหภูมิ

วงจรอ่านค่าสัญญาณผลต่างจากอีสเฟตที่นำเสนอได้ถูกออกแบบให้ทำงานที่แรงดันแหล่งจ่ายไฟเลี้ยง 1 โวลต์ อีสเฟตและรีเฟตถูกจำลองการทำงานโดยใช้แบบจำลองทางคณิตศาสตร์จาก [16] และจำลองการ ทำงานของวงจรโดยใช้โปรแกรม Cadence และพารามิเตอร์จากเทคโนโลซีมอสขนาด  $0.35~\mu m$  มอสเฟต ทุกตัวมีขนาด  $5~\mu m/2~\mu m$  อีสเฟตและรีเฟตมีขนาดเท่ากันคือ  $100~\mu m/10~\mu m$  เพื่อให้มีความสมพงศ์ที่ดี (good matching) แหล่งจ่ายกระแสไฟตรงถูกสร้างโดยใช้วงจรสะท้อนกระแสอย่างง่ายและใช้มอสเฟตที่มี ความยาวช่องทางใหญ่เพื่อให้ได้ความแม่นยำที่ดีและมีความต้านทานเอาท์พุตมาก ตัวแปร  $\alpha/n$  มีค่าเท่ากับ 0.7~h1 ค่ากระแส  $I_O$  มีค่าเท่ากับ 1~n2 และแรงดัน  $V_{REF}$  มีค่าเท่ากับ 200~m4 โดยที่กระแสและแรงดันไบ อัสทั้งหมดถูกเลือกเพื่อให้วงจรทำงานกับค่า p4 อ้างอิงเท่ากับ 7~h6 โดยที่วงจรใช้กำลังไฟฟ้าเท่ากับ 4~n4 nW

รูปที่ 2.10 แสดงผลจำลองการทำงานคุณลักษณะกระแส  $I_{out}$  กับค่า pH ระหว่าง 4 ถึง 10 ที่ค่าแรงดัน  $V_{REF}$  ต่างๆระหว่าง 50 mV ถึง 250 mV โดยที่ค่าแรงดัน  $V_{REF}=200$  mV ค่า  $\log_{10}\left(I_{out}\right)$  กับค่า pH มีคุณลักษณะเป็นเชิงเส้นดีที่สุดในช่วงค่า pH ระหว่าง 4 ถึง 10 ซึ่งช่วงความเป็นเชิงเส้นถูกจำกัดโดยช่วง การทำงานในย่านผันกลับอย่างอ่อนของอีสเฟตที่อยู่ในช่วงการผันแปรของกระแสเดรนประมาณ 1,000 - 10,000 เท่า (i.e. 3-5 decades) รูปที่ 2.10 แสดงให้เห็นว่าแม้แรงดัน  $V_{REF}$  จะมีผันแปรมากกว่า 200 mV ก็ยังไม่มีผลกระทบต่อกระแส  $I_{out}$  ในช่วงค่า pH ระหว่าง 5 ถึง 9 อย่างไรก็ตามที่ค่า pH ต่ำๆ และ ค่า pH สูงๆ ค่ากระแส  $I_{out}$  จะมีการผันแปรไปเนื่องจากกระแสเดรนของอีสเฟตและรีเฟตในวงจรขยาย สัญญาณผลต่างมีการอิ่มตัว หรือกระแสเดรนของอีสเฟตและรีเฟตอย่างใดอย่างหนึ่งมีค่าเป็นศูนย์

เพื่อทดสอบความสามารถในการกำจัดหรือลดทอนผลกระทบของสัญญาณรบกวนโหมดร่วมของวงจร แรงดันอ้างอิง  $V_{REF}$  ถูกจำลองให้มีแรงดันสัญญาณรบกวนขนาด 20 mV (ร้อยละ 10 ของ  $V_{REF}$ ) ที่

รูปที่ 2.10: คุณลักษณะกระแส  $I_{out}$  กับค่า pH ที่ค่าแรงดัน  $V_{REF}$  ระหว่าง 50 mV ถึง 250 mV

รูปที่ 2.11: ผลการจำลองทางเวลาของกระแส  $I_{out}$  ต่อการเปลี่ยนแปลงของค่า pH

ความถี่ 50 Hz และค่า pH ถูกสมมติให้มีการเปลี่ยนแปลงแบบเชิงเส้นระหว่าง 4 ถึง 10 ภายในเวลา 1 วินาที รูปที่ 2.11 แสดงผลการจำลองทางเวลาของกระแสอีสเฟต กระแสรีเฟตและกระแสเอาท์พุตต่อการ ผันแปรของค่า pH ซึ่งจะเห็นได้ว่ากระแสทั้งหมดได้รับผลกระทบจากแรงดันสัญญาณรบกวนโหมดร่วมที่ เกิดขึ้นที่แรงดัน  $V_{REF}$  น้อยมากจนไม่มีนัยสำคัญ ยกเว้นในย่านที่ค่า pH น้อยกว่า 5 หรือมากกว่า 9 ซึ่ง เป็นผลกระทบมาจากการที่กระแสเดรนของอีสเฟตและรีเฟตในวงจรขยายสัญญาณผลต่างมีการอิ่มตัว

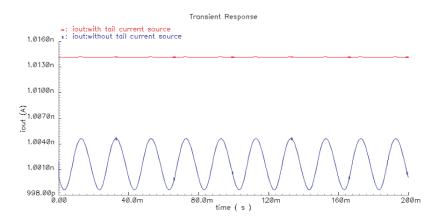

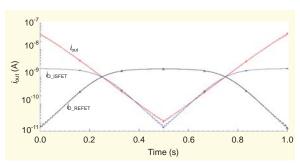

รูปที่ 2.12 แสดงกระแสเอาท์พุตที่ค่า pH = 7 ในกรณีที่วงจรใช้และไม่ใช้แหล่งจ่ายกระแสไบอัส  $(2I_O)$  ซึ่งเห็นได้ว่าในกรณีที่มีแหล่งจ่ายกระแสไบอัสนั้น กระแสเอาท์พุตไม่มีการผันแปร ในขณะที่กรณีที่ไม่ใช้ แหล่งจ่ายกระแสไบอัสกระแสเอาท์พุตมีการผันแปรค่าประมาณ 10 pA หรือร้อยละ 10 ของ  $I_O$  ดังนั้นจึง สรุปได้ว่าวงจรที่นำเสนอนั้นมีความสามารถในการกำจัดหรือลดทอนสัญญาณรบกวนโหมดร่วมสูงมาก

2.5. สรุป

รูปที่ 2.12: กระแสเอาท์พุตที่ค่า pH=7 ในกรณีที่วงจรใช้ (With) และไม่ใช้ (Without) แหล่งจ่ายกระแส ไบอัส  $(2I_O)$

#### 2.5 สรุป

บทนี้ได้กล่าวถึงการออกแบบและ จำลองการทำงานของวงจรอ่านค่าสัญญาณจากอีสเฟตที่ไวต่อค่า pH ซึ่งมีขนาดเล็ก ง่ายต่อการออกแบบและใช้กำลังไฟฟ้าต่ำมาก วงจรที่นำเสนอใช้โครงสร้างของวงจรขยาย สัญญาณผลต่างที่ใช้อีสเฟตและรีเฟตในย่านผันกลับอย่างอ่อน และใช้หลักการทรานส์ลิเนียร์โหมดกระแส เพื่อให้ได้ความเป็นเชิงเส้นที่ดีและสามารถกำจัดสัญญาณรบกวนโหมดร่วมที่ขั้วอิเล็กโตรดอ้างอิง อีกทั้ง ยังสามารถชดเชยผลของตัวถัง (body effects) ของเฟตได้อีกด้วย วงจรที่นำเสนอมีศักยภาพเหมาะ สมสำหรับใช้ในส่วนประมวลสัญญาณของระบบตรวจวัดชีวเคมีแบบฝังตัว (implantable) และเวลาจริง (real-time)

## บทที่ 3

วงจรแปลงสัญญาณแอนะล็อกเป็น

ดิจิตอลโหมดกระแสแบบล็อกการิทึมที่ใช้

กำลังไฟต่ำ (Ultra low-power

current-mode logarithmic

analog-to-digital converter)

#### 3.1 บทนำ

วงจรแปลงสัญญาณแอนะล็อกเป็นดิจิตอลแบบล็อกการิทึม (Logarithmic analog-to-digital converter, LogADC) มักถูกใช้งานในระบบประมวลสัญญาณเพื่อบีบอัดและแปลงสัญญาณแบบไม่เป็นเชิงเส้นเพื่อให้ ได้อัตราส่วนสัญญาณต่อสัญญาณรบกวน (signal-to-noise ratio, SNR) ดีที่สุดสำหรับช่วงสัญญาณอินพุ ตกว้าง วงจร LogADC สามารถถูกสร้างได้โดยใช้วงจรแปลงล็อกการิทึมแบบแอนะล็อกที่อาศัยคุณลักษณะ เอ็กซ์โพเนนเชียลของไบโพล่าร์ทรานซิสเตอร์ [17] หรือไดโอด [18] ร่วมกับวงจรแปลงสัญญาณแอนะ ล็อกเป็นดิจิตอลแบบเชิงเส้น หรือใช้หลักการประมวลสัญญาณในโดเมนล็อกการิทึมซึ่งทำให้สามารถสร้าง LogADC ในโครงสร้างแบบไพพ์ไลน์ (Pipeline) แบบอัลกอริทึม (Algorithmic) หรือแบบแฟลชสองขั้น (Two-step flash) ได้ในเทคโนโลยีซีมอส [19], [20] โดยเมื่อเร็วๆนี้วงจร LogADC และ  $\mu$  – law ADC อย่างง่ายได้ถูกนำเสนอโดยใช้เทคนิควงจรโหมดกระแส [21]

บทนี้นำเสนองานวิจัยเกี่ยวกับการออกแบบและการสร้างวงจร LogADC โหมดกระแสที่ใช้กำลังไฟต่ำ โดยอาศัยโครงสร้างการทำงานแบบไพพ์ไลน์และแบบอัลกอริทึม ที่เหมาะสมสำหรับการใช้งานกับเซ็นเซอร์ และด้านชีวการแพทย์ วงจร ADC ที่นำเสนอมีเป้าหมายเพื่อนำไปใช้กับวงจรอ่านค่าสัญญาณจากอีสเฟตที่ ทำงานในย่านผันกลับอย่างอ่อน [15, 22] ซึ่งมีกระแสเอาท์พุตที่มีความสัมพันธ์กับค่า pH ที่เปลี่ยนแปลง ไปเป็นฟังก์ชั่นเอ็กซ์โพเนนเซียล ดังนั้นวงจร LogADC จะแปลงกระแสเอาท์พุตจากวงจรอ่านค่าสัญญาณ อีสเฟตให้เป็นสัญญาณดิจิตอลเอาท์พุต ซึ่งมีความสัมพันธ์ที่เป็นเชิงเส้นกับค่าอินพุต pH ที่เปลี่ยนแปลง

### 3.2 การแปลงสัญญาณแอนะล็อกเป็นดิจิตอลแบบล็อกการิทึม

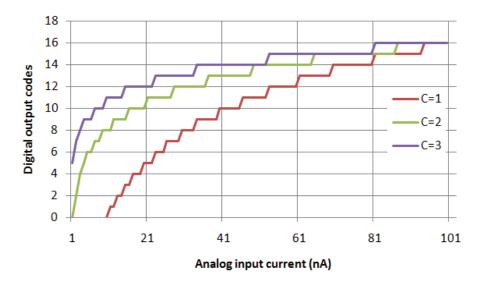

วงจร LogADC โหมดกระแสที่มีสัญญาณดิจิตอลเอาท์พุตจำนวน N บิต ทำหน้าที่แปลงสัญญาณกระแสแอ นะล็อกอินพุต  $(i_{in})$  เป็นสัญญาณดิจิตอลเอาท์พุต  $(D_{out})$  ในโดเมนล็อก ที่มีความสัมพันธ์ดังแสดงในสมการ ที่ 3.1 โดยที่  $I_{FS}$  คือค่ากระแสอินพุตสูงสุดของวงจร ADC ซึ่งให้ค่าดิจิตอลเอาท์พุตสูงสุดเท่ากับ  $2^N-1$  และ C คือสัมประสิทธิ์คุณลักษณะของฟังก์ชั่นล็อกการิทึม โดยถ้า C มีค่ามาก จะทำให้คุณสมบัติฟังก์ชั่นล็อกการิทึมมีความละเอียดมากขึ้นที่ค่าสัญญาณอินพุตน้อยๆ และทำให้วงจร ADC มีพิสัยพลวัต (Dynamic range) สูงขึ้น ดังแสดงในรูปที่ 3.1 ซึ่งแสดงให้เห็นว่าวงจร LogADC มีขนาดของค่าสัญญาณดิจิตอลบิตที่มีความ สำคัญน้อยที่สุด หรือ Least significant bit (LSB) ขึ้นอยู่กับค่าสัญญาณแอนะล็อกอินพุต โดยสัญญาณ อินพุตขนาดเล็กจะมีขนาด LSB ที่น้อยกว่าค่าสัญญาณอินพุตที่มีขนาดใหญ่ หรือหมายความว่าสัญญาณ อินพุตขนาดเล็กจะถูกแปลงเป็นสัญญาณดิจิตอลด้วยความละเอียดมากกว่าค่าสัญญาณอินพุตขนาดใหญ่ และเมื่อเปรียบเทียบกับวงจร ADC แบบเชิงเส้นที่มีขนาดของ LSB (i.e.  $LSB = i_{IN,i+1} - i_{IN,i}$ ) คงที่เท่ากับ  $I_{FS}/2^N$  วงจร LogADC มีขนาดของ LSB ในโดเมนล็อก (i.e.  $LSB(dB) = \log_{10}(i_{IN,i+1}) - \log_{10}(i_{IN,i})$ ) คงที่เท่ากับ  $C/2^N$  ดังนั้นวงจร LogADC ขนาด 8 บิตที่มีค่า C=2 จะมีค่า LSB(dB) =  $2/2^s$ =0.078125

$$i_{in} = I_{FS} \times 10^{C \cdot \left(\frac{D_{out}}{2^N} - 1\right)} \tag{3.1}$$

# 3.3 วงจร LogADC โหมดกระแสแบบไพพ์ไลน์ (Current-mode Logarithmic Pipeline ADC)

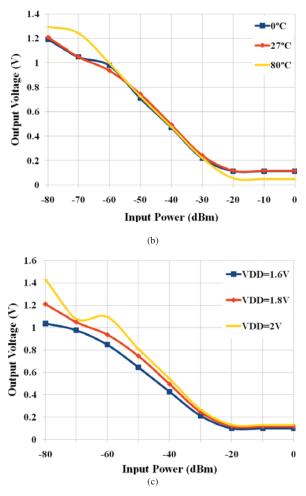

#### 3.3.1 โครงสร้างวงจร

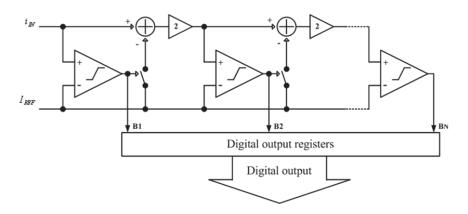

วงจร LogADC แบบไพพ์ไลน์มีโครงสร้างเหมือนกับวงจร ADC ไพพ์ไลน์แบบเชิงเส้น ซึ่งสามารถอธิบาย หลักการทำงานได้โดยการเปรียบเทียบกับวงจร ADC ไพพ์ไลน์แบบเชิงเส้น ซึ่งแสดงในรูปที่ 3.2 ประกอบ ด้วยภาคการแปลงสัญญาณ (stage) ทั้งหมดจำนวน N ภาค โดยที่ N คือจำนวนบิตของสัญญาณดิจิตอล

รูปที่ 3.1: คุณลักษณะอินพุตและเอาท์พุตของวงจร LogADC ขนาด 5 บิต

เอาท์พุตหรือความละเอียด (resolution) ของวงจร ADC โดยสัญญาณอินพุตของวงจร ADC จะถูกแปลง เป็นสัญญาณดิจิตอลเอาท์พุตทีละบิตเริ่มตั้งแต่ภาคแรกจะแปลงสัญญาณดิจิตอลบิตที่มีความสำคัญสูงสุด (Most significant bit, MSB) และส่งสัญญาณส่วนที่เหลือ (residue signal) ไปยังภาคถัดไปเพื่อแปลง สัญญาณดิจิตอลบิตที่อไป จนกระทั่งถึงภาคสุดท้ายที่จะแปลงสัญญาณดิจิตอลบิตที่มีความสำคัญน้อยที่สุด (Least significant bit, LSB) โดยในแต่ละภาคของวงจร ADC ไพพ์ไลน์แบบเชิงเส้นประกอบด้วยวงจรสุ่ม และคงค่าสัญญาณ วงจรเปรียบเทียบสัญญาณ สวิทช์ วงจรบวกลบสัญญาณ และวงจรคูณสองสัญญาณ ซึ่งมีหลักการทำงานดังนี้ โดยวงจรเปรียบเทียบสัญญาณจะเปรียบเทียบสัญญาณอินพุต  $(i_{IN})$  กับสัญญาณ อ้างอิง  $(I_{REF})$  ซึ่งมีค่าเป็นครึ่งหนึ่งของค่าสูงสุดของสัญญาณอินพุต  $(I_{FS})$  หรือช่วงสัญญาณอินพุตทั้งหมด ของวงจร ADC (Input range) ซึ่งในกรณีที่สัญญาณอินพุตมีค่าน้อยกว่าสัญญาณอ้างอิง สัญญาณเอาท์พุต ของวงจรเปรียบเทียบสัญญาณ  $(B_i)$  จะมีค่าเป็นลอจิก "0" ทำให้สวิทช์ไม่เปิดทำงาน (OFF) และสัญญาณอินพุตจะถูกส่งผ่านไปยังวงจรคูณสองและภาคถัดไป ในกรณีที่สัญญาณอินพุตมีค่ามากกว่าสัญญาณอ้างอิง สัญญาณเอาท์พุตของวงจรเปรียบเทียบสัญญาณ  $(B_i)$  จะมีค่าเป็นลอจิก "1" ทำให้สวิทช์ไปดทำงาน (ON) และสัญญาณอินพุทจะถูกลบด้วยสัญญาณอ้างอิง และผลลัพธ์ที่ได้จะถูกส่งผ่านไปยังวงจรคูณสองและภาค ต่อไป และสัญญาณดิจิตอลทั้งหมดจะถูกรวมกันโดยวงจรรีจิสเตอร์

รูปที่ 3.3 แสดงโครงสร้างวงจร LogADC แบบไพฟ์โลน์ ซึ่งมีหลักการทำงานเหมือนกับวงจร ADC เชิง เส้นแบบไพฟ์โลน์ และแต่ละภาคของ ADC ประมวลสัญญาณในโดเมนล็อกการิทึม ซึ่งเมื่อเปรียบเทียบ กับวงจร ADC เชิงเส้นแบบไพฟ์โลน์ การลบสัญญาณจะถูกแทนที่ด้วยการหารสัญญาณ (i.e.  $\log_{10}(A) - \log_{10}(B) = \log_{10}(A/B)$ ) หรือการคูณด้วยค่าคงที่ และการคูณสองจะแทนที่ด้วยการยกกำลังสอง (i.e.  $2 \times (\log_{10} A) = \log_{10} (A^2)$ ) ดังนั้นหลักการทำงานของแต่ละภาคของวงจร LogADC สามารถสรุปได้ดังนี้ เริ่มด้วยวงจรเปรียบเทียบสัญญาณจะเปรียบเทียบสัญญาณจินพุต  $(i_{IN})$  กับสัญญาณอ้างอิง  $(I_{REF})$  คือ

รูปที่ 3.2: โครงสร้างวงจร ADC ไพพ์ไลน์แบบเชิงเส้น

ค่ากระแสอินพุตที่ให้ค่าสัญญาณดิจิตอลเอาท์พุตเท่ากับ  $2^{N-1}$  ซึ่งในกรณีที่สัญญาณอินพุตมีค่าน้อยกว่า สัญญาณอ้างอิง สัญญาณเอาท์พุตของวงจรเปรียบเทียบสัญญาณ  $(B_i)$  จะมีค่าเป็นลอจิก "0" ทำให้สวิทช์ ไม่เปิดทำงาน (OFF) และสัญญาณอินพุตจะถูกส่งผ่านไปยังวงจรยกกำลังสองและภาคถัดไป ในกรณีที่ สัญญาณอินพุตมีค่ามากกว่าสัญญาณอ้างอิง สัญญาณเอาท์พุตของวงจรเปรียบเทียบสัญญาณ  $(B_i)$  จะมีค่า เป็นลอจิก "1" ทำให้สวิทช์เปิดทำงาน (ON) และสัญญาณอินพุตจะถูกหารด้วย  $I_{REF}$  หรือคูณด้วย  $1/I_{REF}$  และผลลัพธ์ที่ได้จะถูกส่งผ่านไปยังวงจรยกกำลังสองและภาคต่อไป และสัญญาณดิจิตอลทั้งหมดจะถูกรวม กันโดยวงจรรีจิสเตอร์เหมือนเช่นกับในวงจร ADC เชิงเส้นแบบไพพ์ไลน์

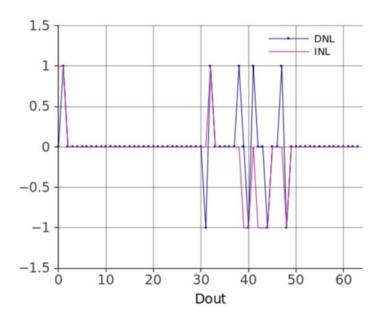

คุณลักษณะความแม่นยำในการแปลงสัญญาณของวงจร ADC สามารถถูกแสดงได้โดยความไม่เป็นเชิง เส้นแบบผลต่าง (Differential non-linearity หรือ DNL) และความไม่เป็นเชิงเส้นแบบผลรวม (Integral non-linearity หรือ INL) ซึ่งสำหรับวงจร LogADC มีค่า DNL และ INL ดังสมการที่ 3.2 และ 3.3 ตาม ลำดับ โดยที่  $\triangle i_k = \ln{(i_{k+1})} - \ln{(i_k)}$  และ  $i_k$  คือค่ากระแสของสัญญาณดิจิตอลเอาท์พุต k และ  $k=0,1,2,\ldots,2^N-1$

$$DNL_k = \frac{\triangle i_{k,REAL} - \triangle i_{k,IDEAL}}{\triangle i_{k,IDEAL}}$$

(3.2)

$$INL_{k} = \frac{\ln(i_{k,REAL}) - \ln(i_{k,IDEAL})}{\triangle i_{k,IDEAL}}$$

(3.3)

ค่าพิสัยพลวัติ (Dynamic range หรือ DR) ของวงจร LogADC คืออัตราส่วนกำลังงานของสัญญาณ อินพุตสูงสุดต่อค่า LSB ที่เล็กที่สุด ( $LSB_{min}$ ) ซึ่งคือผลต่างของค่ากระแสของดิจิตอลเอาท์พุต 1 และ 0 ซึ่ง สามารถแสดงได้ในสมการที่ 3.4

รูปที่ 3.3: โครงสร้างวงจร LogADC แบบไพพ์ไลน์

$$DR = 20 \log_{10} \left( \frac{I_{FS}}{LSB_{min}} \right) = 20 \log_{10} \left( \frac{I_{FS}}{I_{FS} \left( 10^{C \left( \frac{1}{2^{N}} - 1 \right)} 10^{-C} \right)} \right)$$

(3.4)

#### 3.3.2 การออกแบบวงจร LogADC โหมดกระแสแบบไพพ์ไลน์

ในส่วนนี้เราจะ อธิบายการ ออกแบบวงจร LogADC แบบไพพ์ไลน์ในโหมดกระแส สำหรับเพื่อแปลงค่า สัญญาณกระแสเอาท์พุตจากวงจรอ่านค่าสัญญาณอีสเฟตที่ได้กล่าวไว้ในบทที่ 2 ซึ่งให้ค่ากระแสเอาท์พุต สูงสุด 100 nA (i.e.  $I_{FS}=100nA$ ) และต้องการความละเอียดในการแปลงสัญญาณ 8 บิต (N=8) และ  $I_{REF}=I_{FS}\times 10^{2\cdot \left(\frac{2^7}{2^8}-1\right)}=10$ nA ดังนั้นในแต่ละภาคของ LogADC สัญญาณกระแสอินพุต  $i_{IN}$  จะถูก เปรียบเทียบกับ  $I_{REF}$  เพื่อคำนวณค่าสัญญาณดิจิตอลเอาท์พุต ในกรณีที่  $i_{IN} < I_{REF}$  สัญญาณดิจิตอลเอาท์พุตจากวงจรเปรียบเทียบสัญญาณจะมีค่าเป็นลอจิก "0" และสัญญาณอินพุตจะถูกส่งผ่านไปยังวงจร ยกกำลังสองและภาคต่อไป ในกรณีที่  $i_{IN} > I_{REF}$  สัญญาณดิจิตอลเอาท์พุตจะมีค่าเป็นลอจิก "1" และ สัญญาณอินพุตจะถูกหารด้วย  $I_{REF}$  (i.e. หารด้วย 10 หรือคูณด้วย 0.1) และผลลัพธ์ที่ได้จะถูกส่งผ่านไป ยังวงจรยกกำลังสองและภาคต่อไป และสัญญาณดิจิตอลเอาท์พุตของแต่ละภาคจะถูกหน่วงเวลาด้วยรีจีส เตอร์เพื่อรวมเป็นสัญญาณดิจิตอลเอาท์พุต 8 บิตที่สมบูรณ์

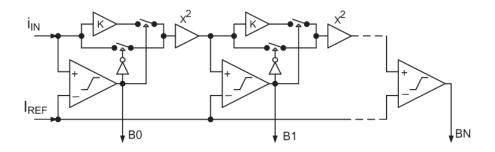

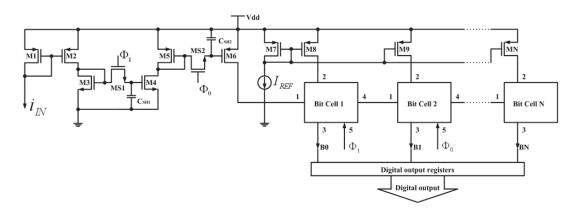

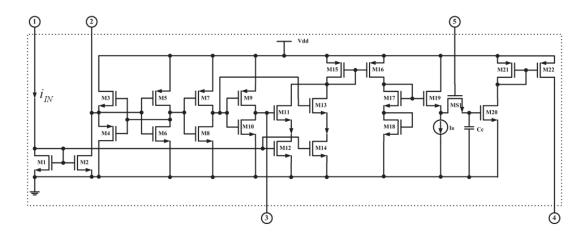

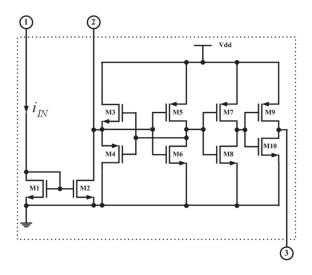

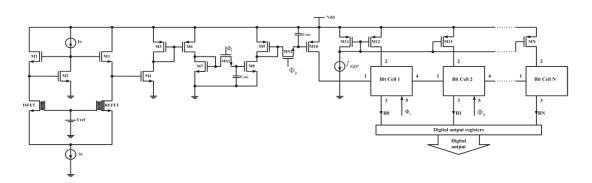

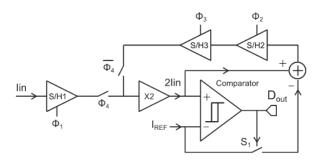

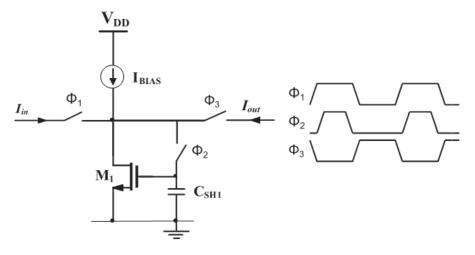

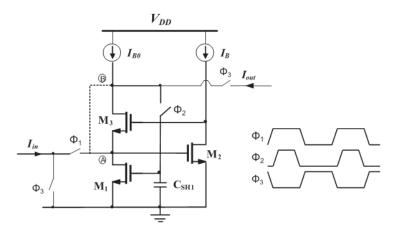

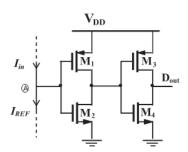

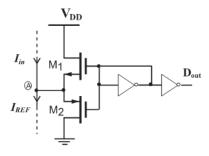

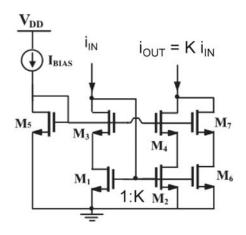

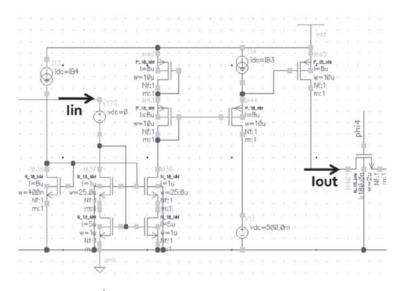

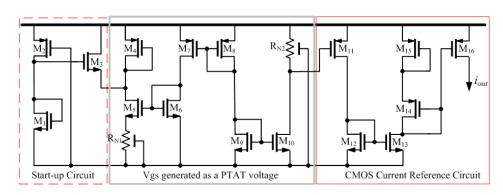

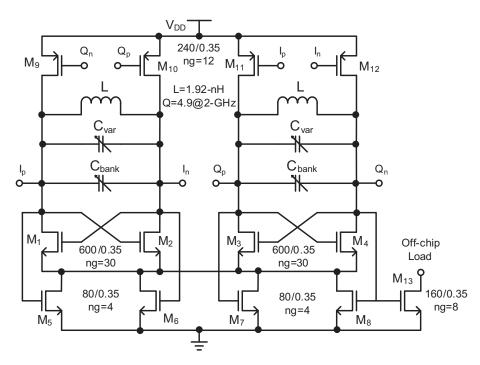

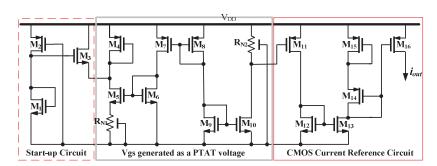

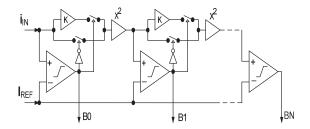

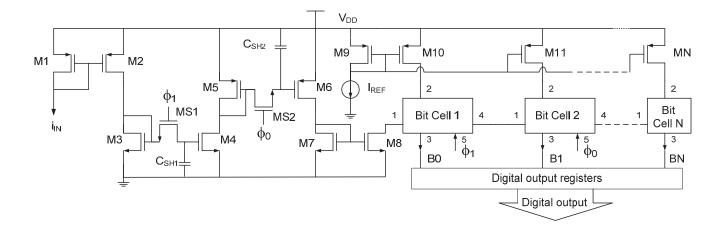

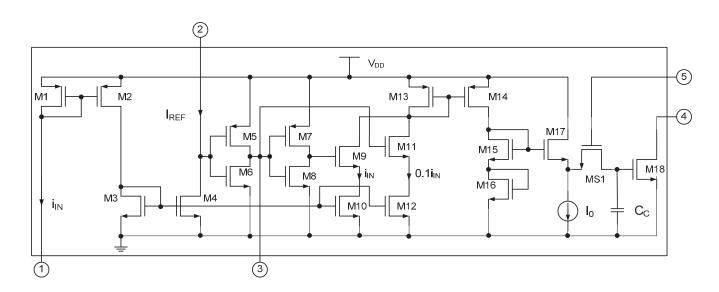

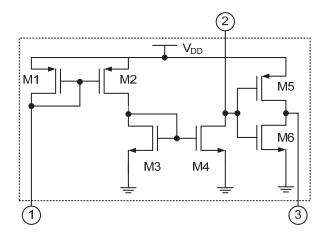

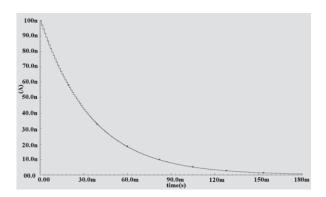

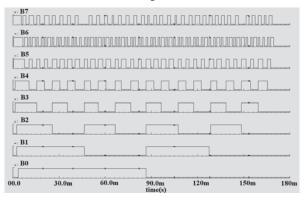

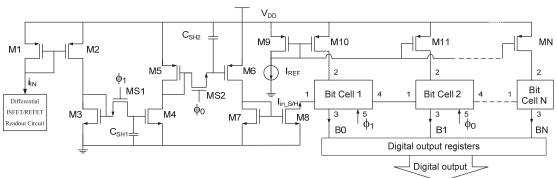

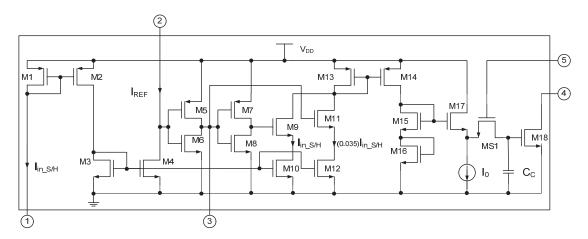

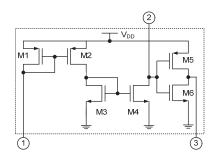

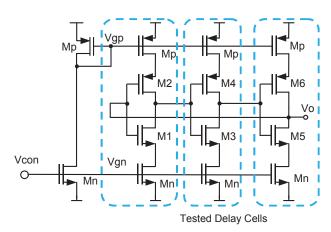

รูปที่ 3.4 แสดงวงจร LogADC ไพพ์ไลน์โหมดกระแส โดยที่มอสเฟต  $M_1-M_6$  มอสเฟตสวิตซ์  $M_{S1}-M_{S2}$  และตัวเก็บประจุ  $C_{SH1}-C_{SH2}$  ทำหน้าที่เป็นวงจรตามและคงค่าสัญญาณ (Sample and Hold: S/H) เพื่อสุ่มสัญญาณกระแสอินพุทส่งไปยังภาคแรกของวงจร LogADC มอสเฟตสวิตซ์  $M_{S1}$  และ  $M_{S2}$  ถูกควบคุมด้วยสัญญาณนาฬิกาที่ไม่ทับซ้อน (Non-overlapping clock signals)  $\phi_1$  และ  $\phi_2$  ตามลำดับ มอสเฟต  $M_7-M_N$  ทำหน้าที่เป็นวงจรสะท้อนกระแสส่งกระแสอ้างอิงส่งไปยังทุกภาคของ LogADC

รูปที่ 3.5 แสดงวงจรในแต่ละภาค (Bit cell) ของ LogADC โดยมีขาที่ 1 เชื่อมต่อกับกระแสอินพุต ขาที่ 2 เชื่อมต่อกับกระแสอ้างอิง ขาที่ 3 คือสัญญาณดิจิตอลเอาท์พุต ขาที่ 4 เป็นขาเอาท์พุตส่งกระแสเอาท์พุต ไปยังภาคถัดไป และขาที่ 5 ต่อกับสัญญาณนาฬิกาควบคุม มอสเฟตทั้งหมดในวงจรถูกไบอัสให้ทำงานใน

รูปที่ 3.4: วงจร LogADC ไพพ์ไลน์โหมดกระแส

ย่านผันกลับอย่างอ่อน มอสเฟต  $M_1-M_2$  ทำหน้าที่เป็นวงจรสะท้อนกระแสรับกระแสเอาท์พุตจากภาค ที่อยู่ข้างหน้า คัดลอกและส่งให้วงจรเปรียบเทียบสัญญาณกระแส  $(M_3-M_8)$  ซึ่งทำหน้าที่เปรียบเทียบ สัญญาณกระแสอินพุทกับกระแสอ้างอิง และให้สัญญาณดิจิตอลเอาท์พุตที่ขา 3 โดยค่าดิจิตอลเอาท์พุตที่ ได้จะใช้ไปควบคุมมอสเฟตสวิตซ์  $M_{11}$  และ  $M_{13}$  เพื่อเลือกว่าจะส่งผ่านกระแสอินพุทที่ผ่านการคูณด้วย 1หรือ 0.1 (i.e. คูณด้วย  $1/I_{REF}$ ) ไปยังวงจรยกกำลังสอง การคูณสัญญาณกระแสอินพุตอาศัยหลักการของ วงจรสะท้อนกระแสโดยใช้ขนาดความกว้างของมอสเฟต  $M_{12}$  และ  $M_{14}$  เป็น 1 และ 0.1 เท่าของขนาด ความกว้างของ  $M_1$  ตามลำดับ ในกรณีที่สัญญาณดิจิตอลเอาท์พุตเป็นลอจิก "1" มอสเฟตสวิตซ์  $M_{13}$  จะ ปิด (OFF) และมอสเฟตสวิตซ์  $M_{11}$  จะเปิด (ON) ส่งผ่านกระแสอินพุทที่คูณด้วย 0.1 และส่งต่อไปยังวงจร ยกกำลังสอง ในกรณีที่สัญญาณดิจิตอลเอาท์พุตเป็นลอจิก "0" มอสเฟตสวิตซ์  $M_{13}$  จะเปิด (ON) และ มอสเฟตสวิตซ์  $M_{11}$  จะปิด (OFF) ส่งผ่านกระแสอินพุทที่คูณด้วย 1 และส่งต่อไปยังวงจรยกกำลังสอง วงจร ยกกำลังสองประกอบด้วยมอสเฟต  $M_{17}-M_{20}$  โดยใช้หลักการทรานส์ลิเนียร์ [23] ซึ่งสามารถแสดงได้ว่า กระแสเอาท์พุตของวงจรที่ขั้วเดรนของ  $M_{20}$  มีค่าเท่ากับค่ายกกำลังสองของกระแสอินพุตหรือ 0.1 เท่า ของกระแสอินพุต หารด้วยกระแสไฟตรง  $I_0$  มอสเฟตสวิทช์  $M_{S1}$  ที่ถูกควบคุมด้วยสัญญาณนาฬิกาและ ตัวเก็บประจุ  $C_C$  ทำหน้าที่คงค่าหรือส่งผ่านกระแสเอาท์พุตไปยังภาคถัดไป ความแม่นยำของวงจรสะท้อน กระแส และวงจรยกกำลังสองมีความสำคัญและส่งผลต่อประสิทธิภาพการทำงานของวงจร LogADC ดัง ้นั้นมอสเฟตทุกตัวจึงถูกเลือกให้มีความยาวช่องทางมาก และภาคสุดท้ายของวงจร LogADC ประกอบด้วย วงจรสะท้อนกระแสและวงจรเปรียบเทียบสัญญาณกระแสดังแสดงในรูปที่ 3.6