# รายงานวิจัยฉบับสมบูรณ์

รหัสแก้ไขความผิดพลาดและการประมวลผลสัญญาณสำหรับ การบันทึกข้อมูลความหนาแน่นสูง

โดย ศาสตราจารย์ ดร.พรชัย ทรัพย์นิธิ

เดือนกันยายน พ.ศ. 2559

# สัญญาเลขที่ RSA568005

# รายงานวิจัยฉบับสมบูรณ์

รหัสแก้ไขความผิดพลาดและการประมวลผลสัญญาณสำหรับ การบันทึกข้อมูลความหนาแน่นสูง

ศาสตราจารย์ ดร.พรชัย ทรัพย์นิธิ สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

สนับสนุนโดยสำนักงานกองทุนสนับสนุนการวิจัยและ ต้นสังกัด

(ความเห็นในรายงานนี้เป็นของผู้วิจัย สกว.และต้นสังกัดไม่จำเป็นต้องเห็นด้วยเสมอไป)

# บทคัดย่อ

Project Code: RSA568005

(รหัสโครงการ)

Project Title : รหัสแก้ไขความผิดพลาดและการประมวลผลสัญญาณสำหรับการบันทึกข้อมูล

ความหนาแน่นสูง

Investigator: ศาสตราจารย์ ดร.พรชัย ทรัพย์นิธิ

สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

E-mail Address: pornchai.su@kmitl.ac.th

Project Period : 15 กันยายน 25556 ถึง 14 กันยายน 2559 (3 ปี)

เทคโนโลยีการบันทึกข้อมูลความหนาแน่นสูงสำหรับอนาคตมีทางเลือกสองทาง คือการ บันทึกเชิงแม่เหล็ก อาทิเช่น การบันทึกแม่เหล็กแนวตั้งขั้นสูง, การบันทึกแม่เหล็กความร้อนช่วย, การบันทึกสื่อแพทเทิรนบิตและ การบันทึกข้อมูลซ้อนทับ ที่ใช้งานในอุปกรณ์ฮาร์ดดิสก์ใดรฟ์ นอกจากนี้ยังมีการบันทึกแบบแฟลชที่ใช้งานในโซลิดสเตทไดรฟ์ การบันทึกเชิงแม่เหล็กได้รับ ผลกระทบจากปรากฏการณ์หลายอย่าง ได้แก่ การเลื่อนทรานซิชันไม่เป็นเชิงเส้น (nonlinear transition shift: NLTS) ความขรุขระอุณหภูมิ thermal asperity) การแทรกสอดระหว่าง สัญลักษณ์ (intersymbol การแทรกสอดระหว่างแทร็ก (inter-track interference: ISI) interference: ITI) รวมทั้งปัญหาเฉพาะในเทคโนโลยีแต่ละประเภท เช่น ผลกระทบจากความร้อน ้ต่อหัวอ่านในการบันทึกแม่เหล็กความร้อนช่วย การเขียนบิตผิดพลาดในการบันทึกสื่อแพทเทิรน บิต เป็นต้น สำหรับการบันทึกแบบแฟลชนั้นได้รับผลกระทบจากสัญญาณรบกวนหลายชนิด เช่น การเก็บรักษาบิต (retention noise) การแทรกสอดระหว่างเซลล์ (inter-cell interference) และการ รบกวนการเขียน-อ่าน (read/write disturb) เป็นต้น สัญญาณรบกวนและความผิดเพี้ยนเหล่านี้ล้วน ้มีผลต่อสมรรถนะของระบบการบันทึกข้อมูลเป็นอย่างมาก ในระบบบันทึกเชิงแม่เหล็ก ขนาดแทร็ก และขนาดบิตที่เล็กลงมีผลทำให้การแทรกสอดระหว่างสัญลักษณ์และการแทรกสอดระหว่างแทร็ก มีระดับที่รุนแรงขึ้น ในขณะที่ระบบการบันทึกแบบแฟลช การบันทึกหลายระดับต่อเซลล์ (multi levels per cell) ทำให้การแทรกสอดระหว่างเซลล์มีค่ามากขึ้น ดังนั้นระดับเอสเอนอาร์ที่ต่ำลงจะมี ผลต่อสมรรถนะของระบบโดยตรง ทำให้มีความจำเป็นที่จะต้องนำเทคนิคการประมวลผลข้อมูลเข้า

มาใช้งาน นอกจากนี้ระดับอัตราบิตผิดพลาดที่ต่ำมากในระดับน้อยกว่า 10<sup>-12</sup> ทำให้ต้องนำรหัส แก้ไขความผิดพลาด (error correction code: ECC) เข้ามาใช้งาน

ในโครงการวิจัยนี้ มีวัตถุประสงค์เพื่อพัฒนาวิธีการการประมวลผลสัญญาณแบบใหม่ และ รหัสแก้ไขความผิดพลาดสำหรับการบันทึกข้อมูล โดยจะทำการออกแบบดีเท็กเตอร์ที่อิงกับกราฟ และเทรลิสสำหรับช่องสัญญาณแบบสองมิติ ข้อดีของการดีเท็กต์แบบกราฟคือใช้จำนวนรอบในการ ทำงานที่ต่ำลง และมีความซับซ้อนแบบเชิงเส้นอีกด้วย สำหรับรหัสแก้ไขความผิดพลาดจะเน้นไปที่ รหัสพาริตี้เช็กความหนาแน่นต่ำหรือรหัสแอลดีพีซีแบบใบนารีและนอนใบนารี ที่ออกแบบด้วย อัลกอริธึม progressive-edge growth (PEG) และมีการถอดรหัสด้วยการจัดเรียงลำดับการอัพเดท ค่าที่แตกต่างจากวิธีดังเดิม โดยจะมีการจำลองสมรรถนะของระบบบันทึกเชิงแม่เหล็กและแบบ แฟลช ท้ายที่สุดจะมีการวิจัยการออกแบบการบันทึกข้อมูลซ้อนทับ

**คำหลัก:** วงจรดีเท็กต์วิเทอร์บิ, แบบจำลองช่องสัญญาณสองมิติ, การบันทึกแม่เหล็กความร้อน ช่วย, การบันทึกสื่อแพทเทิรนบิต, การบันทึกข้อมูลซ้อนทับ, หน่วยความจำโซลิดเสตท, การ ประมวลผลวนกลับ, การอิควอไลซ์เทอร์โบ

## **Abstract**

Project Code: RSA568005

Project Title : รหัสแก้ไขความผิดพลาดและการประมวลผลสัญญาณสำหรับการบันทึกข้อมูล

ความหนาแน่นสูง

Investigator: ศาสตราจารย์ ดร.พรชัย ทรัพย์นิธิ

สถาบันเทคโนโลยีพระจอมเกล้าเจ้าคุณทหารลาดกระบัง

E-mail Address: pornchai.su@kmitl.ac.th

Project Period : 15 กันยายน 25556 ถึง 14 กันยายน 2559 (3 ปี)

The candidates for the next generation of disk drive (HDD) technologies include advanced perpendicular magnetic recording (PMR), heat-assisted magnetic recording (HAMR), bit patterned media (BPM) recording, shingled magnetic writing (SMR) as well as flash-based recording. The first four technologies are based on magnetic recording, while the other relies on the solid-state technology. The magnetic recording is faced with noise and distortion which include media noise, nonlinear transition shift (NLTS), thermal asperity, thermal response, intersymbol interference (ISI), inter-track interference (ITI) as well as system-specific issues such as heating gradients in HAMR, write errors in BPM as well as multiple shingle track pitch in SMR, all of which degrade the system reliability. For the flash-based memory, there are several types of noise sources including retention process, inter-cell interference (ICI), background pattern noise, and read/program disturb. Such noise sources reduce the storage reliability of magnetic and flash memory significantly. The continuous bit cost reduction of both types of devices mainly relies on aggressive technology scaling, which, however, further deteriorates the storage reliability. In magnetic recording, the bit size and track pitch are continually reduced causing the ISI, ITI issues, while for flash-based recording, multi levels per cell lead to increased ICI issues. In addition, the signal-to-noise ratio (SNR) is further decreased resulting in degraded bit error rate (BER). Signal processing is required to tackle the ISI, ITI and ICI issues. The typical storage reliability requirement is that non-recoverable BER must be

below 10<sup>-15</sup>. Such stringent BER requirement makes error correction code (ECC) techniques mandatory to guarantee storage reliability. Different ECC techniques are required in different types of magnetic and flash memory. Turbo equalization between the detectors and ECC decoders can be used to further increase the system performance.

In this project, we develop the novel advanced signal processing and coding schemes for memory storage. Specifically, given a two-dimensional channel matrix, representing the ISI and ITI, we design the myriad detector types such as trellis-based and graph-based detectors. Benefits of such a structure include the SNR gains after fewer iterations, linear complexity and significant mitigation reduction of inter-track interference (ITI) and other distortions on the write side such as nonlinear transition shift (NLTS) and on the read side such as thermal asperity (TA), thermal response (TR) and dual peak-to-peak readback amplitude. For the ECC, binary and non-binary low-density parity-check (LDPC) codes based on progressive-edge growth (PEG) algorithm and the product code structure will be beneficial. For the decoders, the layered-scheduling and mixed-scheduling will be designed and proposed for magnetic-based and flash-based memory storage.

**Keywords:** Viterbi detector, two-dimensional channel model, heat-assisted magnetic recording (HAMR), bit patterned media (BPM), shingled magnetic writing (SMR), solid-state memory, iterative processing, turbo equalization

# **Executive Summary**

Data Storage technology is an integral part of the digital economy, particularly, with the projection of ever increasing amount of data stored at each instants. From personal storage to cloud-based memory, both magnetic and flash recording technologies need to satisfy the insatiable storage demand of the public and the enterprise. Physical layer technology such as advanced signal processing and coding schemes are essential to the high-density magnetic recording beyond terabits per square and the multi-leveled cells (MLC) in solid-state memory. As Thailand is one of the largest manufacturers and a powerhouse in memory storage particularly in magnetic storage, high-quality research is important to raise the human capability as well as producing technology path from within the country. This research project was initiated to address these requirements in developing novel signal processing techniques appropriate for multi-tracking system and powerful error correction codes for both magnetic and flash memory. At the conclusion of this research project, all the research results were published in 3 high-quality journals and presented at 3 international conferences. Three doctoral and one master students graduated in this area of research. In addition, the researcher was invited to host a special session in data storage technology at the APSIPA 2014 conference and invited to be a technical committee member at the prestigious ICC 2014 conference in the data storage track.

## Content

|                                                                                | Page |

|--------------------------------------------------------------------------------|------|

| บทคัดย่อ                                                                       | ļ    |

| Abstract                                                                       | II   |

| Executive Summary                                                              | ٧    |

| Content                                                                        | V    |

| List of Tables                                                                 | V    |

| List of Figures                                                                | VIII |

| 1. Introduction                                                                | 1    |

| 1.1 Introduction to the research problem and its significance                  | 1    |

| 1.2 Objectives                                                                 | 2    |

| 2. Theory                                                                      | 3    |

| 2.1 Candidates for future magnetic recording system technology                 | 3    |

| 2.2 Two-dimensional recording channel models                                   | 6    |

| 2.2.1 Partial-response maximum likelihood (PRML) detector                      | 8    |

| 2.2.2 Modified Viterbi detectors for inter-track interference (ITI) mitigation | 11   |

| 2.2.3 Graph-Based Detector                                                     | 13   |

| 2.2.4 Mutual Information                                                       | 15   |

| 2.3 Background on Low-density parity-check (LDPC) codes                        | 15   |

| 2.3.1 Progressive-edge growth (PEG) algorithm                                  | 15   |

| 2.3.2 Algorithms for LDPC decoder                                              | 18   |

| 2.3.3 Layered belief propagation                                               | 20   |

| 2.3.4 Shuffled belief propagation (SBP)                                        | 21   |

| 2.4 Heat-assisted magnetic recording (HAMR) systems                            | 22   |

| 2.4.1. Transition center $(x_0)$ and transition parameter $a$                  | 24   |

| 2.4.2. The Generation of the HAMR readback signal                              | 26   |

| 2.5 Flash recording channels                                                   | 27   |

| 3 Methodology                                                                  | 31   |

| 4. Results and Discussions                                    |    |

|---------------------------------------------------------------|----|

| 4.1 Heat-assisted magnetic recording systems                  | 33 |

| 4.1.1 Simulation of HAMR readback signals                     | 33 |

| 4.1.2. HAMR System                                            | 37 |

| 4.1.3. Target and Equalizer Design                            | 38 |

| 4.2 Detectors for two-dimensional recording channels          | 42 |

| 4.2.1 Proposed 2-D graph-based detector (M1)                  | 42 |

| 4.2.2. Proposed 2-D graph-based detector (M2)                 | 43 |

| 4.2.3 Simulation Results and Discussions                      | 44 |

| 4.3 LDPC decoder with mixed-schedulings                       | 47 |

| 4.3.1 Reliability of Variable Nodes in Serial Scheduling      | 47 |

| 4.3.2. Mixed Scheduling for Belief-Propagation Algorithm      | 50 |

| 4.3.3 Implementation                                          | 50 |

| 4.3.4 Simulation Results                                      | 51 |

| 4.4 Design of binary and non-binary LDPC codes based on       | 55 |

| progressive-edge growth (PEG) algorithm and the product codes |    |

| 4.4.1. Construction of QC-LDPC Codes Based on PEG Algorithm   | 55 |

| 4.4.2. PEG-QC-LDPC codes with maximized girth property        | 57 |

| 4.4.3. Simulation Results                                     | 59 |

| 4.5 Flash Storage                                             | 62 |

| 4.5.1 Simulation results of flash channels                    | 62 |

| 4.5.2 Soft decoding of flash channels                         | 66 |

| 4.6 Shingled magnetic recording (SMR)                         | 72 |

| 4.6.1 Conventional Perpendicular Magnetic Recording           | 72 |

| 4.6.2 Experiment structure and data analysis                  | 74 |

| 5. Conclusions                                                | 78 |

| 6. Project outputs                                            | 80 |

| References                                                    | 82 |

| Annandix A Publications                                       | 97 |

## **List of Tables**

| Table                                                                 | Page |

|-----------------------------------------------------------------------|------|

| 4.1 HAMR System Parameters                                            | 33   |

| 4.2 PEG-QC Algorithm                                                  | 56   |

| 4.3 PEG-QC-MAX Algorithm                                              | 57   |

| 4.4 Local girth property for PEG, PEG-QC and proposed PEG-QC codes at |      |

| the block size of 1944                                                |      |

| 4.5 Local girth property for PEG, PEG-QC and proposed PEG-QC codes at | 60   |

| the block size of 4608                                                |      |

# List of Figures

| Figure                                                                         | Page |

|--------------------------------------------------------------------------------|------|

| 2.1 Heat-assisted magnetic recording (HAMR)                                    | 4    |

| 2.2 Comparison between conventional continuous domain recording and            | 4    |

| patterned media recording system                                               |      |

| 2.3 Two-dimensional magnetic recording (TDMR) system                           | 5    |

| 2.4 Overall encoding/decoding of TDMR system                                   | 6    |

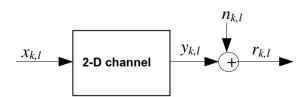

| 2.5 The discrete-time channel model of typical PMS recording system            | 6    |

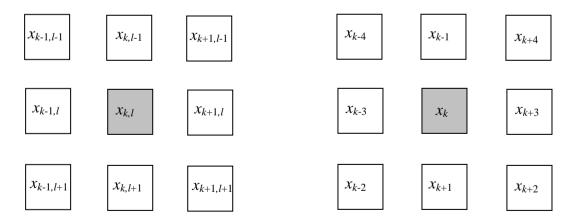

| 2.6 A 3x3 bit configuration                                                    | 7    |

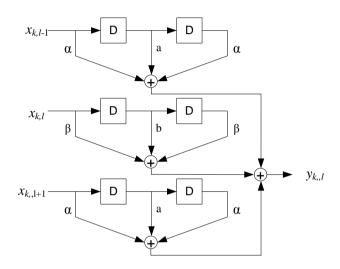

| 2.7 The 2-D channel model with delay blocks                                    | 8    |

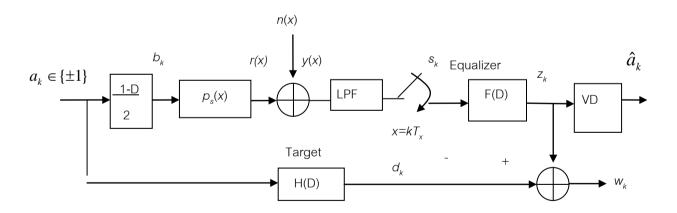

| 2.8 Block diagram of PRML detector                                             | 8    |

| 2.9 The trellis structure of the Viterbi detector for the channel with two ISI | 10   |

| 2.10 Trellis diagrams for modified Viterbi detectors with 1 branch, 3 branches | 12   |

| and 9 branches two connected states                                            |      |

| 2.11 The factor graph of the 2-D channel in (3)                                | 13   |

| 2.12 A tree diagram [25] expanding from the variable node $v_i$ with a depth-/ | 17   |

| 2.13 An example of a PEG-QC-LDPC code with the circulant size of 4×4           | 18   |

| 2.14 An example of a Tanner graph                                              | 19   |

| 2.15 Illustration of procedures for LBP strategy                               | 21   |

| 2.16 Illustration of procedures for SBP strategy                               | 22   |

| 2.17 Structure of flash memory blocks                                          | 27   |

| 2.18 Flash memory channel                                                      | 28   |

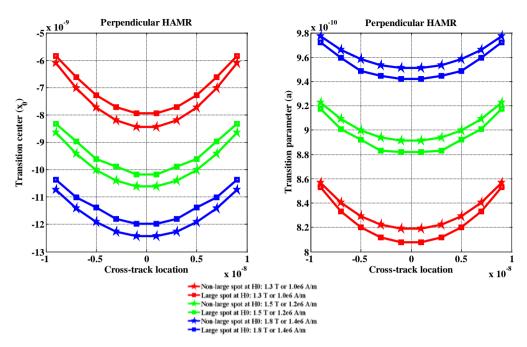

| 4.1 Transition center and parameter with various $H_{\it c}$ dependencies on   | 34   |

| Temperatures                                                                   |      |

| 4.2 Transition center and parameter with various $M_r$ dependencies on         | 34   |

| Temperature                                                                    |      |

| 4.3 Transition center and parameter with various head fields                   | 35   |

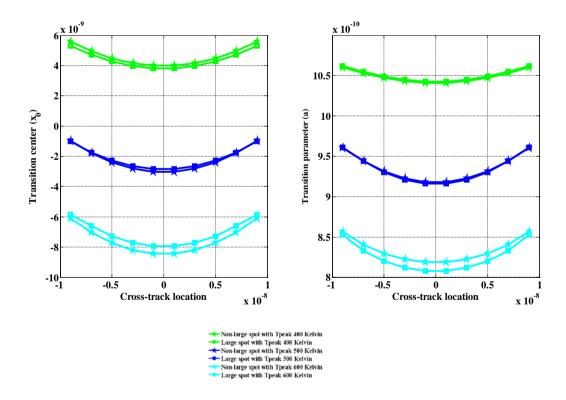

| 4.4 Transition center and parameter with various peak temperatures             | 35   |

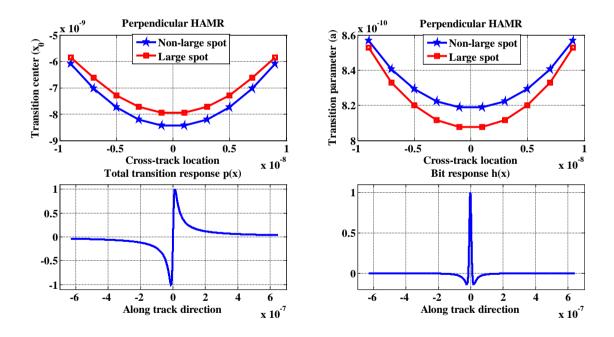

| 4.5 Transition center, parameter, response and bit response                    | 36   |

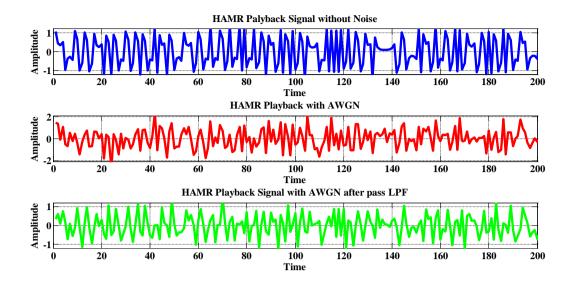

| 4.6 Playback signal with and without AWGN                                      | 37   |

| 4.7 The HAMR system with target-shaping equalization                           | 38   |

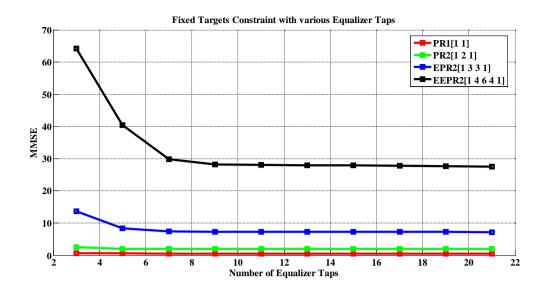

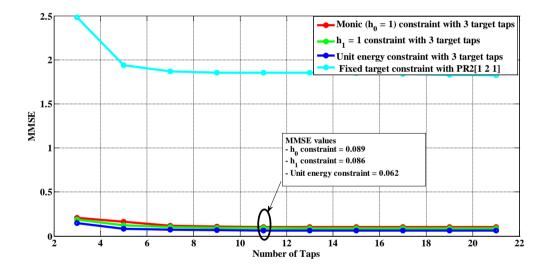

| 4.8 MMSE of fixed-target constraint with various equalizer taps                | 39   |

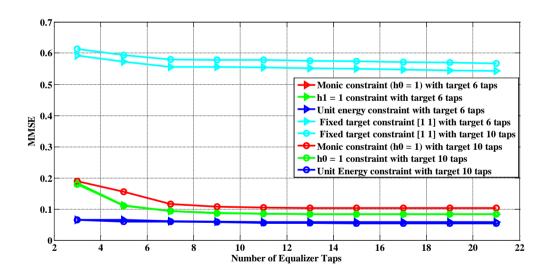

| 4.9 MMSE of various targets constraint using 6 and 10 target taps              | 39   |

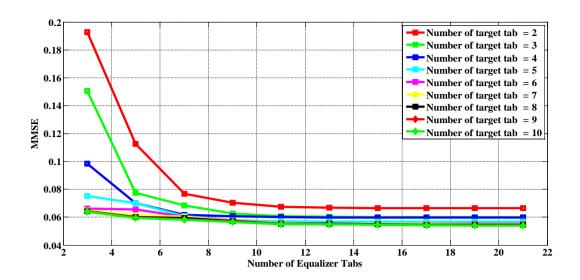

| 4.10 | MMSE of unit-energy constraint equalizers                                        | 40 |

|------|----------------------------------------------------------------------------------|----|

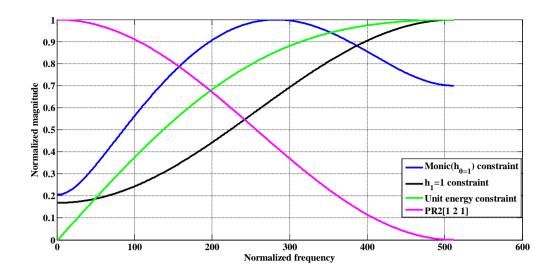

| 4.11 | MMSE of various constraints using 3-tap targets with 11-tap equalizer            | 40 |

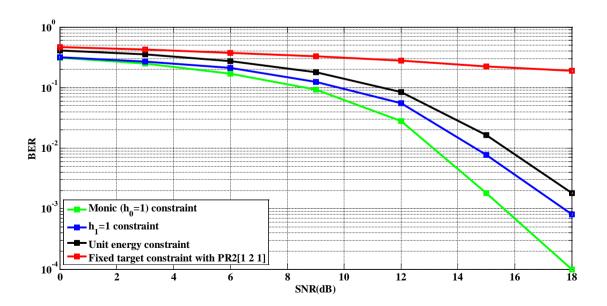

| 4.12 | Frequency responses of GPR targets versus fixed-target (PR2)                     | 41 |

| 4.13 | Bit error rates (BER) of the HAMR system                                         | 41 |

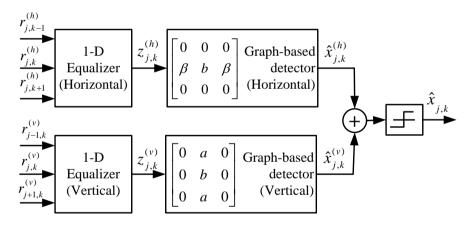

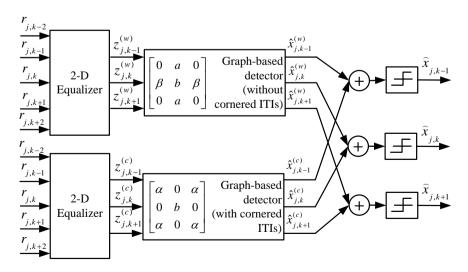

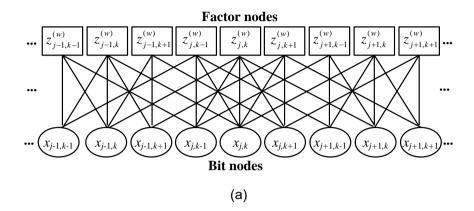

| 4.14 | Block diagram of the proposed 2-D equalizers and 2-D graph detector (M1)         | 42 |

| 4.15 | The factor graphs of the (a) horizontal channel and (b) vertical channel         | 42 |

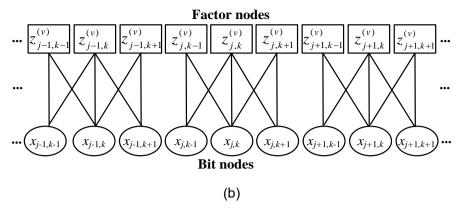

| 4.16 | Block diagram for the 2-D graph-based detector (M2)                              | 43 |

| 4.17 | The factor graph of the 2-D graph-based detector (M2) (a) without cornered       | 44 |

|      | ITIs and (b) with cornered it is                                                 |    |

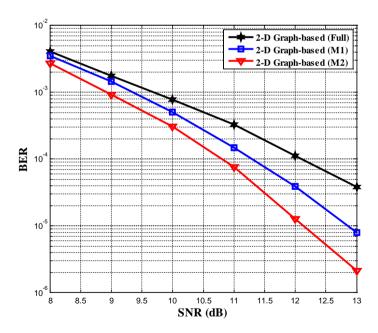

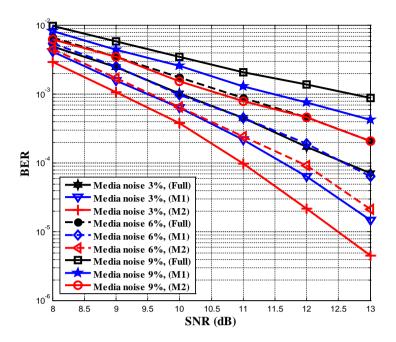

| 4.18 | Performance of the 2-D graph-based detector (Full), 2-D graph-based              | 45 |

|      | detector (M1) and (M2) of the 2-D channel in (4.1)                               |    |

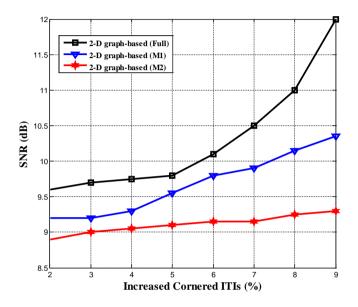

| 4.19 | Performance comparison of 2-D graph-based detectors (Full), (M1) and             | 46 |

|      | (M2) with increased coefficients of cornered ITIs at the BER of 10 <sup>-4</sup> |    |

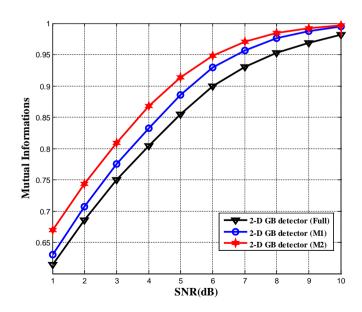

| 4.20 | The mutual information of the three 2-D graph-based detectors                    | 46 |

| 4.21 | Performance comparison of the three 2-D graph-based detectors in the             | 47 |

|      | BPMR system with various media noise levels                                      |    |

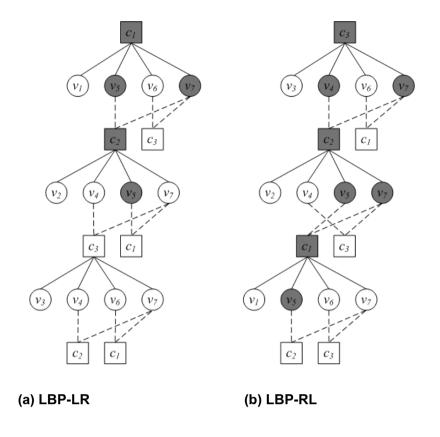

| 4.22 | Procedures of update information for LBP                                         | 49 |

| 4.23 | The reliability of variable nodes $L(Q_i)$                                       | 49 |

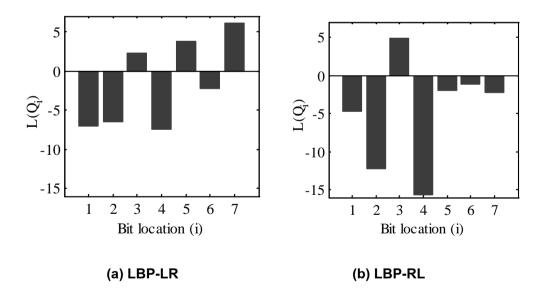

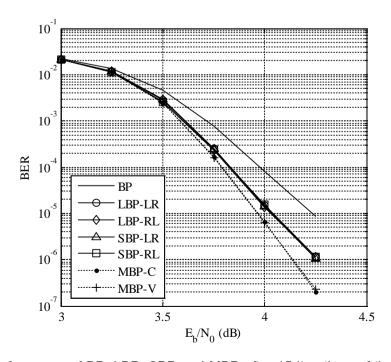

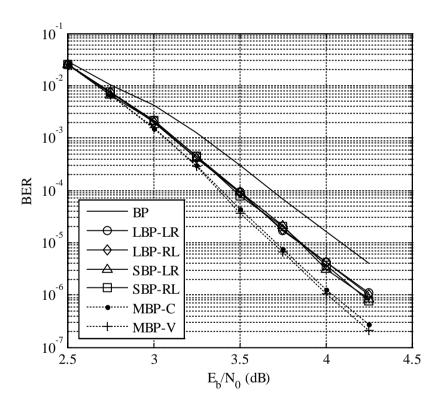

| 4.24 | Performance of BP, LBP, SBP and MBP after 15 iterations of the block             | 51 |

|      | size of 4064 and the code rate is 0.88                                           |    |

| 4.25 | Performance of BP, LBP, SBP and MBP after 15 iterations of the block             | 52 |

|      | size of 1940 and the code rate is 0.8                                            |    |

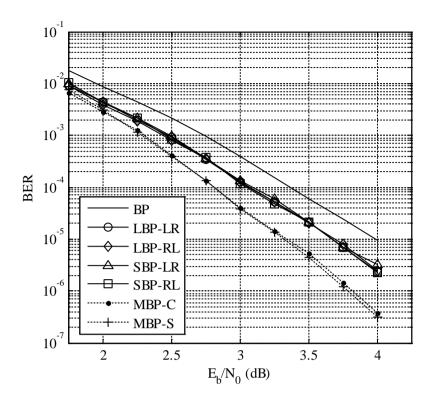

| 4.26 | Performance of BP, LBP, SBP and MBP after 15 iterations of the block             | 53 |

|      | size of 1930 and the code rate is 0.55                                           |    |

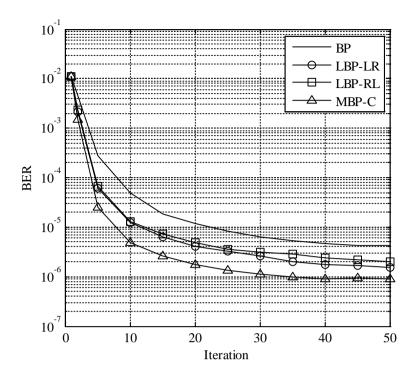

| 4.27 | Performance of BP, LBP and MBP at various iterations for the block size          | 54 |

|      | of 1940, code rate of 0.8 and SNR = 3.9 dB                                       |    |

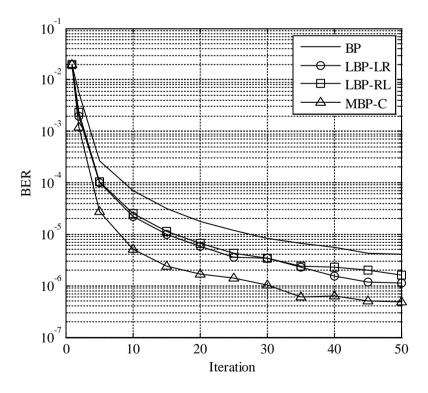

| 4.28 | Performance of BP, LBP and MBP at various iterations for the block size          | 54 |

|      | of 1930, code rate of 0.55 and SNR = 3.7 dB                                      |    |

| 4.29 | An example of a circulant constraint with matrix size of 4×4                     | 56 |

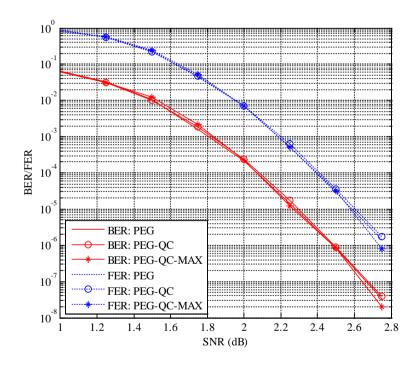

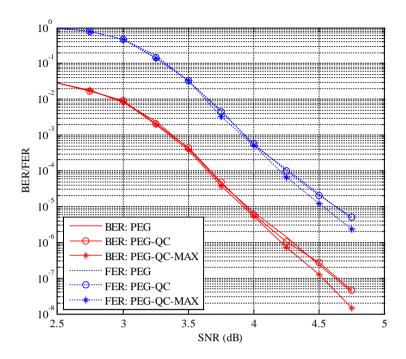

| 4.30 | Performance of PEG, PEG-QC and PEG-QC-MAX codes with block size                  | 61 |

|      | of 1944 bits and the code rate of 1/2 after 25 iterations                        |    |

| 4.31 | Performance of PEG, PEG-QC and PEG-QC-MAX codes with block size                  | 62 |

|      | of 1944 bits and the code rate of 5/6 after 25 iterations                        |    |

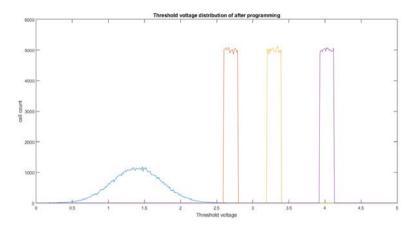

| 4.32 | Distribution of the Erase state and three Program states                         | 63 |

| 4.33 | Distribution of RTN noise with 1000 times of erase and programming           | 63 |

|------|------------------------------------------------------------------------------|----|

| 4.34 | Distribution of RTN noise with 10,000 times of erase and programming         | 64 |

| 4.35 | Distribution of voltages after RTN noise with 1,000 times of erase and       | 64 |

|      | programming                                                                  |    |

| 4.36 | Distribution of voltages after RTN noise with 10,000 times of erase and      | 65 |

|      | Programming                                                                  |    |

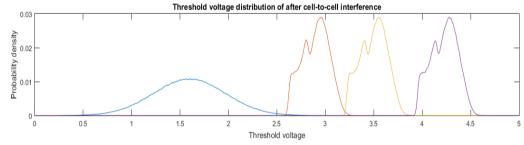

| 4.37 | Distribution of voltages after cell-to-cell interference with $s = 1.5$      | 65 |

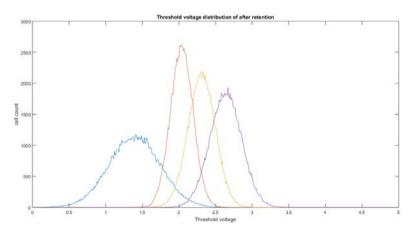

| 4.38 | Distribution of voltages after retention noise of 10 years ( $N = 10,000$ )  | 66 |

| 4.39 | Distribution of voltages after retention noise of 10 years ( $N = 100,000$ ) | 66 |

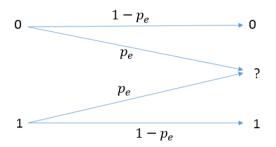

| 4.40 | Binary erasure channels                                                      | 67 |

| 4.41 | An example of a parity-check matrix                                          | 67 |

| 4.42 | The corresponding Tanner graph of Fig. 4.41                                  | 67 |

| 4.43 | The check node connection                                                    | 68 |

| 4.44 | The probability that each incoming branch is erasure                         | 68 |

| 4.45 | The check node connection                                                    | 69 |

| 4.46 | The probability of correct bit node                                          | 69 |

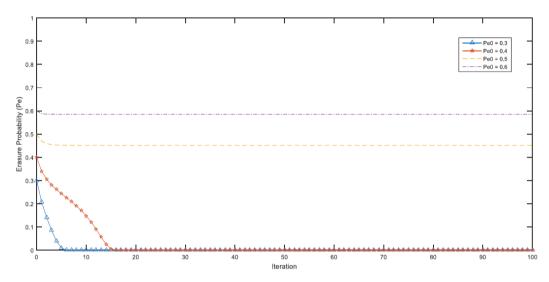

| 4.47 | The probability of erasure correction as various iterations                  | 70 |

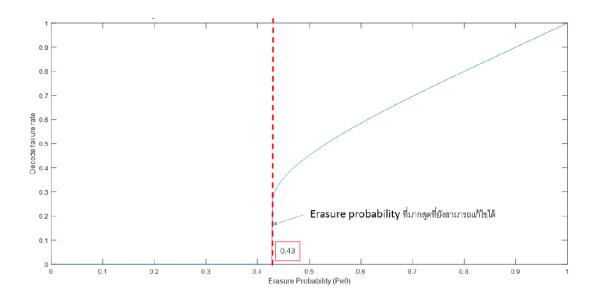

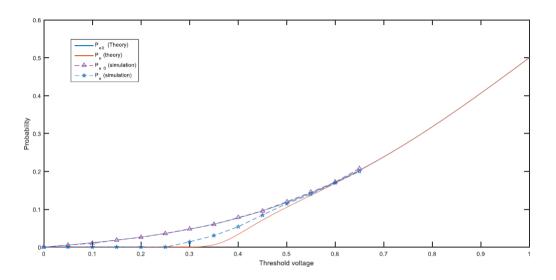

| 4.48 | The decoder failure rate $(P_{^{\prime}e} \uparrow)$ and $P_{e0}$            | 71 |

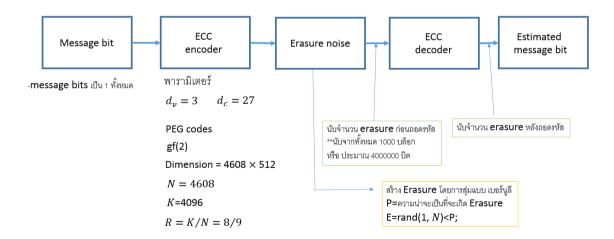

| 4.49 | Block diagram of the simulation setup                                        | 71 |

| 4.50 | Decoding failure rate for finite-length codewords                            | 72 |

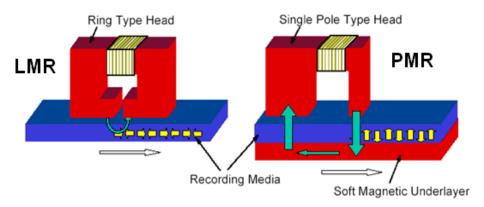

| 4.51 | LMR vs PMR basic head design                                                 | 73 |

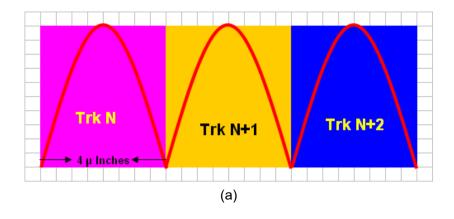

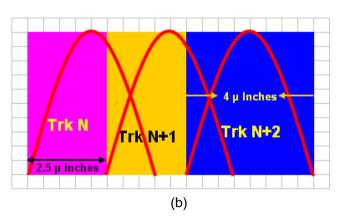

| 4.52 | An understanding of (a) the conventional PMR and (b) SMR track profile       | 74 |

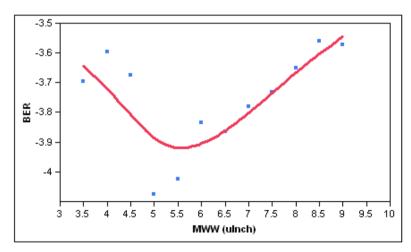

| 4.53 | BER performance against MWW of shingled write recording                      | 75 |

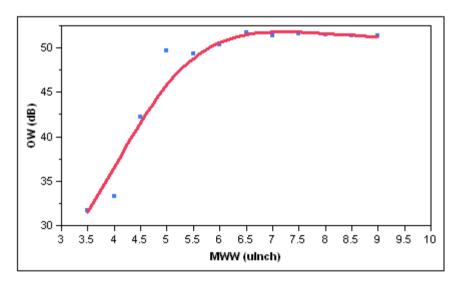

| 4.54 | Reverse Overwrite (ReOW) performance against MWW on shingled                 | 76 |

|      | write recording                                                              |    |

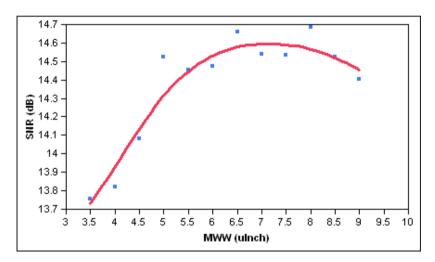

| 4.55 | SNR performance against MWW on shingled write recording                      | 77 |

## 1. Introduction

### 1.1 Introduction to the research problem and its significance

The candidates for the next generation of disk drive (HDD) technologies include advanced perpendicular magnetic recording (PMR), heat-assisted magnetic recording (HAMR), bit patterned media (BPM) recording, shingled magnetic writing (SMR) as well as flash-based recording. The first four technologies are based on magnetic recording, while the other relies on the solid-state technology. The magnetic recording is faced with noise and distortion which include media noise, nonlinear transition shift (NLTS), thermal asperity, thermal response, inter-symbol interference (ISI), inter-track interference (ITI) as well as system-specific issues such as heating gradients in HAMR, write errors in BPM as well as multiple shingle track pitch in SMR, all of which degrade the system reliability. For the flash-based memory, there are several types of noise sources including retention process, inter-cell interference (ICI), background pattern noise, and read/program disturb. Such noise sources reduce the storage reliability of magnetic and flash memory significantly. The continuous bit cost reduction of both types of devices mainly relies on aggressive technology scaling, which, however, further deteriorates the storage reliability. In magnetic recording, the bit size and track pitch are continually reduced causing the ISI, ITI issues, while for flash-based recording, multi levels per cell lead to increased ICI issues. In addition, the signal-to-noise ratio (SNR) is further decreased resulting in degraded bit error rate (BER). Signal processing is required to tackle the ISI, ITI and ICI issues.

Current channel detectors such as Viterbi detector, often known as partial-response maximum likelihood (PRML) detector, are designed to mitigate the ISI rather than ITI. For high-density magnetic recording, particularly, for BPM and TDMR, the ITI needs to be considered. For 2-D interference, the implementation of a 2-D Viterbi detector is impractical due to excessive complexity with exponential complexity as a function of channel lengths. Efforts have been made on reduced-complexity approaches. One such approach is "modified Viterbi detector" which handles ITI by using multiple parallel branches entering and leaving a single state in the trellis. Alternatively, a graph-based structure, which has previously been used as an LDPC decoder, can be designed as a channel detector to mitigate ISI and ITI. The complexity is linear as a function of channel lengths. The structure itself allows SNR gain from running the detector with more iterations

even when the LDPC code is not employed.

The typical storage reliability requirement is that non-recoverable BER must not exceed 10<sup>-15</sup>. Such stringent BER requirement makes error correction code (ECC) techniques mandatory to guarantee storage reliability. Different ECC techniques are required in different types of magnetic and flash memory. Turbo equalization between the detectors and ECC decoders can be used to further increase the system performance.

In this project, we intend to develop the novel advanced signal processing and coding schemes for memory storage. Specifically, given a two-dimensional channel matrix, representing the ISI and ITI, we design the myriad detector types such as trellis-based and graph-based detectors. Benefits of such a structure include the SNR gains after fewer iterations, linear complexity and significant mitigation reduction of inter-track interference (ITI) and other distortions on the write side such as nonlinear transition shift (NLTS) and on the read side such as thermal asperity (TA), thermal response (TR) and dual peak-to-peak readback amplitude. For the ECC, binary and non-binary low-density parity-check (LDPC) codes based on progressive-edge growth (PEG) algorithm and the product code structure will be beneficial. For the decoders, the layered-scheduling and mixed-scheduling will be designed and proposed for magnetic-based and flash-based memory storage.

### 1.2 Objectives

- Design detectors for one-dimensional recording channels in advanced perpendicular magnetic recording (PMR) and heat-assisted magnetic recording (HAMR).

- Design detectors for two-dimensional recording channels in bit patterned media (BPM), shingled recording (SMR).

- 3. Develop the LDPC decoder with mixed-schedulings.

- 4. Design binary and non-binary LDPC codes based on progressive-edge growth (PEG) algorithm and the product codes.

- 5. Investigate the flash-based recording channels and design soft-decisioned detector.

- 6. Perform the experiments and make a trade-off study in shingled magnetic recording (SMR).

## 2. Theory

### 2.1 Candidates for future magnetic recording system technology

At present, the areal density achieved for commercial purpose is estimated at around 800-900 Gbits/in<sup>2</sup>. To design and plan for the next-generation high-density magnetic storage systems, the areal density at the level of over 1 Tb/in<sup>2</sup> (terabits per square inch) has been experimented and prototyped and it is envisioned that the level of 10 Tb/in<sup>2</sup> will be achieved. To increase the areal density, for magnetic recording, two parameters which need to be reduced are bit per inch (BPI) and track per inch (TPI), while for flash-based recording system; the number of bits per cell needs to be increased. Increasing these parameters lead to a decrease of signal-to-noise ratio (SNR), hence, the performance will degrade. For magnetic recording, at present, four candidate technologies are under consideration for the near future. They include advanced perpendicular recording, heat-assisted magnetic recording (HAMR) [1-2], bit patterned media (BPM) [3-5] and, recently proposed, shingled writing and two-dimensional magnetic recording (TDMR) [6].

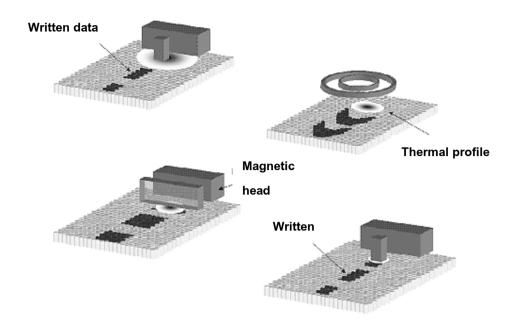

HAMR achieves the balance by allowing high anisotropy media to be written by heating the media during the writing process (e.g., by laser light) to temporarily lower the anisotropy, hence, lower BPI is obtained [1]. HAMR employs a continuous domain writing approach. The image of HAMR is shown in Fig. 2.1.

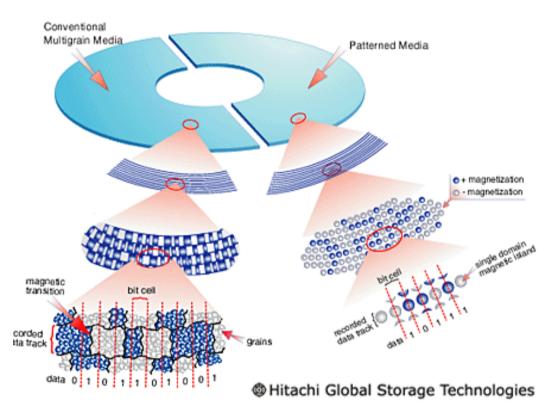

On the other hand, BPM writes data on single domain magnetic island (a few grains); hence, discrete writing is used [2]. As shown in Fig. 2.2, in conventional recording, the information is stored at the transition between magnetic directions, resulting in a continuous region. The aerial density is increased by reducing the bit cell; hence, fewer magnetic particles are contained, causing lower response and the instability of the magnetic field. This effect is often known as "superparamagnetic effect". In PMS, however, each bit is recorded on an ordered array of highly uniform islands on a track of the magnetic film and each recorded bit is represented by a single-domain magnetic island and each island includes a single magnetic grain to achieve high density and stability [2].

Fig. 2.1. Heat-assisted magnetic recording (HAMR).

**Fig. 2.2.** Comparison between conventional continuous domain recording and patterned media recording system.

Moreover, the non-magnetic boundaries between two adjacent bit islands can reduce the transition noise problem, which is one of the serious noises in the conventional continues magnetic media.

In PMS, the distances between islands in along-track and cross-track directions can be reduced to achieve the ultra-high aerial density. And as the read head senses the magnetization, the resulting readback signal is corrupted by a two-dimensional (2D) interference that consists of inter-symbol interference (ISI) and inter-track interference (ITI) [3]-[5], which is one of the main limitations for PMS since it degrades the performance of the data recovery channel.

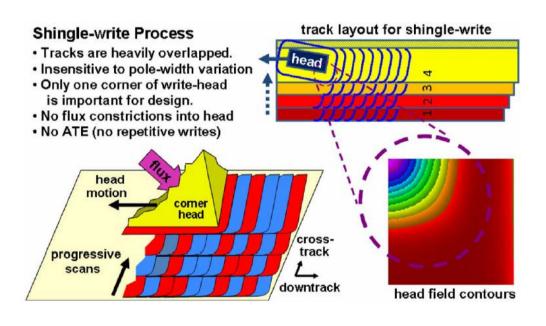

For TDMR, shingled writing is envisioned, whereby the write head writes from a corner only. In addition, written tracks partially overlap the previous ones [7] as shown in Fig. 2.3, hence, higher track density is achieved. For all of these proposed alternatives, as the read head senses the magnetization, the resulting readback signal is corrupted by a two-dimensional (2D) interference that consists of inter-symbol interference (ISI) and intertrack interference (ITI).

Fig. 2.3. Two-dimensional magnetic recording (TDMR) system [7].

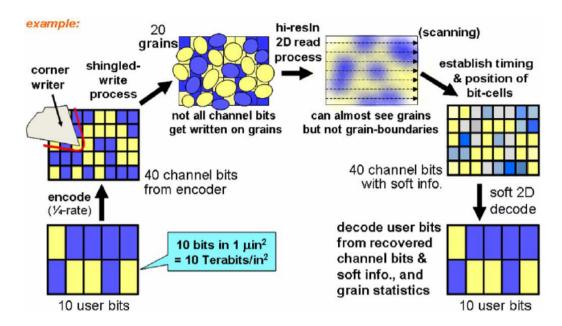

In Fig. 2.4, overall encoding/decoding blocks of the TDMR system are shown. The signal processing and coding are drastically different HAMR and BPM system.

Fig. 2.4. Overall encoding/decoding of TDMR system [7].

The main difference lies in low code rates and ambiguity of the grain boundaries. On the read side, two-dimensional signal processing is required for a 2-D channel model.

#### 2.2 Two-dimensional recording channel models

The 2-D channel model may be obtained from a single read head or multiple read heads. For a single head, a read head detects the signal mainly from the track under it together with some fractions from the above and below tracks [8]. The 2-D readback data can be obtained from a single head scanning a number of tracks, storing in a buffer and releasing the signal to the detector. For multiple read heads, the readback signal from multiple tracks is obtained. The 2-D channel model encompasses the effects from center track and adjacent tracks.

Fig. 2.5. The discrete-time channel model of typical PMS recording system.

A typical discrete-time channel model of 2-D recording system is illustrated in Fig. 2.5. In this model, the data bit at time k along the  $l^{th}$  track,  $x_{k,l}$ , is recorded on the media. The obtained readback signal  $r_{k,l}$  is expressed as

$$r_{k,l} = y_{k,l} + n_{k,l}, (2.1)$$

$$= \sum_{n} \sum_{m} h_{n,m} x_{k-n,l-m} + n_{k,l}$$

(2.2)

where  $h_{n,m}$ 's are the 2-D channel response coefficients and  $n_{k,l}$  is assumed to be additive white Gaussian noise (AWGN) [8]. Without the track misregistration (TMR), a discrete-time 3x3 symmetric channel response matrix **H** [8], [12], in the form of

$$\mathbf{H} = \begin{pmatrix} h_{k-1,l-1} & h_{k,l-1} & h_{k+1,l-1} \\ h_{k-1,l} & h_{k,l} & h_{k+1,l} \\ h_{k-1,l+1} & h_{k,l+1} & h_{k+1,l+1} \end{pmatrix} = \begin{pmatrix} \gamma & a & \gamma \\ \eta & b & \eta \\ \gamma & a & \gamma \end{pmatrix}$$

(2.3)

where b, a,  $\eta$  and  $\gamma$  are the channel coefficients, is a possible channel model among those in [3], [8].

Consider the 3x3 channel model in Fig. 2.6,

Fig. 2.6. A 3x3 bit configuration.

the readback signal in (2.2) can be rewritten as

$$r_k = bx_k + \eta(x_{k-3} + x_{k+3}) + a(x_{k-1} + x_{k+1}) + \gamma(x_{k-4} + x_{k-2} + x_{k+4} + x_{k+2}) + n_k.$$

(2.4)

The first four terms correspond to the noiseless channel output,  $y_{k,l}$ , in (1). The readback signal is corrupted by the ISI (second term), ITI (third and fourth terms) and noise (last term), hence, the challenge is to recover stored bit  $x_{k,l}$  in the environment with such distortions. Based on (2.4), the PMS readback channel can be modeled using the delay blocks as shown in Fig. 2.7

Fig. 2.7. The 2-D channel model with delay blocks.

#### 2.2.1 Partial-response maximum likelihood (PRML) detector

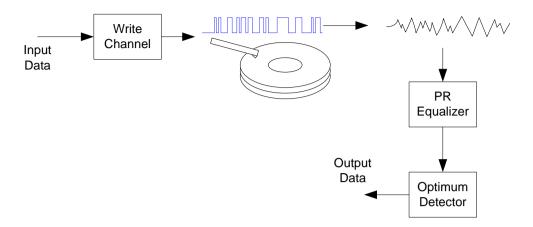

Like a communications channel, the magnetic recording system uses the optimum detection method for the data recovery system. The optimum detection method is based on the maximum-likelihood criterion for detecting sequence of symbols; also known as maximum-likelihood sequence detection (MLSD). It minimizes the probability of error for a received bit sequence [13]. An efficient algorithm for implementing MLSD is the Viterbi algorithm (VA). Although the computational efficiency of the VA is up to the implementation of MLSD, its complexity increases exponentially depending on the span of the ISI. In such cases, the complexity of MLSD needs to be reduced in the data recovery system like reducing the ISI by a partial response (PR) equalization method. Fig. 2.8 shows a block diagram of the PRML detector, which consists of the PR equalizer and the optimum MLSD detector, on the receive side.

Fig. 2.8. Block diagram of PRML detector.

In this study, we design targets (HD) and equalizers (FD) by using the minimum-mean squared error (MMSE) method to minimize the mean-squared error (MSE) between desired outputs and equalizer outputs [17][19][21]. The target H(D) and its corresponding F(D) can be obtained by minimizing

$$E\left\{w_k^2\right\} = E\left[\left(z_k - d_k\right)^2\right]$$

$$= E\left[\left\{\left(s_k * f_k\right) - \left(a_k * h_k\right)\right\}^2\right]$$

(2.5)

where  $w_k$  is the difference between output of equalizer,  $z_k$  and the desired output,  $d_k$  of designed target, \* is the convolution operator and  $E\{.\}$  is the expectation operator,  $h_k$  and  $f_k$  stand for the coefficients of H(D) and F(D). The MMSE can be expressed as

$$\varepsilon^{2} = E\left\{w_{k}^{2}\right\} = \mathbf{F}^{T}\mathbf{R}\mathbf{F} + \mathbf{H}^{T}\mathbf{A}\mathbf{H} - 2\mathbf{F}^{T}\mathbf{P}\mathbf{H}$$

(2.6)

where the vector  $\mathbf{H} = [h_0 \ h_1 \ h_2 \ ... \ h_{L-1}]^T$  represents the L-tap generalized partial response (GPR) target and  $\mathbf{F} = [f_{.K} \ , \ f_{.K+1}, ... f_0 \ ... \ f_{_K}]^T$  represents the K-tap equalizer by where the length of the equalizer is  $N \ (N = 2K+1)$ .  $\mathbf{A}$  is an  $L \times L$  autocorrelation matrix of  $a_k$ ,  $\mathbf{R}$  is an  $M \times M$  autocorrelation matrix of sequence  $s_k$ , and  $\mathbf{P}$  is an  $M \times L$  cross-correlation matrix sequence of  $a_k$  and  $s_k$ . During the minimization process, the specified constraint must be used to avoid the trivial solution of  $\mathbf{F} = \mathbf{0}$  and  $\mathbf{H} = \mathbf{0}$ .

Firstly, by minimizing (2.6) subject to a monic constraint, we fix  $h_0$ =1 and compute

$$\varepsilon^{2} = \mathbf{F}^{T} \mathbf{R} \mathbf{F} + \mathbf{H}^{T} \mathbf{A} \mathbf{H} - 2 \mathbf{F}^{T} \mathbf{P} \mathbf{H} - 2 \lambda \left( \mathbf{I}^{T} \mathbf{H} - 1 \right)$$

$$\lambda = \frac{1}{\mathbf{I}^{T} \left( \mathbf{A} - \mathbf{P}^{T} \mathbf{R}^{-1} \mathbf{P} \right)^{-1} \mathbf{I}}$$

$$\mathbf{H} = \lambda \left( \mathbf{A} - \mathbf{P}^{T} \mathbf{R}^{-1} \mathbf{P} \right)^{-1} \mathbf{I}$$

$$\mathbf{F} = \mathbf{R}^{-1} \mathbf{P} \mathbf{H}$$

(2.7)

where  $\lambda$  is the Lagrange multiplier and **I** is an *L*-element column vector which 1<sup>st</sup> element is 1 and the rest is 0. Secondly, we fix the second target  $h_1$ =1 constraint. Column vector **J** that 2<sup>nd</sup> element is 1 and the others are 0. This is identical to monic constraint solution but **I** is replaced by **J**. Thirdly, the energy  $\mathbf{H}^T\mathbf{H}$ =1 is fixed to minimize (28) called the unit energy constraint.

$$\varepsilon^{2} = \mathbf{F}^{T} \mathbf{R} \mathbf{F} + \mathbf{H}^{T} \mathbf{A} \mathbf{H} - 2 \mathbf{F}^{T} \mathbf{P} \mathbf{H} - 2 \lambda \left( \mathbf{H}^{T} \mathbf{H} - 1 \right)$$

(2.8)

After differentiating and setting the result to 0, the final constraint

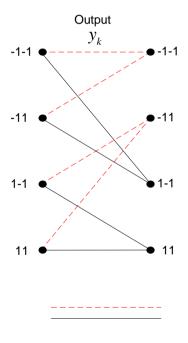

Fig. 2.9. The trellis structure of the Viterbi detector for the channel with two ISI.

The VA processes based on the trellis structure. If the PR equalizer reduces the length of the ISI from two neighboring signal (the number of delay block) to m, the number of states in the trellis structure is  $2^m$ . For example, if there are the two ISI effects in the received signal, the number of states in the trellis will be 4 as shown in Fig. 2.9.

The detector uses Euclidean distance as the branch metrics to find the maximum likelihood sequence of symbol when the received signal is corrupted by additive white Gaussian noise. The branch metric  $I_k$  at time k is

$$I_{k} = (r_{k} - y_{k})^{2}$$

(2.9)

where  $r_k$  is the noisy received signal and  $y_k$  is the noiseless ideal channel output from the trellis. Then the path metric corresponding to each path in the trellis is calculated by adding all branch metrics along the path. The VA detector finds a path in the trellis with the minimum path metric as the maximum likelihood path or survivor path and generates the estimate input data by tracing along this path. Viterbi detector is optimal when the entering noise is AWGN, however, in magnetic recording channel, both media noise and colored noise exist; hence, a noise-predictive version or NPML is proposed [14]. The noise-whitening filter is inserted in front of the Viterbi detector; the trellis complexity is increased as a result.

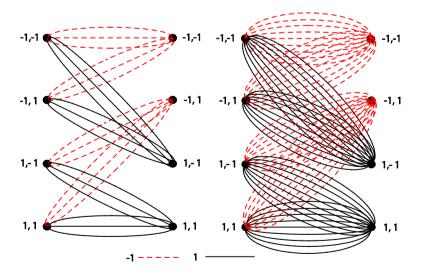

#### 2.2.2 Modified Viterbi detectors for inter-track interference (ITI) mitigation

Current channel detectors such as PRML and NPML detectors are designed to mitigate the ISI rather than ITI. However, for high-density magnetic recording beyond 1  $\text{Tb/in}^2$ , the ITI needs to be considered as well. For 2-D interference, the implementation of a 2-D Viterbi detector is impractical due to excessive complexity, hence, efforts have been made on the reduced-complexity approaches. One such approach is a *modified Viterbi detector* [8] which handles the ITI by using multiple branches from a single state in the trellis. For the channel model in (2.3), assuming that possible values of  $x_{k,l}$  are chosen from  $\{\pm 1\}$ , the noiseless channel output  $y_{k,l}$  from the detected island in (2.4) can be expressed as

$$y_{k,l} = bx_{k,l} + h(x_{k+1,l} + x_{k+1,l}) + v_{k,l} + w_{k,l}$$

(2.10)

with the first ITI term  $v_{k,l} \in \{\pm 2a, 0\}$  and the second ITI term  $w_{k,l} \in \{\pm 4\, \gamma\,,\, \pm 2\, \gamma\,,\, 0\}$ . The ISI portions, the first two terms in (8), result in a trellis with 4 states. Assuming that all corner ITI coefficients,  $\gamma$ , are zero, there are only 3 possible channel outputs. As a result, 3 parallel branches are obtained as shown in Fig. 10. If the values of  $\pm 2\, \gamma$  are neglected, only 9 possible outputs are generated, resulting in 9 parallel branches, otherwise, 15 possible outputs are generated, resulting in 15 parallel branches.

Alternatively, the high complexity of 2-D detector can be avoided by reducing the ISI and mitigating the ITI by using a 2-D equalization method in [10], [12]. In [10], a 2-D generalized partial response (GPR) equalizer using the minimum mean squared error (MMSE) criterion was proposed to mitigate ITI effect in the readback signal before a 1D Viterbi detector. Moreover, in [9], Keskinoz proposed the iterative decision feedback detection (IDFD) method as an alternative method to the 2-D equalization with 1-D detector. For turbo equalization, the soft-output information is required for the decoder of the inner correction code. Two common algorithms are BCJR algorithm [15] and soft-output Viterbi algorithm (SOVA) [16]. In [17], we propose a partial ITI mitigation method (PIMM) based on multi-track processing with the use of an iterative detection by splitting the codeword into three tracks. The resulting trellis has only a single outgoing branch between connected states since all ITI effects are ignored. After the first iteration, hard estimates from the outer code are used compute partial ITI information.

**Fig. 2.10.** Trellis diagrams for modified Viterbi detectors with 1 branch, 3 branches and 9 branches two connected states.

#### 2.2.3 Graph-Based Detector

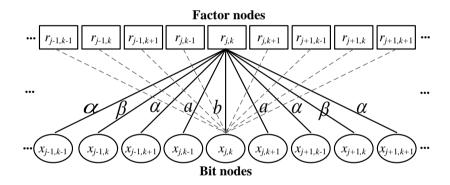

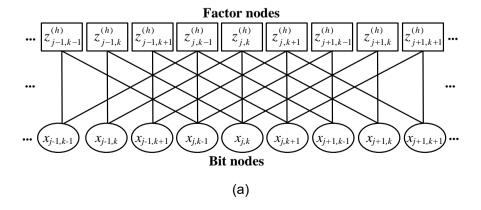

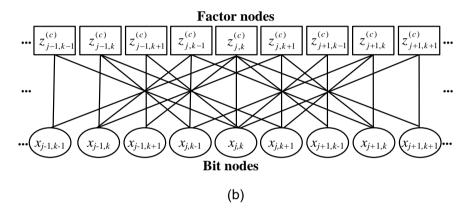

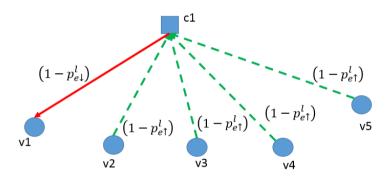

A graph-based detector can be used to handle 2-D interference channels. It is a 2-D detector which processes the readback sequences from multiple tracks, then produces the bit estimates of multiple tracks. A factor graph consists of two categories of nodes, the factor nodes which represent the readback signal  $r_{j,k}$  and the bit nodes which represent the input bits  $x_{j,k}$ . During the detection process, an edge between the factor node and the bit nodes carries the reliability information in terms of the *a posteriori* log-likelihood ratio (LLR) based on the received signal. Figure 2.11 shows the factor graph for the 2-D channel in (2) partially by focusing on the edges from  $r_{j,k}$  to the bit nodes (solid lines) and from  $x_{j,k}$  to the factor nodes (dashed lines) only. Therefore, a full factor graph will have to include other factor nodes and bit nodes. The factor node  $r_{j,k}$  connected to nine bits nodes passes the reliability information to  $x_{j-1,k-1}$ ,  $x_{j-1,k}$ ,  $x_{j-1,k+1}$ ,  $x_{j,k-1}$ ,  $x_{j,k-1}$ ,  $x_{j+1,k-1}$ ,  $x_{j+1,k}$ ,  $x_{j+1,k-1}$ , then each of these bit nodes updates and sends back the message information to the connected factor nodes. Therefore, the three readback sequences are detected by the graph detector to produce the bit decisions of all three tracks  $\{x_{j,k-1}, x_{j,k}, x_{j,k+1}\}$ .

Fig. 2.11. The factor graph of the 2-D channel in (3).

A graph-based detection employs a belief propagation algorithm [47] to compute the LLR information at the factor nodes and bit nodes. For simplicity,  $r_{j,k}$  and  $x_{j,k}$  with the two indices (j,k) are first expressed as the variables  $r_n$  and  $x_p$ , each with a single index. The LLR information is calculated by the sum-product update rule based on the incoming messages from other connected bit nodes and the received signal. Using the max-log approximation  $\log(e^a + e^b) \approx \max(a,b)$ , the update message  $L(\mu_{n \to p})$  from the factor node n to the bit node p is

$$L(\mu_{n\to p}) = \max_{B^n; x_p = +1} \left\{ -\frac{\left(r_n - y_n\right)^2}{2\sigma^2} + \sum_{x_l \in B^n_{\square x_p}, x_l = +1} L(\mu_{l\to n}) \right\}$$

$$- \max_{B^n; x_p = -1} \left\{ -\frac{\left(r_n - y_n\right)^2}{2\sigma^2} + \sum_{x_l \in B^n_{\square x_p}, x_l = -1} L(\mu_{l\to n}) \right\}$$

(2.11)

where  $y_n$  is the noiseless channel output,  $\sigma^2$  is the variance of an AWGN sequence. After receiving the readback signal  $r_n$ , each factor node calculates the LLR messages for every connected bit nodes using (4). For the first term of the numerator, the squared *Euclidean distance* between  $r_n$  and  $y_n$  is calculated for all the possible values of  $y_n$  based on (2), for example, corresponding to all the combination of bit nodes,  $B^n$ , where  $x_p$  is set to +1. For each combination, the summation term is computed with the messages from all the bit nodes  $x_n$ , except  $x_p$ ,  $B^n_{\Box x_p}$ , which has the value of +1 only in the combination set. Finally, the maximum value of the first term is obtained. Similarly, the denominator in (5) is calculated for the set of bit nodes when  $x_p$  is fixed to -1. The LLR information then obtained from the difference of the two maximum values.

After receiving the messages from the factor nodes, all the bit nodes, in turn, generate the LLR message  $L(\mu_{p\to n})$  from the bit node p to the factor node n from

$$L(\mu_{p\to n}) = \sum_{l \in C_{p}^{p}} L(\mu_{l\to p})$$

(2.12)

where  $C_{\square n}^p$  represents the set of factor nodes connected to the bit node  $x_p$  excluding the factor node  $r_n$ . For the first iteration, the messages  $L(\mu_{k^-,n})$  are initialized to zero since all the input bits are assumed to be equi-probable. From the second iteration onward, the factor nodes update the messages using the incoming new messages  $L(\mu_{l^-,n})$ . The updating and exchanging message process will continue until the final iteration is reached. After the specified number of iterations, the LLR information of the estimated output data  $\hat{x}_n$  at bit node n can be computed from

$$L(\hat{x}_n) = \sum L(\mu_{l \to n}).$$

(2.13)

The hard estimates of the input bits can be obtained from

$$\hat{x}_n = \begin{cases} +1, & \text{if } L(\hat{x}_n) \ge 0 \\ -1, & \text{otherwise} \end{cases}$$

(2.14)

Next, we propose two methods to improve the performance of the 2-D graph detector. The channel and target matrices are based on (2).

#### 2.2.4. Mutual Information

The entropy value of a random variable X is measure of uncertainty of the random variable, the amount of information required on the average to describe a random variable. The mutual information between the equally likely X and the LLR for symmetric and consistent L-values by [27]. In graph detector, after the specified number of iterations, the LLR values of each bit can be obtained from (6). For the proposed methods (M1) and (M2), the two resultant LLR values for each bit must be averaged first. We can then measure the mutual information I(L;X) which is defined as

$$I(L;X) = 1 - \int_{-\infty}^{+\infty} p(L \mid x = +1) \log_2(1 + e^{-L}) dL$$

(2.15)

or

$$I(L; X) = 1 - E\left\{\log_2(1 + e^{-L})\right\}$$

(2.16)

where  $E\{.\}$  is the expectation operator.

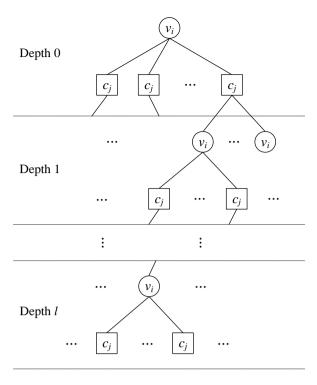

#### 2.3 Background on Low-density parity-check (LDPC) codes

#### 2.3.1 Progressive-edge growth (PEG) algorithm

Low-parity density-check (LDPC) codes were invented in the early 1960's by Robert Gallager [22] but was forgotten. In the 1990's, LDPC codes were again introduced by MacKay and Neal [23]. An LDPC code is a linear block code which shows a good performance approaching the Shannon's limit [23-24] when decoded with the soft decision belief-propagation (BA) or the sum-product algorithm (SPA). LDPC codes can be constructed by random methods. One type of the random LDPC codes is a progressive edge-growth (PEG) LDPC code [25]. This method constructs a parity-check matrix or, equivalently, a Tanner graph, on an edge-by-edge basis giving a large girth and shows an impressive decoding performance through iterative decoding. Unfortunately, the random

LDPC codes do not render efficient encoding structure. Therefore, guasi-cyclic (QC) LDPC codes are preferable since they can be efficiently encoded using simple feedback-shift registers [26]. A disadvantage of the QC-LDPC codes is the limitation of flexible block sizes and code rates. Consequently, in [6], the QC-LDPC codes based on the PEG algorithm or PEG-QC-LDPC codes have been introduced to improve the girth property and the memory requirement. These methods construct the parity-check matrices based on the PEG algorithm [25] with established circulant sub-matrices instead of edges. These codes establish the flexible codes and offer comparable decoding performance to the conventional QC-LDPC codes. Recently, some methods to improve the random LDPC codes based on PEG algorithm have been presented [28-29]. An extended PEG algorithm [29] offers the high-rate random LDPC codes with large girth by considering the local girth on the variable nodes before generating the parity-check matrices, resulting in a high decoding performance. However, it does not provide the maximized girth property. Motivated by this fact, we propose the girth-maximized PEG algorithm and use it to generate the QC-LDPC codes with maximized girth property. This method generates each element of the parity-check matrix based on the PEG algorithm and compute the girth property for every node. Then we select the nodes with the maximum local girth to create the circulant sub-matrix and insert it to the parity-check matrix.

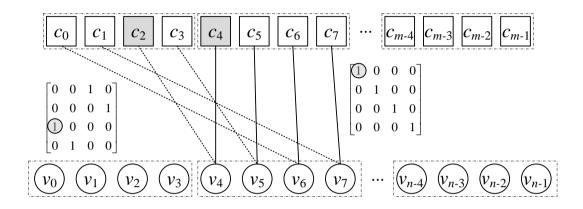

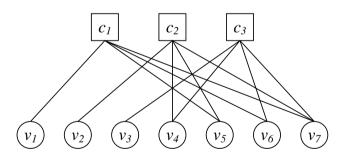

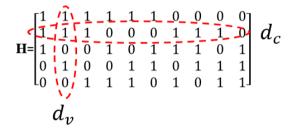

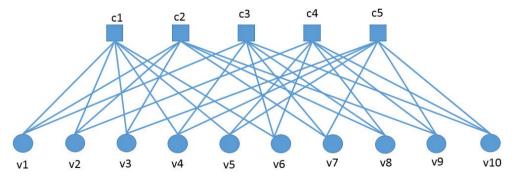

An LDPC code is a linear block code defined by an  $m \times n$  sparse parity-check matrix  $\mathbf{H}$  which can be represented by the Tanner graph [30]. A Tanner graph consists of the set of nodes S and edges E, where S combines the variable nodes and check nodes,  $S = S_c \cup S_v$ , where  $S_c = \{c_0, c_1, c_2, ..., c_{m-1}\}$  is the set of check nodes and  $V_v = \{v_0, v_1, v_2, ..., v_{n-1}\}$  is the set of variable nodes. E comprises the edges between the variable nodes and the check nodes, with  $h_{ji} \neq 0$ , where  $h_{ji}$  is the element in parity-check matrix at the  $f^{th}$  row and the  $f^{th}$  column. The set of edges connected to the variable nodes  $v_i$  is defined as  $E = E_{v_0} \cup E_{v_i} \cup ... \cup E_{v_{n-1}}$ . The degree of variable nodes  $v_i$  is denoted by  $d_v$  and the degree of check nodes  $c_i$  is denoted by  $d_c$ . For a given variable node  $v_i$ , a tree diagram [25] that described a tree spreading from variable node  $v_i$  in the Tanner graph can be drawn as shown in Fig. 2.12 where  $N_{v_i}^I$  is the set of check nodes reached by a tree spreading from  $v_i$  at a depth-I. The complementary of  $N_{v_i}^I$  is  $\overline{N_{v_i}^I}$ , where  $\overline{N_{v_i}^I} = S_c \setminus N_{v_i}^I$ . For each variable node  $v_i$ , the local girth  $v_i$  is defined by the length of the shortest cycle passing through that variable node, or equivalently  $v_i$  is defined by the length of the shortest cycle passing through that variable node, or equivalently  $v_i$  is defined by the length of the shortest cycle passing through that

Fig. 2.12. A tree diagram [25] expanding from the variable node  $v_i$  with a depth-l.

### A. Construction of QC-LDPC codes based on PEG algorithm

The QC-LDPC codes consists of a  $c \times t$  array of circulant matrixes. A circulant matrix is a square matrix with dimension  $p \times p$  in which each row is the cyclic shift of the previous row, and the first row is the cyclic shift of the last row. The parity-check matrixes for QC-LDPC follow the format

$$\mathbf{H} = \begin{bmatrix} \mathbf{H}_{0,0} & \mathbf{H}_{0,1} & \cdots & \mathbf{H}_{0,t-1} \\ \mathbf{H}_{1,0} & \mathbf{H}_{1,1} & \cdots & \mathbf{H}_{1,t-1} \\ \vdots & \vdots & \ddots & \vdots \\ \mathbf{H}_{c-1,0} & \mathbf{H}_{c-1,1} & \cdots & \mathbf{H}_{c-1,t-1} \end{bmatrix}$$

(2.17)

where  $\mathbf{H}_{i,j}$  is circulant matrix with 0 < i < c and 0 < j < t.

#### A. PEG-QC-LDPC codes

The conventional QC-LDPC codes have a limitation of flexible block sizes and code rates. Consequently, the QC-LDPC codes based on the progressive edge-growth (PEG) algorithm have been introduced [27]. The set of variable nodes  $S_{\nu}$  are divided into small

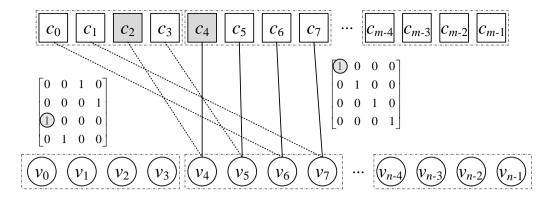

groups with each group having p variable nodes. An edge connected to the first variable node in a group is determined using the PEG algorithm. Then, the edges of other variable nodes in the same group can be automatically determined according to the circulant constraint. Figure 2.13 show an example of a PEG-QC-LDPC code with the circulant size of 4×4. The check nodes connected to the variable node  $v_4$  lead to the circulant constraint of other variable nodes in group.

Fig. 2.13. An example of a PEG-QC-LDPC code with the circulant size of 4×4.

#### 2.3.2 Algorithms for LDPC decoder

Low-density parity-check (LDPC) codes [22] is shown to exhibit the performance approaching the Shannon limit in an additive white Gaussian noise (AWGN) channel [23]. These codes have been widely employed in digital communication systems such as wireless LAN [30], and magnetic recording systems [31] among others.

An LDPC code, a kind of linear block codes, is based on a sparse parity-check matrix. To decode the LDPC codes, the belief-propagation (BP) algorithm is a well-known soft iterative decoding algorithm [23]. To improve the convergence speed of LDPC decoding, serial schedulings [32-37] and informed dynamic schedulings [34-37] have recently been proposed. For the serial schedulings, the check nodes are updated according to the numbered sequence of check nodes, while the updated check nodes can be performed in the increasing or decreasing orders in every iterative decoding proceeds. In [33], the authors further improve the performance of the serial schedulings by applying the opposite check node update directions for the even and odd iterations. For the informed dynamic schedulings, the updated check nodes are indicated by the residual (the difference of information from check node to variable node in the current iteration from the previous iteration). In [30], the serial scheduling

(also known as serial belief propagation) is shown to have the same decoding complexity per iteration as flooding scheduling. However, the informed dynamic scheduling which requires the residual generation and ordering of the residual has a very high complexity [37].

Recently, in [38], the serial belief propagation such as layered belief propagation (LBP) [28-30] and shuffled belief propagation (SBP) [31-33] have been proposed in an ultra-high density magnetic recording system called the bit patterned media (BPM) system. The results show that both the LBP and SBP give the fast convergence speed and they significantly improve the bit error rate performance under various media noise levels. However, the performance of LDPC decoding in the written-in error channel [39-41] that is an important challenge in the ultra-high density magnetic recording system has not been studied. In [42], it is also shown that LBP for nonbinary LDPC codes over GF(q) provides the better performance than the conventional LDPC decoding in conventional magnetic recording systems.

The belief-propagation algorithm is based on the exchange of information or reliability (also called the log-likelihood ratio, LLR) between the nodes of a Tanner graph [17] that represents the relation between codewords and parity-check matrices. A graph is composed of the variable nodes  $v_i$  that represent the  $i^{th}$  code bit and check nodes  $c_j$  that represent the  $j^{th}$  parity-check equation. In the graph, each variable node is connected to  $d_v$  check nodes and each check node is connected to  $d_c$  variable nodes. An example of a bipartite graph is shown in Fig. 2.14.

Fig. 2.14. A Tanner graph.

Belief-propagation algorithm relies on the propagation of the reliability from check nodes to variable nodes  $L(r_{ij})$  as well as the reliability from variable nodes to check nodes  $L(q_{ij})$ . The reliabilities can be computed from

$$L(r_{ji}) = 2 \tanh^{-1} \left( \prod_{i' \in N(c_j) \setminus i} \tanh \left( \frac{1}{2} L(q_{i'j}) \right) \right), \tag{2.18}$$

and

$$L(q_{ij}) = L(v_i) + \sum_{j' \in N(V_i) \setminus j} L(r_{j'i}), \qquad (2.19)$$

where  $i' \in N(c_j)$ Vi denotes the variable nodes connected to the check node  $c_j$  except the variable node  $v_i$ , and  $j' \in N(v_i)$ Vj denotes the check nodes connected to the variable node  $v_i$  except check node  $c_j$ . The log-likelihood ratio (LLR) of the variable node  $v_i$  is  $L(v_i) = \log(P(x_i=0|y_i)/P(x_i=0|y_i))$ , where  $y_i$  is received signal corresponding to the transmitted codeword  $x_i$ . The reliability of a variable node is given by

$$L(Q_i) = L(v_i) + \sum_{j \in N(V_i)} L(r_{ji})$$

(2.20)

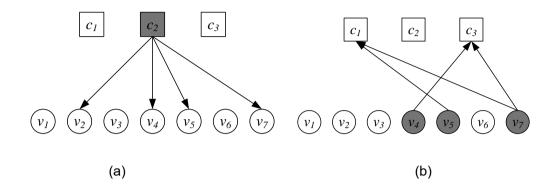

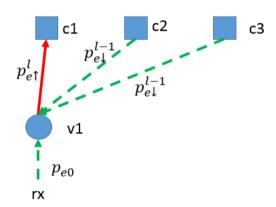

#### 2.3.3 Layered belief propagation

Layered belief-propagation is illustrated in [7] and exhibits a faster convergence than the BP algorithm. LBP relies on different sequences of check node updates from the BP algorithm. In particular, for the BP algorithm, each check node propagates information  $L(r_{ii})$  from the first until the last check nodes before the propagation of reliability  $L(q_{ii})$  from variable nodes can occur. In the LBP, after a check node  $c_i$  passes the updates to connected variable nodes, each of these variable nodes will need to send the updates to its connected check nodes, except check node  $c_i$ , before the next check node can start the propagation so that it is updated using the most recent information. Sequence of check-node updates indicated in LBP is also known as horizontal shuffle scheduling [8-9]. Furthermore, the sequence of check-node propagation in LBP has the same decoding complexity per iteration as the traditional decoding [9-10]. Figure 2.15 shows a graphical explanation of the LBP strategy based on Fig.1. The LBP strategy will schedule to first propagate the information from the same check node  $c_i$  as shown in Fig. 2.15(a). Afterward, the information is propagated from the variable nodes connected to the check node  $c_i$  as shown Fig. 2.15(b). An iteration of LBP strategy will be counted after all the check nodes completely propagate the information  $L(r_{ii})$ . In the previous works, most authors consider the left-to-right direction of check node updates. In general, for LBP, the updated check nodes can start from the leftmost check node of the graph or start from the

rightmost one. In Section IV, we will investigate the difference in error locations from both methods.

Fig. 2.15. Illustration of procedure for LBP strategy.

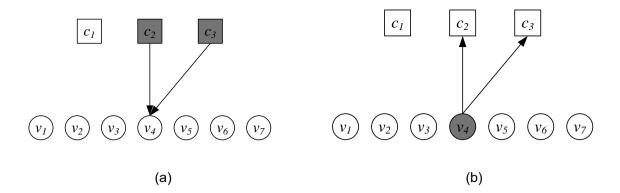

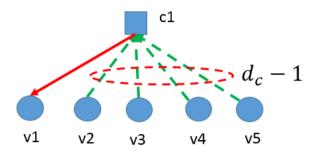

#### 2.3.4 Shuffled belief propagation (SBP)

The shuffled belief propagation [11-12] is a type of serial scheduling which converges faster than the traditional BP decoding. The shuffled belief propagation (also called the vertical shuffle scheduling) is used to sequentially update the variable nodes instead of the check nodes in LBP. However, the sequential update of the variable nodes in SBP has a higher complexity than BP and LBP [10]. The graphical explanation of the SBP strategy is shown in Fig. 2.16. For LBP strategy, each check node will propagate all the information  $L(r_{ji})$ . On the other hand, SBP strategy does not schedule to propagate all the  $L(r_{ji})$  from the same check node  $c_j$  but will schedule to propagate the  $L(r_{ji})$  from the check node connected to the variable node as shown in Fig. 2.16(a). Afterward, the information is propagated from the variable node to all of its connected check nodes as shown Fig. 2.16(b). An iteration of SBP strategy will be counted after each variable node is updated completely.

Fig. 2.16. Illustration of procedure for SBP strategy.

#### 2.4 Heat-assisted magnetic recording (HAMR) systems

The Thermal Williams-Comstock (TWC) model can be used to determine the transition center  $x_0$  and transition width a. First, defined he effective field (h) to account for heating behavior, i.e.,

$$h(x) = \frac{H_a(x)}{H_C(T(x))}.$$

(2.21)

The thermal Williams-Comstock slope equation can then be derived from

$$\frac{dM(x)}{dx}\bigg|_{X_{0}} = \frac{dM(H)}{dH_{a}(T(x_{0}))}\bigg|_{H_{c}(T(x_{0}))} \times \left[\frac{dH_{h}(x)}{dx}\bigg|_{X_{0}} + \frac{dH_{d}(x)}{dx}\bigg|_{X_{0}} - \frac{dH_{c}(T(x_{0}))}{dT}\bigg|_{T(x_{0})} \frac{dT}{dx}\bigg|_{X_{0}}\right].$$

(2.22)

Since dM/dx and  $dH_d/dx$  depend on the parameter a, and it can be solved by using (2.22). To obtain dM/dx, it is assumed that the transition during recording can be described by the arctangent function from which dM/dx can be derived.

$$M(x) = \frac{2M_r(T(x))}{\pi} \tan^{-1} \frac{x - x_0}{a}$$

(2.23)

and dM/dx at  $x_0$  can be solved by differentiating (2.23), i.e.,

$$\frac{dM(x)}{dx}\bigg|_{x_0} = \frac{2M_r(T(x_0))}{\pi a}$$

(2.24)

The term dM(h)/dh from (2.22) at  $x_0$  can be solved as slope of hysteresis loop is always positive at either transition is made from positive or negative  $H_c$

$$\frac{dM(h)}{dh}\Big|_{H_{c}(T(x_{0}))} = \left|\frac{1}{H_{c}(T(x_{0}))} \times \frac{M_{r}(T(x_{0}))}{1 - S^{*}}\right|$$

(2.25)

The term  $dH_h/dx$  of perpendicular recording at  $x_0$  can be solved by using and the symmetry of the longitudinal Karlqvist head field component. The perpendicular head field can be derived by facilitating to turned sideways of longitudinal as

$$H_h = \frac{H_0}{\pi} \left[ \tan^{-1} \left( \frac{y + g/2}{x} \right) - \tan^{-1} \left( \frac{y - g/2}{x} \right) \right],$$

(2.26)

And

$$\frac{H_h(x)}{dx}\bigg|_{x_0} = -\frac{gH_0}{\pi \left(x^2 + (g/2)^2\right)},$$

(2.27)

where  $H_0$  is the deep gap field, g is the gap width between pole head and its image (g = 2d+2t), t is the medium thickness and the field is evaluated at the center of medium (y = t/2). The parameter  $H_d$  for perpendicular recording is obtained by convolving the unit step response at the original and the magnetization gradient, i.e.,

$$H_{d,perp} = -\frac{\partial M(x)}{\partial x} * H_y^{step} = -\frac{\partial M(x)}{\partial x} * \frac{1}{\pi} \tan^{-1} \left(\frac{2x}{t}\right)$$

(2.28)

and

$$\frac{dH_d(x)}{dx} = -\frac{4}{\pi^2} \int_{-\infty}^{\infty} \frac{M_r(T(x'))a}{a^2 + (x' - x_0)^2} \frac{t}{t^2 + 4(x - x')^2} dx' + \frac{4}{\pi^2} \int_{-\infty}^{\infty} \tan^{-1} \left(\frac{x' - x_0}{a}\right) \frac{dM_r(T(x'))}{dT} \Big|_{T(x')} \frac{dT(x')}{dx'} \frac{t}{t^2 + 4(x - x')^2} . (2.29)$$

Here,  $H_c$  and  $M_r$  are linearly temperature-dependent (T),i.e,

$$H_c = -H_{c0}T(x, y) + H_{c const}$$

(2.30)

and

$$M_r = -M_{r0}T(x, y) + M_{r const}$$

(2.31)

where  $H_{c0}$  and  $M_{r0}$  are the temperature sensitivities of  $H_c$  and  $M_r$ ,  $H_{c,const}$  and  $M_{r,const}$  are  $H_c$  and  $M_r$  at 0 Kelvin (K). So  $dH_c/dT$  is  $-H_{c0}$  and  $dM_r/dT$  is  $-M_{r0}$ . A two-dimensional (2D) Gaussian thermal profile is given as

$$T(x, z) = T_{peak} \exp\left(-\frac{(x - c_0)^2}{2\sigma_t^2}\right) \exp\left(-\frac{z^2}{2\sigma_t^2}\right) + 300 \text{ (K)}$$

(2.32)

where  $T_{peak}$  is the peak temperature in the medium above room temperature in degree Celsius,  $c_0$  is the laser spot position, x is defined to the position in down-track direction and z is defined to the position in cross-track direction. Differentiating (2.29), we have

$$\frac{T(x,z)}{dx} = T_{peak} \left( -\frac{\left(x - c_0\right)}{\sigma_t^2} \right) \exp\left( -\frac{\left(x - c_0\right)^2}{2\sigma_t^2} \right) \exp\left( -\frac{z^2}{2\sigma_t^2} \right). \tag{2.33}$$

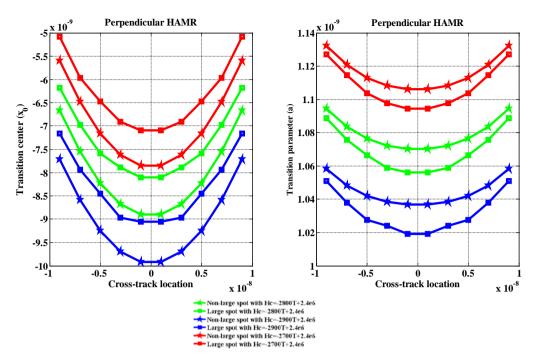

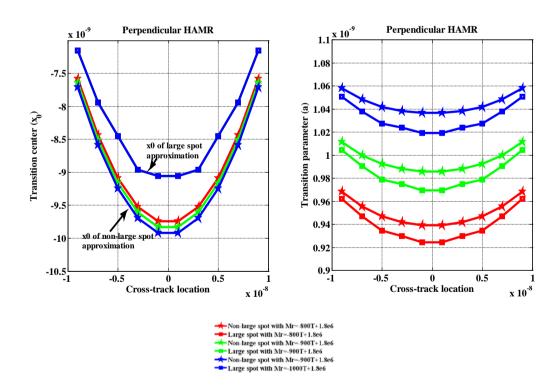

### 2.4.1. Transition center (x<sub>0</sub>) and transition parameter a

The position  $x_0$  is defined as the point where the medium reverses its direction of magnetization and a is measured and related to the width of the magnetization transition. Achieving the narrowest possible transition (smallest a) allows placing recording bits close together and hence results in high linear density. The position  $x_0$  of perpendicular HAMR with large spot and linear relationship for  $H_c$  and  $M_r$  can be calculated by

$$x_{0} = \frac{g + \sqrt{g^{2} - a \tan^{2} \left(\pi \frac{H_{c} \left(T \left(x_{0}\right)\right)}{H_{0}}\right) \left(y^{2} - \left(g/2\right)^{2}\right)}}{2 \tan \left(\pi \left(\frac{H_{c} \left(T \left(x_{0}\right)\right)}{H_{0}}\right)\right)}$$

(2.34)

and a can be also calculated from

$$a = -\frac{\gamma}{2} + \frac{1}{2} \sqrt{\gamma^2 + \frac{4H_c (1 - S^*)t}{\Delta \pi}} \bigg|_{X_0}$$

(2.35)

where

$$\Delta = \frac{H_g g}{\pi \left(x_0^2 + \left(g/2\right)^2\right)} - \frac{dH_c}{dT} \frac{dT}{dx} \bigg|_{x_0}$$

(2.36)

and

$$\gamma = \frac{2M_r}{\Delta \pi} - \frac{t}{2} + \frac{2H_c(1 - S^*)}{\Delta \pi}$$

(2.37)

For non-large spot HAMR,  $x_0$  can be solved by

$$x0, j+1 = \frac{g + \sqrt{g^2 - 4\tan^2\left(\pi \frac{H_c(T(x_0)) + H_d(x_0, j, a_k)}{H_0}\right)\left(y^2 - \left(g/2\right)^2\right)}}{2\tan^2\left(\pi \frac{H_c(T(x_0)) + H_d(x_0, j, a_k)}{H_0}\right)}$$

(2.38)

and a can be solved by

$$a_{k+1} = \frac{-\beta + \sqrt{\beta^2 + 4\pi(\alpha + \delta)H_c(1 - S^*)t}}{2\pi(\alpha + \delta)}$$

(2.39)

where

$$\alpha = \frac{H_g g}{\pi \left(x_{0,j+1}^2 + \left(\frac{g}{2}\right)^2\right)}, \delta = \frac{dH_d \left(a_k, x_{0,j+1}\right)}{dx} - \frac{dHc}{dx}, \tag{2.40}$$

and

$$\beta = -\frac{\pi \alpha t}{2} + 2M_r - \frac{\pi t}{2} \left( \frac{dH_d \left( a_k, x_{0, j+1} \right)}{dx} - \frac{dH_c}{dx} \right) + 2H_c \left( 1 - S * \right)$$

(2.41)

In this work, the medium is assumed to be  ${\rm Fe_{25}Ni_{30}Pt_{45}}$ . For all cases, the laser is assumed to be at the center of the track in the cross-track direction but varied in the down-track direction. The coercivity  $H_c$  and remanent magnetization  $M_r$  have linear relationship with the temperature. The temperature induced by the laser is assumed to be Gaussian in both dimensions with the peak temperature of 330 °C and track width 20 nm.

### 2.4.2. The Generation of the HAMR readback signal

The microtrack model is used for 2D process of heating and magnetization of a medium to solve the problem of determining the transition characteristics in HAMR by dividing recorded track into N individual sub-tracks of equal width with different transition parameters. The TWC equation is applied to determined  $x_0$  and a in each individual sub-track. The playback voltage (V) of perpendicular recording is given by

$$V(x, a_i, x_{0,i}) = -CM_r t \ln \left( \frac{\left( g_r / 2 - (x - x_0)^2 \right) + \left( d + a + t / 2 \right)^2}{\left( g_r / 2 + (x - x_0)^2 \right) + \left( d + a + t / 2 \right)^2} \right)$$

(2.42)

where C is a system specific constant,  $g_r$  is the read head gap, and d is the head-medium spacing and t is denote to media thickness. The overall transition response p(x) can be obtained by weighting the transition response  $p_r(x)$  of each sub-track to obtain

$$p_{i}(x) = \exp \left(-\frac{N+1}{2}\Delta z + i\Delta z\right)^{2} / 2\sigma_{r}^{2} \cdot V(x, a_{i}, x_{0i})$$

$$(2.43)$$

and

$$p(x) = \frac{1}{N} \sum_{i=1}^{N} p_i(x)$$

(2.44)

where  $a_i$  and  $x_{0i}$  are the transition parameter and transition center of the  $i^{th}$  microtrack, i can be 1 to N and  $\Delta z$  stands for the width of each sub-track. The bit response is then

$$h(x) = 0.5 \{ p(x) - p(x - T_X) \}$$

(2.45)

where  $T_x$  denotes the along-track bit period.

### 2.5 Flash recording channels

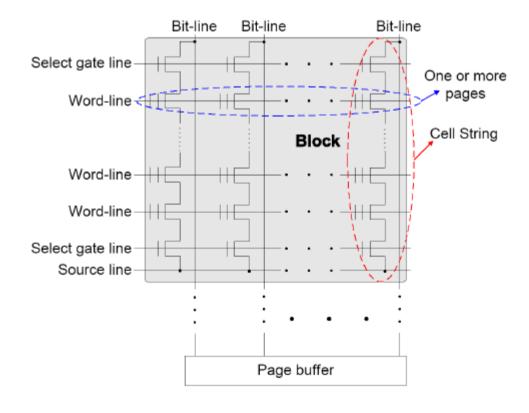

NAND flash memory array is divided into blocks and each block consists of a number of pages as shown in Fig. 2.17. Each block has a number of bit lines (memory cells) and word lines (pages). Each bit line has 16 to 64 memory cells.

Fig. 2.17. Structure of flash memory blocks.

All the memory cells within the same block must be erased at the same time and data are programmed and input in the unit of page. The page size varies from 512 bytes to 8K bytes.

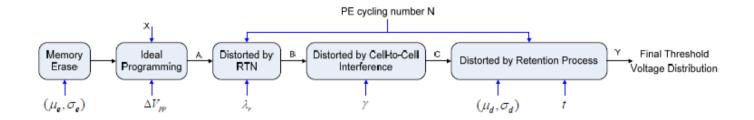

A NAND flash memory channel model is shown in Fig. 2.18.

Fig 2.18. Flash memory channel.

A flash memory cell needs to be erased before it can be programmed. In order to erase a cell, all the charges are removed from the floating gate and the threshold voltage is set to the lowest possible values. The distribution of the threshold voltage of erased state can be modeled by a Gaussian distribution  $N\left(\mu_e,\sigma_e^2\right)$ , i.e.,

$$p_{e}(x) = \frac{1}{\sqrt{2\pi\sigma_{e}^{2}}} e^{-\frac{(x-\mu_{e})^{2}}{2\sigma_{e}^{2}}}$$

(2.46)

where  $\mu_{e}$  and  $\sigma_{e}$  are the mean and standard deviation of the erased state.

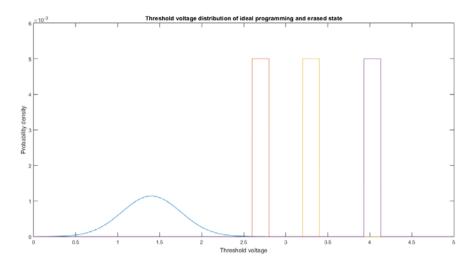

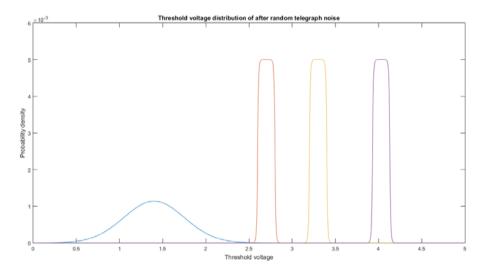

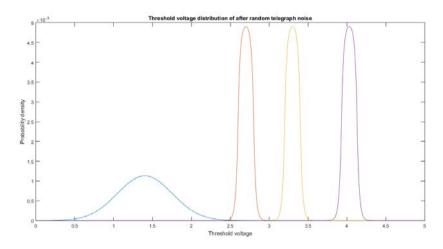

Each programmed state, with program and verify approach, has the threshold voltage of uniform distribution over  $\left[V_p,V_p+\Delta V_{pp}\right]$ . If we denote  $V_p$  and  $V_p+\Delta V_{pp}$  of the k-th programmed state as  $V_l^{(k)}$  and  $V_r^{(k)}$ , then the ideal threshold voltage distribution of the k-th programmed state can be modeled by

$$p_{p}^{(k)}(x) = \begin{cases} \frac{1}{\Delta V_{pp}}, V_{l}^{(k)} \le x \le V_{r}^{(k)} \\ 0, & \text{otherwise} \end{cases}$$

(2.47)

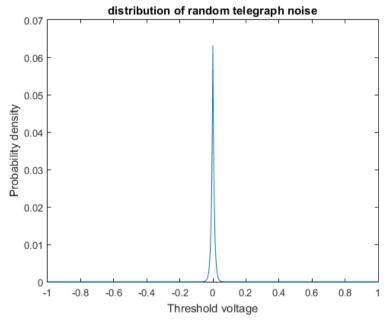

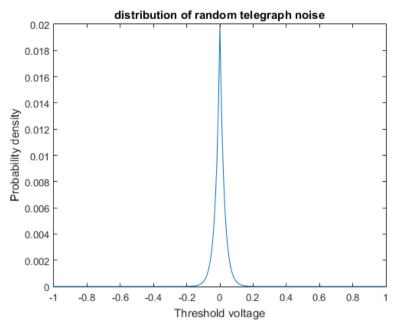

In practice, the ideal threshold voltage distribution is affected by the program/erase (PE) cycling which causes (1) the threshold voltage shift and fluctuation known as random telegraph noise (RTN) and (2) in the memory cell causing data retention issue. The probability density function of the RTN-induced threshold voltage is

$$p_r(x) = \frac{1}{2\lambda_r} e^{-\frac{|x|}{\lambda_r}} \tag{2.48}$$

If N is the cycling number,  $\lambda_r$  scales with a power-law fashion. Additionally, the threshold voltage reduction is modeled as a Gaussian distribution  $N\left(\mu_d,\sigma_d^2\right)$  where  $\mu_d$  and  $\sigma_d^2$  scale with N in a power-law fashion and scales with the retention time t in a logarithmic fashion. The cell-to-cell interference in NAND flash memory is caused by parasitic capacitance-coupling effect. The resulting threshold voltage shift of a victim cell can be approximated as

$$F = \sum_{k} \left( \Delta V_{t}^{(k)} \cdot \gamma^{(k)} \right) \tag{2.49}$$

where  $\Delta V_t^{(k)}$  is the shift in threshold voltage of an interfering cell which is programmed after the victim cell. The coupling ratio is defined as

$$\gamma^{(k)} = \frac{C^{(k)}}{C_{tot}}$$

(2.50)

where  $C^{(k)}$  is the parasitic capacitance between the interfering cell and the victim cell, and  $C_{tot}$  is the total capacitance of the victim cell.

From Fig. 2.18, the threshold voltage distribution after the RTN model is

$$p_{ar}(x) = p_p(x) \otimes p_r(x)$$

(2.51)

where  $p_p(x)$  is the threshold voltage distribution after the ideal programming, and  $p_r(x)$  is from (2.45). For cell-to-cell interference, both the vertical and diagonal coupling ratios are set to be truncated Gaussian distribution, i.e.,

$$p_{c}(x) = \begin{cases} \frac{k_{c}}{\sigma_{c}\sqrt{2\pi}} e^{-\frac{(x-\mu_{c})^{2}}{2\sigma_{c}^{2}}}, |x-\mu_{c}| \leq w_{c} \\ 0, \text{ else} \end{cases}$$

(2.49)

Given that the threshold voltage after the cell-to-cell interference be  $p_{ac}(x)$  and the distribution of retention noise distribution be  $p_{t}(x)$ , the final threshold voltage distribution  $p_{f}(x)$  is obtained as

$$p_f(x) = p_{ac}(x) \otimes p_t(x) \tag{2.50}$$

Finally, the retention noise can be modelled as Gaussian distribution where the mean and std depends on the Erase and Programming cycles N, i.e.,

$$\mu_d = K_s \left( x - x_0 \right) K_d N^{0.5} \ln \left( 1 + \frac{t}{t_0} \right)$$

(2.51)

and

$$\sigma_d^2 = K_s \left( x - x_0 \right) K_m N^{0.6} \ln \left( 1 + \frac{t}{t_0} \right)$$

(2.52)

In [49], proposes the non-uniform fine-grained soft-decision memory sensing and investigates the performance of binary LDPC codes in NAND flash memory channels with 2 bits/cell. In [50], product codes based on the combination of LDPC codes as well as Hamming codes are investigated. For realistic code design, it is essential to understand the error patterns of flash memory, therefore, in [51], the authors spent much efforts characterizing the error patterns in NAND flash memory.

## 3. Methodology

Channel simulations will be made for various types of storage. For advanced PMR and HAMR, the full system will be simulated, then the designed target equalizers as well as detectors will be made. Since the advanced PMR is affected by nonlinearity on the write side and read side, the system performance will be studied. In addition, the nonlinear compensation methods will be proposed. The write nonlinearity will be based on Volterra's model and the use of pseudo-random sequence is exploited to obtain the dipulse and nonlinearity information, the compensation on the nonlinearity echoes will be emphasized. For the read side, nonlinearity such as sudden amplitude changes will be studied in terms of the probability density function (pdf), then the detector will be designed to detect such events as well as improve the system performance. For HAMR, it is well-known that the intersymbol interference level is higher than that in the advanced PMR channels, and in addition, the shape of dibit pulse differs significantly. Therefore, the study on suitable target-shaping equalizers will be made.

For bit-patterned media and shingled writing, we will focus on the 2-D channel models in order to design the 2-D detectors as well as the 2-D error correction codes for such channels. The designed detectors will be based on trellis structure with the focus on reduced-complexity alternatives. The designed codes are binary as well as nonbinary low-density parity-check (LDPC) codes based on the progressive-edge growth (PEG) algorithm. The decoding schedulings will be the mixed-type scheduling which combines the output from the current layered schedulings with right-to-left and left-to-right direction. These designed codes and decoders will be also be designed specifically for flash memory channels as well to test the improvement in it lifetime.

All the simulations will be on made in MATLAB software. The channels and noise would represent the main characteristics of the recording channels. Finally, some experiments on the applicability and reliability of Shingled magnetic writing (SMR) will be made. Some parameters under study are SNR, reverse overwrite (ROW) ratio, areal density, partial erasure (PE), and others.

For the scope of Research, the channels considered are in the continuous-time domain for advanced PMR and HAMR. For detector design, the bit error rate test is limited for BER level of 10<sup>-5</sup> only. To simulate the dibit pulse of HAMR, up to 10 microtracks will be used. The types of noise and distortion considered are jitter noise of up to 50 percent, nonlinear models up to two to three orders. The areal density considered is not more than

5 terabits/square inch. For bit-patterned media and shingled writing, we will focus on the 3x3 2-D channel matrix to account for ITI from two adjacent tracks and ISI from two adjacent bits. For code design, only high-rate LDPC codes of more than 0.8 are considered. When implementing in the system, the BER levels considered is not lower than 10<sup>-8</sup>. For the experiments in Shingled magnetic writing, we use the write and read heads in the actual manufacturing process; therefore, the sizes will vary significantly.

### 4. Results and Discussions

### 4.1. Heat-assisted magnetic recording systems

### 4.1.1 Simulation of HAMR readback signals

Firstly, we fix  $M_r$  magnetization dependencies on temperature to study the behavior of  $x_0$  and a by using various  $H_c$ . With magnetization dependencies on temperature ( $M_r$ =-1000T+1.8x10 $^6$ ), we found that at increasing  $H_c$ ,  $x_0$  is shifted faraway from laser position and a is decreased. Secondly, we vary  $M_r$  to study  $x_0$  and a by using  $H_c$  = -2900T+2.4x10 $^6$  for evaluation. Fig. 4.1 shows that  $x_0$  has almost the same values and small a is found at low  $M_r$ . Small a means narrow transitions, hence, recording bits are packed close together. System parameters are listed in Table 4.1.

TABLE 4.1. SYSTEM PARAMETERS

| Symbol                            | Parameter                                 | Unit                          |

|-----------------------------------|-------------------------------------------|-------------------------------|

| TW                                | track width                               | 20 nm                         |

| Ν                                 | number of sub-track                       | 10                            |

| $C_{o}$                           | laser position                            | 0 nm                          |

| $H_0$                             | deep gap field                            | 1x10 <sup>6</sup> A/m         |

| $T_{peak}$                        | peak temperature                          | 330 ℃                         |

| $\sigma_{\!\scriptscriptstyle t}$ | sigma of temperature profile              | 16.2 nm                       |

| G                                 | gap width between pole head and its image | 32 nm                         |

| $\sigma_{r}$                      | sigma of reader sensitivity function      | 4.23 nm                       |

| d                                 | head-medium distance or fly height        | 6 nm                          |