# รายงานวิจัยฉบับสมบูรณ์

โครงการ: การออกแบบวงจรรวมสำหรับปรับสัญญาณคลื่นไฟฟ้าหัวใจแบบพลังงานต่ำที่มี ช่วงพลวัตรของสัญญาณขาเข้าที่กว้างสำหรับเครื่องวัดคลื่นไฟฟ้าหัวใจแบบสวมใส่

โดย ผศ. ดร. วรดร วัฒนพานิช

พฤษภาคม/2563

สัญญาเลขที่: RSA6080053

# รายงานวิจัยฉบับสมบูรณ์

โครงการ: การออกแบบวงจรรวมสำหรับปรับสัญญาณคลื่นไฟฟ้าหัวใจแบบพลังงานต่ำที่มี ช่วงพลวัตรของสัญญาณขาเข้าที่กว้างสำหรับเครื่องวัดคลื่นไฟฟ้าหัวใจแบบสวมใส่

# โดย <u>ผศ. ดร. วรดร วัฒนพานิช</u> ภาควิชาวิศวกรรมไฟฟ้า คณะวิศวกรรมศาสตร์ มหาวิทยาลัยเกษตรศาสตร์

## สนับสนุนโดยสำนักงานกองทุนสนับสนุนการวิจัยและ มหาวิทยาลัยเกษตรศาสตร์

(ความเห็นในรายงานนี้เป็นของผู้วิจัย สกว และมหาวิทยาลัยเกษตรศาสตร์ไม่จำเป็นต้องเห็น ด้วยเสมอไป)

## กิตติกรรมประกาศ

โครงการวิจัยนี้จะไม่สามารถสำเร็จลุล่วงไปได้หากขาดความร่วมมือร่วมใจจากสมาชิก

ห้องปฏิบัติการวิจัยด้านการออกแบบวงจรรวมและระบบบูรณาการพลังงานต่ำแห่ง

มหาวิทยาลัยเกษตรศาสตร์ทั้งที่ได้จบการศึกษาไปแล้วและกำลังทำการศึกษาอยู่ ที่ได้ร่วมแรงร่วมใจใน

การออกแบบ พัฒนาและทดสอบวงจรต่างๆ และระบบที่ได้อธิบายในรายงานฉบับสมบูรณ์ฉบับนี้

นอกจากนี้ ผู้วิจัยยังขอขอบคุณภาควิชาวิศวกรรมไฟฟ้า และคณะวิศวกรรมศาสตร์

มหาวิทยาลัยเกษตรศาสตร์ ที่ได้สนับสนุนสาธารณูปโภคต่างๆ ด้านการวิจัย ครุภัณฑ์ รวมทั้งเงินทุน

สำหรับลูกศิษย์ที่ได้ช่วยในการทำงานวิจัยนี้

สุดท้ายนี้ ผู้วิจัยขอขอบคุณมหาวิทยาลัยเกษตรศาสตร์และสำนักงานกองทุนสนับสนุนการวิจัย ผู้สนับสนุนงบประมาณหลักสำหรับงานวิจัยนี้ จนผู้วิจัยสามารถทำงานจนสำเร็จลุล่วงไปได้

วรดร วัฒนพานิช

#### **Final Report**

Project Code: RSA6080053

Project Title: Design of A Wide-Dynamic-Range Ultra-Low-Power ECG Signal-Conditioning

Integrated Circuit (IC) for Next-Generation Wearable ECG Acquisition Systems

Investigator: Assistant Professor Dr. Woradorn Wattanapanitch, Department of Electrical

Engineering, Faculty of Engineering, Kasetsart University

E-mail Address: fengwdw@ku.ac.th

Project Period: From 30 May 2017 to 29 May 2020

#### Abstract

In recent years, cardiovascular diseases have become, by far, the leading cause of death among the Thai population. Despite the enormous national budget spent on the diagnoses and treatments of cardiovascular diseases in hospital settings, many fellow Thai citizens still succumb to the diseases daily. The death rate due to heart diseases may be reduced if the majority of the Thai population has easy access to state-of-the-art wearable cardiac monitoring systems. To be useful in clinical applications and be widely adopted by the general public, such wearable cardiac monitoring system must be able to provide high-quality recorded electrocardiograms (ECG) for diagnostic and treatment purposes, be low-power, small in size, and be very convenient to use. These aspects put stringent requirements on the design of the ECG signal-conditioning circuits. In this research, we have designed, built, and tested a low-power wide-dynamic-range ECG signal-conditioning integrated circuit (IC), suitable for use in the next-generation cardiac monitoring systems. The IC, fabricated in a standard 0.18-um CMOS technology, consumes a total current of less than 10 µA from a 1.2-V supply voltage, making it one of the lowest-power ECG readout IC in the literature. Due to its high input impedance, the IC is suitable for recording from dry electrodes, thus paving the way for the development of battery-powered wireless activeelectrode ECG readout systems that are comfortable to wear on the body. As part of this research, we have also developed novel architectures for some of the IC's building blocks, which result in high-impact journal publications. We believe that the results from this study are useful not only in ECG recording applications, but also in implantable biomedical devices, other wearable electronics for health monitoring, and low-power sensor nodes in wireless sensor networks.

**Keywords:** bioelectronics, cardiac monitoring system, mixed-signal integrated circuit design, motion artifact, low-power, instrumentation amplifier, signal-folding amplifier,

**Research area/ sub area of this project:** Electrical Engineering, Analog/Mixed-Signal Integrated Circuit, Biomedical Circuits and Systems

ชื่อโครงการ: การออกแบบวงจรรวมสำหรับปรับสัญญาณคลื่นไฟฟ้าหัวใจแบบพลังงานต่ำที่มีช่วงพล วัตรของสัญญาณขาเข้าที่กว้างสำหรับเครื่องวัดคลื่นไฟฟ้าหัวใจแบบสวมใส่ บทคัดย่อ

ในไม่กี่ปีที่ผ่านมา โรคหัวใจและหลอดเลือดนับเป็นสาเหตุการตายอันดับหนึ่งของประชากรไทย ถึงแม้ว่า รัฐบาลจะได้ทุ่มเทงบประมาณในการตรวจวินิจฉัยและการรักษาโรคหัวใจและหลอดเลือดในโรงพยาบาล ก็ยังมีประชากรไทยจำนวนหลายคนที่ต้องเสียชีวิตจากโรคหัวใจและหลอดเลือดในแต่ละวัน ตาม เราสามารถลดอัตราการเสียชีวิตจากโรคหัวใจได้ถ้าประชากรส่วนใหญ่สามารถเข้าถึงระบบตรวจวัด คลื่นไฟฟ้าหัวใจแบบสวมใส่ที่ทันสมัย ในการจะเข้าถึงและได้รับการยอมรับโดยประชากรส่วนใหญ่ได้ เครื่องตรวจวัดคลื่นไฟฟ้าหัวใจแบบสวมใส่นี้ต้องสามารถตรวจวัดคลื่นไฟฟ้าหัวใจได้อย่างแม่นยำ อีกทั้ง ้ต้องมีขนาดเล็ก มีอัตราการกินพลังงานที่ต่ำ และต้องมีการใช้งานที่ง่ายอีกด้วย ข้อกำหนดเหล่านี้ทำให้ การออกแบบวงจรสำหรับวัดและปรับสัญญาณคลื่นไฟฟ้าหัวใจมีความท้าทายอย่างยิ่ง ดังนั้นในงานวิจัย นี้ ผู้วิจัยจึงได้ทำการออกแบบ ผลิต และทำการทดสอบวงจรรวมสำหรับปรับสัญญาณคลื่นไฟฟ้าหัวใจ แบบพลังงานต่ำที่มีช่วงพลวัตรของสัญญาณขาเข้าที่กว้าง สำหรับการใช้ในเครื่องตรวจวัดคลื่นไฟฟ้า วงจรรวมนี้ได้ถูกผลิตในเทคโนโลยีซีมอสแบบมาตรฐานขนาด หัวใจแบบสวมใส่แห่งอนาคต ไมโครเมตร โดยมีอัตราการกินกระแสน้อยกว่า 10 ไมโครแอมป์จากไฟเลี้ยงขนาด 1.2 โวลต์ นอกจากนี้ ซึ่งเหมาะสมสำหรับการใช้วัดคลื่นไฟฟ้าหัวใจจากอิเล็กโทรดแบบ วงจรยังมีความต้านทานขาเข้าที่สูง อันจะส่งผลให้การสวมใส่เครื่องดังกล่าวมีความสะดวกสบายกว่าการใช้อิเล็กโทรดแบบเปียกเป็น อย่างมาก และในงานวิจัยนี้ ผู้วิจัยยังได้พัฒนาสถาปัตยกรรมวงจรรูปแบบใหม่สำหรับวงจรส่วนประกอบ ต่างๆ ซึ่งได้ถูกรายงานในวารสารทางวิชาการระดับนานาชาติชั้นนำในสาขาวิชานี้ด้วย ผู้วิจัยจึงหวังเป็น อย่างยิ่งว่าความรู้ที่ได้จากงานวิจัยนี้จะเป็นประโยชน์ไม่ใช้เฉพาะในการออกแบบวงจรสำหรับการวัด คลื่นไฟฟ้าหัวใจเพียงอย่างเดียว แต่ยังมีประโยชน์สำหรับการใช้งานแบบอื่นๆ เช่น การออกแบบอุปกรณ์ ชีวการแพทย์แบบฝั่งในร่างกาย และอุปกรณ์วัดสัญญาณชีพแบบสวมใส่อื่นๆ

## Introduction to the research problem and its significance

Cardiovascular diseases and heart failure have become the leading causes of death throughout the world in the last few decades. Recently, due to lifestyle changes such as consuming diets high in saturated fat, exercising less, and smoking and drinking heavily, the Thai population is acquiring cardiovascular diseases at an alarming rate. Besides, Thailand is becoming an aging society, with a growing number of older people that outpaces the national birthrate. These aging people possess higher risks of acquiring cardiovascular diseases and heart failure. Such non-communicable diseases have become an epidemic in modern Thai society and have claimed the lives of a large number of our fellow citizens yearly. From the WHO's 2014 statistics, cardiovascular diseases account for 29 percent of all deaths in the Thai population by far the leading cause of death in our country. There is no better cure for cardiovascular diseases other than changing to healthier lifestyles. Nevertheless, for a country with a large population already suffering from cardiovascular diseases, focusing on the diagnoses and treatments of the diseases should also be an immediate national agenda. Even though Thailand is spending a large amount of money dealing with such diagnoses and treatments, many people still lost their lives to cardiovascular diseases, especially those without easy means to access state-of-the-art medical facilities.

In a fully-equipped health center, medical personnel may observe a patient's electrocardiogram (ECG), the heart's electrical patterns projected onto the patient's body, to determine abnormalities of the heart — abnormalities in the ECG waveforms are usually called arrhythmias. This diagnosis is generally performed at a bulky ECG station at which the patient must lie still to minimize interferences induced by the patient's motions and muscle activities. Long wires are then connected between the ECG acquisition machine and the electrodes attached to various points on the patient's body to acquire the ECG. This cumbersomeness may have shunned even well-to-do patients from having frequent ECG diagnoses. Such frequent diagnoses may help prevent many severe symptoms from going unnoticed, thus helping reduce the number of deaths from cardiovascular diseases and heart failure. For abnormalities that are hard to identify in a limited time at a medical facility, doctors may prescribe the use of a Holter monitoring system, an ambulatory ECG recording device that can continuously record ECG for 24-48 hours. However, most Holter monitors in the market today offer only primitive functionalities while consuming too much power for long-term chronic use; they only store data in the devices' memories to be downloaded and analyzed later by the physicians. With their current power consumption level, most Holter monitors require at least two AAA batteries for 24-48 hours of operation, thus making them relatively large and increasing component and packaging cost. The

cost of a commercially-available mid-range Holter monitor in the market today is approximately 2,000-3,000 US dollars, still too expensive for the Thai general public. As a result, most Holter monitors today are only for diagnostic purposes, in which hospitals lease them to patients with some fees.

Now imagine if we have an ambulatory ECG acquisition system that is an order of magnitude smaller than current Holter monitors, and requires only button batteries to operate for months of operation. Also, imagine that such device can wirelessly transmit the recorded data in real-time to a remote computer on the physician's desk and can issue warnings when cardiac arrhythmias occur while being robust, low-cost, and comfortable to wear on the body. These devices may change the face of the Thai healthcare system regarding the diagnoses and treatments of cardiovascular diseases; with such devices, advanced cardiac monitoring can be accessible by patients with limited means. The full adoption of such technology may help in the early diagnoses and warnings of heart problems, which can save many lives that might otherwise be lost to cardiovascular diseases. The technology can also help reduce the overall healthcare cost since early diagnoses can prevent symptoms from getting worse, thus obviating expensive medical procedures needed for treating severe patients.

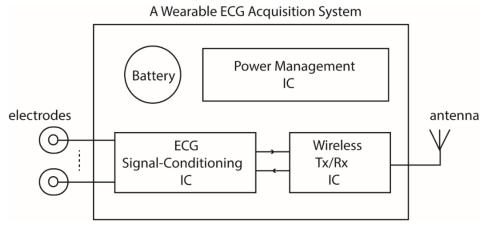

The small form factor and low power consumption of the devices require that such ECG acquisition systems be as integrated as possible. Figure 1 shows a high-level view of a lowpower small-form ECG acquisition system mentioned above. The system consists of three main parts, which can be implemented as low-power integrated circuits (ICs): i) an ECG signalconditioning IC ii) a wireless transceiver IC and iii) a power management IC. The ECG signalconditioning IC interfaces directly with electrodes and performs simple signal-conditioning tasks on the input signal. The wireless transceiver IC transmits the conditioned signal to a nearby computing platform, such as a smartphone, for further processing and also receives commands to configure the system. The power management IC supervises all the power-related tasks of the system. While all the ICs are indispensable for the complete functionality of the system, the ECG signal-conditioning IC is the bottleneck for the performance of the overall acquisition system as it determines the quality of the acquired signal. Whether the acquisition system can be used in clinical applications depends mainly on the ECG signal-conditioning IC. There are many technical challenges regarding the signal conditioning that need to be addressed before such ambulatory ECG acquisition systems come into widespread use. These challenges can be categorized as follow:

Figure 1: A low-power small-form ECG acquisition system.

Comfortability: Current Holter monitors use low-impedance wet Ag-AgCl electrodes to record ECG from the body's surface. This kind of electrode gives the highest signal quality due to its secure contact with the body through the adhesive gel. Though suitable for the diagnoses at an ECG station in a hospital setting, the gel electrode is not very suitable for the chronic monitoring application. After the electrodes are used for a long time, their adhesive gel becomes dry, causing discomfort to the user and significantly degrading the signal's quality. Thus, the majority of users may not be willing to use the device unless necessary, such as when prescribed by a physician. For less degree of discomfort, the device can use non-contact electrodes [1]. These electrodes are like clothes, which can be made as parts of the user's clothing, thus causing much less discomfort to the skin.

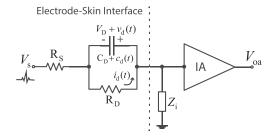

Quality of the Input Signal: Non-contact electrodes have a much higher impedance ( $G\Omega$  range) compared to that of the Ag-AgCl electrode (tens of  $k\Omega$ s range). Due to their high impedances and less secure attachment to the body, non-contact electrodes yield inferior signal qualities compared to those obtained from the Ag-AgCl electrode. If the input impedance of the front-end amplifier is not high enough, the input signal will be attenuated due to the high electrode impedance. Also, non-contact electrodes are very susceptible to motion artifacts, the baseline variations in the recorded signals induced by the movements of electrodes relative to the skin. Motion artifact is a primary concern for most wearable devices intended for use in daily activities, in which the users are not restrained to a sedentary position. Apart from the motion artifact, non-contact electrodes are also susceptible to powerline interference (50/60 Hz interference from the mains). Even with differential recording and infinite common-mode rejection, the ECG recording system may have impedance mismatches in their electrodes, thus converting the common-mode powerline interference on the body into a differential-mode signal. As a result, the output of the front-end amplifier may contain powerline interference that is much larger than the desired ECG

waveform; the large interference significantly increases the dynamic range of the input signal, which complicates the design of the signal-conditioning IC.

Power Consumption: Due to its susceptibility to powerline interference and motion artifact, the ECG acquisition system employing non-contact electrodes must accommodate a large input dynamic range, which can be several times of the desired signal's amplitude. The combined powerline interferences and motion artifact can have amplitudes on the order of tens of millivolts. In contrast, the ECG typically has an amplitude of 1 mV<sub>pp</sub> or less. The large overall input requires that the front-end amplifier of the ECG acquisition system have low gain. As a result, the analog-to-digital converter (ADC) that follows must have a high resolution to resolve the tiny ECG's features buried in the input signal—using a high-resolution ADC in the ECG acquisition system results in high overall power consumption. As a result, the acquisition system may need a larger battery, thus increasing the size and cost of the system; a large device is also less comfortable to wear on the body. As a first step to minimize the overall power consumption and, in turn, the size of the overall system, we need to minimize the required resolution of the ADC.

Output Signal Quality To record ECG waveform with diagnostic level quality, the ECG acquisition system must preserve the fidelity of the output signal even though the ADC's resolution is lowered to reduce the overall power consumption. Since reducing the ADC's resolution requires the frontend amplifier to have a high gain such that the ADC's quantization noise becomes negligible, the acquisition system must reject interferences and motion artifact within the front-end amplifier itself to prevent signal saturation at its output. Due to the limited power and area, we can only incorporate simple interference rejection algorithms on-chip; these algorithms can help reject some degrees of interferences but may distort the desired features of the ECG. Employing high-performance digital algorithms such as the Principle Component Analysis (PCA) or the wavelet transform to reject interferences may help lessen the distortion, but they are power-hungry, and their realization occupies a large chip area, thus are not suitable for low-power on-chip implementation. Our main question is how to use only these simple algorithms to reject interferences while preserving all the important features of the ECG signal.

In this research, we have designed, built, and tested a low-power ECG signal-conditioning IC suitable for acquiring ECG signals from high-impedance (dry/non-contact) electrodes. Circuit techniques and architectures are developed to preserve the important features of the ECG waveform, even when recording amidst large powerline interferences and motion artifacts. Based on the proposed IC, we have also built a prototype of a wireless ECG readout system that can

continuously record ECG from patients and send the recorded data wirelessly to a remote computer. We hope that the knowledge gained from this research will be instrumental in the design of miniaturized, low-cost wireless ECG recording systems, which, one day, can help save thousands of lives that might have been lost from cardiovascular diseases and heart failure.

## Literature Review

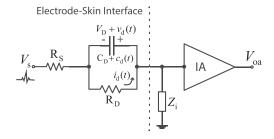

To understand the challenges high-impedance electrodes pose for the design of a lowpower ECG signal-conditioning IC, we first need to understand different types of high-impedance electrodes commonly employed in biosignal acquisition applications. The review paper [1] gives a good overview of the types of high-impedance electrodes and also discusses important issues for designing front-end amplifiers to interface to them. In a broad sense, high-impedance electrodes can be categorized into two types: 1) dry electrodes 2) non-contact or capacitive electrodes. The principle of dry electrodes is somewhat similar to that of the wet Ag-AgCl electrodes. Instead of employing explicit electrolytes, dry electrodes use moisture on the skin to act as an electrolyte. There are several dry electrodes reported in the literature [2-5]. These electrodes are based on rubber and fabric, which should provide enough flexibility for comfortable use in wearable ECG acquisition systems. However, unlike wet Ag-AgCl electrodes, which are fixed on the skin via adhesive gel, dry electrodes are more prone to movement relative to the skin. Such movement usually elicits motion artifact in the acquired ECG; large motion artifact increases the required input dynamic range of the system, thus increasing the design complexity and the overall power consumption. Besides, dry electrodes exhibit higher impedance than the wet Aq-AqCl electrodes, even though the impedance can become lower after a period of use as sweat builds up on the skin. As a result, most successful interfacing circuits employ the active electrode technique — i.e., placing a front-end amplifier right next to every dry electrode to minimize coupling from powerline interference and also minimize the front-end amplifier's input impedance — to buffer the signal and drive the cable [6]. However, this design technique may increase the overall power consumption of the system since all the front-end amplifiers must provide low enough input impedance to drive the cables; biasing the front-end amplifiers for low output impedance requires power. To obtain the best signal quality from dry electrodes, it is best to minimize the electrode impedance through some kinds of skin preparation.

In many cases, the high-resistance layer of the skin, called Stratum Corneum, can be abraded or hydrated to lower the contact resistance. To minimize the movement of electrodes relative to the skin, some electrode designs employ a layer of microfabricated needles [7, 8] to pierce through the Stratum Corneum to achieve a secure grip on the skin. It is not difficult to reason that lowering contact resistance through skin abrasion can cause discomfort to the body. As for the needle electrodes, the authors in [1] reported that such electrodes can cause skin irritation or even pain. In summary, dry electrode, requiring no adhesive gel for operation, may be a little more convenient for long-term use compared to conventional wet Ag-AgCl electrodes. However, due to the higher impedance and less secure contact to the skin, dry electrodes pose

other challenges for the design of interfacing circuits, especially when we want to avoid skin abrasion or the use of needle electrodes to maximize the usability of the ECG acquisition system. Without these techniques, our ECG signal-conditioning IC must exhibit high input impedance and must be able to handle higher levels of powerline interference and motion artifact, while consuming low power.

The other type of high-impedance electrodes, i.e., the non-contact or capacitive electrode, is even of higher interest to the PI than the dry electrode discussed earlier. This kind of electrode can sense signal through an insulating gap, such as clothing or air, between the sensor and the body; this type of electrode should offer maximum comfort when worn on the body and, thus, is a natural candidate for use in our system. Also, there are reports on the systems that use noncontact electrodes to sense biopotentials from sensors mounted on beds, chairs, or even toilet seats [9-11]. However, employing non-contact electrodes in wearable ECG acquisition systems poses even more challenges than does employing dry electrodes. The main reason is that noncontact electrodes exhibit very high source impedance, which can be thought of as consisting of small coupling capacitances (on the order of 10 pFs) and very large resistive elements (> 100 MΩ) [12, 13]. Such high source impedance poses a major challenge for the design of the frontend amplifier that interfaces with non-contact electrodes. The challenge arises because we must design the front-end amplifier to have much higher input impedance than that of the non-contact electrode to not cause strong attenuation due to the voltage division between the front-end amplifier's input impedance and the electrode's impedance. Also, even though we can design a front-end amplifier with a very high input impedance, the electrode-front-end-amplifier interface is a very high impedance node, which is highly susceptible to powerline interference. Therefore, successful systems frequently employ proper shielding and subject grounding techniques to minimize common-mode noise due to powerline [14]. We may envision that these techniques may not be so easily employed in next-generation wearable ECG acquisition systems as they may limit the use of the acquisition systems to only some constrained applications such as in a proper laboratory setting. What if the users wear the ECG acquisition systems in a noisy environment where proper shielding of the mains is not applicable? In this case, the ECG acquisition system should employ a combination of the driven-right-leg active ground technique [15], to minimize the common-mode noise, and other powerline interference cancellation techniques such as [16, 17]. It has been shown in [14] that the driven-right-leg active grounding scheme is effective in suppressing the common-mode noise even through the use of capacitive electrodes.

The major challenge posed by the use of non-contact electrodes is their susceptibility to motion artifact. Even though there are reports on successful systems employing non-contact electrodes in moving subjects [18, 19], these systems use a tight vest and chest band to minimize electrode movement with respect to the body. Without a means to secure the non-contact electrodes in place, the problem of how to cleanly remove motion artifact from the desired signal is still unresolved. In general, there are three main sources of motion artifact due to the use of non-contact electrodes: 1) large time constant of the high-impedance input node 2) electrode-toskin displacement 3) friction between the electrode and insulation. Among these sources, friction is the most serious one since it can cause large voltage excursion at the high-impedance input node. Besides, there is no known solution to correlate the frictional action to its induced motion artifact in the acquired signal. Coupled with the large time constant of the high-impedance input node, the friction-induced motion artifact may cause prolonged signal saturation at the output of the front-end amplifier if its gain is too high. Therefore, the use of one high-gain front-end amplifier, though most efficient in terms of the power-noise tradeoff, may not be the best solution for ECG acquisition systems that employ non-contact electrodes. In this case, the use of distributed-gain front-end amplifier with some forms of motion artifact suppression should prove a more viable candidate. For the motion artifact induced by electrode-to-skin displacement, the authors of [20] proposed a simple method to suppress this type of motion artifact. However, the method relies on the precise knowledge of the electrode-to-skin coupling capacitance. We can thus argue that such a method is effective only in simulations and prepared experimental settings. In this research, we investigate an effective way to prevent signal saturation due to motion artifact, without relying on the precise knowledge of the motion-artifact-causing mechanisms.

Most of the reported ECG signal-conditioning circuits are designed for use with conventional wet Ag-AgCl electrodes, thus are not designed for a large enough input dynamic range necessary for high impedance electrodes. Here we consider a few notable systems, with an emphasis on the recording of the raw ECG since it is most relevant to clinical applications. In [21], the authors present quite a complete analog signal processor chip, consisting of one ECG readout channel for streaming out the raw ECG data, one band-power extraction channel for detecting heartbeats, one continuous-time impedance monitoring channel to detect whether the electrodes make proper contact with the body. The impedance monitoring channel can also be used for the suppression of motion artifact, as will be discussed later. The system contains one 11-bit successive-approximation-register (SAR) ADC, which is shared by all the three channels. The overall system, implemented in a 0.5-  $\mu$ m CMOS process, consumes only 30  $\mu$ m from a supply voltage of 2 V. The ECG readout channel, which we are most interested in, provides four

gain settings ranging from 300 to 1300. This method of gain programmability is employed to increase the dynamic range of the input. The system can use the highest-gain setting if the input is clean (containing only ECG waveform whose amplitude is lower than 1 mV<sub>pp</sub>), while it can switch to the lower-gain settings if the input contains large motion artifact and powerline interference. There are two drawbacks to this approach. First, notice that the system employs quite a high-resolution ADC (11-bit), which consumes a large chip area and a high power. The main reason for utilizing such a high-resolution ADC is the low gain of the signal path. As a rule of thumb, the ADC's quantization noise referred to the input of the system should be less than the input-referred noise of the front-end amplifier. In most systems, the front-end amplifiers are designed to provide input-referred noise lower than 1  $\mu V_{ms}$ ; this is to provide around 60 dB signal-to-noise ratio (SNR) for the ECG signal with 1-m $V_{pp}$  amplitude). For the signal path's gain of only 300, we require an ADC with at least 11 bits to keep the input-referred ADC's quantization noise below that of the front-end amplifier. In this system, the ADC's resolution is chosen based on the worst-case input, which requires a gain of 300 in the signal path. The overall system should be more power-efficient if we can use an ADC with a much lower resolution, regardless of the amplitude of the input. The second drawback of this variable gain approach is that the system requires supervision by the user, which can be very inconvenient in practice. Otherwise, some forms of automatic gain control must be incorporated into the system, which increases the design complexity. In fact, the system in [21] does not include any form of automatic gain control, suggesting that gain calibration is performed manually by the user.

There are other works that employ the variable gain approach with a relatively high-resolution ADC. The work in [22], the follow up of the work in [21], utilizes even lower gains in the signal path (75-300), but compensate for the lower gain with a higher resolution ADC (12-bit SAR ADC). The system consumes 17  $\mu$ W per channel from a 1.2 V supply for the raw data recording mode; such power consumption is quite impressive among systems that employ such a high-resolution ADC. The reason for such power efficiency is the use of the SAR topology. However, their ADC achieves an integral nonlinearity (INL) of almost 4 LSB, suggesting that the chosen SAR topology is practically not suitable for the 12-bit resolution. In this case, the  $\Sigma\Delta$  topology is a more suitable choice. Another system [23] utilizes the variable gain approach with the gain ranging from 22-46 dB. It incorporates a 12-bit  $\Sigma\Delta$  ADC to compensate for the low gain of the signal path. The system consumes 100  $\mu$ W per channel, while the ADC alone consumes 46  $\mu$ W, emphasizing the disadvantage of  $\Sigma\Delta$  ADCs to SAR ADCs in terms of power efficiency. However, given such a high resolution requirement, the  $\Sigma\Delta$  topology is a more natural choice since it is difficult to implement SAR ADC with a resolution of higher than 10 bits due to the

stringent component matching requirement. We thus emphasize that, to avoid the use of a high resolution ADC, we should maximize the overall gain of the signal path. Another low-power ECG signal-conditioning system that is worth mentioning is the work in [24]. This system, with 2 channels of ECG recording, consumes a total power of 74.8  $\mu$ W from a 0.7-V supply. It is interesting to see that the system utilizes the signal path's gain that ranges from only 36-44 dB, but employs a SAR ADC with only 8 bits of resolution. As reported in [24], using such low-resolution ADC with a low signal path's gain comes at a price of almost 6.9  $\mu$ V<sub>rms</sub> noise referred to the input of the system — most systems are designed for input-referred noise of around 1  $\mu$ V<sub>rms</sub>.

Even with standard wet Ag-AgCl electrodes, the ECG acquisition systems mentioned thus far employ relatively low gains in their amplification stages followed by relatively high-resolution ADCs to achieve appropriate input dynamic range, but at the cost of the overall higher power consumption. With high-impedance electrodes, motion artifact and powerline interference will increase the input dynamic range even further. Does this mean that we have to use even a lower gain in the amplification stage and a higher-resolution ADC? This approach would, of course, incur even higher power consumption in the overall system. To reduce the input dynamic range, we should suppress the motion artifact and powerline interferences at the front-end amplifier. Here, let's review some systems that incorporate schemes to suppress motion artifact right at the front-end amplifier. Though these systems are not designed for use with high-impedance electrodes, the ideas presented apply to our proposed system as well. It has been shown in [25] that motion artifact has some correlation with variation in the electrode impedances caused by the user's movement. Thus, we can use an adaptive filtering scheme to find the correlation between the variation in the electrode impedances and the motion artifact in the recorded signal. Such correlation can be used to derive a nulling signal from the variation in the electrode impedances; we can then subtract this nulling signal at the input of the front-end amplifier such that its output is virtually free of motion artifact. There are some works [25, 26] that use adaptive filters with simple least-mean-square algorithms to perform motion artifact removal. But these algorithms are employed in the digital backend; thus, they would not help reduce the input dynamic range of the front-end amplifier. To take the adaptive filtering idea a step further, [27-29] propose a topology that can remove the motion artifact right at the front-end amplifier. The topology performs adaptive filtering on the digitized data using a low-power microcontroller (MSP430 from Texas Instrument) to obtain the nulling signal, then feeds the nulling signal back to cancel with the motion artifact at the input of the front-end amplifier through an on-chip digitalto-analog converter. These methods were shown to be effective, thus helping reduce the required input dynamic range of the system. However, the main drawback of this method is that it requires a strong correlation between the variation in the electrode impedances and the motion artifact in the acquired signal. From what we have experienced in our research, such strong correlation is quite rare in normal usage of the system — such as while running or walking. The only case that we obtain a strong correlation is when we intentionally push and release electrodes in a pulsatile manner. Therefore, adaptive filtering might not be a viable choice for suppressing motion artifact at the front-end amplifier. In this research, we seek another more effective strategy.

Powerline interference is a major concern in most biosignal acquisition systems. Most of the time, we can view powerline interference as the common-mode noise into the input of the system. To minimize powerline interference, most ECG acquisition systems use differential-input topologies for their front-end amplifiers to achieve a high common-mode rejection ratio (CMRR). The works in [30-32] achieve a CMRR on the order of 120 dB at 50 Hz. Another method that is normally employed to minimize powerline interference is to suppress the common-mode noise on the user's body directly. To achieve this, we can use a technique called the driven-right-leg (DRL) that uses negative feedback to set the common-mode voltage on the body and suppress the common-mode noise [15, 33]. In practice, a combination of high-CMRR front-end amplifier and the DRL technique should be applied to suppress this common-mode noise. However, in practice, there exist numerous coupling paths between the mains and the electrodes, creating differential-mode noise at the input of the front-end amplifier. We should thus assume that there always exists differential-mode noise at the input, which cannot be suppressed by a high-CMRR front-end amplifier. A promising approach to suppress the differential-mode interference is to apply a nulling signal to the input of the front-end amplifier to suppress the interference in a feedback manner [16, 34]. This approach effectively creates a notch, at the interference's frequency, in the transfer function of the signal path. However, the current implementation of this approach requires power-hungry circuits such as a phase lock loop and analog multipliers [16] or require an off-chip digital processor to implement full-blown digital filters [34], thus making them unsuitable for ultra-low-power implementation in our system. Toward this aim, we have designed a low-power mixed-signal architecture for powerline interference cancellation [17]. This architecture consumes less than 1 µW of total power. We will use the knowledge gained from designing this architecture for suppressing the powerline interference in our proposed ECG signalconditioning IC.

## **Objectives**

- To develop a new architecture of a low-power ECG signal-conditioning IC for use in wearable ECG acquisition systems.

- 2. To develop new knowledge and architectures on the integrated-circuit building blocks for acquiring ECG signals.

- To demonstrate a high-performance, fully-functional ECG signal-conditioning IC that can record ECG signals from high-impedance electrodes while consuming less than 10 microwatts of power.

## Methodology

## **General Considerations**

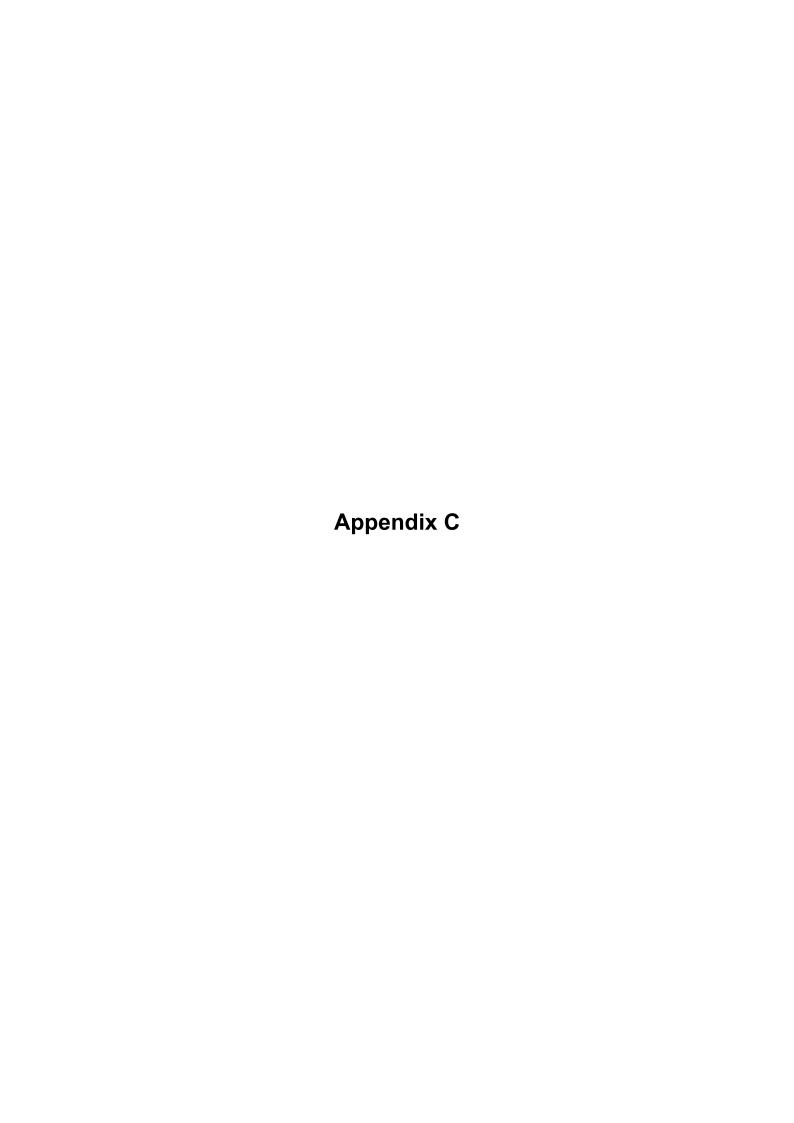

Powerline interferences and motion artifact makes the design of an ultra-low-power ECG signal-conditioning IC for high-impedance electrodes difficult. At the electrodes, these interferences can have amplitudes on the order of tens of millivolts while the ECG waveform itself has an amplitude on the order of 1 mV or less. Thus, the signal-conditioning IC must have a high dynamic range to accommodate those large interferences while being able to resolve tiny features of the ECG waveform. In advanced IC processes, the supply voltage is on the order of 1 V. The conventional approach to acquiring ECG at the presence of large interferences is to employ a front-end amplifier with a relatively low gain (40 dB or less) to ensure no signal saturation at the front-end amplifier's output and then use a high-resolution ADC to resolve the tiny ECG features in the amplified signal.

Let's suppose that the input into the signal-conditioning IC, which operates from a 1.2-V supply voltage, has an amplitude of around 10  $\mathrm{mV}_{\mathrm{pp}}$  due to powerline interferences and motion artifact. Let's also assume that the ECG waveform has an amplitude of 1 mV<sub>pp</sub>, resulting in the combined input into the signal-conditioning IC with an amplitude of around 10 mV $_{pp}$ . Also, let's suppose that, to prevent signal saturation at the output of the front-end amplifier operating from a 1.2-V supply voltage, the front-end amplifier can have a gain of at most 40 dB which results in the output's amplitude of 1 V<sub>pp</sub>, almost the rail-to-rail level of the front-end amplifier. Suppose that the front-end amplifier has an input-referred noise of 1  $\mu V_{ms}$ , i.e, 100  $\mu V_{ms}$  at the front-end amplifier's output and, in turn, at the ADC's input. As a rule of thumb in choosing the ADC's resolution, the ADC's quantization noise should be negligible compared to the noise introduced by the front-end amplifier. For the ADC's full-scale voltage ( $V_{FS}$ ) of 1.2 V whose quantization noise ( $V_Q$ ) can be approximated as  $V_Q = V_{FS} / \left(2^N \sqrt{12}\right)$  where N is the effective number of bits, we require N>11.8 for  $V_O$  to be less than the noise due to the front-end amplifier. In practice, we should use N>13 for the quantization noise of the ADC to be negligible compared to the frontend amplifier's noise. The most commonly-used ADC in a low-power biosignal acquisition system is the SAR type due to its excellent power efficiency at low-to-moderate speed. This type of ADC employs a capacitive digital-to-analog converter (DAC) in feedback to help determine the output bits in the successive approximation fashion. The accuracy of SAR ADCs is normally limited by the matching accuracy of capacitances in the capacitive DAC. The matching accuracy of passive components in an IC process is rarely better than 0.1 % even with a careful layout. Thus, the SAR ADC's resolution is normally limited to 10 bits, without digital calibration. To achieve a

resolution of better than 13 bits, we normally employ the  $\Sigma\Delta$  topology to implement the ADC. Since the  $\Sigma\Delta$  ADC utilizes oversampling and noise shaping — these are power hungry digital techniques — to achieve a high resolution, its energy consumption per quantization level is significantly higher than that of a SAR ADC. Therefore, incorporating a 13-bit  $\Sigma\Delta$  ADC in the signal-conditioning IC will prove prohibitive in terms of power. In this research, we will seek a better alternative.

The most energy-efficient way to minimize the required ADC's resolution is to use a high gain in the amplification stage. For example, if the amplifications stage provides a gain of 2000 (66 dB) and an input-referred noise of 1  $\mu$ V $_{rms}$ , the noise level due to the amplification stage will be 2 mV $_{rms}$  at the ADC's input. An ADC with a full-scale voltage of 1.2 V and a resolution of 8 bits has a quantization noise of 1.35 mV $_{rms}$ , which is already less than the 2 mV $_{rms}$  noise from the amplification stage. Thus, with the amplification stage's gain of 66 dB, an 8-bit ADC is sufficient for use in the system. Ultra-low-power 8-bit SAR ADCs are very common in the literature. During his Ph.D. work, the PI designed a low-power 8-bit SAR ADC using custom digital logics for use in a neural recording system [35]; this ADC consumes energy per quantization level of 80 fJ. If this ADC were to be used in the system to digitize the ECG waveform at a sampling rate of 300 samples/second, it would consume a total power of only 6.14 nW; this power proves negligible in the signal-conditioning IC and further reduction of this power is no longer necessary.

## The Proposed Architecture of The ECG Signal-Conditioning IC

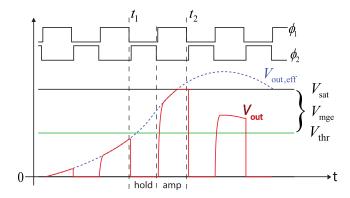

Nevertheless, how can we amplify a  $10\text{-mV}_{pp}$  input signal by a gain of 2000 in a system with the supply voltage of only 1.2 V. Our proposed solution is to cancel large interferences at a node within the front-end amplifier and use a signal-folding technique in the wide-output-range to keep the output signal within its output range. Even with perfect interference cancellation, effectively, the input signal's amplitude will be attenuated from  $10 \text{ mV}_{pp}$  down to  $1 \text{ mV}_{pp}$ , the amplitude of the ECG waveform, which still saturates the amplifier chain with a gain of 66 dB ( $1 \text{ mV}_{pp}$  input signal results in an effective output swing of  $2 \text{ V}_{pp}$ ). To prevent such output saturation, we will use a signal-folding scheme [36, 37] in which we place a circuit in the feedback path to monitor the output level of the wide-output-range amplifier and add appropriate correction voltages to a node within it such that the output level of the wide-output-range amplifier stays within the supply rails.

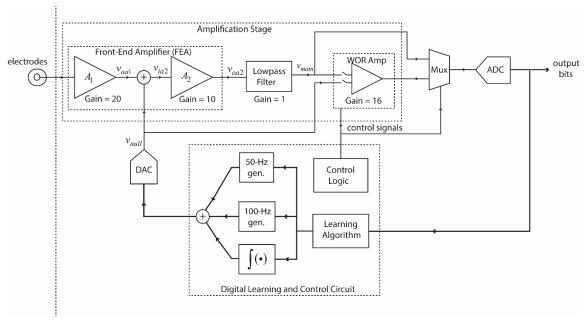

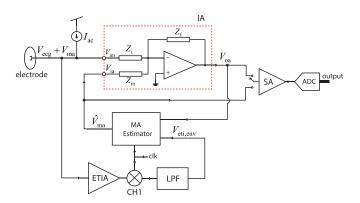

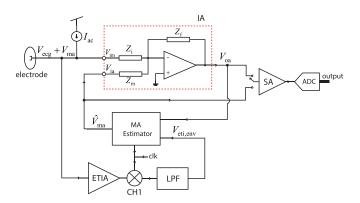

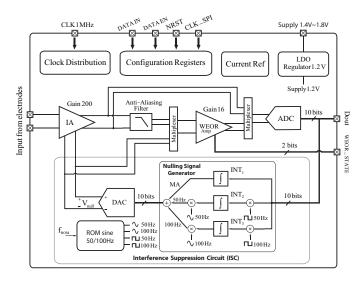

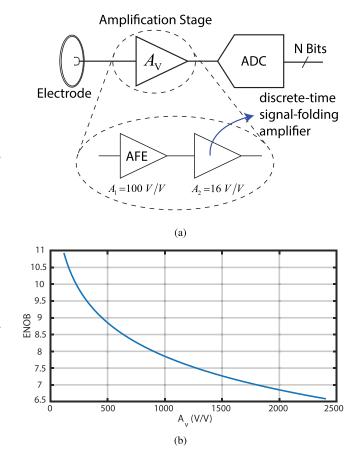

Figure 2: System architecture of the ECG signal-conditioning IC.

Figure 2 shows the conceptual idea of our proposed signal-conditioning IC. The IC consists of the amplification stage, an ADC, a digital learning and control circuit, and a digital-toanalog converter (DAC). The amplification stage consists of an front-end amplifier (in the dashed box), a lowpass filter, and a wide-output-range amplifier (WOR Amp). The front-end amplifier consists of two gain stages  $A_1$  and  $A_2$ ;  $A_1$  provides a gain of 20 (26 dB) while  $A_2$  provides a gain of 10 (20 dB). The choice of the gain of  $A_{\parallel}$  is to ensure that it is high enough such that the inputreferred noise of  $A_2$  is negligible when referred to the input of  $A_1$ . The gain of  $A_1$  is also chosen low enough to prevent signal saturation at the output of  $A_1$  even with large interferences at the input: a 15-mV<sub>pp</sub> input signal at the input of  $A_1$  only results in a 300-mV<sub>pp</sub> signal at the's output, which is easily handled by a standard amplifier operating from a 1.2-V supply voltage. To prevent signal saturation at the output of  $A_2$ , the system will suppress the interferences before the signal is amplified by the amplifier  $A_2$ . This suppression is shown in Figure 2 by the superposition of the output signal of  $A_1$ ,  $v_{oal}$ , and another signal,  $v_{null}$ . The signal  $v_{null}$  is the result of a learning feedback algorithm in the digital learning and control circuit that observes the output of the ADC and adapts  $v_{null}$  until it sufficiently suppresses interferences in  $v_{oal}$ . Once the feedback algorithm converges, the input into  $A_2$ ,  $v_{ia2}$ , will consist mainly of the components from the desired ECG, and probably with little remnants of the interferences. After interference suppression, if the amplitude of  $v_{ia2}$  is no larger than 60 mV<sub>pp</sub>, assuming some remnants of the interferences, the amplitude of the output of  $A_2$ ,  $v_{oa2}$ , will be smaller than 600 mV<sub>pp</sub>, which is still within the supply rails of an amplifier with a supply voltage of 1.2 V.

To amplify the output of  $A_2$  further, we will pass it to the discrete-time amplifier called the wide-output-range amplifier (WOR amp) whose gain is 16 (24 dB). Note that the amplifier  $A_1$  and  $A_2$  are continuous-time amplifiers while  $v_{null}$  is generated from a DAC. Therefore,  $v_{oa2}$  will contain high-frequency contents due to the switching activities within the DAC. To prevent aliasing due to the sampling of  $v_{oa2}$  by the WOR amp, we use a lowpass filter to filter out the high frequency contents in  $v_{oa2}$  before feeding the signal into the WOR amplifier's input. Also notice that the total gain of the amplifier chain is now  $200 \times 16 = 3200$  (70.1 dB). Assuming an input-referred noise of the front-end amplifier of 1  $\mu V_{rms}$ , the noise due to the front-end amplifier at the ADC's input will be 3.2 mV<sub>rms</sub>. An 8-bit ADC with a full-scale voltage of 1.2 V has a quantization noise of 1.35 mV<sub>rms</sub>. Therefore, with this choice of the gain of the amplification stage, it is sufficient to use an 8-bit ADC to digitize the acquired signal, thus lowering the power of the overall system. In section **Error! Reference source not found.**, we will explain the operation of the WOR amplifier that prevents signal saturation at its output.

The major effort of this research is on the design and implementation of the architecture in Figure 2. For this research, we have published the explanation of the overall architecture and some of the measured results in [38]. As [38] is only a conference paper, we did not have enough space to delve into details of the important circuit blocks. For the 3-year period of this research, we only have enough time to go into details of the design and test of three important circuit blocks, including 1) the motion artifact estimator 2) the wide-effective-output-range amplifier and 3) the front-end amplifier. The motion artifact estimator is intended for use in the feedback path of the architecture in Figure 2. However, due to some robustness issues, we decided to replace it with just an integrator to create a lowpass response that helps filter out the motion artifacts. Nevertheless, our in-depth analysis on the design of the motion artifact estimator results in a journal publication [39] in the IEEE Transactions on Biomedical Circuits and Systems, which is one of the foremost publication in the field of biomedical circuits and systems design. The wideeffective-output-range amplifier garners more success in the architecture as it is the instrumental block in allowing us to achieve the high gain required without saturating the signal chain. We have presented our in-depth analysis and the measured results of this important circuit block in another journal article [40]. Finally, at the time of this report writing, we are still writing the third journal article of the project, particularly on the design of the front-end amplifier and its use in our proposed high-gain architecture with high impedance electrodes.

## **Results**

We can divide the main results from this project into four parts. The first three parts are on the design of the architecture and its circuit blocks. The fourth part is on the design of a wireless ECG recording prototype, which demonstrates the functionality and the effectiveness of the proposed IC. In this section, we provide a summary of each part of the results. Interested readers are referred to the conference paper and the journal articles in the report's appendices for further details.

## The High-Gain ECG Readout Architecture

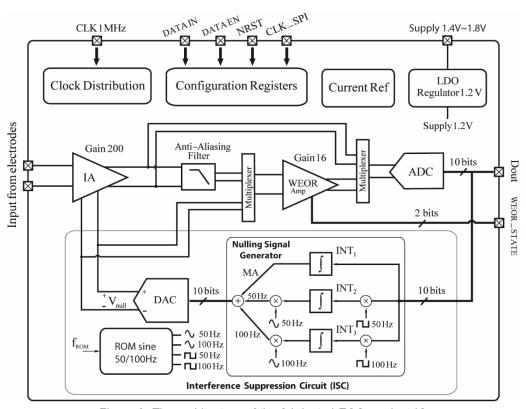

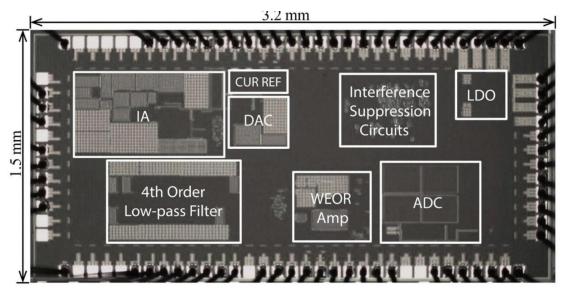

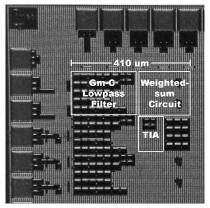

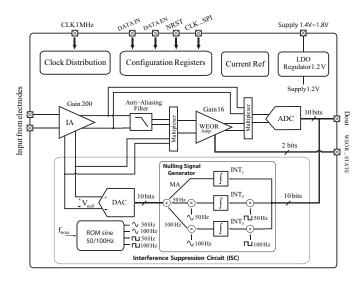

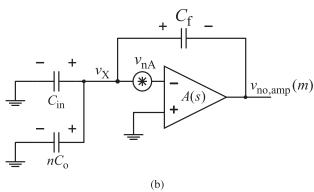

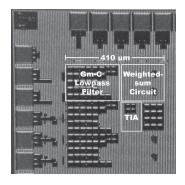

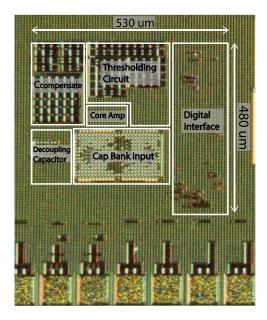

This part of the research involves the overall design of the ECG readout architecture. The actual architecture that we have built for this research project is shown in Figure 3. This IC is fabricated in a  $0.18~\mu m$  CMOS process from United Microelectronic Corp, whose chip micrograph is shown in Figure 4.

Figure 3: The architecture of the fabricated ECG readout IC

Figure 4: Chip micrograph of the ECG readout IC

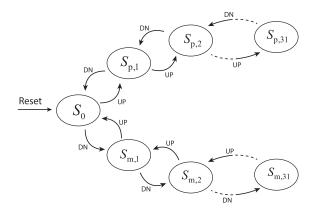

The central thesis of this architecture is the use of a very high gain (70 dB) in the amplification stage to reduce the resolution requirement of the ADC. The amplification stage consists of the instrumentation amplifier (the IA) with a gain of 46 dB and the wide-effectiveoutput-range amplifier (WEOR amplifier) with a gain of 24 dB. Due to such high gain, the required ADC's resolution is only 8 bits for its noise and distortion to be negligible when referred to the input of the readout system. However, we reason that the benefit of a very high gain comes the risk of signal saturation in the presence of large interferences—i.e., the motion artifacts and powerline interferences—at the input. Hence, to prevent such saturation, we incorporate an interference suppression circuit, which feeds back cancellation signals to the IA to suppress the interferences. The interference suppression circuit consists of a digital nulling signal generator and a digital-to-analog converter (DAC) to produce an analog cancellation signal that is fed back to cancel with the interferences at an internal node within the IA. The nulling signal generator consists of three components. The 50-Hz and 100-Hz sinusoidal generators produce sinusoidal waveforms whose frequencies and amplitudes are the same as but whose phases opposite to those of the first and second harmonics of the powerline interferences. The integrator extracts the low-frequency components of the output, which, after being fed back to the IA, creates the overall lowpass transfer function to filter out the motion artifact. To implement this signal nulling generator, we utilize the direct digital synthesis (DDS) approach and an adaptive least-meansquare algorithm to adjust the amplitudes and phases of the outputs to achieve good interference suppression. The chip also contains other peripheral circuits such as a low dropout voltage regulator to provide a stable and clean 1.2-V supply to the chip from a 3.3-V battery voltage, and

the clock distribution circuit to provide clock signals to the WEOR amplifier and the digital circuits on chip.

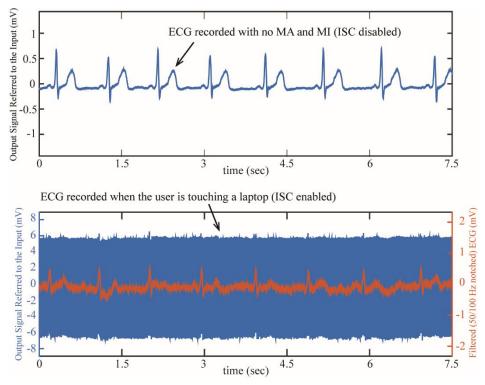

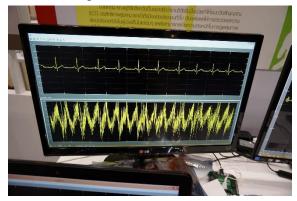

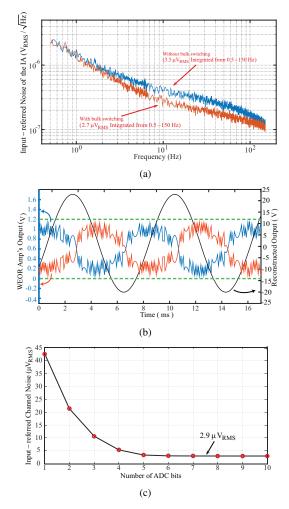

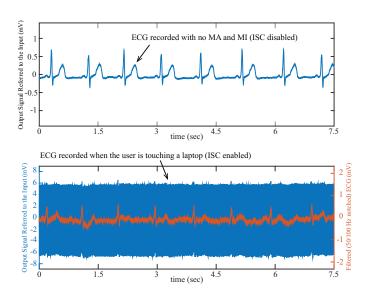

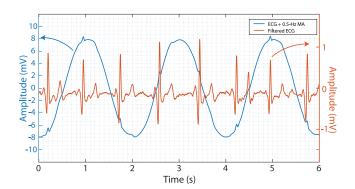

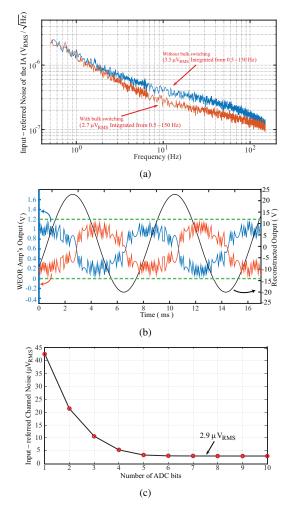

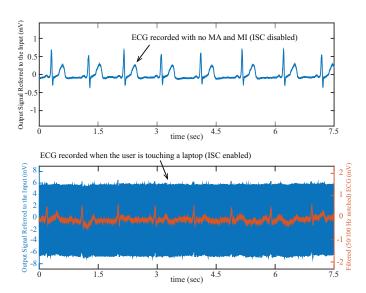

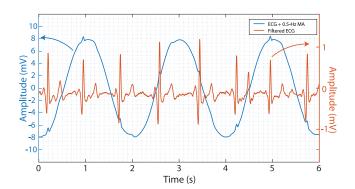

Figure 5: ECG Recording from the proposed ECG readout IC

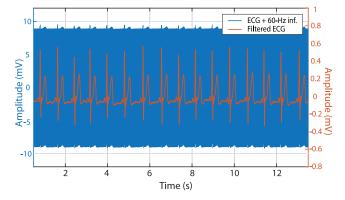

The fabricated readout IC functions as we expected. The IC can record ECG amidst large interferences without saturating the signal chain. To demonstrate this, we use the IC to record ECG while the user was touching a laptop plugged into an electrical wall outlet. The result is shown in Figure 5. Despite the high gain of 70 dB, the IC was able to record the 12-mV<sub>pp</sub> ECG-plus-interferences without saturating the signal (blue curve of the bottom figure), thanks to the use of the Interference Cancellation Circuit (ISC). Since no saturation occurs, all the information of the ECG is preserved, thus allowing us to post-process the recorded signal in the digital backend to recover the desired ECG. After filtering the recorded signal in the digital backend, we obtained the ECG shown in the red curve of the bottom figure. We can see that the filtered ECG is somewhat noisy. We finally found that the noise is due to the imperfect reconstruction scheme used in reconstructing the original signal from the nulling signal. Nevertheless, the QRS complex of the ECG waveform is still well preserved. Therefore, we reason that though the proposed interference cancellation architecture is not yet ready for clinical-quality recording due to it distorting the ECG waveform, the scheme can still be useful in some non-demanding applications such as in heart rate detection for fitness and sports.

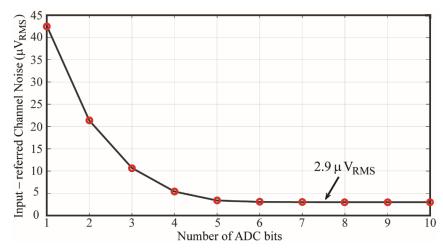

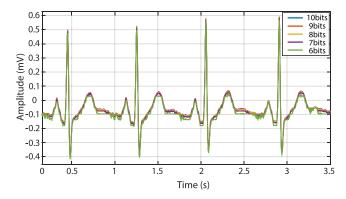

Figure 6: Input-referred noise of the readout system vs. the ADC's resolution

However, the finding above demands us to question our assumption about the need for interference cancellation. The distortion in the waveform is due to the imperfect reconstruction process of combining the nulling signal and the output of the WEOR amplifier. We have argued that we need this process when the interferences are large such as when the user is touching poorly-grounded electrical appliances. We finally figured out later that such large powerline interference occurs when the readout system has a low-impedance path from its ground to earth ground. However, in the real wireless recording environment, such scenario does not usually happen, as the readout system's ground and the earth ground are normally isolated. Therefore, in wireless ECG recording, the interference cancellation circuit may not be necessary. If that's the case, we can use our high-gain architecture to record the ECG without the worry of signal saturation, thanks to the very wide input range of the WEOR amplifier. With this architecture, we only need an ADC with a resolution of 7 bits. An example of ECG waveform recorded by the IC when the Interference Suppression Circuit is not used is shown in the top figure of Figure 5. To show that we only need the resolution of 7 bits in the ADC, we record the ADC's output and calculate the input-referred noise of the readout system while discarding the least significant bits from the output samples. The plot of the system's input noise vs. the number of ADC's bits is shown in Figure 6. We can see that when the number of ADC's bits is above 7, the noise floor remains relatively constant. But when the number of ADC's bits decreases below 6, the noise floor starts to increase. Hence, we can conclude that the ADC's resolution of higher than 7 bits is no longer necessary since the high gain of the amplification stage makes the ADC's noise negligible compared to the noise of the amplification stage when referred to the input.

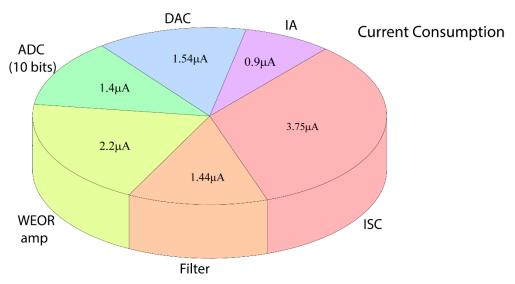

Figure 7: Current breakdown between the circuit blocks of the ECG readout IC

The proposed ECG readout IC consumes very low power. Figure 7 shows the power breakdown among the circuit blocks of the IC. We can see that the overall IC consumes a total current of 11.23  $\mu$ A, 3.75  $\mu$ A of which is dedicated to the operation of the ISC. Thus, if the ISC is not needed, the total current of the chip would amount to 7.48  $\mu$ A, or an equivalent total power consumption of 9  $\mu$ W from a 1.2-V supply. For further information on the design of this IC, please refer to [38].

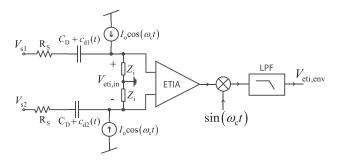

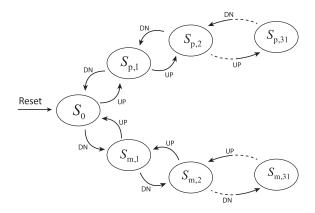

## The Micropower Motion Artifact Estimator

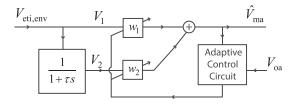

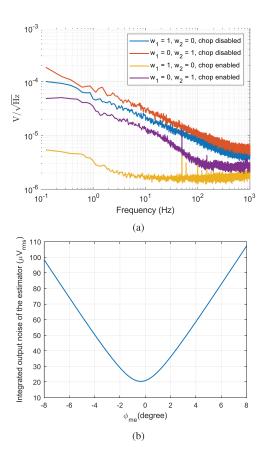

The next part of the results for this research involves the nulling signal generator in the architecture of Figure 2. The nulling signal generator in Figure 2 uses jus an integrator to create a highpass transfer function in the overall amplification chain. This method is only a crude way of removing motion artifacts (by just highpass filtering it out), and thus requires a reconstruction process to recover the original signal. This reconstruction process can also add distortion to the recorded signal unless the digital-to-analog converter used is of a very high resolution. Hence, to avoid this issue, we proposed the use of a low-power mixed-signal motion artifact estimator that can be used to estimate the motion artifact in the input signal accurately. This estimate can then be subtracted from the input signal near the front of the signal chain to prevent signal saturation if the input signal is to undergo large amplification. The architecture employs an adaptive filtering technique with low-power analog filters to create the nulling signal from the output of the IA. Thus, the output of the architecture is already in the analog form; therefore, a DAC is not required to create an analog nulling signal from its digital counterpart. Though its output is analog, the architecture employs a digital adaptation algorithm to avoid the use of large analog integrators in

adjusting the weights of the filters. This design choice results in a compact architecture, which makes it feasible to include the proposed estimator on chip.

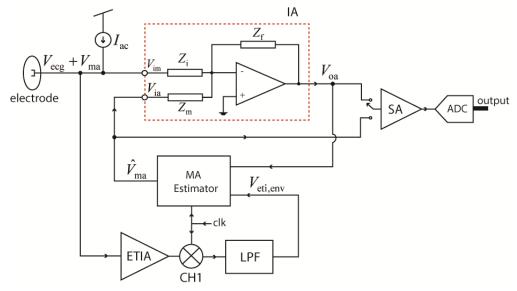

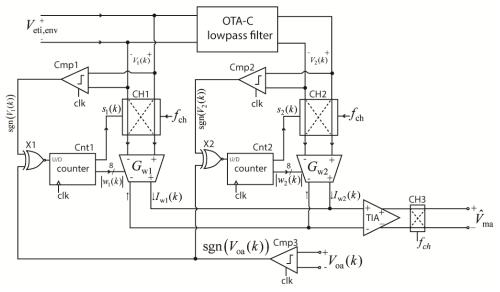

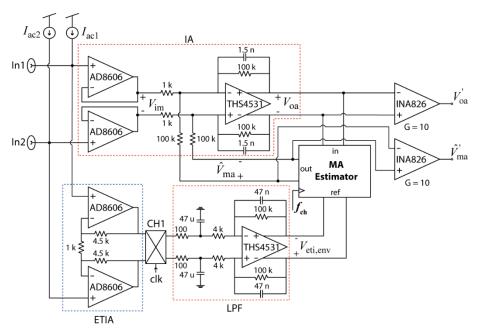

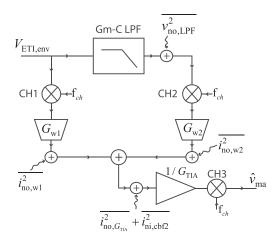

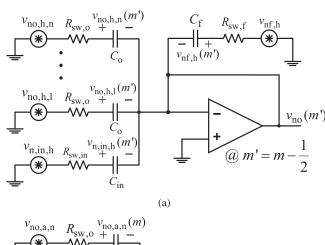

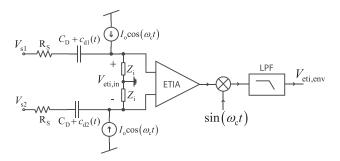

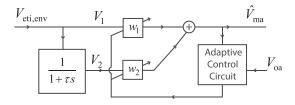

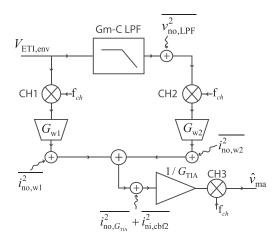

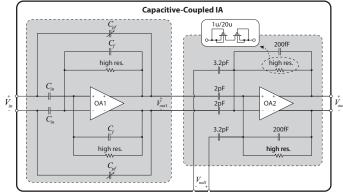

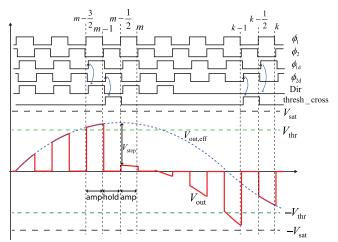

Figure 8: The architecture of the proposed motion artifact estimator

Figure 8 shows the concept of the proposed motion artifact estimator. The estimator produces its output  $V_{\rm ma}$  by utilizing two sources of information: the output of the IA,  $V_{\rm oa}$ , and the envelope of the electrode impedance information  $V_{\rm eti,env}$ . For this scheme to work, we have assumed that the motion artifact in the recorded signal has a strong correlation to  $V_{\rm eti,env}$ . Thus, the estimator should be able to use  $V_{\rm eti,env}$  to produce its output which is a reasonable estimate of the motion artifact in the recorded signal. To know whether the estimator's output is already optimal, we need to observe  $V_{\rm oa}$  and let the adaptive circuit in the estimator adjust the weights of the analog filters until the mean-square-error of  $V_{\rm oa}$  is minimized.

To obtain  $V_{\rm cti,env}$ , we inject an AC current,  $I_{\rm ac}$ , into the electrodes. The variation in electrode impedance due to motion then results in an amplitude-modulated waveform at the input of the IA, with the carrier frequency (modulating frequency) equal to that of the AC current source. To extract the envelope of this modulated signal, we amplify it with an electrode-impedance-information (ETI) amplifier and then demodulate the resulting signal with the chopper switch CH1. The demodulated signal is then lowpass filtered to provide the electrode impedance information into the estimator.

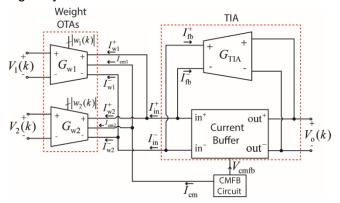

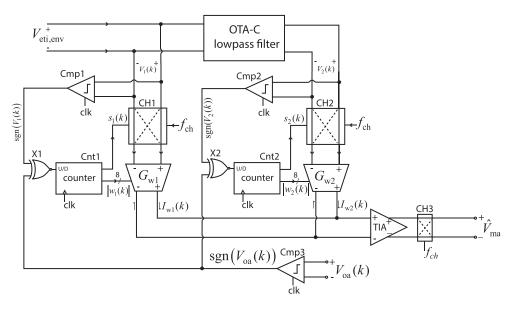

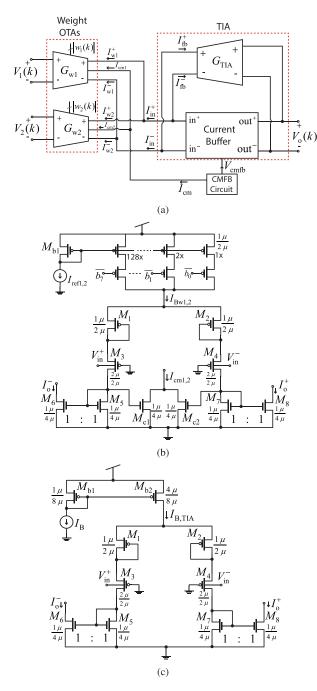

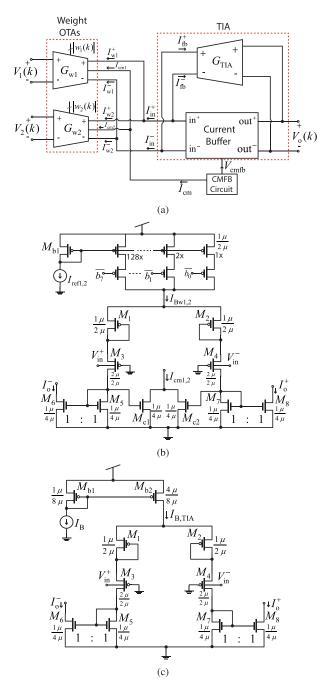

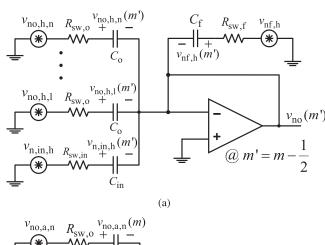

Figure 9: The architecture of the proposed MA estimator

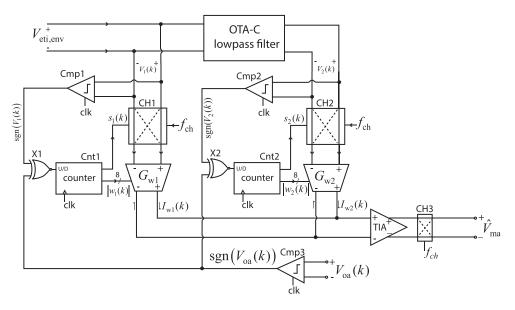

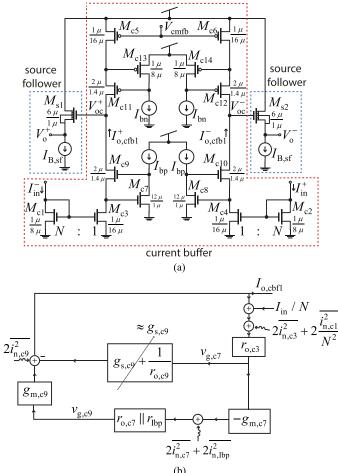

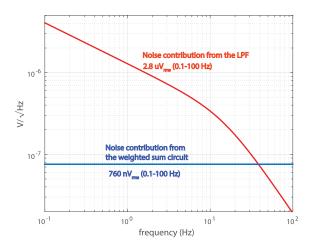

In this part of the research, we have proposed for the MA estimator a mixed-signal architecture shown in Figure 9. The core of the estimator is the transconductance-capacitance (OTA-C) lowpass filter to create two basis functions for producing  $V_{\rm ma}$ —the two basis functions are  $V_1(k)$  and  $V_2(k)$ . The main function of the OTA-C lowpass filter is to create a relative phase shift between these two bases. To produce the output of the estimator, the architecture linearly combines the two bases with adjustable weights provided by the two weight transconductors  $G_{\rm w1}$  and  $G_{\rm w2}$ . To adjust the weights, we use an adaptive algorithm to adjust the effective transconductances of the weight transconductors in a discrete-time fashion—via the up-down counters Cnt1 and Cnt2. To minimize the flicker noise of the two transconductors, we also apply chopper stabilization through the chopper switches CH1-CH3. We then sum the output currents of the weight transconductors and pass the result to a transimpedance amplifier (TIA) to provide the output voltage  $V_{\rm ma}$ .

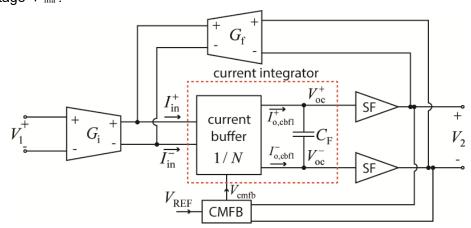

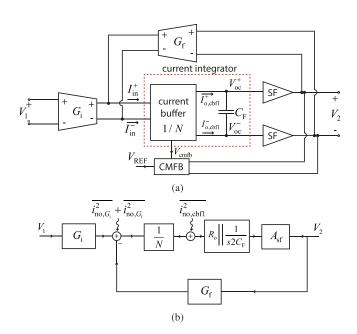

Figure 10: High-level schematic of the OTA-C lowpass filter

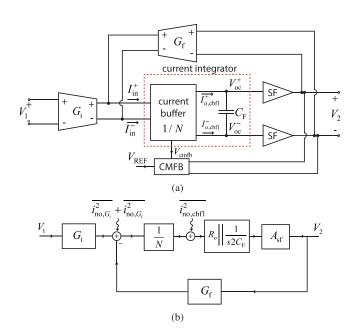

Figure 10 shows the high-level schematic of the OTA-C lowpass filter. It consists of the input OTA,  $G_{\rm i}$ , and the feedback transconductor,  $G_{\rm f}$ . The output currents of the two OTAs are then buffered by the current buffer, before charging the integrating capacitor  $C_{\rm F}$ . The overall transfer function of the OTA-C lowpass filter is given by

$$\frac{V_{\rm o}}{V_{\rm i}} = \frac{G_{\rm i}}{G_{\rm f}} \frac{1}{1 + s / \omega_{\rm f}},$$

where  $G_{\rm i}$  and  $G_{\rm f}$  are the effective transconductance of the input and the feedback OTA. The main challenge in the design of this architecture is that we need the cutoff frequency,  $\omega_{\rm f}$ , to be very small—on the order of less than  $2\pi \left(10\,{\rm Hz}\right)$ —which makes the design of  $G_{\rm i}$  and  $G_{\rm f}$  OTA difficult since we need to bias them with a very small current. Therefore, we need to apply many degeneration techniques to reduce their effective transconductances—such as using the bulk input and the source degeneration—to reduce the effective transconductances of the two OTA without biasing them with excessively small bias currents.

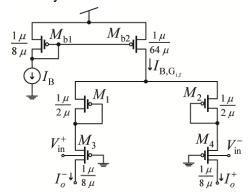

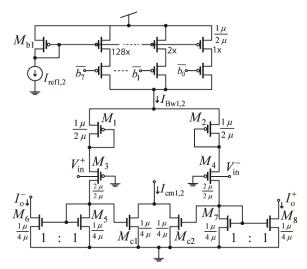

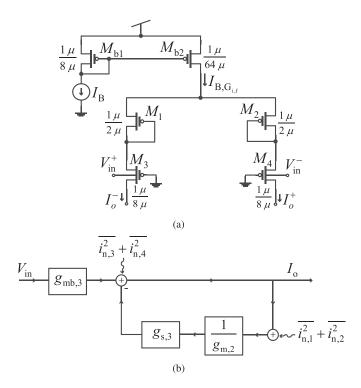

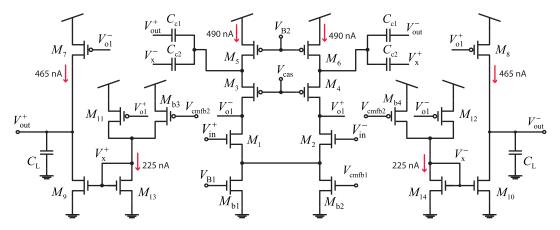

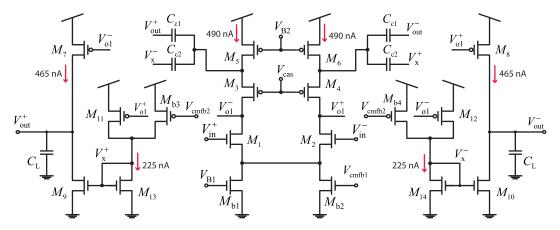

Figure 11: Schematic of the  $G_{\rm i}$  and  $G_{\rm f}$  OTAs

Figure 12: Schematic of the current buffer used in the OTA-C lowpass filter

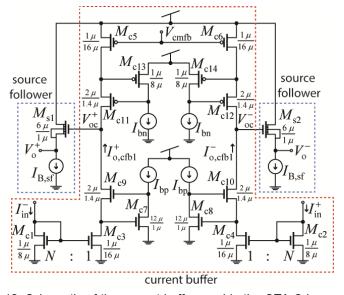

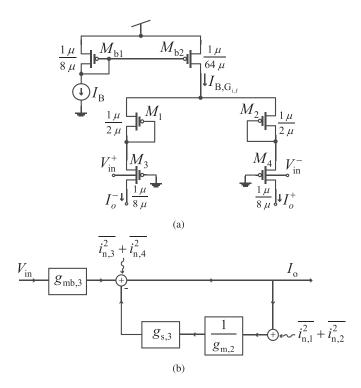

Figure 11 shows the schematic of the  $G_{\rm i}$  and  $G_{\rm f}$  OTA while Figure 12 shows the schematic of the current buffer for the current integrator used in the OTA-C lowpass filter. Please note the use of the bulk inputs for the transistors  $M_3$  and  $M_4$  of the  $G_{\rm i}$  and  $G_{\rm f}$  OTAs, and the source degeneration provided by the diode-connected  $M_1$  and  $M_2$ . To provide a very low cutoff frequency for the lowpass filter, the current buffer needs to provide a very high output resistance. Thus, we use the regulated-cascode technique to augment the output resistance of the current buffer in Figure 12. However, with all these techniques to prevent biasing the OTAs with very small bias current, we still observe large offset voltages in the OTA-C lowpass filter, which unfortunately limits the dynamic range of the overall architecture. If we are to use this architecture in a real ECG readout system, addressing the offset problem in the OTA-C lowpass filter should be one of the main design objectives.

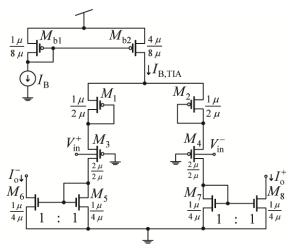

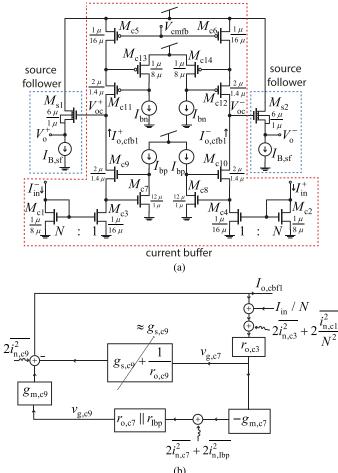

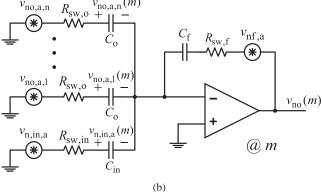

Figure 13: Overall schematic of the weight OTAs along with the TIA

Figure 14: Schematic of the weight OTAs

Figure 15: Schematic of the OTA in the TIA

Figure 13 shows the schematic of the weight OTAs along with the TIA for converting the weight OTAs' output currents into the estimator's output voltage. Shown in Figure 14, the architecture of the weight OTA is similar to those of the OTAs in the lowpass filter except that its current source is implemented with a current DAC for tuning the overall bias current, and, in turn, the weight provided by the OTA. Figure 15 shows the schematic of the OTA used in the TIA. In this research, a lot of our effort is put into theoretically analyzing the noise performance of the overall estimator. The details of those analyses are beyond the scope of this report and we refer the interested readers to [39] for further information.

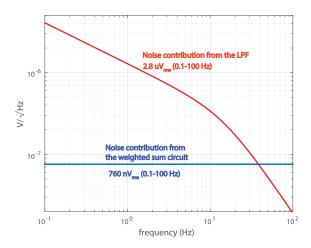

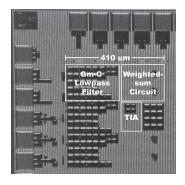

Figure 16: The chip micrograph of the motion artifact estimator

The proposed motion artifact estimator was fabricated in a standard 0.18-μm CMOS process from United Microelectronic Corp (UMC). The overall estimator occupies an active area of 0.11 mm<sup>2</sup>, whose micrograph is shown in Figure 16. The estimator operates from a supply voltage of 1 V and consumes a total bias current between 2.4 μA and 3.2 μA depending on the weight setting.

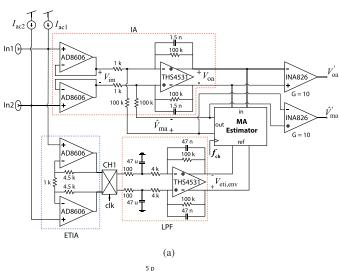

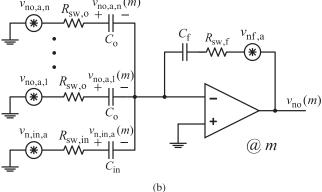

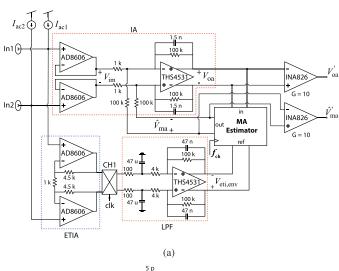

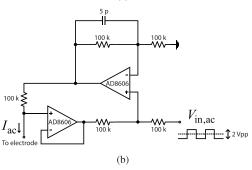

Figure 17: Schematic of the ECG readout emulator

To show the operation of the estimator in the real setting, we have built an ECG readout emulator from off-the-shelf components with our estimator chip on a printed circuit board (PCB) as shown schematically in Figure 17. The IA consists of two unity-gain voltage followers (AD8606 from Analog Devices) to provide high-impedance buffering from the electrodes, In1 and In2, and a summing amplifier built from the opamp THS4531 from Texas Instruments Inc. We built the ETI amplifier using a two-opamp topology (AD8606). The chopper switch CH1 is built from off-the-shelf MOS switches. The lowpass filter is built with a standard RC topology from the opamp THS4531. The signals of interest for this experiment are  $V_{\rm im}$  (the input voltage into the IA),  $V_{\rm ma}$  (the output of the MA estimator), and  $V_{\rm oa}$  (the output voltage of the IA). For correct operation,  $V_{\rm ma}$  should cancel with the motion artifact in  $V_{\rm im}$  such that  $V_{\rm oa}$  is virtually free of motion artifacts.

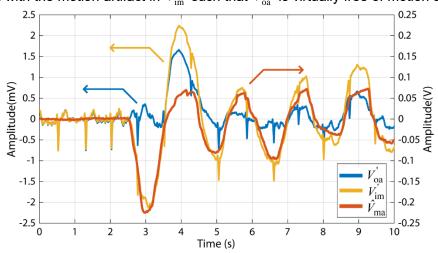

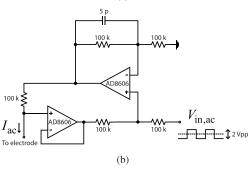

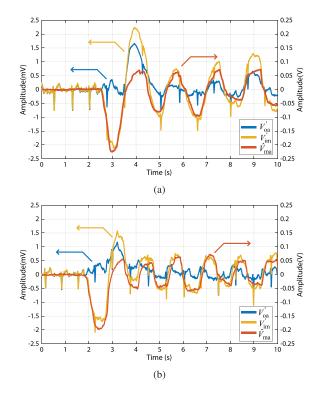

Figure 18: Measured results from the ECG emulator board

Figure 18 shows the buffered versions of the three signals of interest when the user pushes on the recording electrodes, starting from t=2 seconds onward, to induce motion artifact in  $V_{\rm im}$ . We can see that  $V_{\rm ma}$  tracks  $V_{\rm im}$  quite well such that motion artifact in  $V_{\rm oa}$  is suppressed.

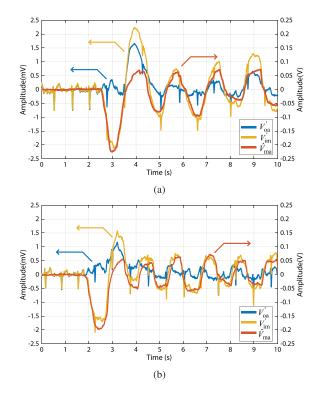

Figure 19: Waveforms showing the reconstruction process in the case of low correlation between  $V_{\rm ma}$  and the motion artifact in the input signal.

However, we have found from this study that how well the architecture suppresses motion artifact depends largely on the correlation between the electrode impedance information and the motion artifact in the recorded signal. If the correlation between the two signals are low, it is impossible for the estimator to produce  $V_{\rm ma}$  to cancel with the motion artifact in the recorded signal. In this case,  $V_{\rm ma}$  will introduce undesirable noise and distortion into the recorded signal, causing information loss. To prevent this scenario, we allow for the reconstruction of the original signal. To do so, we propose that the readout system digitizes  $V_{\rm ma}$  and also report off-chip, such that we can use the digitized  $V_{\rm ma}$  and  $V_{\rm oa}$  to recover the original recorded signal in the digital backend. Since all the information is preserved, we can apply other sophisticated digital processing techniques to remove motion artifacts from the reconstructed data. Figure 19 shows

such reconstruction concept for the's sample rates of 10 Hz and 100 Hz. We can see that for both cases, the reconstructed signals track the original signals quite well, but the high sample rate on  $V_{\rm ma}$  consistently produces lower mean-square error between the original and reconstructed signals. Indeed, the reconstruction error from the 100-Hz sample rate case is only 3.27  $\mu V_{\rm rms}$  when referred to the input of the readout system. This noise level is on the same level as the noise introduced by the front-end IA. Thus, we can conclude that the proposed scheme can help lower the dynamic range in ECG recording even with the presence of large motion artifacts. Even when the correlation between the electrode impedance information and the motion artifact in the recorded signal is low, our proposed scheme also provides a safety measure in preventing the corruption of the recorded signal.

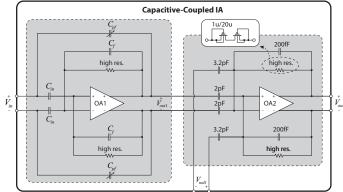

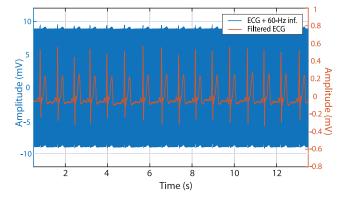

## The Wide-Effective-Output-Range Amplifier

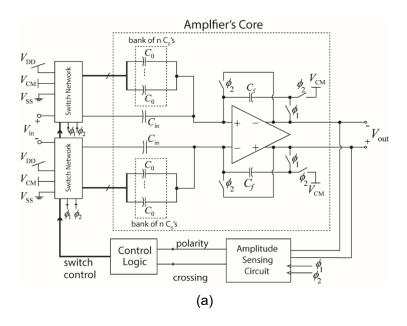

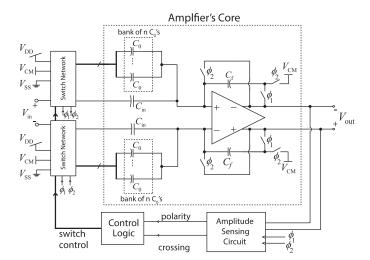

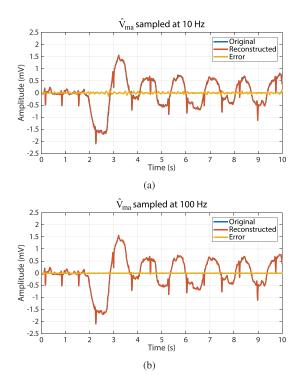

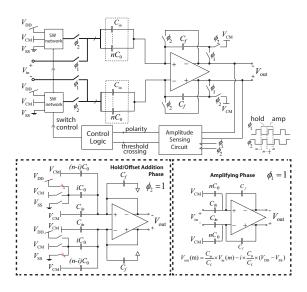

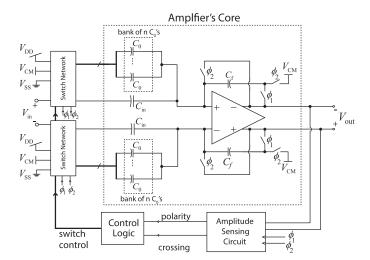

This part of the research focuses on the wide-effective-output-range amplifier (WEOR amplifier in Figure 3). The WEOR amplifier is at the heart of our proposed high-gain architecture as it allows for the use of a very high gain in the amplification chain without the risk of signal saturation. We have explained the design of the WEOR amplifier and presented its detailed measured results in [40]. In this report, we only summarize the important concepts of this crucial circuit block.

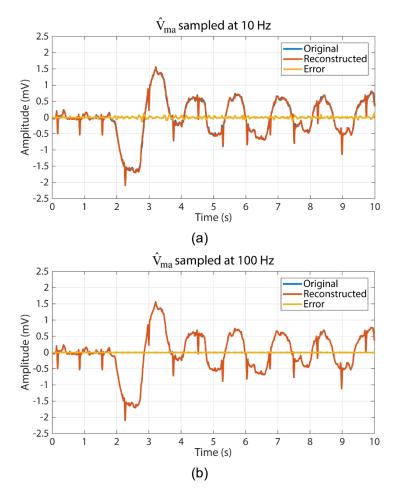

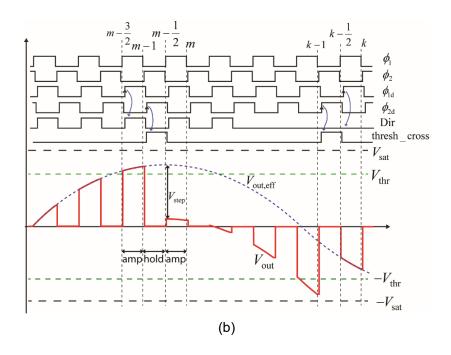

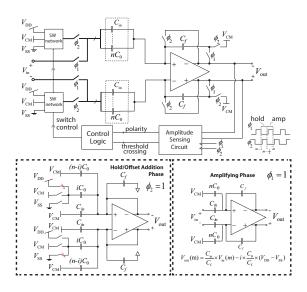

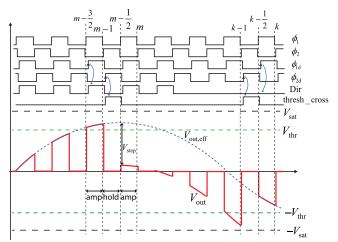

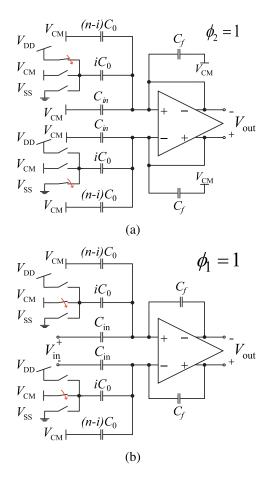

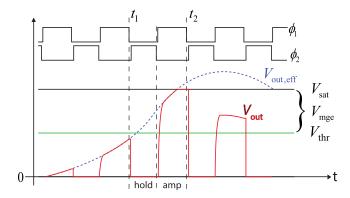

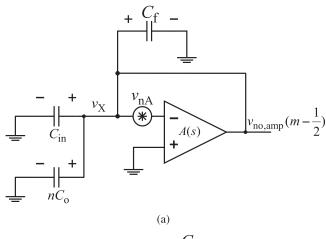

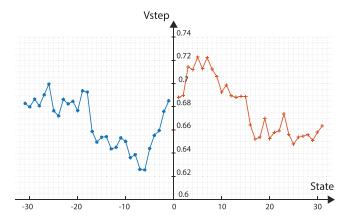

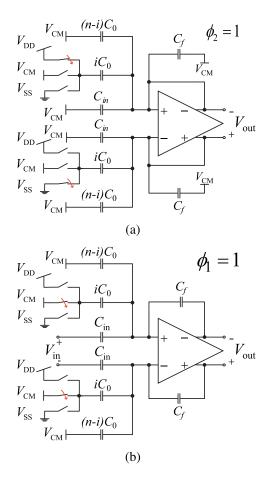

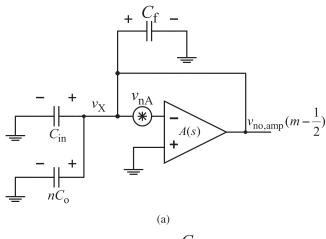

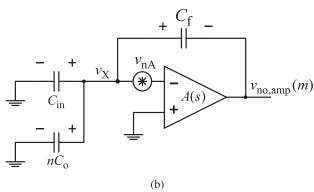

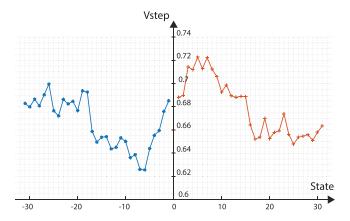

Figure 20: (a) The overall schematic of the WEOR amplifier (b) Timing diagram showing the signal-folding operation.

The main objective of the WEOR amplifier is to provide an additional gain to the amplification stage—provide an additional gain of 24 dB (16 V/V) for a total of 70 dB gain of the amplification stage—while preventing signal saturation. To do so, the WEOR amplifier utilizes a discrete-time signal folding technique; this technique uses a feedback network to monitor the amplifier's output level and, if it exceeds specific voltage thresholds, fold it back to the middle of the rail. As a result of this folding, the amplifier's output level will stay within a pre-defined range near the middle of the rail, without reaching the saturation level dictated by the voltage headroom of the output stage. Figure 20(a) shows the overall schematic of the WEOR amplifier, which consists of the amplifier's core, the feedback monitoring network (the amplitude sensing circuit and the control logic), and the input switch networks. The amplifier's core is based on the standard switched-capacitor gain circuit normally used in conventional switched-capacitor circuit design. The amplifier has its gain determined by the capacitance ratio  $C_{

m in}$  /  $C_{

m f}$  . However, it also incorporates the offset capacitor banks—those consisting of  $C_{\scriptscriptstyle 0}$  's—for adding offset voltages into the input signal to effectively fold the output voltage to the desired level. The operation of the WEOR amplifier can be understood by the timing diagram in Figure 20(b). When the clock signal  $\phi_2$  is high, the amplifier is in the hold phase, with the information of the output voltage  $V_{

m out}\,$  stored in the feedback capacitors's. During this hold phase, the control logic adds appropriate offset into the offset capacitor banks based on the state of the amplifier. Once the clock signal  $\phi_1$  goes high, the amplifier enters the amplifying phase, and the amplifier amplifies the input

signal  $V_{\rm in}$  to produce  $V_{\rm out}$ . During the amplifying phase, the amplitude sensing circuit senses whether the output  $V_{\rm out}$  has exceeded either of the threshold levels  $(\pm V_{\rm thr})$ . If so, the control logic adjusts the state of the amplifier such that, in the next amplifying phase, an appropriate offset voltage is added to the input signal to constrain  $V_{\rm out}$  to within the threshold levels. To recover the original signal, we keep track of the amplifier's state at every folding instant. Since a fixed value of offset voltage is either added or subtracted from  $V_{\rm out}$  at every folding instant, we can use the information on the amplifier's state to reverse the operation to produce the original  $V_{\rm out}$  from its folded counterpart.

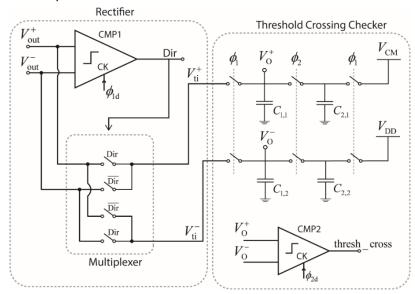

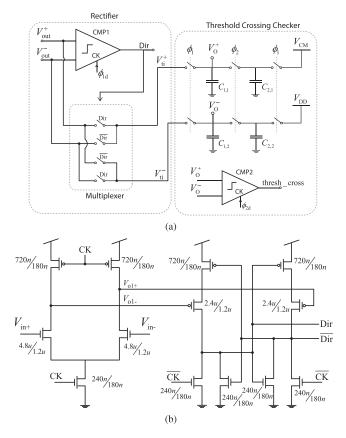

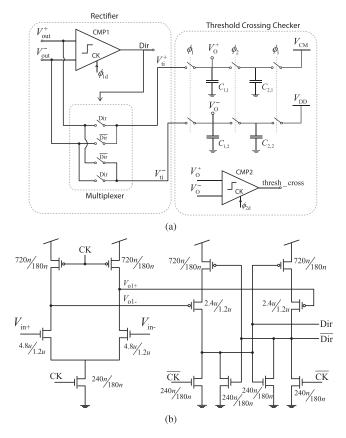

Figure 21: Schematic of the amplitude sensing circuit

Figure 21 shows the schematic of the amplitude sensing circuit, which consists of a rectifier and a threshold crossing checker. The rectifier is responsible for producing the output  $V_{\rm ti}^+ - V_{\rm ti}^-$  which is the absolute value of  $V_{\rm out}$ . Then the threshold crossing checker determines whether  $V_{\rm ti}^+ - V_{\rm ti}^-$  has exceeded the threshold value or not. If so, it flags the signal thresh\_cross to the control logic to configure the amplifier into an appropriate state. Note that the amplitude sensing circuit performs all of its computations using a switched-capacitor network and a dynamic comparator, thus consuming no bias current. This implementation choice results in a very low power consumption for the amplitude sensing circuit.

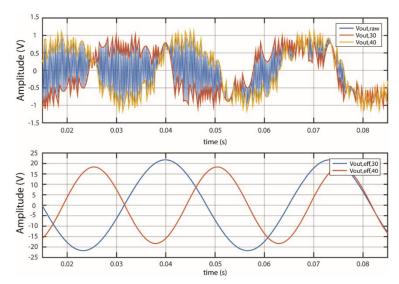

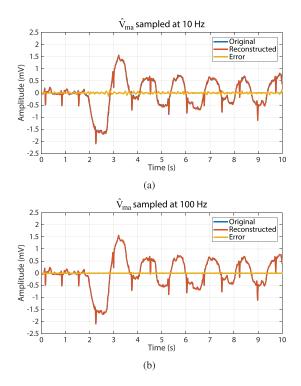

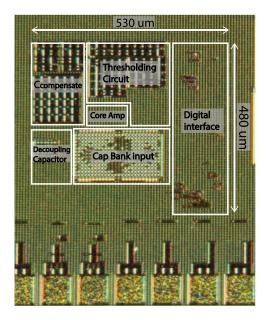

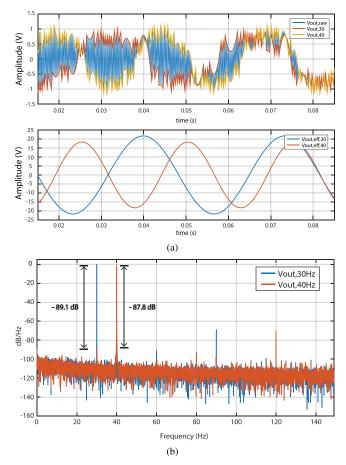

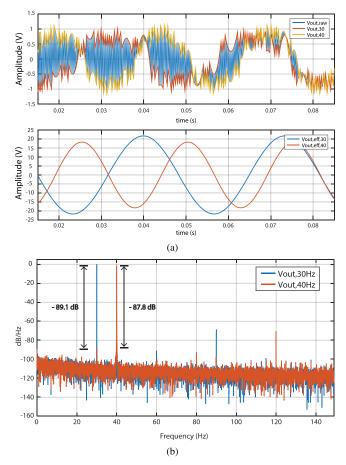

Figure 22: Measured results from the WEOR amplifier

The WEOR amplifier was fabricated as part of the ECG readout system in a standard 0.18- $\mu$ m CMOS process from UMC. The amplifier occupies a total active area of 0.254 mm². Operating from a 1.2-V supply voltage, the amplifier exhibits a gain of 17.8 V/V (instead of its nominal value of 16 V/V) due to inaccuracies in the layout modeling of our process. To test the functionality of the WEOR amplifier, we feed two rail-to-rail input signals as input into the amplifier and record its output, one signal a sinusoidal waveform at 30 Hz and the other at 40 Hz. The top pane of Figure 22 shows the raw output waveform of the amplifier, while the red and yellow curves indicate parts of the waveforms corresponding to the 30-Hz and 40-Hz input signals, respectively. After using the information on the state of the amplifier to reconstruct the original input, we obtain the plot in the bottom pane of Figure 22. We can see that the two reconstructed outputs have amplitudes of approximately 40  $V_{pp}$ , which are much larger than the 2.4 V maximum differential output swing of the WEOR amplifier, thanks to the use of the signal-folding technique.

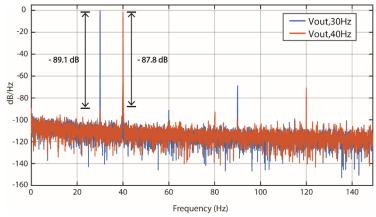

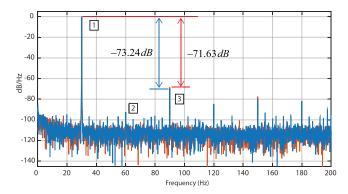

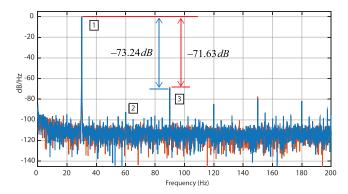

Figure 23: Power spectrum of the 30-Hz and 40-Hz output waveforms showing their crosstalk

Having a large amplitude is practically useless if the output waveform is highly distorted. In other words, we must ensure that the WEOR exhibits excellent linearity if it is to be useful in ECG recording applications. To test the linearity of the WEOR amplifier, we analyzed the two reconstructed output signals in the frequency domain and obtained the power spectral density plots as shown in Figure 23. Also indicated on the plots are the levels of crosstalk from one input to the other. We can see that the crosstalks are on the order of -90 dB, thus indicating that the amplifier can amplify two signals without having them interfere with each other.

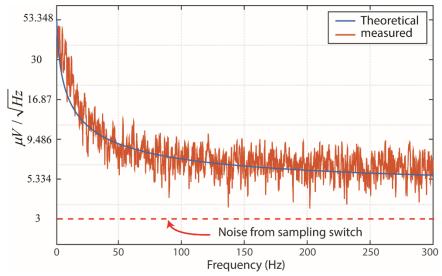

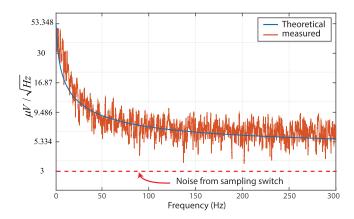

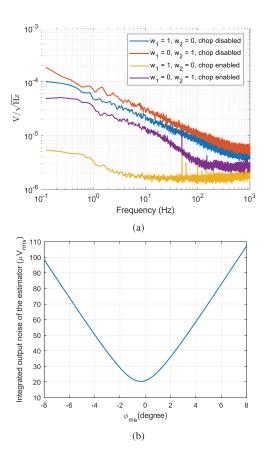

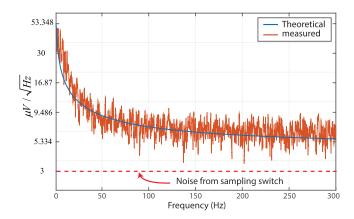

Figure 24: Measured input-referred noise power spectral density of the WEOR amplifier

As a significant part of this research, we spent a considerable effort in theoretically analyzing the noise performance of the WEOR amplifier. The detail of the analysis is beyond the scope of this report and we refer interested readers to [40]. Nevertheless, we have shown in our measurement result that our theoretical noise analysis matches very well with the measured result. Figure 24 shows the power spectral density of the WEOR amplifier's input-referred noise along with the result obtained from our theoretical analysis. Integrating under the red curve yields a total input-referred integrated noise of 143.6  $\mu V_{rms}$ . Such input noise level indicates that if we are to precede the WEOR amplifier with an IA whose gain is around 200 V/V, the WEOR amplifier's noise referred to the input of the system would be around 0.7  $\mu V_{rms}$ , which is less than the input-referred integrated noise of the IA.

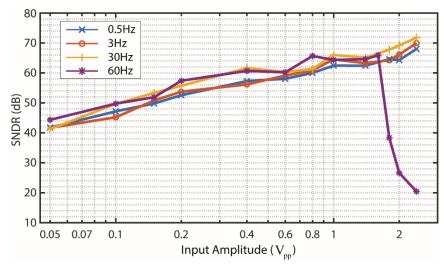

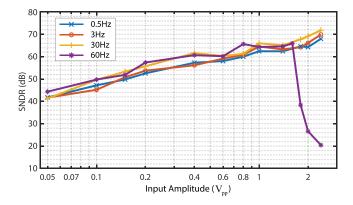

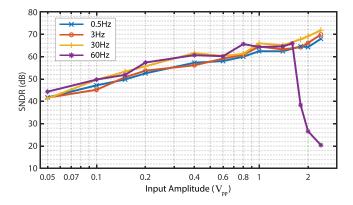

Figure 25: SNDR as a function of the input amplitude at various frequencies of the input

Though the discrete-time folding technique is very accurate and can be implemented with low-power consumption, it has one important inherent limitation: speed. Since the technique uses a clock, we must ensure that the WEOR amplifier's output do not change too fast and cross a threshold in one clock period. This scenario can happen for fast input with large amplitude. Fortunately, the interferences into the ECG readout system are normally slow signals: the motion artifact has energy concentrated below 5 Hz while the powerline interference's frequency is at 50 or 60 Hz. Therefore, if these interferences are not extremely large, the WEOR amplifier should be fast enough to constrain its output to within the threshold levels such that no signal saturation occur. We tested the amplifier's performance for the input frequencies of 0.5 Hz, 3 Hz, 30 Hz, and 60 Hz. For a given frequency of the input, we increased its amplitude and measured the signal-to-noise-plus-distortion (SNDR) of the output. Figure 25 shows the resulting SNDR for this measurement. We can see that for the test frequencies below 60 Hz, the SNDR (dB) is approximately a linear function of the logarithm of the input amplitude up to the input amplitude of as high as  $2.4~V_{pp}$ . This indicates that, for these input frequencies, the amplifier behaves linearly for the whole rail-to-rail input range. However, when the input frequency is 60 Hz (the frequency of the powerline interference), the SNDR falls sharply when the input amplitude reaches 1.8  $V_{pp}$ . This happens because the amplitude sensing circuit cannot operate fast enough in folding the output signal away from the saturation level of the WEOR amplifier's output stage. Fortunately, such input saturation level occurs when the 60-Hz signal is as large as 1.8  $V_{pp}$ , a level much larger than the maximum powerline interference expected in our system.

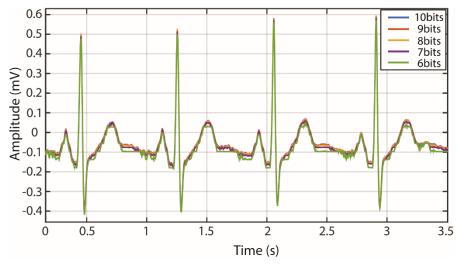

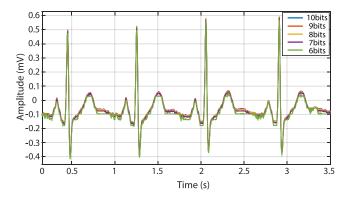

Figure 26: The ECG waveforms as digitized by the ADC at various resolutions.

The major benefit of the WEOR amplifier is to allow the very high gain in the amplification stage without the risk of signal saturation. Such high gain helps relax the resolution requirement of the ADC that follows the amplification stage. As a result, an ADC of only 7-8 bit of resolution is required for digitizing the WEOR amplifier's output signal. To illustrate this concept, we recorded an ECG from standard Ag-AgCl electrodes using the ECG readout IC discussed in [38]. We then amplified the ECG in digital with a gain of 200 and fed the result to the WEOR amplifier's input and then digitized its output signal. Then, we discarded specific numbers of the least significant bits to mimic the digitization by ADCs of lower resolution. Figure 26 shows the resulting digitized waveforms referred to the input of the readout system by various ADC's resolutions. We can see that the ECG waveforms from the digitization at higher than 7 bits are nearly indistinguishable from each other, thus indicating that increasing the resolution beyond 7-bits provides negligible SNR improvement.

# The ECG Readout System Prototype

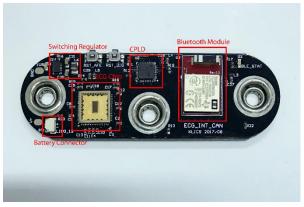

Figure 27: A battery-powered wireless ECG readout system.

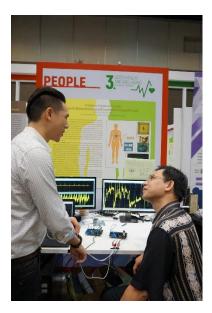

To illustrate the functionality of the ECG readout IC in real recording environment, we have built a battery-powered wireless ECG readout system on a PCB with our ECG readout IC at its core. Figure 27 shows our readout system. The system can be attached directly to the chest of the user and can transmit the recorded data wirelessly to a receiver at the remote computer. We have demonstrated that the system functions correctly. We have exhibited this system at งาน 25 ปี สกว: สร้างคน สร้างความรู้ สร้างอนาคต at Siam Paragon on 25-26 August 2017. The atmosphere during the exhibition of our system is shown in Figure 28.

Figure 28: The exhibition of the wireless ECG recording system at งาน ปี สกว 25: สร้างคน สร้างความรู้ สร้าง อนาคต at Siam Paragon on 25-26 August 2017

# Conclusion