#### 4. CONCLUSION

The realization of current-mode squarer and full-wave rectifier in the same circuit based on the use of a modified CMOS class AB amplifier has been proposed. Their performances have been demonstrated by the HSPICE program.

#### **ACKNOWLEDGEMENT**

This work is partly funded by the Thailand Research Fund (TRF) under the Senior Research Program, grant number RTA/04/2543.

The support provided by the Japan International Cooperation Agency (JICA) is also acknowledged.

#### 5. REFERENCES

- G. Giustolisi, G. Palmisano and G. Palumbo, "1.5V power supply CMOS voltage squarer," Electron. Lett., vol. 33, no. 13, June 1997.

- [2] Cheng-Chieh Chang, Shen-Iuan Lui and Jiin-Long Lee, "Analogue BiCMOS squarer and its application," Electron. Lett., vol. 35, no. 5, March 1999.

- [3] Shen-luan Lui and Cheng-Chieh Chang, "A CMOS Square-Law Vector Summation Circuit," *IEEE Trans. Circuits Syst. II*, vol. 43, no. 7, pp. 520-524, July 1996.

- [4] Wanlop Surakampontom and Vanchai Riewruja, "Integrable CMOS sinusoidal frequency doubler and full-wave rectifier," Int. J. Electronics, vol. 73, no. 3, pp. 627-632, 1992.

- [5] Wantop Surakampontom, K. Anuntahirunrat and Vanchai Riewruja, "Sinusoidal frequency doubler and full-wave rectifier using translinear current conveyor," Electron. Lett., vol. 34, no. 22, otc. 1998.

- [6] C. Toumazou, F.J. Lidgey and S. Chattong, "High frequency current conveyor precision full-wave rectifier," Electron. Lett., vol.30, no.10 May 1994.

- [7] N. Battersby, and C. Toumazou, "Class AB switchedcurrent," Electronics letters, 10, pp. 873-874, 1991.

- [8] P. R. Gray and R. G. Meyer, "Analysis and Design of Analog Integrated Circuits," New York: Wiley, 1984.

- [9] Adel S. Sedra and Kenneth C. Smith, Microelectronic Circuits," New York: Oxford, 1998.

ROCHEDINGS of the 2003 DEEL Uniternational Symposius on Circuits and Systems

BANCKOK • THATLAND

DIOICHIMEINIT (CHINE)

FOREWORD

©2008 IEEE

TVABILE OF CONTENTS

AUTHORS

SE/ARICH

IEEE Catalog No. 03CH37430C ISBN: 0-7803-7762 I

Technical inquiries Contact: MosArt Productions e-mail: "ISCAS2003@conference.org Phone: (831) 625-5257 Fax: (815) 550-0345

However, permission to full education of the contesting or the contesting to the con

#### REALIZATION OF ELECTRONICALLY TUNABLE LADDER FILTERS USING MULTI-OUTPUT CURRENT CONTROLLED CONVEYORS

Amorn Jiraseree-amornkun<sup>†</sup>, Nobuo Fujii<sup>‡</sup> and Wanlop Surakampontorn<sup>†</sup>

<sup>†</sup> Faculty of Engineering and Research Center for Communications and Information Technology King Mongkut's Institute of Technology Ladkrabang, THAILAND

<sup>1</sup> Department of Physical Electronics, Tokyo Institute of Technology, JAPAN

#### **ABSTRACT**

A systematic realization of continuous-time current-mode ladder filter using multi-output second generation current controlled conveyor (MCCCII) has been presented. The proposed technique is based on leapfrog simulation of RLC ladder filter using only MCCCIIs and capacitors that lead to simple structure, easy to design and suitable for IC fabrication. A fifth-order Butterworth low-pass filter and a sixth-order Chebyshev bandpass filter which retain a minimum requirement of passive elements and have an advantage of electronically tunable will be introduced. The feasibility of realization strategy is confirmed through HSPICE circuit simulations.

#### 1. INTRODUCTION

Double terminated passive RLC ladder filters are well known on having an inherent advantage over active filter in terms of their sensitivity to component tolerances. There are several methods to extract this benefit from the prototype passive filter using the opamp-based RC-active and OTA-C-based circuits [1]. The leapfrog structure seem to receive more popular due to it share all the low sensitivity characteristic and low component spread of the precedent RLC filter. Traditionally, the simulation is based on modeling all circuit equations as voltage signals [1]. Recently, current-mode signal processing has been received substantial consideration owing to its higher performance properties. Consequently, many suggestions of current-mode leapfrog ladder filter had been published employing OTAs [2] and CCIIs [3] as the active building blocks. However, all of them are established from simulating the operation of the ladder by mean of realizing the transfer function, which require a lot of active and passive elements and sometime the sensitivity may not necessitate being low. In very recent, the implementation of leapfrog filter using current differential buffered amplifies or CDBAs has been proposed [4], which can perform high frequency and low voltage supply operation. This scheme can simplify the signal flow graph of leapfrog filter and then realize each circuit element one by one, hence the low sensitivity basis is promised. Unfortunately, several floating resistors are required for voltage to current conversion and the utilized frequency is exactly fixed by determined passive elements.

This paper follows the idea of realizing the voltage-current relationships of each element corresponding to the prototype RLC filters one by one. Current controlled conveyor is chosen to function as a V-to-I converter cell regenerating all voltage parameter into current form. This proposed scheme possesses

many advantages. Firstly, the structure is very simple and easy to design. No any external resister is required, which can safe the area in case of fabricating in a silicon chip. Moreover, the center frequency can be tuned electronically by adjusting the bias current of MCCCIIs. This will be useful in redeeming when the values of passive devices are deviated; including changing the system's characteristic is also very comfortable.

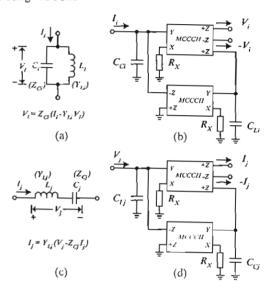

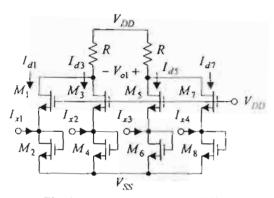

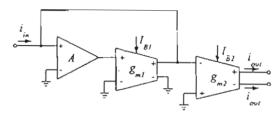

#### 2. CURRENT CONTROLLED CONVEYOR

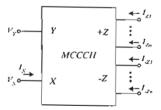

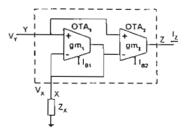

Second generation current conveyors (CCIIs) have found useful applications especially in current-mode world. Based on a complementary translinear loop, the current conveyor will be possible to operate at high frequency in class AB. In addition, the translinear current conveyor has a structure as simple as basic OTA but take less power consumption [5]. Despite this, it has only one output terminal and a current signal is available only once for each signal feed back. Therefore, in the multi-loop feedback path topology like leapfrog, multi-output characteristic seem to play an important role. The circuit symbol of multi-output current controlled conveyor is shown in figure 1, which has both positive output terminal represented by +Z and negative output terminal by -Z.

Figure 1. Circuit symbol of MCCCII

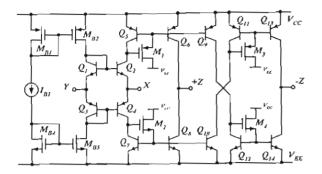

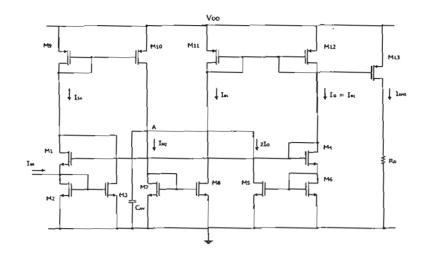

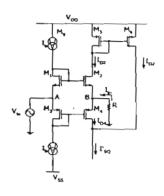

The schematic implementation of BiCMOS transfinear MCCCII is shown in figure 2, which the ports relation can be described by the following matrix equation:

$$\begin{bmatrix} I_{y} \\ V_{x} \\ I_{z} \\ I_{z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & R_{x} & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & -1 & 0 & 0 \end{bmatrix} x \begin{bmatrix} V_{1} \\ I_{x} \\ V_{z} \\ V_{z} \end{bmatrix}$$

(1)

where  $R_X = V_T/2I_{BI}$  is an intrinsic small signal resistance of the equivalent voltage follower. It is possible to control  $R_X$  by

Figure 2. BiCMOS implementation of MCCCII

varying the bias current  $I_{BI}$ . Note that since the main contribution in noise is coming from current mirrors, the employment of MOS transistors in the biasing circuit is to minimize noise [5]. The multi-output topology can be easily implemented by adding the further output transistors. MOS transistors,  $M_I - M_I$ , are used to supply base current to all output transistors for accurate current transfer.

#### 3. FILTER DESIGN METHODOLOGY

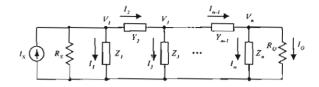

In order to develop the simulation procedure, consider the general ladder structure in figure 3. Here we focus on the realizing of the doubly terminated RLC filter. The characteristic of this structure can be expressed as following:

$$I_{1} = I_{S} - \frac{V_{1}}{R_{S}} - I_{2},$$

$$V_{1} = Z_{1}I_{1},$$

$$I_{2} = Y_{2}(V_{1} - V_{2}),$$

$$V_{3} = Z_{3}(I_{2} - I_{3}),$$

$$\vdots$$

and

$$I_{n-1} = Y_{n-1}(V_{n-2} - V_{n}),$$

$$V_{n} = Z_{2}(I_{n-1} - I_{D})$$

(2)

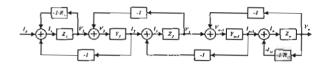

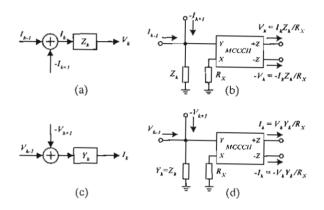

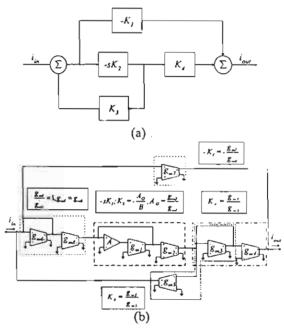

where  $Z_i$  and  $Y_i$  stand for the impedance and admittance, respectively. These equations can be represented with block diagram in form of leapfrog structure as shown in figure 4. It can be observed that the diagram comprises of 2 operations, current to voltage and voltage to current conversion, as sketched in figure S(a) and S(c). Then if we convert the variables to be processed in only one type, the current variable, the execution would be simpler and ease in design. As seen in figure S(b) and S(d), with transforming all voltage to its current counterpart using MCCCIIs, these two operators can then be implemented using the same circuit. It should be noted that  $R_X$  is intrinsic resistance at port X of MCCCII introduced in the previous section. Since after the transformation, all variables are related to  $R_X$ , altering on  $R_X$  can also varying the characteristic of the filter that is the key of electronically tunable property.

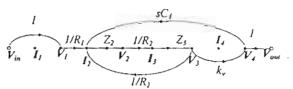

Figure 3. General doubly terminated ladder network

Figure 4. Block diagram redrawn from figure 3

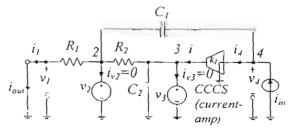

Figure 5. Basic blocks and the realization using MCCCIIs

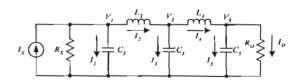

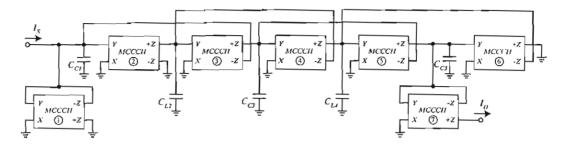

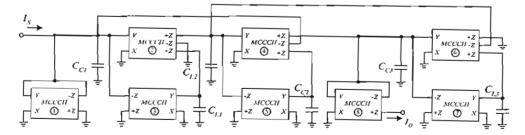

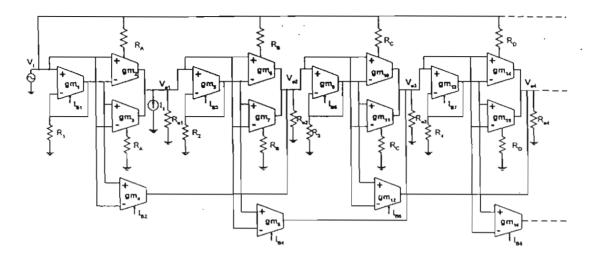

A current-mode fifth-order Butter-worth low-pass RLC ladder filter shown in figure 6 is adopted as an example and the consequent circuit is shown in figure 7. It comprises of the minimum requirement of MCCCIIs and capacitors. As it is clearly seen that only five MCCCIIs and five capacitors are needed for realizing the fifth-order filter. There is no obligation of any external resistor, even the terminated resistor,  $R_S$  and  $R_O$ , are also implementing using MCCCIIs. Not only the attempt to eliminate the passive components, it is the necessary for tuning center frequency feature. Then, in general, merely n+2 MCCCIIs and n capacitors are required for the  $n^{th}$ -order filters implementation. Furthermore, this composition has several high impedance outputs, which allow to be easily cascaded without any additional matching circuits.

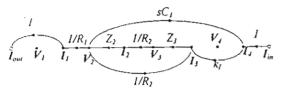

Figure 6. Prototype current-mode fifth-order Butterworth low-pass RLC ladder filter

Figure 7. Current-mode tunable fifth-order Butterworth low-pass filter using MCCCHs

Figure 8. Current-mode sixth-order RLC band-pass filter

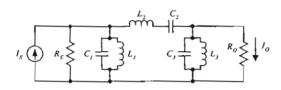

In addition, deriving the RLC ladder band-pass filter with this procedure is also possible. Consider a current-mode sixth-order band-pass filter in figure 8. In this case, the parallel and series LC branches can be realized using the basic block as shown in figure 9. And then the full leapfrog filter is obtained as in figure 10.

# 4. SIMULATION RESULTS AND DESIGN EXAMPLE

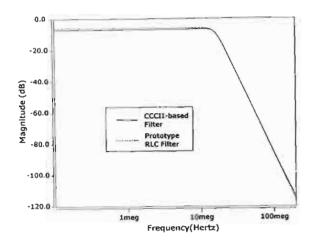

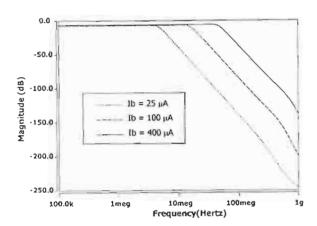

The performance of the proposed filter is verified through HSPICE circuit simulation based on 0.8- $\mu$ m BiCMOS process technology supplied by AMS. The emitter areas for bipolar transistors are all equaled while set the W/L ratio of CMOS bias circuit.  $M_{hI} = M_{hI}$ , to  $10\mu$ m/ $1\mu$ m and current mirror CMOS transistors,  $M_I = M_{el}$ , to  $5\mu$ m/ $1\mu$ m. The bias current is set to  $1_{BI} = 100 \mu$ A under the voltage supply of  $\pm$ V =  $\pm$ 2 V. The basic characteristics of the MCCCII as a transconductance cell are listed in table 1.

To picture out the feasibility of the proposed filter technique, a current-mode fifth-order Butterworth low-pass filter has been designed with a half-power frequency  $\omega_{.3dB}$  of 100 Mrad/s (15.9 MHz). The terminated resistances are chosen to 1  $\Omega$  in prototype RLC filter. Then after scaling with MCCCH's intrinsic resistance

Figure 9. Basic blocks of filter in fig. 8 using MCCCIIs

Table1. Transconductance cell characteristic of MCCCH

| Parameter         | Simulated val. | Unit |

|-------------------|----------------|------|

| Open loop $G_m$   | 5              | mA/V |

| -3 dB Bandwidth   | 306            | MHz  |

| Input resistance  | 5.72           | kΩ   |

| Output resistance | 140            | kΩ   |

$R_X$  (1/ $G_m$ ), the capacitances' values are  $C_{CJ} = C_{CS} = 30.9$  pF,  $C_{L2} = C_{L4} = 80.9$  pF and  $C_{C3} = 100$  pF. The simulated frequency

Figure 10. Current-mode sixth-order Chebyshev band-pass filter using MCCCIIs

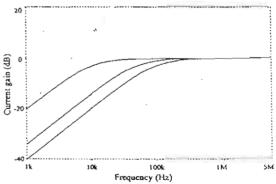

response of the designed circuit and prototype RLC filter are compared in figure 11. Tuning ability is also simulated and shown in figure 12 by varying bias current to 25 µA and 400 µA.

Figure 11. Simulated frequency response of the fifthorder low-pass filter

Figure 12. Simulated response of tuning cutoff frequency

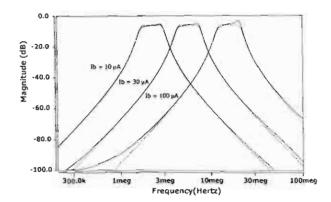

A sixth-order Chebyshev band-pass filter deriving from RLC grouping as shown in figure 8 has been designed as well with the center frequency of 100 Mrad/s (15.9 MHz). The passive components are set to  $C_{CI} = C_{C3} = 114.5$  pF,  $C_{LI} = C_{L3} = 21.8$  pF,  $C_{C2} = 19.6$  pF and  $C_{L2} = 127.5$  pF. Adjust the bias current to 10  $\mu$ A and 30  $\mu$ A as the example of tunable ability. The simulated results are shown in figure 13.

It can be observed the well agreement with the passive prototype in low-pass filter implementation. However, there are some deviations in realizing band-pass filter especially in the higher frequency range. This is due to the conversion resistance  $R_X$  is not pure resistance but combined from both RLC, since the simulation using ideal MCCCII with genuine  $R_X$  have the exact response to the passive filter one as shown in dash line of figure 13. The high frequency compensation can be worked out to improve the efficiency in the future work.

Figure 13. Simulated frequency response of tuning the sixth-order band-pass filter

#### 5. SUMMARY

A realization of leapfrog ladder filter using multi-output current controlled conveyor is proposed. The design strategy is very simple and requires the minimum passive components. The center frequency can be tuned electronically by controlling the bias current of current conveyor, which is very helpful in compensating unmatched components as well as varying the characteristic without changing any device. Fifth-order Butterworth low-pass filter and sixth-order Chebyshev band-pass filter are derived as examples. HSPICE simulation results give a good agreement with the theoretical expectation. Nevertheless, the frequency compensation should be done on implementing current conveyor for serving the filters' responses much more perfect.

#### 6. ACKNOWLEDGEMENT

The first author would like to thank Mr. Worapong Tangsirat for useful discussions on ladder filter design. This work is partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency (JICA) is also acknowledged.

#### 7. REFERENCES

- R. Schaumann, and M.E. Van Valkenberg, Design of Analog Filters, Oxford University Press, New York, 2001.

- [2] J. Ramírez-Angulo, and E. Sánchez-Sinencio "High Frequency Compensated Current-Mode Ladder Filters Using Multiple Output OTAs," *IEEE Trans. Circuits Syst.* 11, vol. 41, no. 9, pp. 581-586, Sep. 1994.

- [3] Y.S. Hwang, P.T. Hung W. Chen and S.I. Liu, "Systematic Generation of Current-Mode Linear Transformation Filters Based on Multiple Output CCHs," J. Analog Integrated Circuit and Signal Proc., vol. 32, pp. 123-134, Aug. 2002.

- [4] W. Tangsrirat, N. Pujii, and W. Surakampontorn, "Current-Mode Leapfrog Ladder Filters using CDBAs," Proc. Int. Symp. Circuits Systems, pp. V57-V60, 2002.

- [5] A. Fabre, O. Saaid, F. Wiest, and C. Boucheron, "High-Frequency High-Q BiCMOS Current-Mode Bandpass Filters and Mobile Communication Application," *IEEE J Solid State Circ.*, vol. 33, no. 2, pp. 614-625, Apr. 1998.

### **PROCEEDINGS**

# 2001 IEEJ International Analog VLSI Workshop

May 14-15, 2001 Fortune Hotel, Bangkok, Thailand

#### CMOS Multi-Output FTFN: A Translinear Approach

A. Jiraseree-amornkun, W. Tangsrirat and W. Surakumpontom

Faculty of Engineering and Research Center for Communication and Information Technology

King Mongkut's Institute of Technology Ladkrabang

Ladkrabang, Bangkok 10520, THAILAND

Phone (66-2) 739-1362, FAX (66-2) 739-2398, E-mail: amorn@ieee.org

#### Abstract

An alternative CMOS implementation scheme of a multi-output four-terminal floating nullor (MFTFN) proposed. The presented scheme is based on the advantages of a complementary transconductance amplifier and a class AB translinear cell type circuit that comes up with extremely high gain and wide bandwidth. The MFTFN is a very useful building block that can be used to substitute the other well-known blocks in every application. The characteristics of the proposed universal active circuit element are confirmed through HSPICE simulations. Current-mode band-pass filter and multifunction biquadratic filter are determined to exhibit the potentiality of this proposed scheme.

Keywords: Universal Active element, FTFN, Translinear, CMOS analog circuit, Current-mode filter

#### 1. Introduction

Current-mode circuits have gained essential consideration recently. This arises from their significant advantages over the voltage-mode, especially for higher frequency operation and simpler structure. The regular active devices that have been used in current-mode are a second-generation current conveyor (CCII), a current feedback op-amp (CFOA), an operational transconductance amplifier (OTA) and a four-terminal floating nullor (FTFN). However, it has been recently shown that the FTFN is more flexible and versatile than the other building blocks. These lead up to the increasing interest in using FTFNs to design current-mode circuits: for example, filters, gyrators, simulated floating impedance and sinusoidal oscillator [1-3]. FTFN-based structures provide a number of influential advantages such as minimum number of employed elements, complete absence of passive component-matching requirement and endowing high frequency characteristic. Although FTFN-based and CCII-based currentmode circuits can simply be designed through a systematic transformation, based on the use of a nullor which consist of a nullator and a norator, from a regular RC active circuit. However, the CCII-based implementations are more complex and require the additional number of the active elements. This owes to the fact that when using the transformed nullor equivalent circuit the nullator/norator pair can simple be represented by an FTFN without imposing any restrictions. Moreover, by

designing through a dual transform technique, the transformed current-mode FTFN-based circuit furnishes a high output impedance source. This property enables the circuit to be used in cascade form.

There are many FTFN realisations that have been recently reported in literatures [4-5]. However, this paper shows an alternative form to realise an integrable multiple-output port FTFN in CMOS technology, with offers higher gain and bandwidth. The proposed scheme realises through the combination of a complementary transconductance amplifier, a translinear cell and current mirrors. In addition, the number of output ports can easily be expanded to support the designer applications. For example, recently, there are some interests on realising and using the FTFN which has been extended more than four terminal such as the socalled a five-terminal floating nullor (FiTFN) [2, 6], which are good basic applications for our multi-output FTFN idea. The current-mode band-pass filter is adopted to demonstrate the FTFN-based circuit capability. While the universal current-mode biquadratic filter is employed to demonstrate the proposed multipleoutput FTFN application example.

#### 2. Basic idea

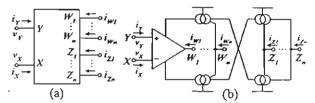

In general, FTFN is equivalent to an ideal nullor, which can imply to be a high gain transconductance amplifier with independently floating characteristic at

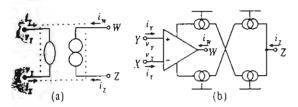

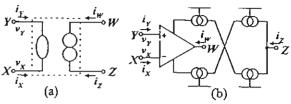

input and output terminals. Fig. 1(a) shows a nullor model of an FTFN that can be described by its port relation characteristics as:

$$v_Y = v_X$$

$i_Y = i_X = 0$   $i_Z = -i_W$  (1)

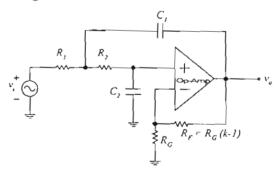

W and Z ports are generally arbitrary. Usually, the lisations of FTFN are based on the use of the lisational op-amps as the basis parts. One of the famous realisation techniques of the FTFNs is it up from a basic type shown in Fig. 1 (b) [1, 2, 6]. It using one op-amp and supply current sensing majue, where the output impedance of port W is very and the impedance of port Z is very high.

(a) A nullor model (b) traditional implementation.

propriate for high frequency applications due to come with the frequency applications due to come with the first state of the f

fication from the original FTFN to be a MFTFN

is done by adding the new output terminals as shown in Fig. 2. Fig. 2 (a) shows the schematic diagram of the MFTFN, where its characteristics can be point out by the following port relations:

$$v_{\gamma} = v_{\chi}$$

$$i_{\gamma} = i_{\chi} = 0$$

$$i_{Z1} = i_{Z2} = \dots = i_{Zn} = -i_{w1} = -i_{w2} = \dots = -i_{wn} \quad (2)$$

where n is number of the output ports. The implementation scheme of the MFTFN will be shown in the section 3 and the application of the MFTFN will be outlined in the section 5.

Fig.2 (a) Multi-output FTFN symbol (b) possible implementation.

#### 3. Circuit description

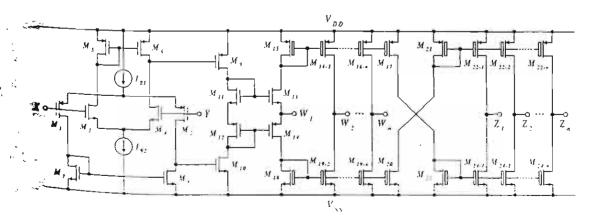

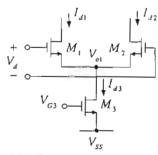

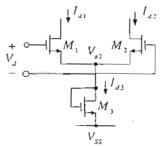

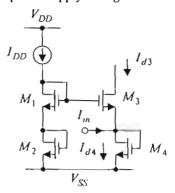

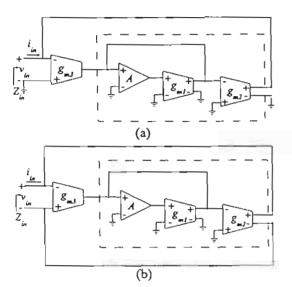

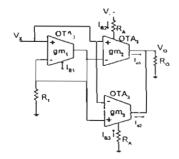

From the drawback of previous works, there is a motivation to find out a simple realisation structure, which has simultaneously high gain and bandwidth. The circuit diagram of the proposed multi-output FTFN is shown in Fig. 3. This circuit basically comprises of a complementary transconductance amplifier, a basic translinear cell and some of current mirrors. Transistors  $M_I$  to  $M_A$  and the bias current sources  $I_{BI}$  and  $I_{B2}$  perform a complementary differential amplifier, which

Fig. 3 Schematic diagram of the multi-output FTFN.

are connected with active loads, current mirrors  $M_5$  -  $M_6$ and  $M_7 - M_8$ . It should be noted that a P-channel input pair,  $M_1 - M_2$ , is employed to be able to reach the negative supply rail while an N-channel input pair, M3 - $M_4$ , is able to reach the positive supply rail. As a result, the common-mode input range of this circuit extends nearly from rail to rail. This complementary input stage feed a differential output voltage, which is continuously enlarged by the gain stage, transistors  $M_9$  and  $M_{10}$ . The converted current signal from the gain stage is injected to the translinear cell,  $M_{II} - M_{I4}$ , and then summing to be output current at port  $W_i$ . This configuration provides very high transconductance gain over a wide frequency range. Ideally, it is required that the pairs of transistors  $M_{II}$ ,  $M_{I3}$  and  $M_{I2}$ ,  $M_{I4}$  are closely matched and all current mirrors have the exact unity gain. This translinear cell act as a current-follower that allows output current  $i_{WI}$  to sources and sinks at port  $W_I$  and will be reflected and inverted to be current  $i_{ZI}$  at terminal Z<sub>i</sub>. With this cross-coupled current mirror technique, it can be easily kept up  $i_{ZI} \equiv -i_{WI}$ . The transistors having boxes as gates are composite transistors with high output impedance such as normal cascodes, low-voltage cascodes, or regulated cascodes [8]. The multi-output concept can be easily adapted by adding transistors to the output current mirror set. Transistors  $M_{16-2} - M_{16-n}$  and  $M_{19-2} - M_{19-n}$  are used to perform the output terminals  $W_2$  to  $W_m$ , respectively. Similarly, transistors  $M_{22\cdot 2}-M_{22\cdot n}$  and  $M_{24\cdot 2}-M_{24\cdot n}$  are used to perform the output terminals  $Z_2$  to  $Z_n$ .

#### 4. Simulation results

The performance of the proposed circuit is verified by HSPICE circuit simulation program based on the SCN2 level-2 CMOS model obtained through MOSIS [9]. All transistor dimensions are listed in Table 1,

Table 1 Transistors dimension

| Transistors                                                                            | W (μm) | L (µm) |

|----------------------------------------------------------------------------------------|--------|--------|

| M <sub>1</sub> , M <sub>2</sub>                                                        | 300    | 2      |

| M1, M4                                                                                 | 150    | 2      |

| Ms. Ms. M10                                                                            | 40     | 2      |

| M7. M8                                                                                 | 20     | 2      |

| Ma                                                                                     | 80     | 2      |

| M <sub>II</sub> , M <sub>C</sub>                                                       | 100    | 2      |

| M <sub>13</sub> , M <sub>14</sub>                                                      | 200    | 2      |

| $M_{15}, M_{16\cdot 2} - M_{10\cdot n}, M_{17}, M_{21}, M_{22\cdot 1} - M_{72\cdot n}$ | 70     | 2      |

| $M_{1x}, M_{19-2} = M_{19,m}, M_{20}, M_{23}, M_{24,1} = M_{24,1}$                     | 35     | 2      |

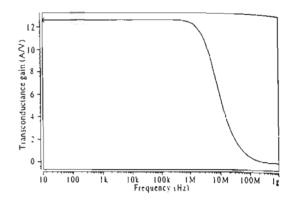

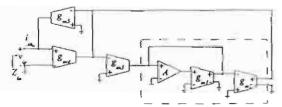

where W is channel width and L is channel length. The bias currents are set to  $I_{BI} = I_{B2} = 2\text{mA}$ . Supply voltages are taken as  $V_{CC} = +5\text{V}$  and  $V_{EE} = -5\text{V}$ . The simulated characteristic of open loop transconductance gain is given in Fig. 4 showing a significant greate; amplification circuits both gain and bandwidth than eve: published  $\{4-6\}$ .

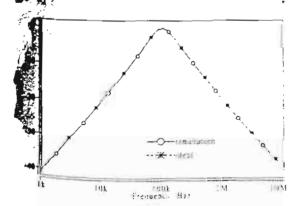

Fig. 4 Simulated open loop transconductance gain.

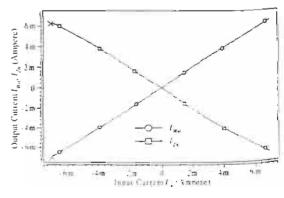

From the response, it can be estimated the -3 dB bandwidth in a very high frequency as nearly as 5 MHz and the transconductance gain of over 12 A/V is obtained. This gain is exceptionally high especially comparing to the preceding proposed circuit, which have the transconductance gain not exceeding a few hundred of milliampere per volt [4-5]. The simulated DC offset voltage between input port is approximately 90  $\mu$ V and the offset current of the output port is about 1  $\mu$ A. The input voltage swing and the output current swing are in the range of  $\pm 3.5$  V and  $\pm 7$ mA. respectively. The current follower operation proves the linear identity over a very wide current range as shown in Fig. 5 where  $I_{Wn}$  and  $I_{Zn}$  are the currents from port  $W_n$  and  $Z_n$ ,  $n=1,2,\ldots$ , respectively.

Fig. 5 Current following operation at output port.

### ion Examples

realisation of a current-mode band-pass from reference 4 is chosen as an illustrative the FIFN-based circuit and is shown in Fig. fer function of this filter is:

$$\frac{-s/3C_1R_2}{\left(\frac{1}{C_1R_1} + \frac{1}{3C_2R_2} - \frac{1}{3C_1R_2}\right) + \frac{1}{3C_1C_2R_1R_2}}$$

(3)

fatural angular frequency and quality factor

$$\omega_0 = \frac{1}{\sqrt{3C_1C_2R_1R_2}} \tag{4}$$

$$Q = \frac{\sqrt{3C_1C_2R_1R_2}}{3C_1R_2 + C_1R_1 - C_2R_1}$$

(5)

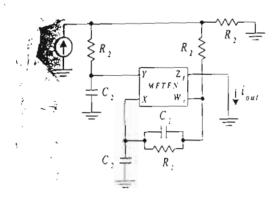

FTFN-based current-mode band-pass filter.

components are chosen as  $R_1 = 3 \text{ k}\Omega$ ,  $R_2 = 1 \text{ k}\Omega$  $C_2 = 0.5 \text{ nF}$ . The simulation result of the filter

Fig. 7 Simultations result of FTFN-based current-mode band-mass filter and ideal function.

using the proposed multi-output FTFN, function as a traditional FTFN, and using ideal transfer function are compared in Fig. 7. It is clearly seen the perfect match between the two cases over a very wide frequency range. This is due to the truly high gain and wide bandwidth of the proposed device.

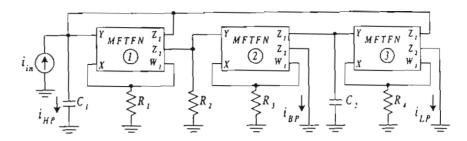

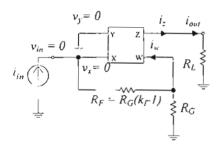

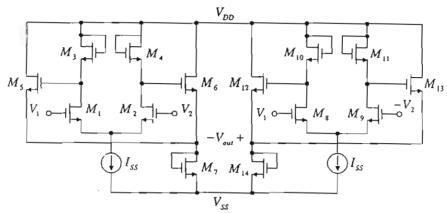

The other interesting application that demonstrated the availability of multi-output principle is the current-mode multifunction biquadratic filter. This filter can simultaneously realise three types of current-mode filtering function i.e. low-pass, band-pass and high-pass in the same configuration without changing any circuit topology or elements. Moreover, its primary parameters, the natural angular frequency  $\omega_0$  and the quality factor Q, can be orthogonally tuned and both of its active and passive sensitivities are quite small [2].

The accomplishment design of the filter using MFTFNs is shown in Fig. 8. It has all passive components really grounded. By routine circuit analysis, the following current transfer functions yielded

$$T_{HP}(s) = \frac{i_{HP}(s)}{i_{i_0}(s)} = \frac{s^2}{D(s)}$$

(6)

$$T_{RP}(s) = \frac{\iota_{RP}(s)}{\iota_{rr}(s)} = -\frac{s\left(\frac{1}{C_{r}R_{r}}\right)}{D(s)}$$

(7)

$$T_{LP}(s) = \frac{i_{LP}(s)}{i_{m}(s)} = -\frac{\left(\frac{R_{-}}{C_{+}C_{-}R_{+}R_{+}R_{+}}\right)}{D(s)}$$

(8)

and  $D(s) = s^{2} + s \left(\frac{1}{C_{1}R_{1}}\right) + \left(\frac{R_{2}}{C_{1}C_{2}R_{1}R_{3}R_{4}}\right)$

where  $T_{HP}(s)$ ,  $T_{BP}(s)$  and  $T_{LP}(s)$  are the high-pass, bandpass and low-pass current transfer functions, respectively. These transfer functions can be contemporaneously obtained from the original circuit without changing any configuration and elements. The natural angular frequency  $\alpha_0$  and the Q-factor of this configuration can be given by

$$\omega_{\rm n} = \sqrt{\frac{R_2}{C_1 C_2 R_1 R_1 R_1}} \tag{9}$$

$Q = \sqrt{\frac{C_1 \mathcal{R}_1 \mathcal{R}_2}{C_2 \mathcal{R}_1 \mathcal{R}_2}} \tag{10}$

and

Fig. 8 Current-mode multifunction biquadratic filter using MFTFN.

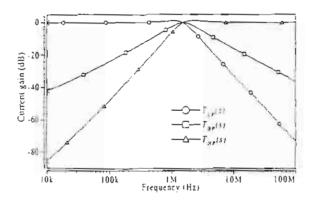

The grounded resistor values are set to  $R_1 = R_2 = R_3 = R_4 = 1 \,\mathrm{k}\Omega$  while the grounded capacitor values are  $C_1 = C_2 = 0.1$  nF. The setting was designed to acquire the natural frequency  $\omega_0 / 2\pi = 1.59$  MHz at Q-factor = 1. Fig. 9 shows the simulated frequency responses of the multifunction biquadratic filter using the proposed MFTFN. The simulated natural frequency measured from the HSPICE is approximately equal to 1.55 MHz, which attained to be in a very good agreement with the predicted value.

Fig. 9 Simulation result of the current-mode multifunction filter using MFTFN.

#### 6. Summary

We have proposed a simple scheme for implementing FTFN circuit with additional extended output port. The proposed scheme is suitable for CMOS process monolithic integrated circuit form, and has been realised through the use of a complementary transconductance amplifier, a translinear cell and some of current mirrors. Simulation results from HSPICE program are used to confirm the high performance of our presented structure. The current-mode band-pass filter is an example to identify the feasibility of the FTFN-based circuit. The current-mode inultifunction biquadratic filter is also used to demonstrate the

of the device and additional useful applications will the subjects of the further publications.

#### 7. Acknowledgements

This work is partly funded by the Thailand Research Fund (TRF), under the senior Research Scholar Program grant number RTA/04/2543. The support from the Japan International Cooperation Agency (JICA) is also gratefully acknowledged.

#### 8. References

- [1] B. Chipipop and W. Surakampontom, "Realisation of current-mode FTFN-based inverse filter," Electronics Letter, vol. 35, 1999, pp. 690-692.

- [2] W. Tangsrirat, S. Unnavanich, T. Dumawipata and W. Surakampontorn. "A realization of currentmode biquadratic filters using multiple-output: FTFNs." Proceeding of IEEE APCCAS2000, 2000, pp. 201-204.

- [3] M. T. Abuelma'attı and H. A. Al-Zaher, "Current-Mode Sinusoidal Oscillators Using Single FTFN," IEEE trans, on Circuits and Systems II: Anslog and Digital Signal Processing, vol. 46, 1999, pp. 69-74.

- [4] U. Çam, A. Toker and H. Kuntman, "CMOS FTFN realisation based on translinear cells," *Electronics Letter*, vol. 36, 2000, pp. 1255-1256.

- [5] TH. Laopoulos, S. Siskos, M. Bafleur, PH. Givelin and E. Tourmer, "Design and applications of an easily integrable CMOS operational floating amplifier for the megahertz range," Analo; Integrated Circuits and Signal Processing, vol. 7, 1995, pp. 103-111.

- [6] J. H. Huising and J. De Korte, "Monolithic Nullor A Universal Active Network Element," *IEEE J. Solid-State Circuits*, vol. 12, 1977, pp. 59-64.

- [7] M. T. Abuelma'attı, H. A. Al-Zaher and M.A. Al-Qahtani, "Novel grounded-capacitor active biquads using FiTFN," *Microelectronics Journal*, vol. 29, 1398, pp. 123-132.

- [18] E. Säckinger and W. Guggenbühl, "A high-swing, high-impedance MOS cascode circuit," *IEEE J. Solid-State Circuits*, vol. 25, 1990, pp. 289-298.

- [9] H. O. Elwan and A. M. Soliman, "Low-voltage low-power CMOS current conveyor," *IEEE trans. on Circuits and Systems I: Fundamental Theory and Applications*, vol. 44, 1997, pp. 828-835.

### **PROCEEDINGS**

# 2001 IEEJ International Analog VLSI Workshop

May 14-15, 2001 Fortune Hotel, Bangkok, Thailand

#### AN INTEGRABLE CMOS-BASED GROUNDED-CAPACITOR TRUE RMS-TO-DC CONVERTER

K. Kaewdang, K. Kumwachara, C. Fongsamut, A. Jiraseree-amornkun and W. Surakampontorn

Faculty of Engineering and Research Center for Communication and Information Technology

King Mongkut's Institute of Technology Ladkrabang

Ladkrabang, Bangkok 10520, Thailand.

Phone: (662)326-9968, Fax: (662)739-2398

Email: s3061304@kmitl.ac.th

#### Abstract

A simple integrable CMOS circuit design technique to realize a grounded-capacitor true rms-to-de converter is described in this paper. The conversion circuit consists of a squarer circuit, a low-pass filter and current mirrors and does not require a full-wave rectifier circuit. In order to reduce the value of the capacitor suitable for monolithic integration, a capacitance multiplier circuit that can multiply the value of the capacitance for the order of 1,000 time is also incorporated. The performance of the proposed circuit is studied through PSPICE and Cadence simulation results.

Keywords: True RMS-to-DC Converter, Capacitance multipliers, Analog VLSI

#### 1. Introduction

It is well accepted that a true rms-to-de converter, which is used for measuring the average energy content in an electrical signal, is found useful in the fields of instrumentation, communication and display systems. Many true rms-to-dc converters are available. However, these design methods are based on bi-polar integrated circuit technology and the rms-to-dc conversions are performed through the use of a full-wave rectifier and a multiplier/divider circuits employing a log-antilog principle[1-3]. Due to the bandwidth and the slew-rate of the full-wave rectifiers, the useful frequency range of these converters are limited. Although, a design technique for a true rms-to-dc converter based on the use of a dual translinear loop have been proposed recently [4]. However, the implementation scheme is suitable for bipolar technology. As more and more electronic systems are implemented using CMOS technology, the purpose of this paper is to present a CMOS circuit technique for the realization of a true rms-to-dc converter, where a grounded capacitor is used. A full-wave rectifier is not required by the proposed realization scheme. The conversion circuit is simple, suitable for implementing in monolithic integrated form, and can be readily integrated as part of a larger system. The performance of the conversion

circuit is studied from PSPICE and Cadence IC circuit design systems simulation results.

#### 2. Conversion Circuit

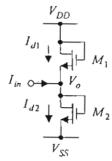

The proposed grounded-capacitor true rms-to-dc converter is shown in Fig 1. The operation of the circuit is based on the square law characteristic of MOS transistors biased in the strong inversion region [5,6]. Transistors  $M_1$  through  $M_3$  function as a current squarer circuit, where  $M_4$  and  $M_6$  and the current  $I_O$  form the current-controlled bias circuit, and the current  $I_{SA}$  can be written as

$$I_{SA} = I_{IN}^2 / 8I_O + 2I_O \tag{1}$$

where the currents  $I_{IN}$  and  $I_O$  are the input and the bias currents, respectively. Due to we design such that the drain of transistor  $M_5$  sources the current  $2I_O$  at point A, then the current  $I_{SO}$  can be expressed as

$$I_{SQ} = I_{IN}^2 / 8I_O (2)$$

The current  $I_{SQ}$  passes through the first-order current-mode low-pass filter, which is consisting of the current mirror (formed by transistors  $M_7$  and  $M_8$ ) and the grounded capacitor  $C_{AV}$  connected parallel to the mirror input. The current  $I_{OI}$  can be written as

$$I_{OI} = \frac{I}{8I_{O}T} \int I_{IN}^{2} dt \tag{3}$$

where  $T = C_{AM}/gm_7$  is the time constant of the filter and  $gm_7$  is the transconductance of the transistor  $M_7$ . Due to the unity gain current mirrors of  $(M_7$  and  $M_8$ ) and of  $(M_{11}$  and  $M_{12})$ , the bias current  $I_O$  is driving by  $I_{OI}$  such that

$$I_O = I_{OI} \tag{4}$$

At the output, since we set the transistor channel widths as  $W_{I3} = \sqrt{8} W_{II}$ , this means the output current

$$I_{RMS} = \sqrt{8}I_{Q} \tag{5}$$

Then, from eqns. (2),(3) and (4) and solving for  $I_{RMS}$ , we get

$$I_{RMS} = \sqrt{\frac{I}{T} \int I_{IN}^2 dt}$$

(6)

It is clearly seen that the output current  $I_{RMS}$  is in the form of the root-mean-square value as required. It should be noted that, for a sinusoidal signal, the circuit can be easily modified to also measure the average value of the signal by using the method of the reference 7.

However, in order that the proposed rms-to-dc converter give a good performance in the required frequency range, the value of the capacitor  $C_{AV}$  must be chosen such that [4]

$$C_{AV} >> g_{m7(MAX)}/4f_{(MIN)} \tag{7}$$

where  $f_{(MIN)}$  is the lower end of the frequency range of interest. For example, for  $K_P = 2.226 \times 10^{-5}$  A/V, then  $gm_{7(MAX)}$  can be given by

$$g_{m7(MAX)} = 29.84 \times 10^{-3} \sqrt{I_M} A/V$$

(8)

where  $I_M$  is the peak amplitude of the input signal. In this case  $C_{AV}$  must be chosen such that

$$C_{AV} >> (2.37 \times 10^{-3} \sqrt{I_M}) / f_{(MIN)}$$

(9)

If a sinusoidal input signal with  $I_M = 1$  mA and  $f_{(MIN)} = 100$  Hz, the averaging capacitance must be chosen such that  $C_{AV} >> 0.75 \ \mu\text{F}$ . For example,  $C_{AV} = 7.5 \ \mu\text{F}$  must be employed. It is well accepted that this value of capacitance is not suitable for monolithic integration.

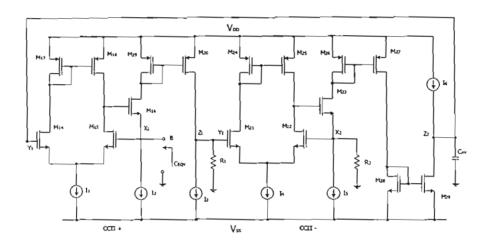

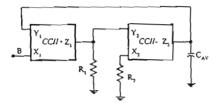

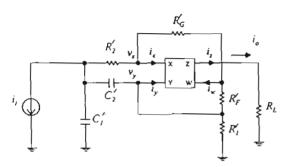

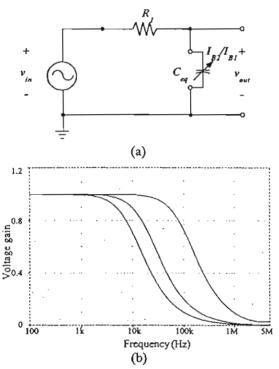

To reduce the size of the capacitor used, a current-controlled C-multiplier as shown in the Fig. 2 is presented, where the current conveyors (CCIIs) that reported in reference 9 have been used. The current-controlled C-multiplier, which is composed of two CCII (CCII+ and CCII-), is similar to the voltage-controlled C-multiplier proposed in the reference 8. But, in this case, the input signal is a current signal that injected into port  $X_1$  and the capacitor  $C_{AV}$  is connected at the port  $Y_1$ . If we let  $n = R \not R_I$ , the value of the capacitance that appeared at the port B to ground or  $C_{EQV}$  will be equaled to

$$C_{rov} = nC_{Av} = (R_1/R_1)C_{Av}$$

(10)

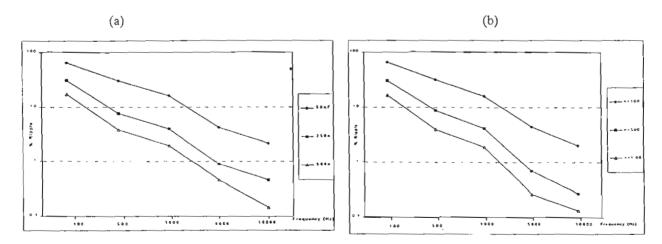

#### Simulation results

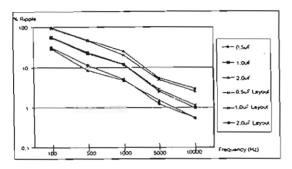

The characteristics of the converter were studied through the simulation results using PSPICE [10]. The transistor dimensions of the circuit in Fig.1 are in micron and are listed in the Table 1, where W is channel width and L is channel length, and the dimensions of all the transistor of the circuit in Fig 2 are W=50µm and L=5µm. The simulation was carried out using the transistor parameter of the 0.35-um CMOS TSMC Therefore, the simulation results were listed in the Table II. Note that the circuit exhibits the bandwidth of 200 MHz at  $I_{IN} = 1$  mA<sub>ms</sub>. The maximum conversion nonlinearity, for the input signal in the range from 2 uA<sub>rms</sub> to 1 mA<sub>rms</sub>, of about 0.8 % was achieved. The simulation for the frequency response for the sine wave input current signal with the amplitude of 20, 50 and 90 percents of the full scale current  $(I_{IN(MAX)}=1\text{mA})$ was also carried out. The results show the bandwidth of about 30 MHz, 80 MHz and 100 MHz, respectively. Fig. 3(a) shows the plot of the percent ripple of the  $I_{RMS}$ versus frequency. The simulation results demonstrate that the percent ripple is small for high value of CAV, such as, for example, for the case of  $C_{AV} = 2.5 \mu F$  and  $C_{AV} = 5 \mu F$ . Fig. 3(b) shows the plot of the percent ripple of the  $I_{RMS}$  versus frequency for the case that  $C_{AV}$ has been replaced by the C-multiplier circuit of the Fig.2, where port B is connected to point A of the Fig. 1. In order to compare with the plot in the Fig. 3(a),  $C_{AV}$  and  $R_1$  are kept constant at 0.5 nF and 10  $\Omega$ , respectively, and n is varied by varying the value of the resistor R2, for n=100, 500 and 1,000, respectively. From the Fig. 3(b), it is demonstrated that the percent ripple for the case of n=100, 500 and 1000 are quite in good agreement with the percent ripple for the case  $C_{AV}$ =50nF, 250nF, and 500nF, respectively, of the Fig. 3(a). But, however, we found that for larger value of n, the percent ripples for the case of C-multiplier are larger than the percent ripples of the circuit in Fig.1, particularly for the high frequency range. This is due to that for large value of n the offset of the CCIIs have also been multiplied and cause the value of  $C_{EQV}$  deviated from the value predicted from the eqn. (10).

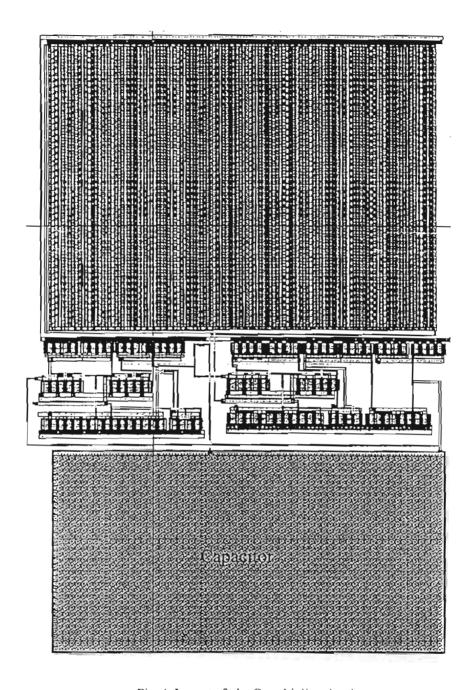

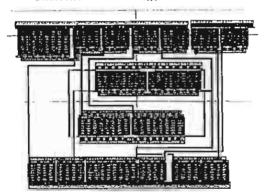

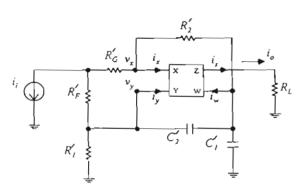

However, the simulation performance of the circuit using PSPICE is much depending on the chosen transistor parameters. Therefore, in order to test for the circuit workability, the performance of the rms-to-dc converter circuit and the C-multiplier circuit will be further studied through the layout by using Cadence's IC Circuit Design Systems, which is an integrated circuit design software running on Workstation [11]. The layout in a 0.35 um TSMC CMOS process was drawn by using Virtuoso Layout Editor of Cadence's system. Fig. 4 shows the layout of the C-multiplier circuit. The Diva interactive Electrical Rules Checker program, which is the layout extractor in the Cadence program, was then employed to translate the layout drawing into the SPICE-compatible text file for the simulation. Then the Analog Artist Design Environment is used to simulation the C-multiplier Table III shows the effective capacitances of the layout circuit of the Fig. 4, where for n = 1,  $C_{AV} = 100$  pF. Further investigation for the performance of the circuit for a large value of n and also the rms-to-dc converter will be reported.

#### 4. Conclusion

We have developed a simple grounded-capacitor true rms-to-de conversion circuit. For a more suitable for monolithic integration, the capacitance multiplier circuit has been used in order to reduce the value of the capacitor. The realization scheme is suitable for implemented in a standard CMOS process. The circuit has been fully simulated, through the use of PSPICE simulation program, and the characteristics of the conversion circuit have been reported. The circuit characteristic studied from Cadence IC circuit design systems is also included.

#### 5. Acknowledgments

This work is partly funded by the Thailand Research Fund (TRF), under the senior Research Scholar Program grant number RTA/04/2543. The support of the Cadence IC Circuit Design Systems from the Japan International Co-operation Agency (JICA) is also gratefully acknowledged.

#### 6. References

- J.K. Kalanko, "Accurate measurement of power, energy, and true rms voltage using synchronous counting, "IEEE Trans. Instrum. Meas., vol. 42, pp.752-754, 1993.

- E. Seevinck, R.F. Wassenaar and H.C.K. Wong, "

A wide-band technique for vector summation and rms-to-dc conversion, " IEEE J. Solid-State Circuits, vol. SC-19, pp.311-318, 1984.

- R.F. Wassenaar, E. Seevinck, M.G. Van Leeuwen, C.J. Speelmanand and E. Holle, "New techniques for high-frequency rms-to-dc conversion based-on a multifunctional v-to-i converter," *IEEE J. Solid-State Circuits*, vol. 23, pp.802-814, 1988.

- W. Surakampontorn and K. Kumwachara, "A dual translinear-based true rms-to-dc converter," *IEEE Trans.Instrum. Meas.*, vol. 47, pp.459-464, 1999.

- K. Bult and H. Wallenga, "A class of analog CMOS circuits based-on the square-law characteristic of an MOS transistor in saturation," *IEEE J. Solid-State Circuits*, vol. SC-22, no.6, pp.357-365, 1987.

- O. Landolt, E. Vitlez and P. Heim, "CMOS self biased euclidean distance computing circuit with high dynamic range," *Electron. Lett.*, vol. 28, no.4, pp.352-354, 1992.

- W. Wang, "Novel pseudo RMS current converter for sinusoidal signals using a CMOS precision current rectifier," *IEEE Trans. Instrum. Meas.*, vol. 39, pp.670-671, 1990.

- G. Di Cataldo, G. Ferri and S. Pennisi, "Active capacitance multipliers using current conveyors," Proc. 1998 IEEE International Symposium on Circuits and Systems, vol.2, pp.343-346, 1998.

- W. Surakampontorn, V. Riewruja, K. Kumwachara and K. Dejhan, "Accurate CMOS-based current conveyors," *IEEE Trans. Instrum. Meas.*, vol. 40, pp.699-702, 1991.

- PSPICE, Microsim Corp., Laguna Hills, CA 92653, U.S.A., May, 1980.

- 11). Cadence Design Systems, San Jose, CA 95134, U.S.A., December 1995.

Table I Transistors dimension

| Transistors          | W(μm) | L(µm) |

|----------------------|-------|-------|

| M1,M2,M3,M4,M6,M7,M8 | 40    | 5     |

| M9,M10,M11,M12       | 100   | 5     |

| M5                   | 80    | 5     |

| M13                  | 283   | 5     |

Table II Summary of the characteristics of the circuit of Fig. 1

| Parameters                                                                                                                                                                                                                                                                                                                                                                         | Simulated results                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Supply voltage (rated)                                                                                                                                                                                                                                                                                                                                                             | 3V to 15V                                                |

| Input current range(max)                                                                                                                                                                                                                                                                                                                                                           | 1mA                                                      |

| Gain error                                                                                                                                                                                                                                                                                                                                                                         | 2% Max. nonlinearity,<br>10μA to 1mA input               |

| Peak amplitude value $I_{IN} = 10 \text{ μA}  (1.0\% \text{ of } I_{IN(MAX)})$ $I_{IN} = 100 \text{ μA}  (10\% \text{ of } I_{IN(MAX)})$ $I_{IN} = 200 \text{ μA}  (20\% \text{ of } I_{IN(MAX)})$ $I_{IN} = 500 \text{ μA}  (50\% \text{ of } I_{IN(MAX)})$ $I_{IN} = 900 \text{ μA}  (90\% \text{ of } I_{IN(MAX)})$ $I_{IN} = 1000 \text{ μA}  (100\% \text{ of } I_{IN(MAX)})$ | -3dB bandwidth 450 kHz 5 MHz 10 MHz 20 MHz 40 MHz 45 MHz |

Table III Equivalent Capacitances of the Fig. 4

| n    | Expected Capacitance (F) | Equivalent Capacitance (F) |

|------|--------------------------|----------------------------|

| 1    | 100pF                    | 96.81pF                    |

| 10   | 1nF                      | 0.973nF                    |

| 100  | 10nF                     | 9.542nF                    |

| 1000 | 100nF                    | 82.25nF                    |

Figure 1. Schematic diagram of the rms-to-dc converter.

Figure 2. A current-controlled capacitance multiplier circuit.

Figure 3. Plots of percent ripple versus frequency for (a) difference values of  $C_{\mathsf{AV}}$  and (b) difference values of n.

Fig. 4 Layout of the C-multiplier circuit

### **PROCEEDINGS**

# 2001 IEEJ International Analog VLSI Workshop

May 14-15, 2001 Fortune Hotel, Bangkok, Thailand

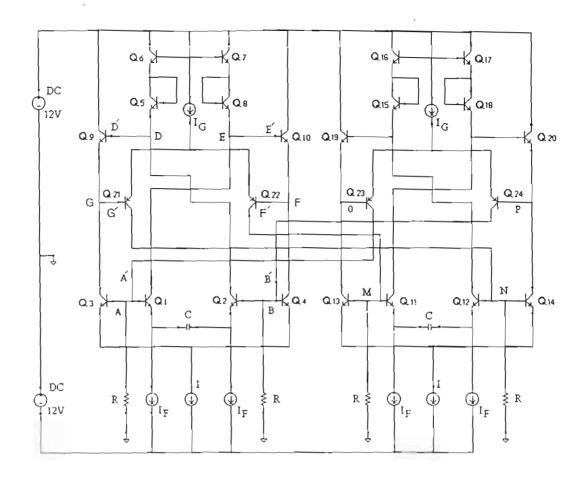

differential, input voltage  $V_{AB}$  is applied to the bases of Q1 and Q2 across nodes A and B, and the small-signal, differential, output voltage  $V_{GF}$  is taken across the emitters of Q9 and Q10 between nodes G and F. The current I /2 biases the (Q3, Q9) and the (Q4, Q10) branches, whilst the frequency setting current  $I_P$  biases the (Q1, Q8, Q7) and the (Q2, Q5, Q6) branches. The differential pair (Q21 and Q22), functioning as a voltage-to-current converter, constitutes the required loop gain controllable by the loop-gain setting current  $I_G$  to initiate and to sustain steady-stead oscillations.

Similarly, for the second stage, the phase-lead all-pass filter is formed by ten matched transistors (Q11 to Q20), a capacitor C and current sinks I and  $I_P$ , where the small-signal, differential, input voltage  $V_{MN}$  is applied to the bases of Q11 and Q12 across nodes M and N, and the small-signal, differential, output voltage  $V_{OP}$  is taken across the emitters of Q19 and Q20 between node O and P. The current I/2 biases the (Q13, Q19) and the (Q14, Q20)branches, whilst the frequency setting current  $I_P$  biases the (Q11, Q18, Q17) and the (Q12, Q15, Q16) branches. The differential pair (Q23 and Q24) constitutes the required loop gain controllable by the loop-gain setting current  $I_G$  to initiate and to sustain steady-stead oscillations.

The input of the first stage  $V_{AB}$ , across nodes A and B, is connected to the output of the second stage  $V_{A'B'}$ , across nodes A'and B', but they possess the opposite polarities. On the other hand, the input of the second stage  $V_{MN}$ , across nodes M and N, is connected to the output of the first stage, and they possess the same polarities. The circuit is fully differential so as to enable accurate quadrature signals with symmetry. There are other significant, well understood, advantages in employing a fully differential realization [17]. The circuit is also relatively simple and integrable as devices can be fabricated on-chip.

#### 3. Ideal analysis

The analysis of Fig. 1 assumes that each transistor acts as an idealized voltage-controlled current source (VCCS), where the collector current is simply equal to the small-signal voltage across the base-emitter nodes divided by re, where re is the usual ratio of the thermal voltage and the emitter bias current. The common-emitter current gain factors (β's) are also assumed to be infinite. As the two stages of Fig. 1 are identical, only the first stage will be described. For clarity, the phase-lead all-pass filter of the first stage can be described by the isolation from other connections such that the inputs of the phase-lead all-pass filter at nodes A and B are disconnected from the outputs of the second stage at nodes A' and B', respectively, and that the outputs of the phase-lead all-pass filter at nodes G and F are disconnected from the inputs of the differential amplifier at nodes G' and F', respectively.

For such isolation, it can be assumed for the moment that the bases of Q9 and Q10 at nodes D' and E' are temporarily disconnected from nodes D and E. respectively. As a result the bases of Q9 and Q10 at nodes D' and E' are then temporarily connected together to appropriate bias voltage say Vblas. In such temporary cases, let Vo1 be the small-signal, differential, output voltage at node D with respect to node E, and Vo2 be the small-signal, differential, output voltage at node F with respect to node G. The input voltage VAB results in a small-signal, differential, output current  $i_{d1} = sCV_{AB}$  / (1+st) passing through nodes D and E and the loading resistance  $4r_{e1}$  where  $r_{e1} = (V_T / I_P)$  is the emitter resistance of either Q1, Q2, Q5, Q6, Q7 or Q8, V<sub>T</sub> is the usual thermal voltage of approximately 25 mV associated with a pn junction at room temperature, and time constant  $\tau = 2Cr_{el}$ . Therefore the transfer function  $V_{O1} / V_{AB} = 2s\tau / (1+s\tau)$  represents a first-order highpass filter. In addition, VAB also results in another smallsignal, differential, output current id2 = VAB / 2re2 passing through nodes F and G and the loading resistance  $2r_{e2}$  where  $r_{e2} = (2V_T / I)$  is the emitter resistance of either Q3, Q4, Q9 or Q10. Therefore the transfer function  $V_{O2}/V_{AB} = 1$  represents a buffer.

By reconnecting the bases of Q9 and Q10 at nodes D' and E' to nodes D and E, respectively (as shown in Fig. 1), the total output voltage  $V_{GP}$ , at node G with respect to node F, is obtained through superposition, i.e.  $V_{GP} = V_{O1} - V_{O2}$  and hence the name 'signal differencing'. Consequently, the transfer function  $V_{GF} / V_{AB}$  represents a phase-lead all-pass filter with phase angle  $\theta$  of the forms

$$\frac{V_{GF}}{V_{AB}} = -\left(\frac{l - s\tau}{l + s\tau}\right) \tag{1}$$

$$\theta = 2 \tan^{-1} (\omega \tau) \tag{2}$$

where  $\theta = \pi/2$  at  $\omega = 1/\tau = I_f / (2CV_T)$ .

As mentioned earlier,  $V_{AB}$  across nodes A and B and the resulting small-signal, differential, output voltage  $V_{A'B'}$  across nodes A' and B' possess the opposite polarities. By reconnecting the phase-lead all-pass filter to the original connections as shown in Fig. 1, the relationship between  $V_{AB}$  and  $V_{A'B'}$  can be written as

$$\frac{V_{A'B'}}{V_{AB}} = -\left[G\left(-\frac{1-s\tau}{1+s\tau}\right)\right]^2 \tag{3}$$

where  $G = R / r_{e3}$  is the gain of each differential amplifier and  $r_{e3} = (2V_T / I_G)$  is the emitter resistance of either Q21 or Q22 of the first stage, or either Q23 or Q24 of the second stage. For steady-state sinusoidal oscillations to be sustained, the ratio  $V_{A'B'} / V_{AB}$  must be unity. Setting (3) to unity and rearranging yields

$$s^{2} - s\frac{2}{\tau} \left( \frac{G^{2} - 1}{G^{2} + 1} \right) + \frac{1}{\tau^{2}} = 0$$

(4)

Upon substituting s in (4) with  $j\omega_0$ , and setting the real and the complex parts to zero simultaneously, the required value of G to sustain steady-state sinusoidal oscillations and the angular frequency of oscillations  $\omega_0$  can be written as

$$G = \frac{R}{r_{ct}} = R \frac{I_C}{2V_T} \tag{5}$$

$$\omega_0 = \frac{1}{\tau} = \frac{I_F}{2CV_T} \tag{6}$$

Equation (5) shows that the required condition for steady-state oscillations can be set by adjustments of  $I_G$ . Equation (6) indicates that the frequencies of oscillations are linearly proportional to the bias current  $I_P$  and hence the name 'current-tunable'. By substituting (6) in (2) for  $\omega = \omega_0$ , it follows that the phase angle  $\theta_0$  of  $V_{MN}$  of the second stage is different from the phase angle  $\theta_1$  of  $V_{AB}$  of the first stage by  $\theta_0$ - $\theta_1 = \pi/2$ . In order words,  $V_{MN}$  and  $V_{AB}$  provide quadrature oscillation of values  $\cos \theta_0$  and  $\sin \theta_0$ , respectively, and hence the name 'sinusoidal quadrature oscillator'.

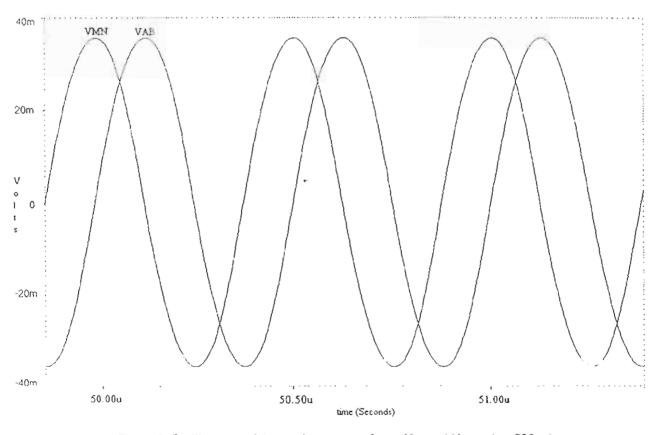

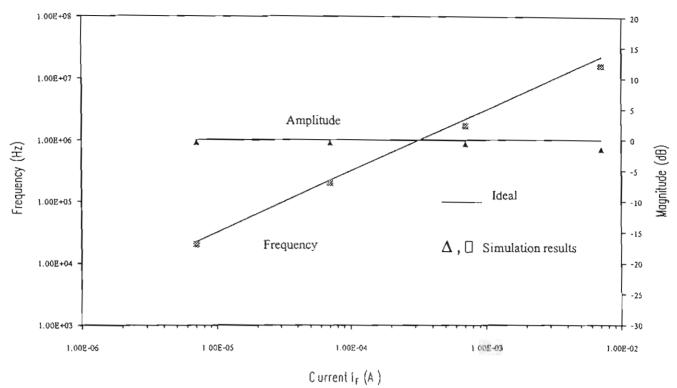

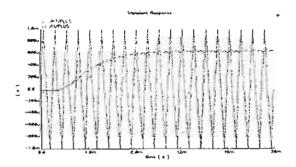

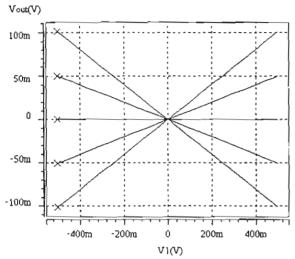

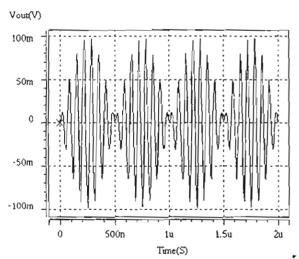

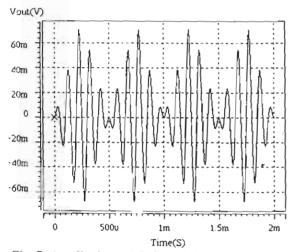

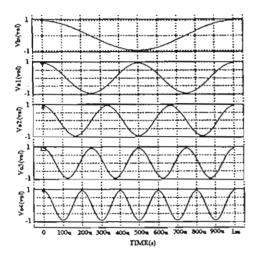

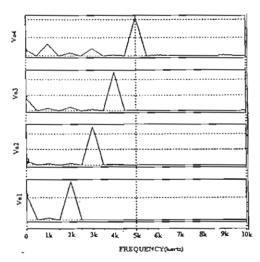

#### 4. Simulation results

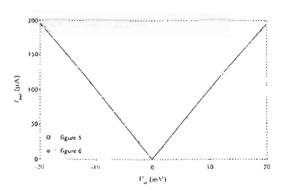

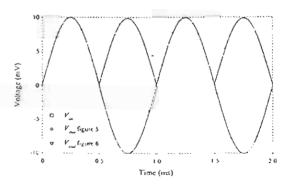

The performance of the circuit shown in Fig. 1 has been simulated through PSPICE. Q2N3904 and QMPS3640 model the npn and pnp transistors, where the average transition frequencies (f<sub>T</sub>) are at 300 and 500 MHz, respectively. As an example, the values of capacitor C is equal to 1000 pF,  $R = 50 \Omega$ , bias current I and I<sub>G</sub> are approximately 200 µA and 1.2 mA, respectively. Figure 2 shows the resulting sine and cosine oscillograms of the quadrature waveforms VAB and  $V_{MN}$ , respectively, at  $I_P = 700 \mu A$  where the oscillation frequency is measured to be 2 MHz. Figure 3 illustrates comparisons of the plots of oscillation frequencies and amplitudes versus bias current IP for cases of ideal analysis and PSPICE analysis. As shown in Fig. 3, the oscillation frequencies are tunable by the bias current I<sub>F</sub> over approximately three orders of magnitude. It can be seen from Fig. 3 that the maximum useful frequency of oscillation is approximately 19 MHz.

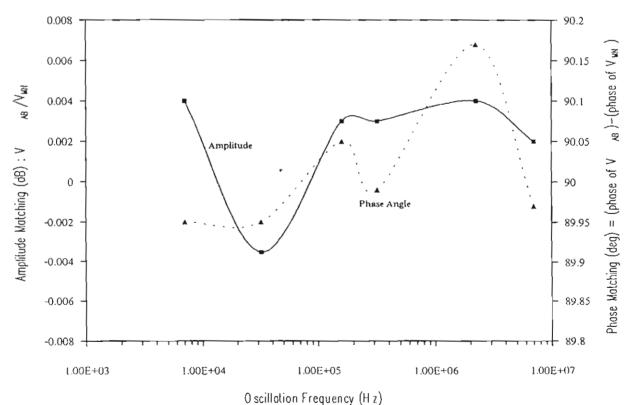

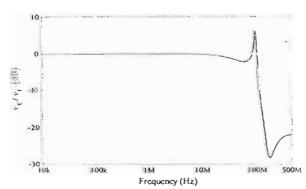

Figure 4 depicts the amplitude matching (dB) in terms of the ratio  $V_{AB}/V_{MN}$ , as well as the phase matching (deg) in terms of [(phase of  $V_{AB}$ ) – (phase of  $V_{MN}$ )] of the quadrature signals versus frequency. The amplitude matching is as near as 0.004 dB, whilst the phase matching for 90° is better than 0.17°.

#### 5. Conclusions

A fully-differential current-tunable sinusoidal quadrature oscillator has been presented using r<sub>e</sub> tunable phase-lead all-pass filters as the frequency-selective network. The filter is realized through the use of a signal-differencing technique. The oscillation frequency is current-tunable over a wide-frequency sweep range of approximately three orders of magnitude. The amplitude matching and the quadrature phase matching are better than 0.004 dB and 0.17°, respectively. The maximum useful frequency of oscillation is approximately 19 MHz.

#### 6. Acknowledgements

The authors are grateful to Mr. M. Watchakittikorn for his useful suggestion. This work is partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program, grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency (JICA) is also acknowledged.

Figure 1. Circuit diagram of the fully balanced high-frequency sinusoidal quadrature oscillator using current-tunable phase-lead all-pass filters

Figure 2. Oscillograms of the quadrature waveforms  $V_{AB}$  and  $V_{MN}$  at  $I_P$  = 700  $\mu A$

Figure 3: Plots of oscillation frequencies and amplitude versus bias current I<sub>F</sub>

Figure 4 . A mplitude and phase matching of the quadrature signals versus frequency

#### 7. References

- Verhoeven., C.J.M. "A high-frequency electronically tunable quadrature oscillator". *IEEE Journal of Solid-State Circuits*, 27: 1097-1100, 1992.

- [2] Buchwald., A.W., and Martin., K.W. "High-speed voltage-controlled oscillator with quadrature outputs". *Electronics Letters*, 27: 309-310, 1991.

- [3] Johns, D. A. and Martin, K. Analog Integrated Circuit Design. John Wiley & Sons, New York, 1997.

- [4] Linares-Baranco, B., Rodrigez-Vazqez, A., Sanchez-Sinencio, E., Huertas, J.L. "10 MHz CMOS OTA-C voltage-controlled quadrature oscillator", *Electronics Letters*, 25: 765-767, 1989.

- [5] Davidse, J. Analog Electronic Circuit Design. Prentice Hall, New York, 1991.

- [6] Tang, J.van der, Kasperkovitz, D. "A 0.9-2.2 GHz monolithic quadrature mixer oscillator for directconversion satellite receivers". Proceedings of the 1997 IEEE International Solid-State Circuits Conference, 1997, pages 88-89.

- [7] Sedra., A., and Smith., K.C. Microelectronic Circuits. 4th Ed. Oxford University Press, New York, 1998.

- [8] Duncan, R., Martin, K., Sedra, A. "1 GHz quadrature sinusoidal oscillator". Proceedings of the 17th Annual Custom Integrated Circuits Conference, May, 1995, pages 91-94.

- [9] Craninckx, J. and Steyaert, M. "A CMOS 1.8 GHz low-phase-noise voltage-controlled oscillator with prescaler". Proceedings of the 1995 IEEE International Solid-State Circuits Conference, 1995, pages 266-267.

- [10] Rofougaran, A., Rael, J., Rofougaran, M. and Abidi, A. "A 900 MHz CMOS LC-oscillator with quadrature outputs". Proceedings of the 1996 IEEE International Solid-State Circuits Conference, 1996, pages 392-393.

- [11] Pookaiyaudom, S. and Satvichit, K. "RC phase-shifter variable sinusoidal oscillators using initial conditions-restoration amplitude control". *IEEE Transactions on Instrumentation and Measurement*, 39: 1038-1044,1990.

- [12] Holzel, R. "A simple wide-band sine wave

- quadrature oscillator", IEEE Transactions on Instrumentation and Measurement, 42: 758-760, 1993.

- [13] Pookaiyaudom, S. and Samootrut, K. "Crrent-mirror phase-shifter oscillator". Electronics Letters, 23: 21-23, 1987.

- [14] Chen, J.-J., Chen, C.-C., Tsao, H.-W. and Liu, S.-I. "Current-mode oscillators using single current follower". *Electronics Letters*, 27: 2056-2058, 1991.

- [15] Liu, S.-I, and Liao, Y.-H. "Current-mode quadrature sinusoidal oscillator using FTFN", International Journal of Electronics, 81: 171-175, 1996.

- [16] Srisuchinwong, B. "Fully balanced current tunable sinusoidal quadrature oscillator", *International Journal of Electronics*, 87: 547-556, 2000.

- [17] Schaumann, R., Ghausi, M.S. and Laker, K.R. Design of analogue filters passive, active RC and switched capacitor. Prentice Hall, New York, 1990.

## **PROCEEDINGS**

# 2001 International Symposium on **Communications and Information Technology**

# **ISCIT 2001**

The Merging Decade of Communication Systems and Information Technology

November 14 - 16, 2001

Chiang Mai Orchid Hetel, Chiang Mai, Thailand

#### TUNABLE FTFN AND ITS APPLICATIONS

W. Tangsrirat

A. Jiraseri-amornkun

and W. Surakampontorn

Faculty of Engineering and Research Center for Communication and Information Technology (ReCCIT), King Mongkut's Institute of Technology Ladkrabang, Ladkrabang, Bangkok 10520, THAILAND Phone: +66-2-326-9989, Fax: +66-2-326-9989

E-mail: ktworapo@kmitl.ac.th, amorn@ieee.org, kswanlop@kmitl.ac.th

#### ABSTRACT

This paper proposes a circuit configuration for the realization of a four-terminal floating nullor (FTFN) with electronically tunable current gain. It mainly employs a transconductance amplifier, an improved translinear cell, two complementary current mirrors with variable current gain and five improved Wilson current mirrors, which provides wide bandwidth and suitability to implementation in monolithic bipolar technology. The validity of the performance of the scheme is verified through PSPICE simulation results. Some example applications employing the proposed tunable FTFN as a tunable active element show that the circuit properties can be varied by electronic means are also included.

#### 1. INTRODUCTION

Presently, current-mode circuits have drawn a considerable owing to their significant advantages, which are elementary wide bandwidth, wider dynamic range, simpler circuitry and low power consumption [1]. The realizations of current-mode circuits using high performance active devices such as, a second-generation current conveyor (CCII), a current feedback op-amp (CFA) and a fourterminal floating nullor (FTFN), have been recently reported. However, it has been demonstrated that the FTFN is more flexible and versatile building block than other active devices [2-3]. These lead up to the growing interest in designing currentmode circuits based on the use of FTFN as an active element, for instance, filters, gyrators, sinusoidal oscillators and floating immittances [2-5]. This is due to the fact that the FTFN-based structures provide a number of potential advantages such as, complete absence of passive componentmatching requirement, minimum number of employed passive elements and improvement of high frequency characteristic [6]. Although there are many FTFN realizations that have been available in the literatures [7-9], the realization scheme of an electronically tunable FTFN that is suitable for implementing monolithic integrated circuit form has not yet been reported. The FTFN whose the current gain can be tuned by electronic means seems to be more attractive, flexible and suitable for design and implementation of the frequency selective systems, such as, biquads, oscillators and so forth.

Therefore, this paper proposes an alternative scheme for realizing a monolithically integrable FTFN that can provide variable current gain. The proposed circuit is simple and based on the use of a transconductance amplifier, an improved translinear cell and some current mirrors. Some applications using the proposed tunable FTFN are given with the simulation results and will show that the characteristics of the resulting circuit become an electronically tunable.

#### 2. CIRCUIT DESCRIPTION

#### 2.1 Nullor Model of the FTFN

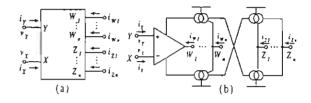

Fig.1: Model of the FTFN

(a) an ideal nullor model

(b) possible implementation model

An FTFN is a high gain transconductance amplifier with floating input and output terminals or can be called as an operational floating amplifiers (OFAs) [6]. The nullor model of an ideal FTFN is shown in Fig.1(a), where the port characteristics can be described as:

$$i_Y = i_X = 0$$

,  $v_X = v_Y$  and  $i_Z = i_W$  (1)

It should be noted that the output impedance of the W- and Z-ports are generally arbitrary. However, most of the FTFNs are traditionally realized from the basic type shown in Fig.1(b), where the output impedance of the W-port is very low and that of the Z-port is very high. This type of FTFN is also called as operational mirrored amplifiers (OMAs) [7]. In addition, the usefulness of the FTFN can be extended if eqn.(1) is implemented in such a way that the current transfer ratio between iw and iz can be varied by electronic means, in which case

a more generalized tunable FTFN should be investigated.

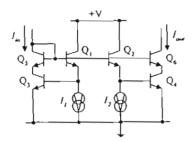

Fig.2: Cascode npn current mirror with adjustable current gain

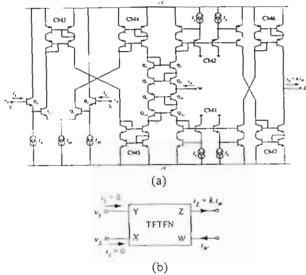

Fig.3: The proposed tunable FTFN (a) circuit diagram (b) its symbol

## 2.2 Current Mirror with Adjustable Current Gain

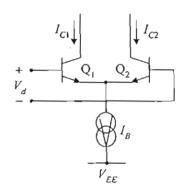

Fig.2 shows the cascode npn current mirror that can adjustable the current gain by the external bias currents, where  $I_{in}$  and  $I_{out}$  are the input and output signal currents. Transistors  $Q_t$  to  $Q_4$  function as a classical translinear loop, and the currents  $I_1$  and  $I_2$  are the external dc bias currents with controllable values [10]. In addition, the cascode stages  $Q_5$  and  $Q_6$  provide the high output impedance and also lead to minimize the severe peaking of the frequency responses. Applying the translinear principle and assuming that all the transistors are well matched with the commonemitter current gains  $\beta$  are >>1, then the relationship of the collector currents can be characterized by the following equation:

$$I_{C1}I_{C3} = I_{C2}I_{C4} \tag{2}$$

where  $I_{C1} = I_{I}$ ,  $I_{C2} = I_{2}$ ,  $I_{C3} = I_{in}$  and  $I_{C4} = I_{out}$ . Therefore, the output current  $I_{out}$  of this circuit becomes

$$I_{out} = k.I_{in} \tag{3}$$

where k is the current gain of the mirror and equals to the ratio of the external bias currents  $I_1/I_2$ .

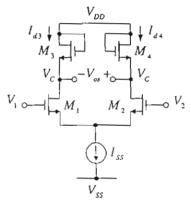

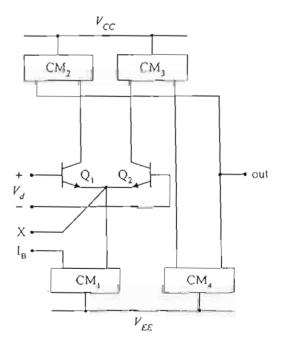

#### 2.3 Proposed Tunable FTFN

The circuit implementation and representation of the proposed tunable FTFN, namely TFTFN, with variable current gain is shown in Fig.3, which is suitable for the implementation in bipolar integrated circuit form. The proposed circuit consists of a transconductance amplifier Q1-Q4, an improved translinear cell Q5-Q12, two complementary current mirrors with controlled current gain CM1-CM2 and five standard improved Wilson current mirrors CM3-CM7. Transistors Q1-Q4 and the bias currents IB1-IB3 function as a transconductance amplifier with very high input impedance so that  $iy \cong ix \cong 0$ . If  $Q_1-Q_4$  are perfectly matched, then the voltage at node X will follow the voltage at the port Y, or  $v_X \equiv v_Y$ . Group of transistors Q5-Q12 forms an improved translinear cell, which Q7-Q10 functions as a dual translinear loop. It should be noted that the so called "piledstage structure" [11] consisting of eight transistors which can improve performance and accuracy of the basic loop is employed, where the standard translinear condition  $V_{CB} = 0$  are forced by the additive cascode transistors Q5, Q6, Q11 and Q12.

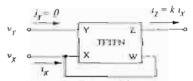

Ideally, it is required that the pair of transistors  $Q_7$ - $Q_8$  and  $Q_9$ - $Q_{10}$  are closely matched and the cascode current mirrors CM3, CM4 and CM5 have the exactly unity gain. Consequently, for  $vy \equiv v\chi \equiv$ 0, the quiescent currents through  $Q_6$ ,  $Q_8$  and  $Q_{10}$ , Q12 are respectively equal to the quiescent current of the diode-connected transistors Qs and Qu, and are equal to I<sub>BI</sub>/2. This translinear cell performs as a current follower, where its allow an input current iw to source and sink at terminal W. By two complementary variable-gain current mirrors CM1-CM2 and assuming that the current gain of the current mirrors CM6-CM7 are equal to unity, the current ity flowing through the port W will be reflected and inveited to the port Z, which has the current transfer ratio as  $k = i \frac{z}{i y}$ . The output impedance at the port W is low since it is looking into the emitters of translinear cell's transistors while the output impedance of the port Z is very high due to the effective parallel combination of output impedances of the cascode current mirrors Therefore, this TFTFN will CM6 and CM7. provide a unity voltage transfer between ports Y and X, and a current transfer between ports W and Z that the gain value is equal to k. The voltagecurrent characteristics of this device can be characterized as follows:

$$i_Y = i_X = 0$$

,  $v_X = v_Y$  and  $i_Z = k.i_W$  (4)

we can see that the proposed FTFN in Fig.3 can be tuned electronically by adjusting the ratio of the external bias currents  $I_1/I_2$ .

#### 3. SIMULATION RESULTS

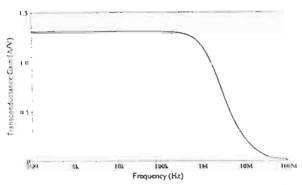

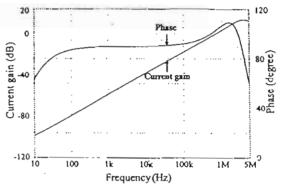

The performance of the proposed TFTFN in Fig.3 has been verified by PSPICE simulation results. The simulation results were obtained employing the AT&T ALA400-CBIC-R process parameters of NR100N and PR100N for npn and pnp transistors, respectively [12]. The bias currents were set to IBI = 1 mA,  $IB2 = IB3 = 50 \text{ \muA}$  and the supply voltages were set to +V = -V = 5V. Fig.4 shows the characteristic of the open loop transconductance gain of the proposed circuit. From the response, it can be measured that the -3dB bandwidth in a high frequency as nearly as 1.4 MHz and the transconductance gain of about 1.3 A/V is obtained.

Fig.4: Simulated open loop transconductance gain

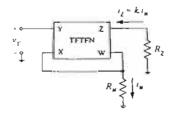

Fig.5: TFTFN-based voltage-to-current converter

Fig.6: Voltage transfer characteristic vy/vy

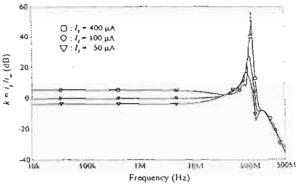

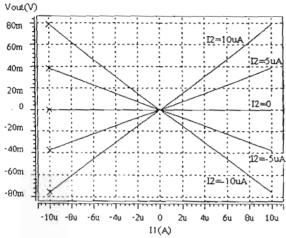

In order to demonstrate the tunable performances of the proposed circuit, the TFTFN was used to construct the voltage-to-current converter shown in Fig.5 with  $R_W = 1 \text{ k}\Omega$  and output Z short-circuited. The voltage transfer characteristic from the port Y to the port X is shown in Fig.6. Fig.7 represents the frequency responses of the current gain k, for three different values of the dc bias current  $I_I$  whereby  $I_2$  is set to  $100 \ \mu\text{A}$ . The simulated current transfer characteristic proves that the circuit can exhibit an electronically tunable current gain over a very wide current range.

Fig.7: Current transfer characteristic iz/iw when the external bias current  $I_I$  was varied.

Fig.8: An electronically tunable current conveyor

Fig.9: Current-mode allpass filter using TFTFN

#### 4. APPLICATION EXAMPLES

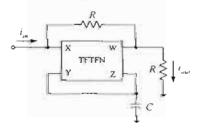

In this section, the outlines of some examples on the application of the proposed TFTFN as a tunable active element will be described, demonstrating the wide-ranging usefulness of this device. The first one is an electronically tunable current conveyor. It can be slightly modified from the circuit of Fig.3 by connecting the low-output-impedance port W to the port X as shown in Fig.8, then the circuit behaves as an electronically tunable negative current conveyor. From direct inspection of the circuit readily shows that the port relations of the tunable current conveyor of this case can be written

$$v_X = v_Y$$

,  $i_Y = 0$  and  $i_Z = k i_X$  (5)

As the second example of the proposed TFTFN, it was constructed an electronically tunable current-mode allpass filter shown in Fig.9. The circuit is based on a current-mode allpass filter by using FTFN with grounded capacitor [3], routine analysis yields the current transfer function expressed by

$$\frac{I_{out}(s)}{I_{in}(s)} = \frac{1 - \left(sRC/k\right)}{1 + \left(sRC/k\right)} \tag{6}$$

and

$$\theta_{\vec{a}} = -2 \tan^{-1} \left( \frac{\omega RC}{k} \right)$$

(7)

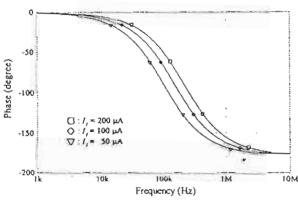

where  $\theta_d$  is the phase angle of the filter. As an example, the simulation results of a current-mode allpass filter in Fig.9 were presented with R=1  $k\Omega$ , C=1 nF, this phase shifter was designed for a 90° phase shift at  $\omega_0/2\pi=159$  kHz when k=1 ( $I_1=I_2=100$   $\mu$ A). Fig.10 shows the frequency responses of the filter of Fig.9 for three different values of the control currents,  $I_1$ . In the figure, it can be seen that the parameter  $\theta_d$  can be adjusted by controlling the current gain  $k=I_1/I_2$ . This confirms the validity of the results of the theoretical analysis.

Fig. 10: Frequency responses of the TFTFN-based current-mode allpass filter

#### 5. CONCLUSIONS

A generalized electronically tunable FTFN, which is suitable for realizing in bipolar monolithic integrated circuit form, has been presented. Simulation results obtained from PSPICE program verify the high qualification performances of the proposed circuit. Some application examples have been demonstrated that the use of the proposed scheme is attractive in that the obtained characteristic of the circuit will become electronically tunable.

#### 6. ACKNOWLEDGEMENT

This work was partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program, grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency (JICA) is also acknowledged.

#### REFERENCES

- B. Wilson, "Recent development in current conveyors and current mode circuits", IEE Proceedings, Pt. G., Vol.137, pp.63-77, 1990

- [2] M. Higashimura, "Realization of current-mode transfer function using four-terminal floating nullor", Electronic Letters, Vol.27, pp.170-171, 1991.

- [3] M. Higashimura, "Current-mode allpass filter using FTFN with grounded capacitor", Electronic Letters, Vol. 27, pp.1182-1183, 1991.

- [4] S.I. Liu, "Single-resistance-controlled sinusoidal oscillator using two FTFNs", Electronic Letters, Vol.33, pp.1185-1186, 1997.

- [5] R. Senani, "A novel application of fourterminal floating nullors", Proceedings of the IEEE, Vol.75, pp.1544-1546, 1987.

- [6] J.H. Huijsing, "Operational floating amplifier", IEE Proceedings, Pt. G., Vol.137, pp.131-136, 1990.

- [7] J.H. Huijsing and C.F. Veelenturf, "Monolithic class AB operational mirrored amplifier", Electronic Letters, Vol.17, pp.119-120, 1981.

- [8] T.H. Laopoulos, S. Siskos, M. Bafleur, P.H. Givelin and E. Tournier, "Design and application of an easily integrable CMOS operational floating amplifier for the megahertz range", Analog Integrated circuits and Signal Processing, Vol.7, pp.103-111, 1995.

- [9] U. Cam, A. Toker and H. Kuntman, "CMOS FTFN realization based on translinear cells", Electronic Letters, Vol.36, pp.1255-1256, 2000

- [10] B. Gilbert, "Current-mode circuits from a transfinear viewpoint: A tutorial", in Analog IC Design: The Current-Mode Approach, TOUMAZOU, C., LIDGEY, F.J., and HAIGH, D.G., Eds. London, U.K.: Peter Peregrinus, pp.11-91, 1990

- [11] A. Fabre, "New formulations to describe translinear mixed cells accurately", IEE Proceedings, Pt. G., Vol.141, pp.167-173, 1994

- [12] D.R. Frey, "Log-domain filter: an approach to current-mode filtering", IEE Proceedings, Pt. G., Vol.140, pp.406-416, 1993

#### REALIZATION OF CURRENT-MODE FTFN-BASED LOWPASS FILTER FROM THE OPTIMAL SALLEN AND KEY LOWPASS FILTER (SARAGA DESIGN) USING DRIVING POINT IMPEDANCE AND SIGNAL-FLOW GRAPH (DPI/SFG) METHOD TO PRESERVE THE SENSITIVITIES OF THE ORIGINAL CIRCUIT

B. Chipipop and W. Surakampontorn

Mixed-Signal Laboratory

Department of Electronics

Faculty of Engineering

King Mongkut's Institute of Technology

Ladkrabang

Ladkrabang

Ladkrabang, Bangkok 10520 Thailand

Phone: (662)-(02)-326-7723

Fax: (662)-(02)-326-9968

E-mail: boonruk@cpe.eng.kmutt.ac.th

Mixed-Signal Laboratory

Department of Electronics

Faculty of Engineering

King Mongkut's Institute of Technology

Ladkrabang

Ladkrabang, Bangkok 10520 Thailand Phone: (662)-(02)-326-7723 Fax: (662)-(02)-326-9968 E-mail: kswanlop@kmitl.ac.th

#### ABSTRACT

This paper shows that the current-mode FTFN-based lowpass filter obtained from the optimal voltage-mode op-amp-based Sallen and Key lowpass filter (Saraga Design) using driving point impedance and signal-flow graph (DPI/SFG) method preserves the optimal passive sensitivities and has better active sensitivities.

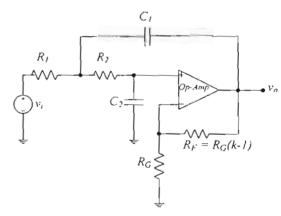

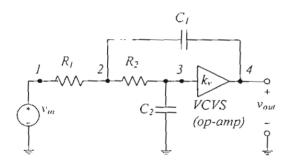

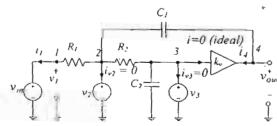

#### 1. INTRODUCTION