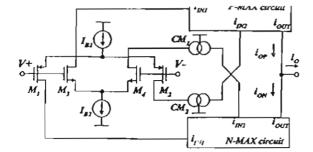

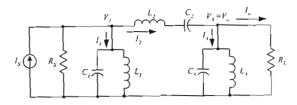

Fig.3 Rail-to-rail input stage using current selector circuit

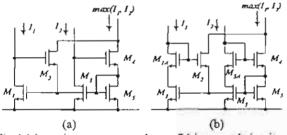

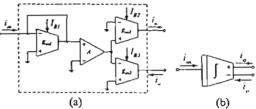

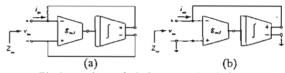

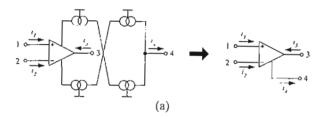

The proposed structure is shown in Fig. 3. Transistors  $M_i$  to  $M_4$  and the bias current sources  $I_{B1}$ ,  $I_{B2}$  perform the P-N complementary differential pairs. The output signal currents are sent to the maximum current selector P-MAX and N-MAX, where PMAX and NMAX are symbols of PMOStype and NMOS-type circuit, respectively. CM<sub>1</sub> and CM<sub>2</sub> are replaced with the unity gain current mirrors. The maximum-current selector proposed by Huang and Lui has been chosen for our work and the NMOS-type circuit is redrawn in Fig. 4(a). This maximum circuit was developed based on the bounded difference equation analysis, which can diminish the accumulated errors in the old type binary tree structure [7]. It works like a Wilson current mirror, therefore, the accuracy of the selector circuit can be gained up by appending the additional diode in the same manner as improved Wilson current mirror. In this case, transistor  $M_{LA}$ and Mid have been added to the circuit as shown in Fig. 4(b). From the basic analysis of the differential amp, the total output current io can be simply depicted as

$$i_{O} = \max(g_{mN}, g_{mP})(v_{+} - v_{-})$$

(3)

Fig.4 (a) maximum current selector (b) improved circuit

where  $g_{mN}$  and  $g_{mP}$  are transconductance gain of N and P pairs, respectively. Moreover, since this technique directly measures current from diff-amp using only current maximum selector circuit, it can work well independent of transistor process (bipolar or CMOS) and mode of operation (weak or strong inversion).

### 3.2 Output stage

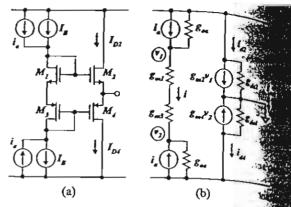

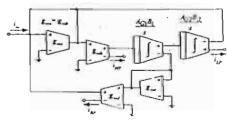

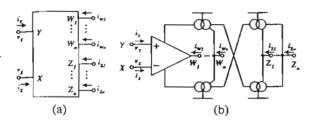

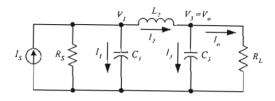

The dual translinear loop output stage is shown in Fig. 5(a) which has been modified by injecting small signal current  $i_a$  along with DC current bias  $I_B$ . The small signal model for calculating current gain  $A_i$  of this stage appears in Fig. 5(b). Assume all transistors are identical, we can estimate the current gain as

Fig.5 (a) translinear O/P stage (b) small signal model

$$A_{l} = \frac{i_{out}}{i_{o}} = \frac{g_{m(tran)}}{g_{os} //g_{os}}$$

where  $g_{m(nom)}$  is the transconductance gain of M transistor in translinear loop and  $g_{\infty}$  is the conductance of current signal source  $i_{\infty}$

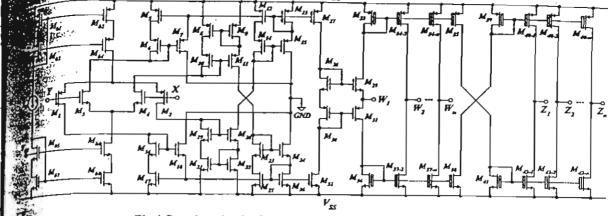

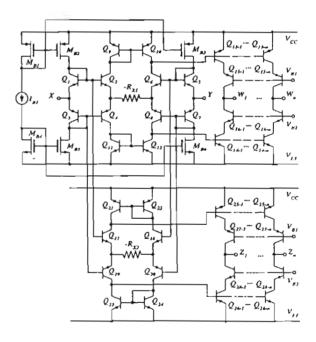

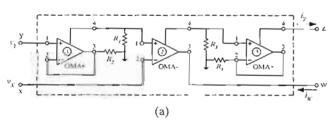

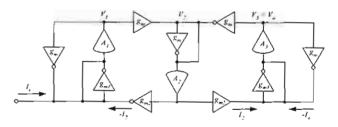

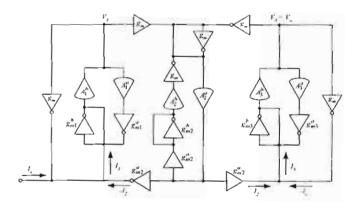

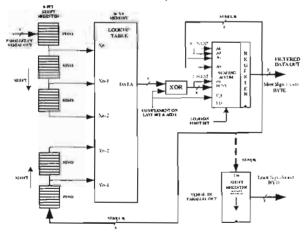

### 3.3 Overall amplifier

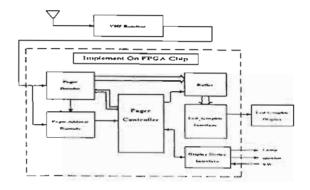

The simplified schematic of the constant-g, rail-to-CMOS multi-output FTFN is illustrated in Fig. 6. 12 designed with the building blocks introduced above, using 0.7 µm CMOS process supplied by EUROPRACTICE According to the complete circuit, the maximum selected current from the input stage will be sensed and enlarged transistor  $M_{27}$ ,  $M_{32}$  before injected to the translinear cell  $M_{28} - M_{31}$ , and then summed to be output current at port W<sub>I</sub>. This configuration provides high transconductance gain over a wide frequency range. Transistors M33 and M4 detect output current at port Wian d then copy to the other ports. Ideally, it is required that the translinear loop transistors  $M_{28} \sim M_{31}$  are closely matched and all currents mirrors have the exact unity gain. We can evaluate the total transconductance gain G<sub>m</sub> of this FTFN from combining equation (3) and (4) and give

$$G_{m} = \frac{i_{W1}}{(v_{Y} - v_{X})} = \frac{\max(g_{mN}, g_{mP})g_{m(tran)} \frac{(W/L)_{11}}{(W/L)_{13}}}{g_{ds27} // g_{ds32}}$$

It should be noted that the transistor with a box at its gale imply to be the super transistor such as cascode or regulated cascode transistor. After using the FTFN in the network with a proper feedback, the translinear cell act as a current follower that allows output current  $i_{WI}$  to sources and sinks at port  $W_I$  and will be reflected and inverted to be current  $i_{ZI}$  at terminal  $Z_I$ , which keeps up  $i_{ZI} \cong -i_{WI}$ . The multi-output topology can be easily adapted by adding transistors to the output current mirror set. Transistors  $M_{3L-2} - M_{3L-n}$  are used to perform the output terminals  $W_I$  to  $W_{n_I}$ , respectively. Similarly, transistors  $M_{4L-2} - M_{4L-n}$  are used to perform the output terminals  $W_I$  to  $W_{n_I}$  respectively. Similarly, transistors  $M_{4L-2} - M_{4L-n}$  are used to perform the output terminals  $W_I$  to  $W_{n_I}$  respectively. Similarly, transistors  $M_{4L-1} - M_{4L-n}$  are used to perform the output terminals  $W_I$  to  $W_{n_I}$  respectively.

Fig.6 Complete circuit of constant-g, rail-to-rail multi-output FTFN

### 3. Simulation Results

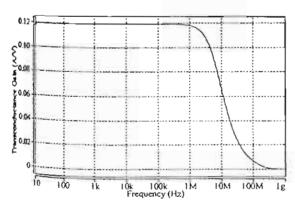

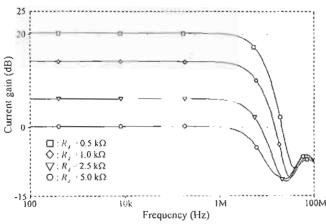

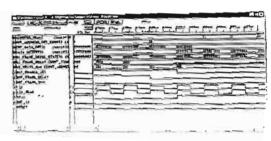

The performance of the proposed circuit is verified by BPICE circuit simulation program based on 0.7- $\mu$ m OMOS process level-49. All transistor dimensions are listed in Table 1, where W is channel width and L is channel length. The bias currents are set to  $I_B = 50 \mu$ A where the list voltages are  $V_{BI} = +1.5$ V and  $V_{B2} = -1.5$ V. Supply voltages are taken as  $V_{DO} = +2.5$ V and  $V_{SS} = -2.5$ V. The characteristic of open loop transconductance gain is given in Fig. The -3 dB bandwidth can be estimated as about 7 MHz and the transconductance gain about 120 mA/V is obtained.

Table 1 Transistors dimension

| Transistors                                                                                                 | W/L                 |

|-------------------------------------------------------------------------------------------------------------|---------------------|

| M <sub>11</sub> M <sub>2</sub>                                                                              | 150μ/0.7μ           |

| M <sub>h</sub> M <sub>c</sub>                                                                               | $50\mu/0.7\mu$      |

| M3-M15, M61, M62, M65, M66, M33,                                                                            | μ/0.7س              |

| $M_{342} - M_{34-0}, M_{35}, M_{39}, M_{40-1} - M_{40-1}$                                                   |                     |

| M <sub>bl</sub> , M <sub>b4</sub>                                                                           | 45µ/0.7µ            |

| M <sub>16</sub> - M <sub>26</sub> , M <sub>67</sub> , M <sub>68</sub> , M <sub>36</sub> , M <sub>41</sub> , | 5μ/0.7μ             |

| $M_{11-2} - M_{37-0}, M_{42-1} - M_{42-0}$                                                                  |                     |

| M <sub>24</sub> , M <sub>29</sub>                                                                           | 100μ/0.7μ           |

| $\underline{\mathbf{M}}_{\mathbf{x}_1} \mathbf{M}_{31}$                                                     | $300 \mu / 0.7 \mu$ |

Fig.7 Open loop transconductance gain

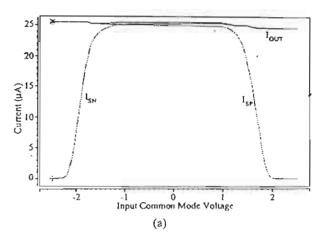

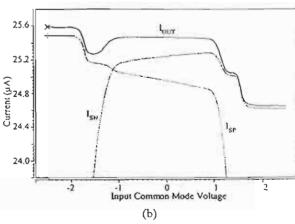

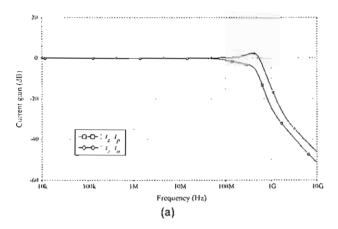

This circuit consumeab out 3mW power dissipation. Fig. 8(a) shows the input constant-g<sub>m</sub> feature where I<sub>SN</sub> and I<sub>SP</sub> are currents from N-differential pair and P-differentialp air, respectively. Fig.8 (b) shows the enlarged view of the maximum current selector operation that can notice a quite good in tracking of output current I<sub>OUT</sub>. The CMRR of the amplifier is also simulated and shown in Fig. 9.

Fig.8 (a) Input stage current (b) enlarged view

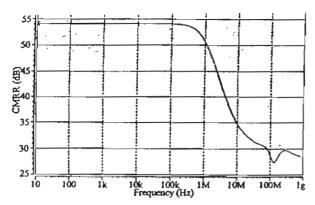

Fig.9 Simulated CMRR of the multi-output FTFN

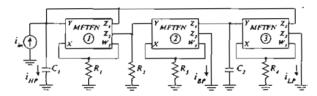

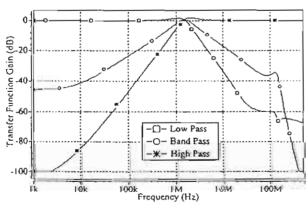

The frequency response of the CMRR can keep in the same length both in magnitude and bandwidth with a bit better compared to the method mentioned in reference 5 while our proposed structure is simpler. Realisation of a current-mode multifunction filter from reference 2 is chosen as an illustrative example. Filter's structure is redrawn in Fig. 10. MFTFN symbol refers to our proposed multi-output FTFN. The simulation result of the current-mode filter using the proposed multi-output FTFN is given in Fig. 11. It can be observed that the current-mode multifunction filter cannot response correctly since the frequency up to about 100MHz. This is due to the parasitic elements inside the FTFN, which can also be noticed the deviation at the same point of the simulated CMRR result in Fig. 9. One of the major limitations is from current selector circuit itself, which cannot operate in high frequency. The improvement can be done by improving current selector circuit's characteristic.

Fig. 10 Current-mode multifunction filter

Fig.11 Simulated results of the current-mode multifunction filter

4. Summary

We have proposed a constant-g FTFN and additional extended output port. The achievement realised through the use of a P-N complementary ductance amplifier, a translinear cell and standard current mirrors. The maximum current selectors are control the overall transconductance of the Simulation results from HSPICE program confirm qualification of our presented circuit. A current multifunction filter is an example to identify the feat of the circuit.

5. Acknowledgement

This work was partly funded by the Thailand Refund (TRF) under the Senior Research Scholar Progrant number RTA/04/2543. The support provided Japan International Cooperation Agency (JICA) acknowledged.

### References

- B. Chipipop and W. Surakampontom, "Realisation current-mode FTFN-based inverse filter," Election Letter, 35, pages 690-692, 1999.

- [2] W. Tangsrirat, S. Unhavanich, T. Dumawipata and Surakampontom, "A realization of current in biquadratic filters using multiple-output FTFF Proceeding of IEEE APCCAS2000, pages 201-2000.

- [3] U. Cam, A. Toker and H. Kuntman, "CMOS FIR realisation based on translinear cells," *Electron Letter*, 36, pages 1255-1256, 2000.

- [4] A. Jiraseree-amornkun, B. Chipipop and Surakampontom, "Novel Translinear-Based Man Output FTFN," Proceeding of ISCAS2001, pages 1 183, 2001.

- [5] F. You, S. H. K. Embabi and E. Sánchez-Sinencio, the Common Mode Rejection Ration in Low Volta Operational Amplifiers with Complementary N-P Impair," *IEEE Trans. on Circuits and Systems II*, Vol. 100, 8, pages 678-683, August 1997.

- [6] R. Hogervorst and J. H. Huijsing, "Design of low voltage, low-power operational amplifier cells Kluwer Academic Publishers, 1996.

- [7] C. -Y. Huang and B. -D. Lui, "Current-mode multiput maximum circuit for fuzzy logic controllern Electronics Letter, 30, pages 1924-1925, 1994.

Phuket Arcadia Hotel & Resort Phuket, Thailand

### ponsored by

horn International Institute of echnology, Thammasat University, Thailand Mongkut's University of Technology honburi, Thailand nal Electronic and Computer Technology Center, Thailand With Technical Cooperation of IEICE IEEK

IEEE Thailand Section

### Co-Organized by

King Mongkut's University of Technology Thonburi, Thailand Sirindhorn International Institute of Technology, Thammasat University, Thailand

try of University Affairs, Thailand

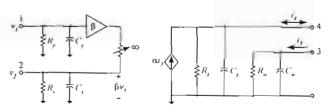

### A Simple Current-Mode Analog Multiplier-Divider Circuit Using Olas

Wanlop Surakampontorn Khanittha Kaewdang and Chalermpan Fongsamut

Faculty of Engineering and Research Center for Communication and Information Technolog (ReCCIT), King Mongkut's Institute of Technology Ladkrabang (KMITL),

Ladkrabang, Bangkok 10520, THAILAND. e-mail: s3061304@kmitl.ac.th, kswanlop@kmitl.ac.th

Abstract: An analog multiplier-divider circuit that realized through the use of OTAs, which does not require external passive circuit elements and temperature compensated, is proposed in this paper. Since the scheme is realized in such a way that employs only OTA as a standard cell, the circuit is simple and can be easily constructed from commercially available IC. The circuit bandwidth is wide and close to the transistor  $f_T$ . Simulation results that demonstrate the performances of the multiplier-divider circuit are included.

### 1. Introduction

Analog multipliers and dividers are important nonlinear building blocks that have found useful in a wide range of applications, such as telecommunication, control, instrumentation and signal processing. At present, because of the main featuring of wider bandwidth, greater linearity, wider dynamic range and simple circuitry compared with their voltage-mode counterparts, current-mode circuits have been received growing interest in analog signal processing circuits. Many techniques to design current-mode analog multiplier-divider circuits have been presented in the literature [1-3]. Recently, a multiplier-divider circuit using only two second-generation current-controlled current-conveyors (CCCIIs) has been presented, where no resistors, no capacitors and no MOS transistors are required by such a realization scheme [4].

It is well accepted that OTA is a useful circuit building block in the design of analog circuits. It has been employed in the realization of active network elements, such as filters, oscillators, instrumentation amplifiers and gyrators. The OTA is a commercially available, low cost device that incorporates all the attractive features of an operational amplifier (OA). Since OTA is a programmable device and has only a single high-impedance node, this makes the OTA an attractive device for high frequency and programmable basic building block [5,6]. Therefore, the implementation of analog circuits in such a way that employs only OTA as a standard cells will not only be easily constructed from readily available cells, but also significantly simplified the design and layout. A circuit technique to employ OTAs to implement analog multiplier has been presented [7]. However, the circuit is voltagemode circuit and only multiplication function is implemented. In this paper, a current-mode temperature compensated multiplier-divider circuit using only OTAs as active circuit elements has been presented, where no passive elements are required by this realization scheme

PSPICE simulation results will be used to demonstrate the performance of the proposed scheme.

### 2. Basic principle

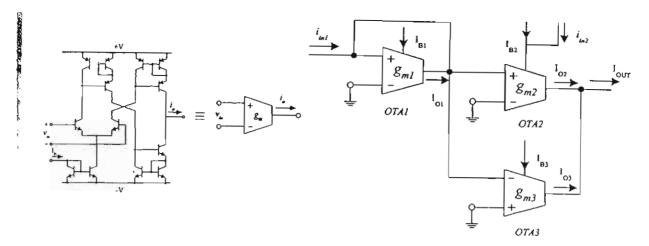

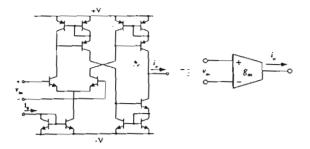

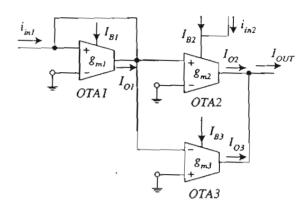

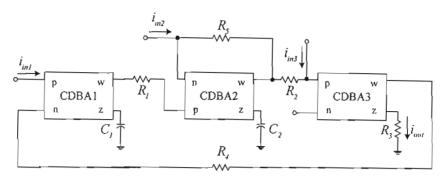

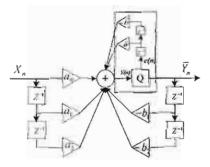

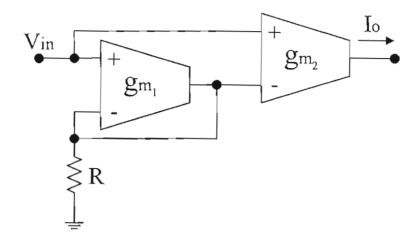

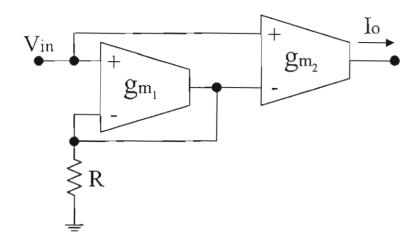

The schematic diagram of the proposed current multiplier-divider circuit using OTAs is shows in Fig. 1. The input signal current  $i_{int}$  is injected into the operational transconductance amplifier OTA1, which is connected as a grounded resistor. The voltage across the OTA1 is then used as the input voltage for the OTA2 and OTA3. The input signal current  $i_{in2}$  is added with the bias current  $I_{B2}$  of the OTA2. If  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  are the transconductance gains of the OTA1, OTA2 and OTA3, respectively; then, from routine circuit analysis, the output currents  $I_{O2}$  and  $I_{O3}$  of the OTA2 and OTA3, respectively, can be written as

$$I_{o2} = \frac{g_{m2}}{g_{m1}} i_{in1} = \frac{(I_{B2} + i_{in2})}{I_{B1}} i_{in1}$$

(1)

and

$$I_{o3} = -\frac{g_{m3}}{g_{m1}}i_{m1} = -\frac{(I_{g3})}{I_{g1}}i_{in1}$$

(2)

where  $g_{ml} = I_{Bl}/2V_T$ ,  $g_{m2} = (I_{B2} + i_{m2})/2V_T$  and  $g_{m3} = I_{B3}/2V_T$  and  $V_T$  is the thermal voltage.

If we set  $I_{B2} = I_{B3} = I_B$ , the output current  $I_{OUT}$  of the circuit, that is the summation of the currents  $I_{O2}$  and  $I_{O3}$ , can now be given by

$$I_{out} = I_{o2} + I_{o3} = \frac{i_{in1} i_{in2}}{I_{o3}}$$

(3)

which is in the form of a current-mode analog multiplication division function. The circuit performs as a four-quadrant multiplier if  $i_{in1}$  and  $i_{in2}$  are the input signals, while it performs as a divider circuit if  $i_{in1}$  (or  $i_{in2}$ ) and  $l_{B1}$  are the input signals. It should be noted that, since it is the ratio of OTAs transconductance gain, the output current  $l_{out}$  is less sensitive to temperature.

The major factors that contribute to the error and non-linearity in the circuit can be classified as follows. The first factor is due to the offset current at the output port of the OTA1. From (3), if  $I_{os}$  is the offset current, the output current  $I_{out}$  can be rewritten as

Fig. 1 The schematic diagram of the OTA.

$$I_{out} = \frac{(i_{in1} + I_{os})i_{in2}}{I_{in1}}$$

(4)

We can see that, particularly for the peak value  $|i_{iml}| \le I_{im}$ , the multiplication for the positive peak and the negative peak of  $i_{iml}$  will not be equal. Thus the signal peak value should be selected such that  $|i_{iml}| \ge I_{os}$ . While the offset currents at the output ports of the OTA2 and OTA3 are not contribute to the multiplication error, but will produce a DC current at the output of the circuit. The second factor affecting the non-linearity of the circuit is due to the limited linear range of the input stage of the OTA2 and OTA3. For a bipolar-based OTA, where the input stage is a conventional differential pair, the input differential voltages for linear operation are restricted to be less than 26 mV. Since  $1/g_{m1} = 2V_1/I_{B1}$ , this restricted linear range can be improve by increasing  $I_{m1}$ .

### 3. Simulation results

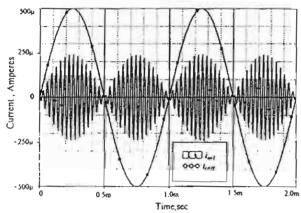

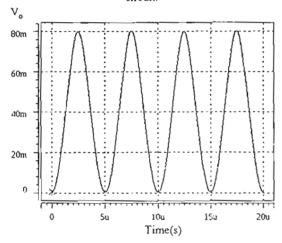

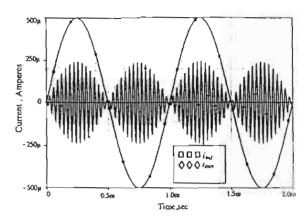

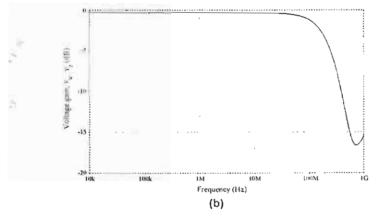

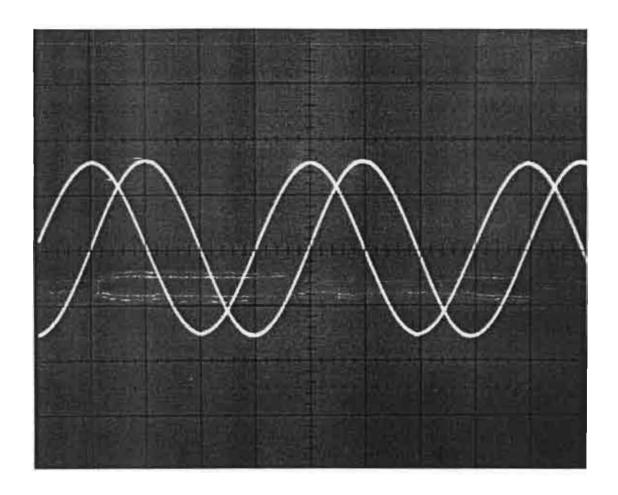

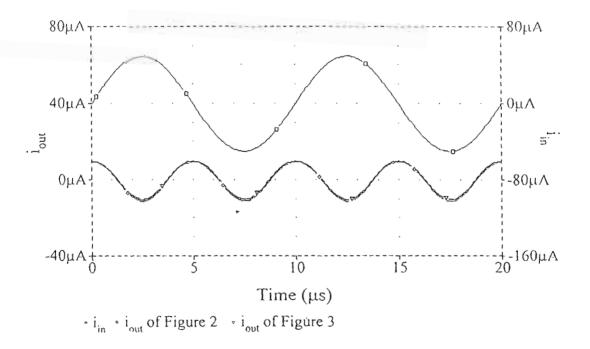

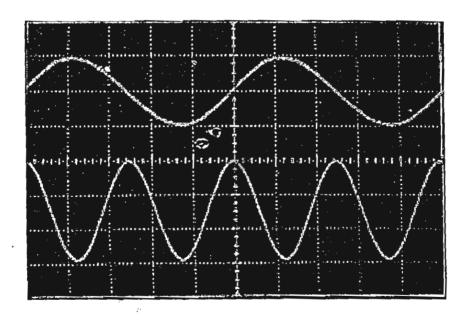

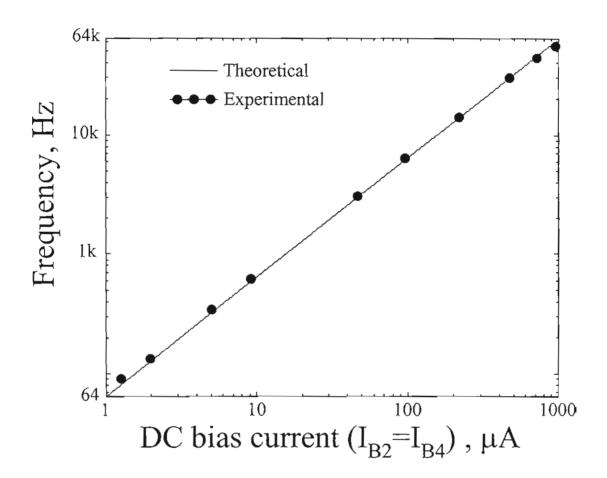

As shown in Fig.1, in this work an OTA that realized in bipolar transistor technology will be employed as active circuit elements. Its transconductance gain  $(gm = I_T/2I_B)$  can be tune by the DC bias current  $(I_B)$ . The performance of the proposed multiplier-divider circuit of Fig.1 was verified through the use of SPICE simulation results. All the OTA was simulated by using the bipolar transistor parameters of the 2N3904 and 2N3906 for the NPN and PNP transistors, respectively. The transistors fr were 186 MHz. The circuit of Fig. 2 was simulated using the PSPICE circuit simulation program. The multiplier function was tested by multiplying two sinusoidal signals. The result obtained are shown in Fig. 3 for  $i_{int} = 0.5\sin(2\pi)$ 1000t) mA,  $I_{m2} = 0.5\sin(2\pi 3000t)$  mA and  $I_{BI} = 1$ mA. Since the DC offset current will distort the output signal, a DC current of about 64A was injected at the output of the OTA1 to adjust the offset to be less than ±0.14A.

Similarly, a DC current of about 4 $\mu$ A' was used to keep the offset current at the output of the circuit to be less than  $\pm$  0.1 $\mu$ A. The power supply voltages were set to VCC = 10V and VEE = -10V

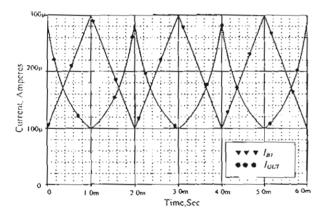

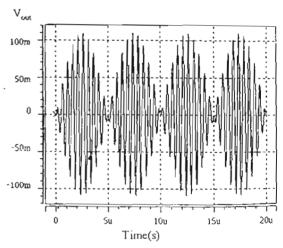

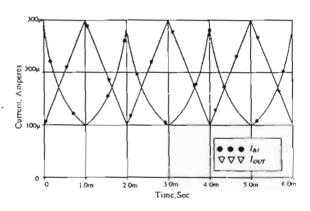

The divider function was tested by inverting a triangular signal. The results obtained are show in Fig. 4. Fig. 4 show the simulated transient response of the circuit that function as a divider. The output current  $I_{OLT}$ , which in this case is an inverting function of a triangular signal, was simulated for  $i_{ml} = 100 \text{ HA}$ ,  $i_{m2} = 300 \text{ HA}$ , and  $I_{BI}$  is a 500 Hz triangular wave with amplitude of 100 HA and DC component of equal to 200 HA.

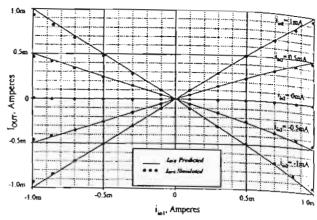

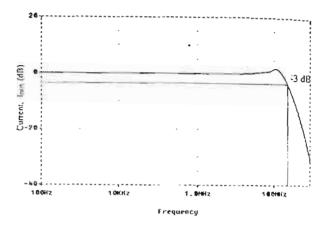

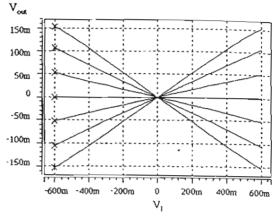

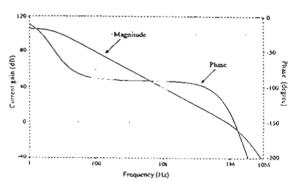

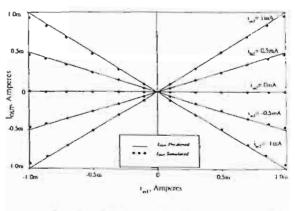

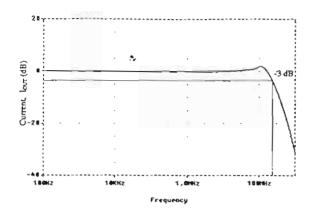

simulated DC transfer Fig.5 shows the characteristics for the multiplier function, where the bias currents were set to  $I_{HI} = I_{H2} = I_{H3} = 1 \text{ mA}$ . The figure shows the plot of the output current lour against the input signal current imt from -1mA to 1mA and the input signal current im2 from -1mA to 1mA with 0.5mA per step. The simulation and calculated data are agree very well over the ±0.8mA input range with an error of less than 0.1%. We can see large non-linearity for im close 1mA this is due to that the voltage across the OTA1 is closed to the limited linear range. Fig. 5 show the simulated transient response of the circuit that function as a divider. The output current IOUT, which in this case is an inverting function of a triangular signal, was simulated for  $i_{ml} = 100 \mu A$ ,  $i_{m2} =$ 300HA, and IBI is a 500Hz triangular wave with amplitude of 100HA and DC component of equal to 200HA Fig.6 shows the simulated frequency response of the circuit from the input  $i_{ml}$  to the output, with  $i_{m2} = 100 \mu A$  and  $I_{Bl} = 1 m A$ . The response indicates that the circuit -3dB bandwidth is about 162 MHz that is close to the transistor  $f_T$ . The total harmonic distortion (THD) against input current, for the case that the input signal  $i_{m2}$  is a dc current,  $i_{m2} = 100 \mu A$ and the input signal current  $i_{ml} = 0.1\sin(2^{\pi}10000t)$  mA, is about 0.24%. On the other hand, when the input current turn is dc current,  $i_{ml} = 100 \mu A$ , and the signal current  $i_{m2} =$  $0.1\sin(2^{\pi}10000t)$  mA, the THD is about 0.39%

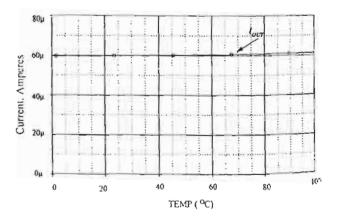

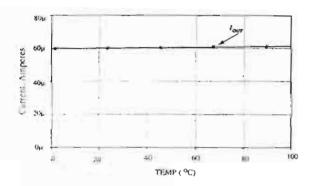

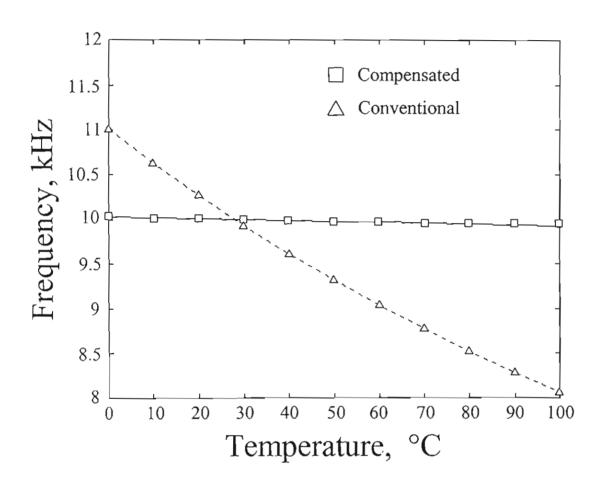

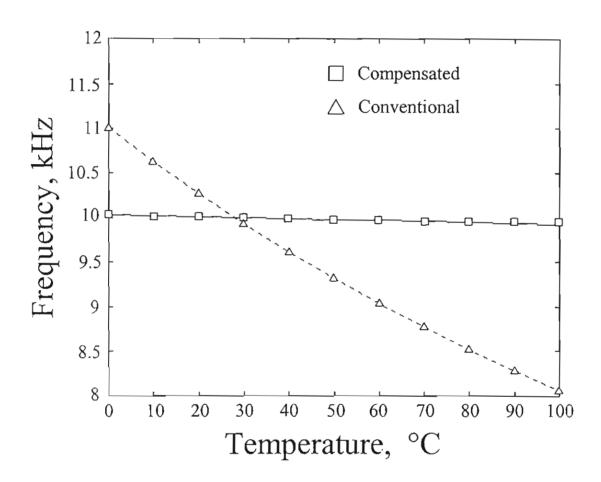

Fig. 7. Shows the simulation result of the output current ( $Iou\tau$ ) due to the change of temperature for operating temperature variations from 0 °C to 100 °C. We set the input signal currents  $i_{ml}$  and  $i_{m2}$  as dc currents, where  $i_{int} = 1000 \,^{\text{H}}\text{A}$  and  $i_{m2} = 60 \,^{\text{H}}\text{A}$ , where  $Iou\tau = 60 \,^{\text{H}}\text{A}$ . From the figure, the output current varies only from 59.62  $^{\text{H}}\text{A}$  to 61.38  $^{\text{H}}\text{A}$ , for the temperature 0 °C to 100 °C respectively. This simulation result shows that the temperature dependence of transconductance pains  $g_{ml}$ ,  $g_{m2}$  and  $g_{m3}$  of the bipolar OTAs are compensated.

Fig. 3 Simulated transient response for the multiplier function.

Fig. 4 Simulated transient response for the divider function.

Fig. 5 Simulated DC transfer characteristic of the multiplier-divider.

Fig. 6 Frequency response of current-mode multiplier-divider circuit using OTAs.

Fig. 7 Frequency response of current-mode multiplier-divider circuit using OTAs.

# Phoceedings Julijia Phuket Arcadia Hotel & Resort Phuket, Thailand

### onsored by

norn International Institute of chnology, Thammasat University, Thailand longkut's University of Technology nonburi, Thailand al Electronic and Computer Technology enter, Thailand y of University Affairs, Thailand

### With Technical Cooperation of

IEICE IEEK IEEE Thailand Section

### Co-Organized by

King Mongkut's University of Technology Thonburi, Thailand Sirindhorn International Institute of Technology, Thammasat University, Thailand

### Voltage-Mode CMOS Squarer/Multiplier Circuit

B. Boonchu1 and W. Surakampontorn2 Mahanakom University of Technology,

51 Cheum-Sumpan Road, Nong-Chock District Bangkok, Thailand 10530 Phone (662)9883655 ext.239 Fax (662)9883687 Email: boonchai@mut.ac.th

<sup>2</sup>King Mongkut's Institute of Technology Ladkrabang

Ladkrabang, Bangkok 10520, Thailand.Phone: (662) 326-9968, Fax: (662) 739-2398 Email: kswanlop@kmitl.ac.th

Abstract: In this paper, a low-voltage CMOS squarer and a four-quadrant analog multiplier are presented. It is based on a source-coupled pair and a scaled-floating voltage generator which are modified to work as a voltage squaring and a sum/difference circuits. The proposed squarer/multiplier have been simulated with HSPICE, where -3dB bandwidth of 10MHz is achieved. The power consumption is about 0.6mW, from a ±1.5V supply, and the total harmonic distortion is less than 0.7%, with a 1.21 peak-to-peak IMHz input signal.

### Introduction

A squarer circuit is an importance basic building block for the design of analog nonlinear function circuits, for examples, frequency translation, waveform generation, neural networks, and it can be applied to work as a quartersquare multiplier circuit. Usually, the common-source differential squaring circuit configuration as a two-input NOR gate with resistance load is widely used for the design of squarer/multiplier circuits in CMOS technologies [1]-[2]. The other approaches are that based on square-law current to voltage characteristics of MOS transistor which are biased in the saturatoin and nonsaturation region [3]-[9]. The squarer and multiplier proposed in this paper also use the square-law of the MOS transistor. But, however, the proposed circuit does not require resistors to obtain the output signal in voltage [10]

### 2. Circuit Description

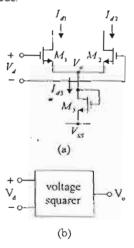

### 2.1 MOS Differential Squaring Circuit

Fig. 1 shows the voltage-mode squaring circuit and its symbol which is made up of a differential-input sourcecoupled pair. Assuming that all NMOS devices are biased in the saturation region with individual wells connected to their sources to eliminate the body effect [3]. Let  $M_1$  and  $M_2$  are identical, and the aspect ratio of  $M_3$  be twice that of  $M_1$ . If the differential-input voltage  $V_d$ , with the same common-mode de voltage  $V_C$  is applied, the drain currents of MOS transistors can be expressed as

$$I_{d1} = K_1 \left( V_C + \frac{V_d}{2} - V_o - V_T \right)^2 \tag{1}$$

$$I_{d2} = K_2 \left( V_C - \frac{V_d}{2} - V_o - V_T \right)^2 \tag{2}$$

$$I_{d3} = K_3 (V_o - V_{SS} - V_T)^2$$

(3)

$$I_{d1} + I_{d2} = I_{d3} \tag{4}$$

where  $K_i = \mu_n C_{\infty} W_i / 2L_i$  is transconductance parameter,  $\mu_n$  is the effective surface mobility,  $C_{\infty}$  is the gate capacitance per unit area, and  $V_T$  is the threshold voltage of the transistor, respectively. The output voltage V

$$V_{o} = \frac{(\bar{V}_{C} - \bar{V}_{T})^{2} - (\bar{V}_{SS} + \bar{V}_{T})^{2}}{2(\bar{V}_{C} - \bar{V}_{SS} - 2\bar{V}_{T})} + \frac{\bar{V}_{d}^{2}}{8(\bar{V}_{C} - \bar{V}_{SS} - 2\bar{V}_{T})}$$

The output voltage  $V_o$  is related to the square of the differential-input voltage  $V_d$ . The eqns. (1)-(5) are valid if  $(V_C - V_{SS} - V_d/2) > 2V_T$ , where all devices are biased in the saturation mode

Fig. 1. Voltage-mode squaring circuit (a) circuit and (b) symbol.

### 2.2 Scaled Differential-Voltage Generator

A circuit for generating differential-voltage generator is shown in Fig. 2 [8]. Matched transistor  $M_1$  and  $M_2$  form an input differential pair, while the other four identical NMOS devices,  $M_3$ ,  $M_4$  and  $M_5$ ,  $M_6$  form floating differential outputs that are biased by current sources Iss

of the same magnitude. If voltage  $V_{tn}$  is applied to the input, the output voltages  $V_{01}$  and  $V_{02}$  can be given by

$$V_{o1} = -V_{o2} = \sqrt{\frac{K_3}{K_1}} V_{in} \tag{6}$$

The output voltages is a scaled voltage which is equal to input voltage multiplied by a factor that is depend on transconductance parameter of the transistors  $M_3$  and  $M_1$

Fig. 2. Scaled differential-voltage generator (a) circuit and (b) its symbol.

### 2.3 Voltage-Mode Squaring Circuit

By combining the voltage squarer circuit and the scaled differential-voltage that shown in Fig. 1 and Fig.2, respectively, the block diagram of the voltage-mode squaring circuit is shown in Fig. 3, where the reference voltage  $V_{ref}$  is the constant de voltage,  $V_{in}$  and  $V_o$  are the input and output voltage respectively. From eqns.(5)-(6) we find that

$$V_o = \frac{(V_{ref} - V_T)^2 - (V_{SS} + V_T)^2}{2(V_{ref} - V_{SS} - 2V_T)} + \frac{V_{ot}^2}{2(V_{ref} - V_{SS} - 2V_T)}$$

$$\downarrow^+ c$$

scaled differential voltage generator +  $V_o$

$$\downarrow^- V_{td}$$

$$\downarrow^- V_{td}$$

Fig. 3. Block diagram of the proposed squaring circuit.

The eqn. (7) shows that the output voltage  $V_o$  is equal to the square of the input voltage  $V_m$  and a factor which is in the

form of the voltage reference  $V_{\rm ref}$  . Then, we can adjust the output-offset voltage and the magnitude of  ${V_{\rm in}}^2$  by tuning  $V_{\rm ref}$  .

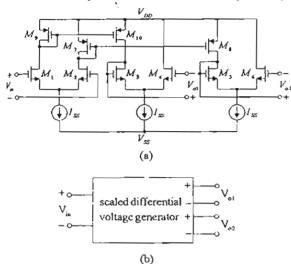

Fig. 4. Block diagram of the proposed multiplier

### 2.4 Voltage-Mode Four-Quadrant Multiplier

Fig. 4 shows a block diagram of the four-quadrant analog multiplier that consists of three basic scaled differential-voltage generator and two voltage squarer, where  $V_1, V_2$  and  $V_{out}$  are the input and output voltage of the multiplier, respectively. From the quarter-square algebraic identity  $(V_1 + V_2)^2 - (V_1 - V_2)^2 = 4V_1V_2$ , therefore, the output voltage of the voltage-mode multiplier can be written as

$$V_{out} = \frac{(V_1 + V_2)^2 - (V_1 - V_2)^2}{8(V_C - V_{SS} - 2V_T)}$$

$$= \frac{V_1 V_2}{2(V_C - V_{SS} - 2V_T)}$$

(8)

The output voltage is equal to the multiplication of the two input voltage and a factor which is in the form of the common-mode de voltage  $V_C$  and the power supply voltage  $V_{SS}$ . Consider the multiplier circuit block diagram in Fig. 4, if we set both the input voltages to zero, then  $V_C$  will be zero.

The channel length modulation, which causes the effective channel length, and thus the device W/L ratio, to be a function of the device drain-to-source voltage. However, this effect can be neglected if the long channel transistors are used.

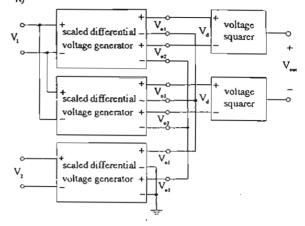

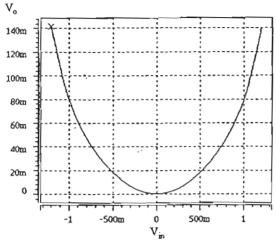

### 3. Simulation Results

The proposed squarer/multiplier circuit have been simulated by HSPICE using the model parameters of HP  $0.5\mu$  level 49 CMOS process. For the voltage-mode squaring circuit that is shown in Fig. 1, the aspect ratios of transistors  $M_1-M_2$  are 5/5, and  $M_3$  is 10/5. The ratios

of the devices of the scaled differential-voltage generator that is shown in Fig. 2,  $M_1-M_6$  and  $M_7-M_{10}$  are 5/10 and 20/5, respectively. The power supply voltage is  $\pm 1.5V$  and the bias current  $I_{SS}$  is  $20\mu A$ .

Fig. 5. The transfer characteristic curves of the squaring

Fig. 6. The output waveform of the proposed squaring circuit

Fig. 5 and Fig. 6 show the simulations for the voltage-mode squaring circuit. The transfer characteristic curve is shown, where  $V_{in}$  is varied from -1.2V to 1.2V. The output signal shown in Fig. 6 is measured by applying the sinusoidal input voltage  $V_{in}$  with peak amplitude of 1V and the frequency is 100kHz.

The dc characteristic curves of the proposed multiplier are shown in Fig. 7, for the input voltage  $V_1$  varied from -0.6V to 0.6V and  $V_2$  changing from -0.6V to 0.6V with 200mV steps.

Fig.8 demonstrates the use of this multiplier as an amplitude modulator, a 100kHz sine wave is modulated by 2MHz, where the amplitude of the signals are 500mV

The total harmonic distortion is measured by setting  $V_2$  to 600mV dc voltage:  $V_1$  is the sinusoidal signal with peak amplitude of 600mV and the frequency is 1MHz. The simulated maximum THD is about 0.7%, and the power consumption is about  $550\mu W$ .

To measure the frequency characteristic of the multiplier, a 600mV dc voltage is applied to  $V_2$  while  $V_1$  is the variable frequency sinusoidal input current with peak amplitude of 600mV. From the simulation, the -3dB bandwidth up to 10MHz is achieved.

Fig. 7. The transfer characteristic curves of the multiplier

Fig. 8. Amplitude modulation of the two sinusoidal input

### 4. Conclusion

A new CMOS voltage-mode squarer and four-quadrant analog multiplier base on the differential-input source-coupled pair and scaled differential-voltage generator have been presented. To obtain the output voltage, the proposed circuits are performed by using the voltage-mode squaring circuits which does not require a resistor There performances have been demonstrated by using HSPICE simulations.

ITC-CSCC 2002

# ITC-CSCC 2002

The 2002 International Technical Conference On Circuits/Systems, Computers and Communication

Phuket Arcadia Hote Phuket, Thailand

Sitindhorn International Institute of

Technology, Thammasat University, Thailand

King Mongkut's University of Technology

Thonburi, Thailand

National Electronic and Computer Technology

Center, Thailand

Ministry of University Affairs, Thailand

With Technical Cooperation of

IEICE

**IEEK**

IEEE Thailand Section

### Co-Organized by

King Mongkut's University of

--Technology Thonburi, Thailan

Sirindhorn International Institute of Technology, Thammasat

University, Thailand

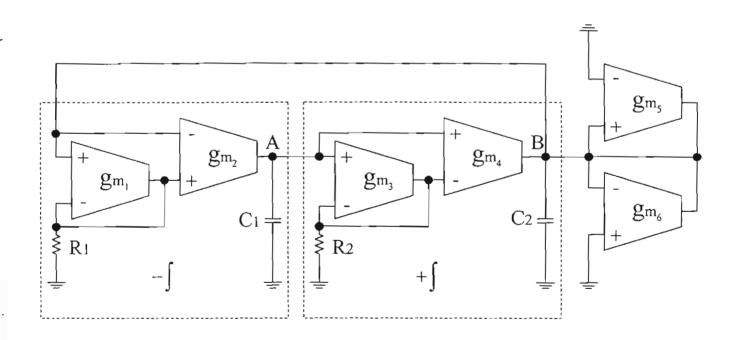

# Current-Mode Integrator using OA and OTAs and Its Applications

Katesuda Klahan<sup>1</sup>, Worapong Tangsrirat<sup>1</sup>, Teerasilapa Dumawipata<sup>2</sup> and Wanlop Surakampontorn<sup>1</sup>

Faculty of Engineering and Research Center for Communication and Information Technology (ReCCIT), King Mongkut's Institute of Technology Ladkrabang (KMITL), Ladkrabang, Bangkok 10520, THAILAND Tel. +66-2-326-9968, Fax.: +66-2-739-2398

Department of Industrial Electrical Technology (IET), Faculty of Engineering, King Mongkut's Institute of Technology North-Bangkok (KMITNB), Bangsue. Bangkok 10800, THAILAND

E-mail: s3061312@kmitl.ac.th, ktworapo@kmitl.ac.th, trs@kmitnb.ac.th, kswanlop@kmitl.ac.th

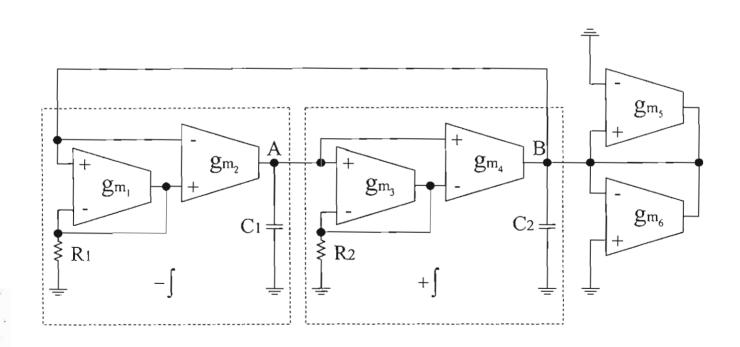

Abstract: A circuit building block for realizing a continuous-time active-only current-mode integrator is presented. The proposed integrator is composed only of internally compensated type operational amplifier (OA) and operational transconductance amplifiers (OTAs). The integrator is suitable for integrated circuit implementation in either bipolar or CMOS technologies, since it does not require any external passive elements. Moreover, the integrator gain can be tuned through the transconductance gains of the OTAs. Some application examples in the realization of current-mode network functions using the proposed current-mode integrator as an active element are also given.

### 1. Introduction

In the last decade, the realizations of various active circuits utilizing the operational amplifier (OA) pole have received considerable attention for their potential advantages such as attractive for monolithic IC integration, ease to design, and suitable for high frequency operation [1-2]. Several OA-based active-R capacitor-less circuits for realizing analog transfer functions have been reported [3-4]. Presently from the above reasons, there is the strong motivation to design resistor-less and capacitor-less filter circuits utilizing the finite and complex gain natures of internally compensated OAs and OTAs. Due to the active only nature, the resistor-less and capacitor-less active filter would be attractive for its integratability, programmability and wide frequency range of operation. implementations in active-only filter design are available in the literature [5-7].

It is well-known fact that an integrator is an important circuit building block, which are widely used in analog signal processing applications, such as, filter design, waveform shaping, process controller design, and calibration circuit, etc. However, the implementation of a continuous-time current-mode integrator that employs only active elements has not yet been reported. Therefore, a circuit configuration for realizing active-only current-mode integrator is proposed in this paper. The proposed integrator consists of one OA and two OTAs. Since no passive element is required, the integrator can be implemented in integrated circuit form in both bipolar and CMOS technologies. The integrator gain can be electronically tuned by adjusting the transconductance

gains of the OTAs. The various realizations of active-only analog signal processing circuits employing the proposed integrator will also be presented. Finally, the workabilities of the proposed integrator and its applications have been simulated based upon a LM741 type IC OA and a CA3080 type IC OTA.

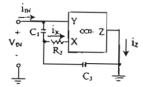

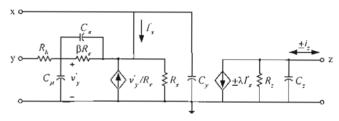

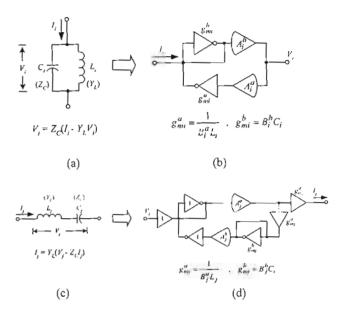

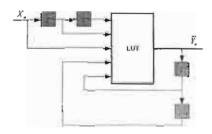

Fig.1: The proposed active-only current-mode integrator

(a) circuit implementation (b) circuit representation

### 2. Circuit Description

The proposed active-only dual-output current-mode integrator implementation and its representation are shown in Fig.1. It consists of only an OA and OTAs, where the dual-current-output OTA2 is implemented by using single-ended output OTAs in parallel connection [8]. If  $\omega_a$  is the 3-dB bandwidth of the OA and by considering the OA for the frequencies  $\omega >> \omega_a$ , the open-loop gain  $\Lambda_{OA}(s)$  of the OA can be approximately given by

$$A_{OA}(s) = \frac{A_a \omega_{a}}{s + \omega} : \frac{B}{s}$$

(1)

where B represents the gain-bandwidth product (GBP) of the OA, which is the product of the de gain  $A_o$  and the 3-dB bandwidth  $\omega_o$ . Let assume that  $g_{m1}$  and  $g_{m2}$  denote the transconductance gains of the OTA1 and OTA2, respectively, then the current transfer function of the current-mode integrator can be expressed as:

$$\frac{I_o(s)}{I_{in}(s)} = \frac{B}{s} \left[ \frac{g_{m2}}{g_{mi}} \right] = \frac{B}{s} A_G \tag{2}$$

where  $A_G$  denotes the integrator gain, which is the ratio between  $g_{m2}$  and  $g_{m1}$ . Eqn.(2) indicates that the relationship of the currents  $I_g$  and  $I_m$  is in the form of the integrating

action as required. It should be noted that, for ordinary bipolar OTAs,  $g_{m1} = I_{B1}/2V_T$  and  $g_{m2} = I_{B2}/2V_T$ , where  $V_T$  is the thermal voltage and  $I_{B1}$  and  $I_{B2}$  are the bias currents of the OTA1 and OTA2, respectively. Thus, eqn.(2) becomes

$$\frac{I_o(s)}{I_{in}(s)} = \frac{B}{s} \left[ \frac{I_{B2}}{I_{B1}} \right] = \frac{B}{s} A_G \tag{3}$$

Now  $A_G$  is the current gain that is the bias current ratio between  $I_{B2}$  and  $I_{B1}$ . In this case, the temperature dependence of the transconductance gains  $g_{m1}$  and  $g_{m2}$  of the bipolar OTAs are also compensated.

Deviation from the ideal performance that predicted from the eqn. (2) is due to the parasitic effects of the non-ideality characteristics of the OA and OTAs. If the second dominant pole  $\omega_b$  of the OA is taken for consideration, the OA open-loop gain  $A_{OA}(s)$  can be rewritten by

$$A_{OA}(s) = \frac{B}{s} \frac{\omega_b}{(s + \omega_b)} = \frac{B}{s} \frac{1}{(1 + \tau_b s)}$$

(4)

where  $\tau_b = 1/\omega_b$ . For the OTAs, let  $\omega_c = 1/\tau_c$  represents the effective transconductance internal-pole of the OTA and  $g_{m0}$  is the low frequency transconductance gain. The OTA open-loop gain  $g_m(s)$  for general case can be described by

$$g_{-}(s) = \frac{g_{m0}}{\left(1 + \frac{s}{\omega_c}\right)} \cong g_{m0} \left(1 - \frac{s}{\omega_c}\right)$$

(5)

Therefore, the frequency response of the current-mode integrator in Fig.1 that including the second dominant pole of the OA and the transconductance internal-poles of the OTAs can now be given by

$$\frac{I_o(s)}{I_{in}(s)} = \left[\frac{B}{s}\right] \left[\frac{1}{1+\tau_b s}\right] \left[\frac{g_{m02}}{g_{m01}}\right] \left[\frac{\omega_{c2} - s}{\omega_{c2}}\right] \left[\frac{\omega_{c1}}{\omega_{c1} - s}\right]$$

(6)

where  $\omega_{c1}$  and  $\omega_{c2}$  are the effective transconductance internal-poles of the OTA1 and OTA2, respectively. It can be seen that if the conditions  $(\omega_{c1} \cong \omega_{c2})$  and  $(\omega_{c1}, \omega_{c2} >> \omega)$  are satisfied, then eqn. (6) becomes frequency independent. Let us define that  $A_{CO} = g_{m02}/g_{m01}$  is the dc integrator gain, as a result, it can be reasonably reduced to

$$\frac{I_o(s)}{I_{io}(s)} = \left[\frac{A_{co}B}{s}\right] \left[\frac{1}{1+\tau_b s}\right] \tag{7}$$

One can see that the frequency characteristic of the proposed current-mode integrator has a dc current gain equaled to eqn. (2) and has a high frequency dominant pole located at  $\omega_b$ . Hence, the OA pole  $\omega_b$  should be the major high-frequency limitation of the proposed current-mode integrator

### 3.Application examples

The following sections will concentrate on the usefulness of the proposed current-mode integrator. Some application examples to realize driving-point impedance function elements, current-mode biquadratic filter and current-mode nth-order filter will be demonstrated.

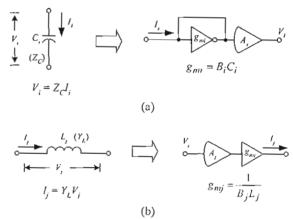

### 3.1. Inductance simulations

Fig. 2(a) shows the circuit diagram of a tunable floating inductance simulation. From this circuit, it can easily be shown that the value of the floating simulated inductance is

$$L_{eq} = \left[\frac{1}{g_{ms}A_{G}B}\right] \tag{8}$$

It should be noted that the equivalent inductance  $L_{eq}$  can properly be tuned by electronic means through the current ratio  $A_G$  and/or the transconductance gain  $g_{eq}$ . In addition, the circuit in Fig.2(a) can easily be modified to simulate a grounded inductor by replacing the dual-output OTA2 with the single-output OTA2 as shown in Fig.2(b).

Fig.2: Active-only inductance simulations

# 3.2. Electronically tunable active-only current-mode biquadratic filter ·

Fig.3 shows the circuit diagram of the tunable current-mode filter based on the use of the proposed current-mode integrator, where  $i_{LP}$ ,  $i_{BP}$ , and  $i_{HP}$  are the lowpass, bandpass and higpass current-output terminals, respectively. The circuit parameters  $\omega_0$  and Q-factor of this filter can be written by

$$\omega_o = \sqrt{A_{G1}A_{G2}E_1E_2} \tag{9}$$

and

$$Q = \frac{g_{\text{mc}}}{g_{\text{end}}} \sqrt{\frac{A_{C2}B_{2}}{A_{G1}B_{1}}}$$

(10)

One can see that the filter also enjoys orthogonal uning of  $\omega_o$  and Q-factor via the transconductance gains of the OTAs and it's also temperature independent.

Fig.3: Active-only current-mode biquadratic filter

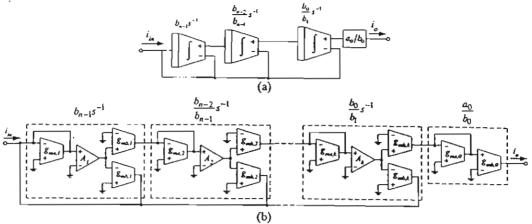

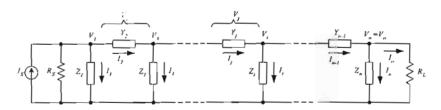

Fig.4: (a) nth-order current-mode filter representation (b) nth-order current-mode filter realization using only active elements

### 3.3 nth-order current-mode filters

The standard current transfer function of an nth-order lowpass filter is often expressed as the following form:

$$\frac{I_o(s)}{I_{in}(s)} = \frac{a_0}{s^n + b_{o,i}s^{n,i} + \dots + b_i s + b_0}$$

(11)

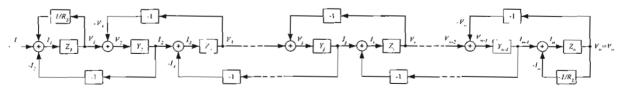

One can straightforwardly realize the nth-order current transfer function of equation (11) by cascading the proposed current-mode integrator of Fig.1. The system diagram thus obtained can be shown in Fig.4(a) and the coefficient of the standard function in terms of the circuit parameters can be expressed as follows:

$$b_{n-1} = A_{G_1}B_1$$

;  $A_{G_1} = \frac{g_{mb}}{g_{ma,1}}$  (12)

$$\frac{b_{n+1}}{b_{n+1,k}} = A_{Gk}B_k \quad ; \quad A_{Gi} = \frac{g_{mn,k}}{g_{mn,k}} \tag{13}$$

$$\frac{a_0}{b_n} = \frac{g_{mb,0}}{g_{max,0}} \tag{14}$$

where  $A_{Gk}$  and  $B_k$  represent the current gain and GBP of the k-th integrator (for  $k=2,3,\ldots,n$ ). For this implementation, n active-only current integrators and two additional transconductance elements that employed for realizing the output proportional gain block  $(g_{mb,0}/g_{ma,0})$  are required. Fig.4(b) shows the nth-order current-mode filter realization based on the use of only active components. In addition, if coefficients  $a_0$  and  $b_0$  are equaled, then two additional transconductance elements will also be eliminated.

### 4. Design examples and Simulation results

In order to verify the theoretical study of the proposed current-mode integrator, PSPICE simulation results are included. In this simulation, the OTA is modeled by employing CA3080 type OTA with a macro model [8] and LM741 type OA with the gain-bandwidth product B=5.906 Mrad/s is used [5]. Fig.5 shows the simulated frequency responses of the proposed current-mode integrator. The results show that the circuit acts as an integrating function with a slope -20 dB per decade for the frequency range from 10 Hz to 1 MHz and has less than 10% phase error from the frequency range of 30 Hz to 500 kHz.

Fig.5: Frequency responses of the proposed integrator

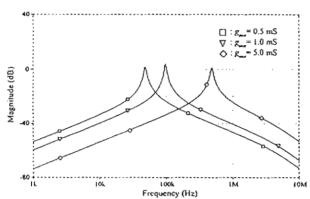

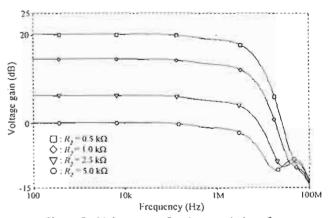

The performance of the floating inductance circuit of Fig.2(a) is demonstrated through the use of an electronically tunable active RL low-pass filter in Fig.6(a) with the external resistor  $R_1 = 1 \text{ k}\Omega$ . The bias current ratio  $A_G = I_B \chi I_{B1} \ (= g_m \chi g_{m1})$  is set to 0.5, 1 and 2, while  $g_{m1}$  and  $g_{m3}$  are respectively set to constant at 1 mS and 0.4 mS; thus the cut-off frequencies  $f_C$  are approximately equal to 200 kHz, 400 kHz and 800 kHz, respectively. The frequency responses of the low-pass filter are shown in Fig.6(b).

Fig. 7 shows simulated responses of the tunable current-mode multifunctional filter of Fig. 3, when  $A_{G1} = A_{G2} = 0.05$  and  $g_{mc}/g_{md} = 0.1$ . This filter is designed for  $\omega_d/2\pi = 50$  kHz at the unity Q-factor. All the simulated results shown above imply that the proposed integrator exhibit reasonably good agreement with the predicted values.

Fig.6: (a) first-order RL lowpass filter (b) frequency responses of the simulated RL lowpass filter

Fig.7: Simulated frequency response of current-mode filter of Fig.3

Fig.8: Simulated frequency response of nth-order current-mode filter of Fig.4

To illustrate the current-mode filter using all active elements of Fig.4(b), a design of a third-order Butterworth filter with a cut-off frequency of 100 kHz is an example. The normalized transfer function for this filter can be written by

$$\frac{I_o(s)}{I_{in}(s)} = \frac{1}{s^3 + 2s^2 + 2s + 1} \tag{15}$$

The active-only filter realization based on the circuit of Fig.4 is constructed, in which the transconductance elements  $g_{mn,0}$  and  $g_{mh,0}$  will be eliminated due to the

coefficient values  $a_0$  and  $b_0$  equal to unity. Thus, by calculating the circuit parameters we obtain:  $g_{mh,1} = 0.424$  mS,  $g_{mb,2} = 0.212$  mS and  $g_{mh,3} = 0.106$  mS, while  $g_{ma,l}$  (i = 1, 2, 3) are set equal to 2 mS. In addition, the values of  $g_{ma,l}$  can be used to change the cut-off frequency. The simulated frequency responses are shown in Fig.8 that exhibit reasonably close agreement with theoretical results. It is also shown that the cut-off frequency can be tuned electronically through adjusting the transconductance gains  $(g_{ma,1} = g_{ma,2} = g_{ma,3})$ .

### 5. Conclusions

This paper presented an alternative scheme for realizing continuous-time active-only current-mode integrator. The proposed integrator is realizable with only internally compensated type OA and OTAs, and does not require any external passive elements. Because of their active-only nature, the integrator can be easily employed to realize active network functions and are suitable for implementing in monolithic integrated form in both bipolar or CMOS technologies. Since the proposed circuit utilizes an OA pole, it is also suitable for high frequency operation. The simulated results have been used to verify the theoretical analysis.

### 6. Acknowledgment

This work is partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program, grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency (IICA) is also acknowledged.

### References

- [1] J.R. Brand and R. Schaumann, "Active-R filters: review of theory and practice", *Electronic Circuits and Systems*, vol.2, pp.89-101, 1978.

- [2] U. Kumar and S.K. Shukla, "On the importance, realization, experimental verification and measurement of active-R and active-C filters", *Microelectronics J.*, vol.21, pp.21-45, 1990.

- [3] M. Higashimura, "Current-mode lowpass and bandpass filters using the operational amplifier pole", Int. J. Electron., vol.74, pp.945-949, 1993.

- [4] M.A. Soderstrand, V.H.C. Watt, K.B. Kee and D. Mcginity, "Implementation of an active-R filter building block in semi-custom VLSI", Int. J. Electron., vol.76, pp.469-482, 1994.

- [5] A.K. Singh and R. Senani, "Low-component-count active-only imittances and their application in realizing simple multifunction biquads", *Electron. Lett.*, vol.34, pp.718-719, 1998.

- [6] M.T. Abuelma'atti and H.A. Alzaher, "Universal three inputs and one output current-mode filter without external passive elements", *Electron. Lett.*, vol.33, pp.281-283, 1997.

- [7] T. Tsukutani, M. Higashimura, Y. Sumi and Y. Fukui, " Electronically tunable current-mode active-only biquadratic filter", Int. J. Electron., vol.87, pp.307-314, 2000.

- [8] J. Wu, "Current-mode high-order OTA-C filters", Int. J. Electron., vol.76, pp.1115-1120, 1994.

# ITC-CSCC 2002

The 2002 International Technical Conference On Circuits/Systems, Computers and Communications

Phuket Arcadia Hotel & Resi Phuket, Thailand

Sirindhorn International Institute of

Technology, Thammasat University, Thailand

King Mongkut's University of Technology

Thonburi, Thailand

National Electronic and Computer Technology

Center, Thailand

Ministry of University Affairs, Thailand

### With Technical Cooperation of

**IEICE**

**IEEK**

IEEE Thailand Section

Co-Organized by

King Mongkut's University of

Technology Thonburi, Thailand

Sirindhorn International Institute of Technology, Thammasat University, Thailand

# Design of a Current-Mode CCII-Based Bandpass Filter from Immittance Function Simulator using Commercial Available CCII (AD844)

Songphan Prakobnoppakao<sup>1</sup>, Boonruk Chipipop<sup>1</sup>, Wanlop Surakampontorn<sup>2</sup> and Kenzo Watanabe<sup>3</sup>

VLSI and Signal Processing Laboratory,

Department of Computer Engineering, Faculty of Engineering, King Mongkut's University of Technology Thonburi, 91 Pracha-Uthit Road, Bangkok 10140, Thailand Tel. +66-2-470-9083, +66-2-470-9085, Fax.: +66-2-872-5050

<sup>2</sup> Department of Electronics, Faculty of Engineering, King Mongkut's Institute of Technology Ladkrabang, Ladkrabang District, Bangkok 10520, Thailand Tel. +66-2-326-7723, Fax.: +66-2-326-9968

<sup>3</sup> Research Institute of Electronics, Shizuoka University, 3-5-1 Johoku, Hamamatsu 432-8011, Japan

Tel. +81-53-478-1326, Fax.: +81-53-478-1326 e-mail: boonruk@cpe.eng.kmutt.ac.th, kswanlop@kmitl.ac.th, watanabe-k@rie.shizuoka.ac.jp

Abstract: This paper proposes the design of a current-mode CCII-based 2<sup>pd</sup>-order bandpass biquad filter from a grounded series capacitor and frequency-dependent negative conductor (C-D) immittance function simulator using the macro model of a commercial available CCII+, AD844, from Analog Devices, Inc. The results are compared with the other results those are designed using ideal model of CCII-. The gain and phase deviations; due to the effects of passive sensitivity, active sensitivity, gain sensitivity and component variability; are considered using Monte-Carlo analysis of PSpice program.

### 1. Introduction

CCII has been proposed since 1970 by A. Sedra and K.C. Snith [1]. Now, it is a famous and versatile current-mode device. One important class of its application is continuous-time filter. Filter can be designed by many methods. One method uses immittance function simulator [2-5]. But the method proposed by T. Sattaya-aphitan, et. al. [6] uses less components, component matching is not required and more generalized method than the previous papers. Nevertheless, they use ideal model of CCII-.

Nowadays, there are only CCII+ in the market. We must use 2-CCII+ connected in cascade to form CCII-. The real characteristics of CCII+ and CCII- are not exactly the same as the ideal cases. In this paper, we use off-the-shelf integrated circuit no. AD844 of Analog Devices,Inc. functions as CCII+, and use macro model [7] in design a current-mode 2<sup>nd</sup>-order bandpass biquad filter from a grounded series capacitor and frequency-dependent negative conductor (C-D) immittance function simulator.

### 2. Theory

### 2.1 CCII ±

In general, the characteristic of an ideal second generation current conveyor (CCII) is given by the following hybrid matrix:

$$\begin{bmatrix} i_r \\ v_x \\ i_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} v_r \\ i_x \\ v_x \end{bmatrix}$$

(1)

+1 in equation(1) is referred to CCII+ and -1 is referred to CCII-. All currents go into the terminals of CCII+.

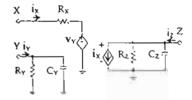

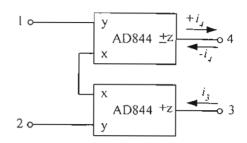

The macro (or real) model of AD844 functions as CCII+ is shown in figure 1.

Figure 1. Macro model of AD844.

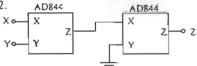

Where  $R_X = 50 \Omega$ ,  $R_Y = 10 M\Omega$ ,  $R_Z = 3 M\Omega$ ,  $C_Y = C_Z = 4.5$  pF. The two-cascaded AD844 functions as CCII- is shown in figure 2. AD844

Figure 2. AD844 implementation as CCII-.

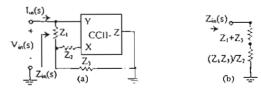

# 2.2 Grounded Series Immittance Function Simulator

The grounded series immittance function simulator [6] is shown in figure 3 and its input impedance is shown in equation (2).

Figure 3. (a) Grounded series immittance function simulator.

(b) Equivalent circuit.

$$Z_{in}(s) = \frac{1}{Y_{in}(s)} = \frac{V_{in}(s)}{I_{in}(s)} = Z_1 + Z_2 + \frac{Z_1 Z_2}{Z_2}$$

(2)

Given  $Z_1 = 1/sC_1$ ,  $Z_2 = R_2$  and  $Z_3 = 1/sC_3$ . We obtain the grounded series C-D immittance function as shown in equation (3).

$$Z_{in}(s) = \frac{1}{sC_{\infty}} + \frac{1}{s^2 D_{\infty}}$$

(3)

$Z_{in}(s) = \frac{I}{sC_{eq}} + \frac{I}{s^2D_{eq}}$ where  $C_{eq} = C_1C_3/(C_1+C_3)$  and  $D_{eq} = C_1C_3R_2$ which  $D_{eq} = \text{equivalent frequency-dependent negative}$ conductance (FDNG)

Figure 4. Grounded series C-D immittance function simulator.

We substitute the macro model of AD844 of figure 1 into the blocks of figure 2, after that, substitute it in CCII- of figure 4. We will obtain the input admittance as shown in equation (4) below.

$$Y_{m}(s) = \frac{I_{m}(s)}{V_{m}(s)} = \frac{As^{2} + Bs + C}{Ds + E}$$

(4)

$$\begin{split} & A = C_1 C_3 + C_1 C_Y + C_3 C_Y + C_1 C_Y G_3 R_X + C_3 C_Y G_3 R_X + C_1 C_3 G_2 R_X \\ & B = C_1 G_Y + C_Y G_2 + C_3 G_Y + C_1 G_3 G_Y R_X + C_3 G_3 G_Y R_X \\ & C = G_2 G_Y \\ & D = C_1 + C_3 + C_1 G_2 R_X + C_3 G_2 R_X \\ & \mathcal{E} = G_3 \end{split}$$

### 3. The Practical Bandpass Filter

We construct the practical bandpass filter as shown in figure 5 and the obtained current-mode bandpass transfer function is shown in equation (5).

Figure 5. The practical bandpass filter.

$$T_{gp}(s) = \frac{I_s(s)}{I_s(s)} = \frac{K\frac{\omega_p}{Q_p}s}{s^2 + \frac{\omega_p}{Q_p}s + \omega_p^2}$$

(5)

where

$$\omega_{\rho} = \sqrt{(C + EG_{o})! A} = \omega_{o}$$

(for BP filter)

$Q_{\rho} = \sqrt{A(C + EG_{o})! (B + DG_{o})}$

$K = -C_{o}G_{o}! (B + DG_{o})$

### 4. Simulation Results

We use PSpice program as the tool for simulation. First, given  $C_1 = C_3 = 22.5$  pF,  $R_2 = 5$  k $\Omega$  and  $R_0 = 10$  k $\Omega$ . The gain and phase responses are shown in figure 6 and important data are shown in table 1.

Figure 6. Uncompensated BP filter vs ideal-model BP filter.

Figure 7. Compensated BP filter vs ideal-model BP filter.

Table 1. Bandpass filter characteristics of figure 6.

| Tuois to the part of  |                |                |  |

|-----------------------|----------------|----------------|--|

|                       | BPF using      | BPF using real |  |

|                       | ideal model of | model of       |  |

|                       | CCII-          | CCII-          |  |

| fo = center frequency | 1.0 MHz        | 833.28 kHz     |  |

| Lower and upper       | 515 kHz and    | 284 kHz and    |  |

| cutoff frequency (f1  | 1.93 MHz       | 2.48 MHz       |  |

| and f <sub>2</sub> )  |                |                |  |

| Bandwidth (BW)        | 1.415 MHz      | 2.196 MHz      |  |

| Quality factor (Q)    | 0.707          | 0.38           |  |

| Gain at fo(dB)        | 75.04n         | -6.89          |  |

|                       |                |                |  |

Second, given  $C_1 = C_3 = 22.5$  pF,  $R_0 = 10$  k $\Omega$  and adjust  $R_2$  to be 3.5 k $\Omega$ . The gain and phase responses of the compensated BP filter are shown in figure 7 and important data are shown in Table 2.

Table 2. Bandpass filter characteristics of figure 7.

|                          | BPF using      | BPF using real |

|--------------------------|----------------|----------------|

|                          | ideal model of | model of       |

|                          | CCII-          | CCII-          |

| $f_0$ = center frequency | 1.0 MHz        | 1.0 MHz        |

| Lower and upper          | 515 kHz and    | 330 kHz and 3  |

| cutoff frequency (f1     | 1.93 MHz       | MHz            |

| and f <sub>2</sub> )     |                |                |

| Bandwidth (BW)           | 1.415 MHz      | 2.67 MHz       |

| Quality factor (Q)       | 0.707          | 0.375          |

| Gain at f₀(dB)           | 75.04n         | -5.62          |

|                          |                |                |

If all values of components in the model of CCII- are changed within  $\pm 1\%$ , the gain and phase deviations are shown in figure 8 and table 3.

Figure 8. Gain and phase deviations due to active devices

If all values of other passive components are also changed within ±1%, the gain and phase deviations are shown in figure 9 and table 3.

Figure 9. Gain and phase deviations due to passive elements.

Table 3.  $\Delta G$  and  $\Delta \varphi$  at lower and upper cutoff frequency and at center frequency.

### (a) Due to active elements only.

| frequency   | 330 kHz | 1 MHz  | 3 MHz  |

|-------------|---------|--------|--------|

| ΔG (dB)     | 0.0046  | 0.0139 | 0.0281 |

| Δφ (degree) | 0.061   | 0.093  | 0.096  |

### (b) Due to passive elements only.

| frequency       | 330 kHz | 1 MHz  | 3 MHz  |

|-----------------|---------|--------|--------|

| $\Delta G (dB)$ | 0.1155  | 0.0779 | 0.1878 |

| Δφ (degree)     | 0.666   | 0.785  | 0.818  |

### (c) Due to both active and passive elements .

| frequency   | 330 kHz | 1 MH2 | 3 MHz  |

|-------------|---------|-------|--------|

| ΔG (dB )    | 0.1317  | 0.636 | 0.1041 |

| Δφ (degree) | 0.708   | 0.78  | 0.64   |

If all values of active devices and passive elements are changed within  $\pm 1\%$ , the gain and phase deviations are shown in figure 10 and table 3.

Figure 10. Gain and phase deviations due to all elements.

### 5. Discussion & Conclusion

Real model of commercial CCII- (2-cascaded AD844) causes the gain and phase responses deviate from the responses of the prototype that uses ideal model of CCII-, although we use the same values of passive components.

We can see the effect in figure 6 that we call "uncompensated BP filter". The phase response is shifted about 180° for all frequency range.

After trying to adjust all components and observed the effects that happened. We found that it will give the best results when adjust R<sub>2</sub> only. The results is shown in figure 7 that we call "compensated BP filter". Nevertheless, the phase response is still shifted about 180° for all frequency range.

The right way to correct the phase response is to use 180°-phase shifter at the source or at the output.

In this design, we use Butterworth approximation for the clear picture of graphs.

There are still deviations both gain and phase responses around center frequency due to the effects of nonidealities of the real CCII-

The effects of passive sensitivity, active sensitivity, gain sensitivity and component variability to the gain and phase deviations are very small. We can observe the effects in the graphs of figure 8 to figure 10 and table 3.

i<sub>X</sub> is drawn from the BP filter by wide band current amplifier and is transmitted to a load.

If we break terminal Z from ground to draw current  $i_Z$  instead of  $i_X$  as the output current, the responses are not as good as we do because of the effect of  $R_Z$  and  $C_Z$ .

### References

- A. Sedra and K.C. Smith, "A second-generation current conveyor and its applications," *IEEE Trans. Circuit Theory*, vol. CT-17, no.2, pp. 132-134, 1970.

- [2] M. Higashimura and Y. Fukui, "Novel method for realizing lossless floating immittance using current conveyors," *Electron. Lett.*, vol. 23, no. 10, pp. 498-499,1987.

- [3] C.-L.Hou, R.-D. Chen, Y.-P. Wu and F.-C. Hu, "Realization of grounded and floating immittance function simulators using current conveyors," Int. J. Electron., vol. 74, no. 6, pp. 917-923, 1993.

- [4] A. Fabre and O. Saaid, "Novel translinear impedance converter and bandpass filter applications," *Electron. Lett.*, vol. 29, no. 9, pp. 746-747, 1993.

- [5] J. Malhotra and R. Senani, "Class of floating, generalized, positive/negative immittance converters/inverters realized with operational mirrored amplifiers," *Electron. Lett.*, vol. 30, no. 1,pp. 3-5, 1994.

- [6] T. Sattaya-aphitan, Boonruk Chipipop and Booncharoen Sirinaovakul, "Realization of grounded immittance functions using a single CCJI and their applications to current-mode biquad synthesis," Ladkrabang Engineering Journal, vol. 17, no. 1, pp. 138-143, 2000.

- [7] J.A. Svoboda, "Comparison of RC Op-Amp and RC current conveyor filters," Int. J. Electron., vol. 76, no. 4, pp. 615-626, 1994.

### Acknowledgement

This work is partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program, grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency ( JICA ), the Japan Society for the Promotion of Sciences ( JSPS ), and King Mongkut's University of Technology Thonburi are also acknowledged.

Besides, the authors would like to thank Miss Trungjai Tangsakul, Mr. Parinya Disorntetiwatana, Mr. Pantin Nantajiwakornchai, Mr. Rangsan Chaisrichareon, Mr. Seksan Mathulaprung-san, Mr. Tanya Sattaya-aphitan, Associate Professor Dr. Booncharoen Sirinaovakul, and Associate Professor Dr. Kobchai Deihan for their support.

# **Proceedings**

# 2002 IEEJ International Analog VLSI Workshop

September 11 - 12, 2002 Hilton Singapore, Singapore

Organized by

Research Committee on Electronic Circuits of

The Institute of Electrical Engineers of Japan (IEEJ)

In cooperation with IEEE Circuit and Systems Society Japan Chapter

### Dual Translinear Loop Multi-Output FTFN

### Amorn JIRASEREE-AMORNKUN<sup>†</sup>, and Wanlop SURAKAMPONTORN<sup>†</sup>

†Faculty of Engineering and Research Center for Communications and Information Technology (ReCCIT) King Mongkut's Institute of Technology Ladkrabang (KMITL), Ladkrabang, BKK 10520 THAILAND

E-mail: amorn@ieee.org, and kswanlop@kmitl.ac.th

### ABSTRACT

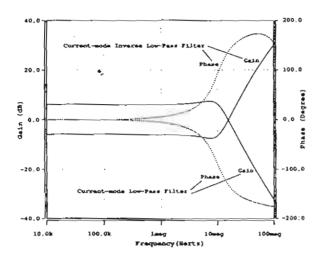

An alternative implementation scheme of a multi-output four-terminal floating nullor (FTFN) using dual translinear loops in BiCMOS technology is proposed. This presented circuit is simple and realized by base on the advantages of dual translinear loop cell circuit that comes up with high gain and wide bandwidth. The negative impedance is inserted between translinear loops to compensate the parasitic elements. The circuit performances are confirmed through HSPICE simulations. A current-mode low-pass filter and current-mode inverse low-pass filter with 10 MHz cut-off frequency are determined to exhibit the potentiality of this proposed scheme.

Keywords: Translinear, Multi-output, FTFN, Current-mode Filter

### 1. Introduction

In recent, there are many attempts to design a high performance four-terminal floating nullor (FTFN), which has been stood out as a more flexible and versatile than the other building blocks [1] - [4], especially in current-mode circuits. This paper shows another way to realize an integrable multiple-output FTFN in BiCMOS technology, which offers higher gain and wider bandwidth.

Since many FTFNs are usually implemented by using the conventional op-amp with a supply current sensing method, which are suffering from the critical limitation of op-amp itself and ungeneralized feedback path caused from using the cross-coupled current mirrors [1] - [2]. Translinear implementation, in contrast, allows the design of high performance circuits that provide both extended bandwidth and high thermal stability [5] - [6].

In addition, the number of output ports can be easily expanded to support the designer applications. It has been specified in the literature that an inappropriate implementation of the nullor can lead to errors in the realization of inverse filter [8]. Therefore, the current-mode low-pass and inverse low-pass filters are adopted to demonstrate the performance of this proposed circuit.

### 2. Basic Theory

### 2.1 Multi-Output FTFN

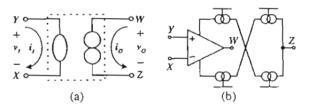

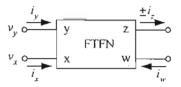

FTFN is an active device that equivalent to an ideal nullor, which can imply to be a high gain transcon-

Fig. 1. (a) A nullor model (b) traditional implementation.

ductance amplifier with floating characteristic at input and output terminals. Fig. 1(a) shows a nullor model of an FTFN that can be described by its port relation in matrix form as:

$$\begin{bmatrix} v_I \\ i_I \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} v_O \\ -i_O \end{bmatrix} \tag{1}$$

This mean the differential voltage across and the current feed through the input port are both zero. Moreover, the output properties are arbitrary with any restriction to input signal[9].

One of the most famous realisation techniques is built up from a basic type shown in Fig. 1 (b) [1] - [2]. It is using one op-amp and supply current sensing technique, where the output impedance of the port W is very low and the impedance of the port Z is very high.

The multi-output idea can be easily applied to the original FTFN by adding the new output terminals as shown in Fig. 2, where its characteristics can be

pointed out by the matrix

$$\left[\begin{array}{c} v_X \\ i_Y \\ i_{Zn} \end{array}\right] = \left[\begin{array}{ccc} 0 & 1 & . \\ 0 & 0 & 0 \\ 0 & 0 & -1 \end{array}\right]_{\ L}$$

where  $n = 1, 2, 3, \dots$  is number of the ou

Fig. 2. (a) Multi-output FTFN block (b) possible implementation.

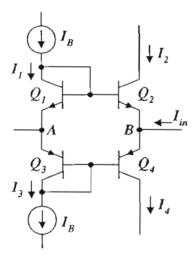

Fig. 3. Schematic form of the dual translinear loop.

### 2.2 Dual Translinear Loop

The dual translinear loop as shown in Fig. 3 composes of two PNP's and two NPN's transistors. Its characteristic is analyzed from the translinear relationship between collector currents of those transistors [5]:

$$I_1 I_3 = I_2 I_4 \tag{3}$$

The dc currents  $I_B$  are biased both  $Q_1$  and  $Q_3$ . Thus, we can get  $I_1 = I_3 = I_B$  by assuming that the current gain  $\beta$  of the transistors are much greater than unity.

The voltage between this two points depends on the ant  $I_{in}(t)$  as given by

$$V_{BA}(t) = \frac{V_T}{2I_B}I_{in}(t) \tag{4}$$

$^{7}/q \simeq 26$  mV at 27°C is the thermal sume that the magnitude of the cursuch smaller than  $2I_B$  [7]. It should be ance at port B is low. Therefore, this dual assinear cell can be used to realize the FTFN of Fig. 1(b).

### 3. Circuit Diagram

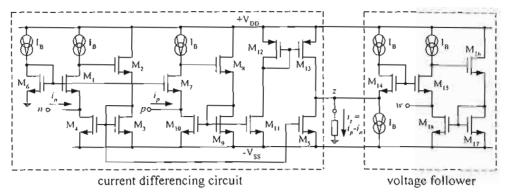

Fig. 4. Complete circuit of the dual translinear loop multi-output FTFN.

### 3.1 Overall Circuit

Fig. 4 show the complete circuit of the multi-output FTFN. This circuit basically comprises of 4 dual translinear loop cells connected each 2 cells' low-impedance ports together. Transistors  $Q_1$  to  $Q_8$  and the bias circuit, current source  $I_{B1}$  and transistor  $M_{B1}$  to  $M_{B6}$ , perform the first 2-dual translinear cells. Note that MOS transistors are used for the biasing to minimize noise; the main contribution in noise coming from current mirrors.

Fig. 9. Frequency response of current-mode filter.

### 5. Conclusions

We have proposed a simple FTFN circuit with additional extended output ports. The achievement has been realized through the use of quad dual translinear loop cells. The negative impedance implemented from dual translinear loop is added to compensate the internal parasitic impedance that can boot up the gain and also extend the operation frequency. Simulation results from HSPICE program confirm the high qualification of our presented circuit. A current-mode low-pass filter and its inverse filter are good examples to identify the feasibility of the circuit, however, the useful applications from the multi-output topology are still need some further researches.

### 6. Acknowledgements

This work was partly funded by the Thailand Research Fund (TRF) under the Senior Research Scholar Program grant number RTA/04/2543. The support provided by the Japan International Cooperation Agency (JICA) is also acknowledged.

### References

- [1] B. Chipipop and W. Surakampontorn, "Realisation of current-mode FTFN-based inverse filter," Electronics Letters, 35, pp. 690-692, April 1999.

- [2] W. Tangsrirat, S. Unhavanich, T. Dumawipata and W. Surakampontorn, "A realization of current-mode biquadratic filters using multiple-output FTFNs." Proc. IEEE APCCAS, pp. 201-204, 2000.

- [3] U. Cam, A. Toker and H. Kuntman, "CMOS FTFN realisation based on translinear cells," Electronics Letters, 36, pp. 1255-1256, July 2000.

- [4] A. Jiraseree-amornkun, B. Chipipop and W. Surakampontorn, "Novel Translinear-Based Multi-Output FTFN," Proc. IEEE ISCAS, pp. 180-183, 2001.

- [5] B. Gilbert, "Translinear circuits: a proposed classification," Electronics Letters, 11, pp. 14-16, Jan 1975.

- [6] A. Fabre, "New Formulation to Describe Translinear Mixed Cell accuracy," IEE Proc. G, Circuits, Devices and Systems, 141, pp. 167-172. June 1994.

- [7] A. Fabre, "High Frequency Applications Based on a New Current Controlled Conveyor," IEEE Trans. Circuits & Syst., CAS-43, 2, pp.82-91 February 1996.

- [8] A. Leuciuc, "Using nullor for realisation of inverse transfer functions and characteristics." Electronics Letter, 33, pages 949-951, May 1997.

- [9] L. T. Bruton, RC-Active Circuit Theory and Design, New York: John Wiley&Sons Inc., 1966

# **Proceedings**

# 2002 IEEJ International Analog VLSI Workshop

September 11 - 12, 2002 Hilton Singapore, Singapore

Organized by

Research Committee on Electronic Circuits of

The Institute of Electrical Engineers of Japan (IEEJ)

In cooperation with IEEE Circuit and Systems Society Japan Chapter

### A Wide-Band Current-Mode Analog Multiplier-Divider Using OTAs

Khanittha Kaewdang, Chalermpan Fongsamut and Wanlop Surakampontorn

Faculty of Engineering and Research Center for Communications and Information Technology (ReCCIT) King Mongkut's Institute of Technology Ladkrabang (KMITL), Ladkrabang, BKK 10520 THAILAND

E-mail: s3061304@kmitl.ac.th, kswanlop@kmitl.ac.th

### ABSTRACT

An analog multiplier-divider circuit that realized through the use of OTAs is proposed in this paper. Since the scheme is realized in such a way that employs only OTAs, which does not require external passive circuit elements and temperature compensated as a standard cell and does not require external passive circuit the circuit is simple and can be easily constructed from commercially available IC. The circuit bandwidth is wide and close to the transistor  $f_T$ . Simulation results that demonstrate the performances of the multiplier-divider circuit are included.

Keywords: Current-Mode. Multiplier-Divider, OTAs

### 1. Introduction

Analog multipliers and dividers are important nonlinear building blocks that have found useful in a wide range of applications, such as telecommunication, control, instrumentation and signal processing. At present, because of the main featuring of wider bandwidth, greater linearity, wider dynamic range and simple circuitry compared with their voltagemode counterparts, current-mode circuits have been received growing interest in analog signal processing circuits. Many techniques to design currentmode analog multiplier-divider circuits have been presented in the literature [1-3]. Also, a multiplierdivider circuit using only two second-generation current-controlled current-conveyors (CCCIIs) has been presented recently, where no resistors, no capacitors and no MOS transistors are required by such a realization scheme [4].

It is well accepted that OTA is a useful circuit building block in the design of analog circuits. Since OTA is a programmable device and has only a single high-impedance node, this makes the OTA an attractive device for high frequency and programmable basic building block [5,6]. Therefore, the implementation of analog circuits in such a way that employs only OTA as a standard cells will not only be easily constructed from readily available cells, but also significantly simplified the design and layout. Although, a circuit technique to employ OTAs to implement analog multiplier has been presented [17]. However, the circuit is a voltage-mode circuit where

only multiplication function is realized and the circuit bandwidth is only about 2 MHz. In this paper, a current-mode temperature compensated multiplier-divider circuit using only OTAs as active circuit elements has been presented, where no passive elements are required by this realization scheme. It should be mentioned that this realization scheme is suitable for the bipolar-based and CMOS-based OTAs that their transconductance gain can be tune by DC bias currents [8-9]. PSPICE simulation results will be used to demonstrate the performance of the proposed scheme.

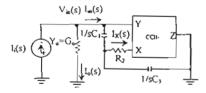

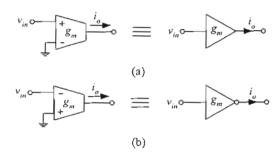

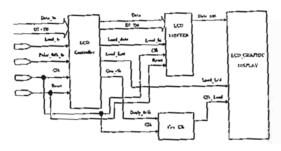

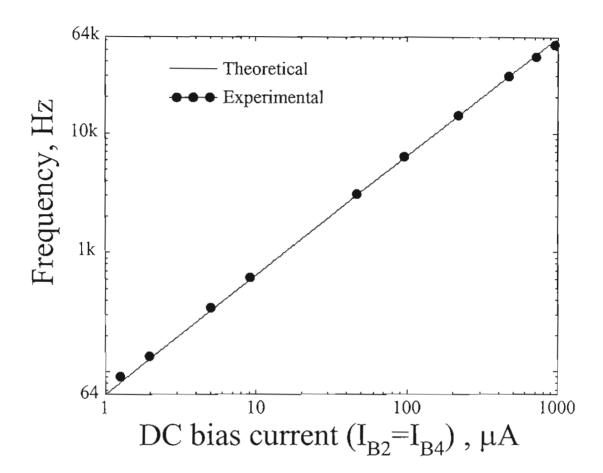

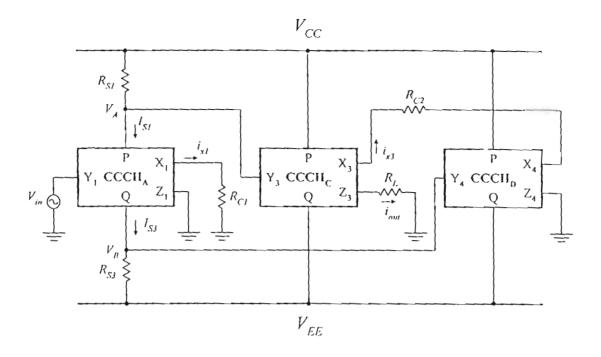

### 2. Basic principle

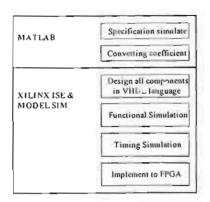

As shown in Fig.1, in this work an OTA that realized in bipolar transistor technology will be employed as active circuit elements. Its transconductance gain  $(g_m = I_B/2V_T)$ can be tune by the DC bias current  $(I_B)$ . The schematic diagram of the proposed current multiplier-divider circuit using OTAs is shows in Fig. 2. The input signal current tinl is injected into the operational transconductance amplifier OTA1, which is connected as a grounded resistor. The voltage across the OTA1 is then used as the input voltage for the OTA2 and OTA3. The input signal current  $i_{in2}$  is added with the bias current  $I_{B2}$  of the OTA2. If  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  are the transconductance gains of the OTA1, OTA2 and OTA3, respectively: then. from routine circuit analysis, the output currents I.v. and  $I_{O3}$  of the OTA2 and OTA3, respectively, can be written as

Fig. 1. The schematic diagram of the OTA.

$$I_{O2} = \frac{g_{m2}}{g_{m1}} i_{in1} = \frac{(I_{B2} + I_{in2})}{I_{B1}} i_{in1} \tag{1}$$

and

$$I_{O3} = -\frac{g_{m3}}{g_{m1}}i_{in1} = -\frac{(I_{B3})}{I_{B1}}i_{in1} \tag{2}$$

where  $g_{m1} = I_{B1}/2V_T$ ,  $g_{m2} = (I_{B2} + i_{in2})/2V_T$  and  $g_{m3} = I_{B3}/2V_T$  and  $V_T$  is the thermal voltage. If we set  $I_{B2} = I_{B3} = I_B$ , the output current  $I_{out}$  of the circuit, that is the summation of the currents  $I_{O2}$  and  $I_{O3}$  can now be given by

$$I_{out} = I_{O2} + I_{O3} = \frac{i_{in1}i_{in2}}{I_{B1}} \tag{3}$$

which is in the form of a current-mode analog multiplication-division function. The circuit performs as a four-quadrant multiplier if  $i_{in1}$  and  $i_{in2}$  are the input signals, while it performs as a divider circuit if  $i_{in1}$  (or  $i_{in2}$ ) and  $I_{B1}$  are the input signals. It should be noted that, since it is the ratio of OTAs transconductance gain, the output current  $l_{out}$  is less sensitive to temperature.

The major factors that contribute to the error and non-linearity in the circuit can be classified as follows. The first factor is due to the offset current at the output port of the OTA1. From (3), if  $I_{os}$  is the offset current, the output current Iout can be rewritten as

$$I_{out} = \frac{\sqrt{i_{:n1} + I_{os}})i_{:n2}}{I_{B1}} \tag{4}$$

We can see that, if  $i_{in1}$  is small or the peak value  $|i_{in1}| < I_{os}$ , the multiplication for the positive peak and the negative peak of  $i_{in1}$  will not be equal. While the offset currents at the output ports of the OTA2 and OTA3 are not contribute to the multiplication

Fig. 2. The proposed current-mode multiplier-divider circuit using OTAs.

error, but will produce a DC current at the output of the circuit. The second factor affecting the nonlinearity of the circuit is due to the limited linear range of the input stage of the OTA2 and OTA3. For a bipolar-based OTA, where the input stage is a conventional differential pair, the input differential voltages for linear operation are restricted to be less than 26 mV. Therefore, to minimize this error, the voltage swing across the OTA1 should be kept to be less than 26 mV. Since  $1/g_{m1} = 2V_T/I_{B1}$ , this restricted linear range can be improve by increasing  $I_{B1}$ .

### 3. Simulation results

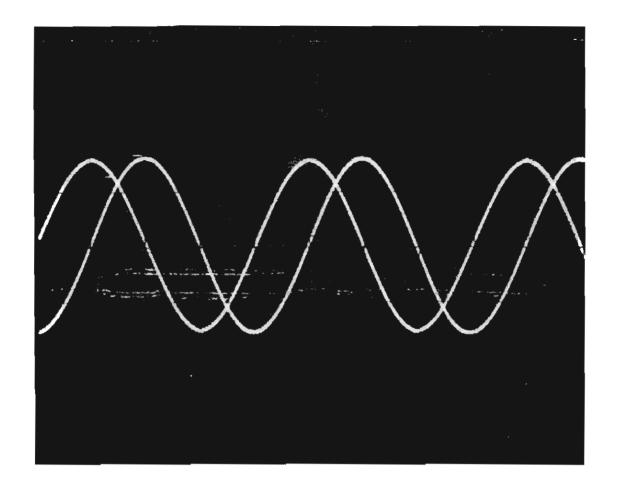

The performance of the proposed multiplier-divider circuit of Fig.2 was verified through the use of SPICE simulation results. All the OTA was simulated by using the bipolar transistor parameters of the 2N3904 and 2N3906 for the NPN and PNP transistors, respectively. The transistors  $f_T$  were 186MHz. The multiplier function was tested by multiplying two sinusoidal signals. The result obtained are shown in Fig.3 for  $i_{in1} = 0.5sin(2\pi 1000t) \text{mA}$ .  $i_{1n2} = 0.5 sin(2\pi 30000t)$ mA and  $I_{B1} = 1$ mA. Since the DC offset current will distort the output signal, a DC current of about 5µA was injected at the output of the OTA1 to adjust the offset to be less than 0.1 µA. Similarly, a DC current of about 5 µA was used to keep the offset current at the output of the circuit to be less than  $0.1\mu A$ . The power supply voltages were set to  $V_{CC} = 10 \text{V}$  and  $V_{EE} = -10 \text{V}$ .

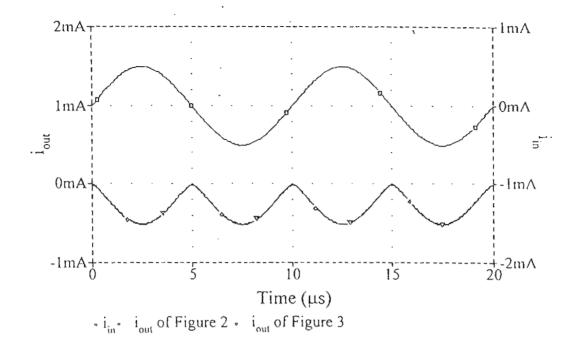

The divider function was tested by inverting a triangular signal. The results obtained are show in Fig.4. Fig.4 show the simulated transient response of the circuit that function as a divider. The output current  $I_{out}$ , which in this case is an inverting function of a triangular signal, was simulated for  $i_{in1} = 100 \text{mA}$ ,  $i_{in2} = 300 \text{mA}$ , and  $I_{B1}$  is a 500Hz triangular wave with amplitude of  $100 \mu \text{A}$  and DC component of equal to  $200 \mu \text{A}$ .