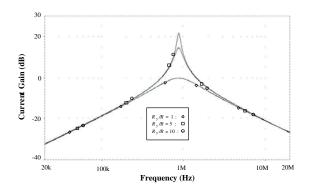

frequencies as a result. This thus implies bandwidth degradation in both the lossy SH and HS networks due to the Q reduction.

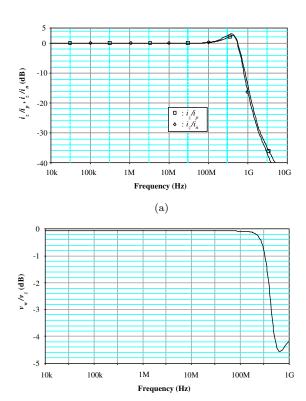

Similar to the analysis in Section III, the peaking and bandwidth performance of the lossy SH and HS networks can be determined from the transresistance,  $H'(i\omega)$ , of the reference network in Fig. 11(a) and this is given by (9), shown at the bottom of the page, where the quality factors in the equation are defined as  $Q_{Ls} =$  $\omega L_S/R_S$ ,  $Q_{C_{1,2}} = 1/\omega r_{1,2}C_{1,2}$  and  $Q' = Q_{L_S}Q_{C_1}Q_{C_2}$ . With the use of (9), the passband-edge peaking of the lossy reference network  $G_p'$  can be approximated at  $\omega_2$  of the ideal reference network of Fig. 5(b) [see (2)] and this is expressed as  $G_p' = \delta G_p$  where  $\delta$  is given by (10), shown at the bottom of the page. Note that  $Q_{Ls}$ ,  $Q_{C1,2}$  and Q' in (10) are also defined at  $\omega_2$  of the ideal network. By using (10), the surface plot of the peaking level  $G_p'$  versus the Qs is shown in Fig. 12(a) for the SH network at  $C_d/C_g=0.6$ , and in Fig. 12(b) for the HS network at  $C_d/C_q = 1.0$ . Due to higher losses, the peaking continuously drops at smaller Qs. For a particular case of interest at  $Q_{Ls} = Q_{Cq} = 8$ , the SH network exhibits about 1.26-dB peaking—a drop by as much as 7 dB from the ideal response in Fig. 10(b). For the HS network, the peaking disappears and there is attenuation at about -1.87 dB [see (9) and (10)].

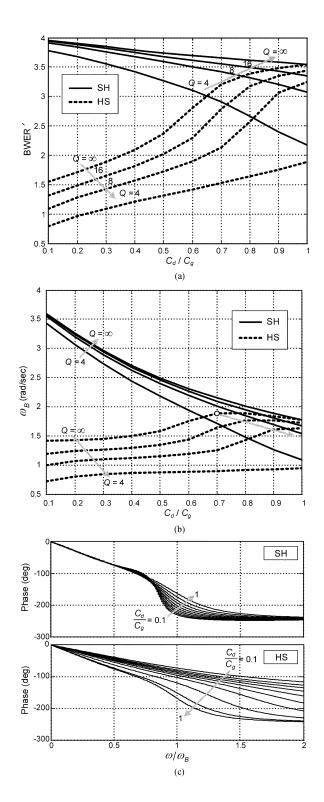

Also based upon the transfer function in (9), the resulting BWER and absolute bandwidth that include the effect of the parasitic resistances can be computed numerically. The BWER dependences against the ratio  $C_d/C_g$  are given in Fig. 13(a) for a set of  $Q_{Ls}=Q_{Cg}=4, 8, 16, \text{ and } \infty \text{ at } \omega_2$ . Whereas the plots indicate the degradation of the BWER with the  ${\cal Q}$  reduction as implied by the triple resonance movement in Fig. 11(b), it is noticed that the impact on HS peaking is more pronounced. Another important observation can be made from the plots of the corresponding absolute bandwidth in Fig. 13(b) for the normalized networks with  $R = 1/g_m = 1$  and  $C_q = 1$ . When compared to the ideal case in Fig. 8(b), in the presence of the parasitics, the optimum bandwidth of HS peaking occurs at a larger  $C_d/C_g$ , i.e., approaching  $C_d/C_g = 1$ , with a consequent requirement of a larger  $C'_d$ . Also, from the phase plots versus the normalized frequency  $\omega/\omega_B$  of Fig. 13(c), as compared to Fig. 8(c), the lossy SH network exhibits considerably less steep phase characteristics, particularly at a small  $C_d/C_q$ .

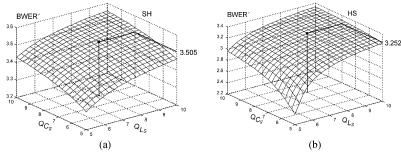

The surface plots of the BWER versus  $Q_{Ls}$  and  $Q_{Cg}$  at  $\omega_2$  are given in Fig. 14(a) for lossy SH peaking at  $C_d/C_g=0.6$ , and in Fig. 14(b) for the optimum lossy HS peaking at  $C_d/C_g=1.0$ . At  $Q_{Ls}=Q_{Cg}=8$ , the BWER drops from 3.7 to 3.5 (5.4% reduction) for SH, and from 3.54 to 3.25 (8% reduction) for HS peaking. This suggests that, although the parasitic effect is included, SH peaking still maintains a bandwidth advantage.

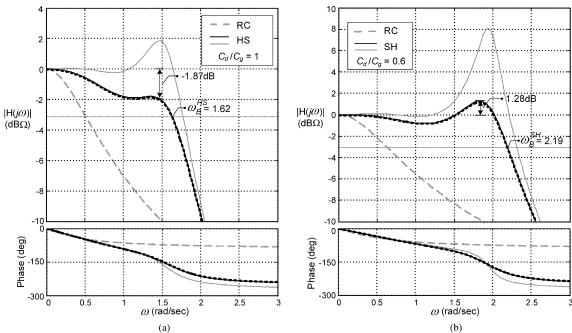

As a verification, simulated magnitude and phase responses for the lossy SH and HS peaking networks are given where two cases are considered, i.e., at: 1)  $C_d/C_g=1.0$  for the normalized

HS network [Fig. 15(a)], and 2)  $C_d/C_g = 0.6$  for the normalized SH network [Fig. 15(b)]. Also included in Fig. 15(a) and (b) for comparison are the simulated responses based on the distributed RC gate model at N = 32 [see Fig. 11(c)] where close matching with the responses based on the single  $r_q - C_q$ gate model is observed. From the magnitude plots, the HS network exhibits a BWER of 3.25 and an attenuation at -1.87 dB whereas the simulated responses for SH indicate the BWER at 3.5 and peaking at 1.28 dB, in good agreement with the plots of Fig. 12(a) and (b) and Fig.14(a) and (b). The phase plots indicate similar phase characteristics between the two networks with respect to their corresponding bandwidths. It should be noted that, due to such changes of both peaking and bandwidth of a practical CA, some adjustments on  $L_H$  and  $L_S$  from the design equations in (4) and (6) are necessary to maintain a flat response at midband frequencies.

#### C. Noise Characteristics

Due to the multiplicative noise characteristic of a CA, its noise performance is inferior to a classical DA. By considering only thermal noise, the noise factor F of a CA with identical stages for frequencies up to near the passband edge can be expressed by

$$F = 2 + 4\frac{R}{R_o} \left( \left( \frac{1}{(g_m)^{2n} R^{2n-1} R_o} - 1 \right) + \left( 1 + \frac{\gamma}{g_m R} \right) \sum_{i=0}^{n-1} \frac{1}{(g_m R)^{2i}} \right)$$

(11)

where  $R_o$  represents both the input source and output load impedances, and  $\gamma$  denotes the excess noise coefficient. Note that the noise figure equation omits thermal noise from the bulk resistance of the gate material, and the gate-induced noise that is only significant when the operating frequency approaches the transition frequency  $f_T$  of the transistors [13]. Since a CA typically exhibits bandwidth somewhat less than  $f_T$ , only the drain current thermal noise appears as the dominant transistor noise source over the entire bandwidth of the amplifier. To assist the following design procedure in Section V, (11) may be expressed in terms of the overall amplifier parameters, with all variables related to devices and components removed, as

$$F = 2 + \left(\frac{1}{G_{\text{tot}}^2} - 4\rho\right) + \left(4\gamma \left(\frac{\rho^{2(n-1)}}{4G_{\text{tot}}^2}\right)^{1/2n} + 4\rho\right) \sum_{i=0}^{n-1} \left(\frac{1}{4\rho^2 G_{\text{tot}}^2}\right)^{i/n}$$

(12)

where  $\rho = R/R_o$ ,  $G_{\rm tot} = (g_m R)^n/2\rho = G_i^n/2\rho$  [8], [9]. It should be noted from (12) that F increases with both n and  $\rho$ .

$$H'(j\omega) = \frac{R\left[\left(1+j\omega m\left(\frac{\tau_{2}^{2}}{\tau_{4}}\right)\right)\left(-Q_{Ls}(Q_{C1}+Q_{C2})+j\left(Q'-Q_{Ls}\right)\right)\right]}{\left[\omega^{4}(\tau_{1}\tau_{2})^{2}Q_{C1}Q_{C2}+\omega^{3}\tau_{2}^{2}\tau_{3}Q'+\omega^{2}\left(\tau_{2}^{2}(Q_{Ls}Q_{C2}(1+m)-Q_{C1}Q_{C2})+\tau_{1}^{2}Q_{Ls}Q_{C1}\right)-\omega Q'(\tau_{3}+\tau_{4})+Q_{Ls}(1-(Q_{C1}+Q_{C2}))\right]+} \qquad (9)$$

$$j\left[\omega^{4}(\tau_{1}\tau_{2})^{2}Q'-\omega^{3}\tau_{2}^{2}\tau_{3}Q_{C1}Q_{C2}-\omega^{2}\left(\tau_{2}^{2}(Q'(1+m)+Q_{C2})+\tau_{1}^{2}Q'\right)-\omega Q_{Ls}(\tau_{3}Q_{C1}+\tau_{4}Q_{C2})+Q'-Q_{Ls}\right]}{m\sqrt{(Q_{Ls}(Q_{C1}+Q_{C2}))^{2}+(Q'-Q_{Ls})^{2}}}$$

$$\delta = \frac{m\sqrt{(Q_{Ls}(Q_{C1}+Q_{C2}))^{2}+(Q'-Q_{Ls})^{2}}}{\sqrt{\left[\left(\omega_{2}\tau_{1}\right)^{4}Q_{C1}Q_{C2}+\omega_{2}^{2}\tau_{1}^{2}\tau_{3}Q'+\omega_{2}^{2}\tau_{1}^{2}(Q_{Ls}(Q_{C2}+m(\alpha_{C1}+Q_{C2}))-Q_{C1}Q_{C2})-\omega_{2}(\tau_{3}+\tau_{4})m\alpha Q'+m\alpha Q_{Ls}(1-(Q_{C1}+Q_{C2}))\right]^{2}+}}$$

$$\left[\left(\omega_{2}\tau_{1}\right)^{4}Q'-\omega_{2}^{3}\tau_{1}^{2}\tau_{3}Q_{C1}Q_{C2}-\omega_{2}^{2}\tau_{1}^{2}(Q'(1+m(1+\alpha))+Q_{C2})-\omega_{2}(\tau_{3}Q_{C1}+\tau_{4}Q_{C2})m\alpha Q_{Ls}+m\alpha(Q'-Q_{Ls})\right]^{2}}$$

$$(10)$$

Fig. 13. Effect of parasitic resistances (via the Q factors  $Q_{Ls}=Q_{Cg}=Q$ ) on (a) BWER, (b) normalized bandwidth and (c) phase responses at Q=8.

At a larger n, a lower gain per stage, particularly in the first few stages, leads to more noise contribution of subsequent stages and hence a higher F results. At a higher  $\rho$ , although the stage transconductance  $g_m$  is reduced, more stage noise ( $\propto g_m R^2 = g_m \rho^2 R_o^2$ ) is effectively generated due to higher interstage resistance. From the described characteristic, it follows that, given

CA specifications, both n and  $\rho$  should be minimized for a low noise design.

#### V. DESIGN EXAMPLES

### A. Initial Design Calculation

Based on the developed equations in the previous sections, a flow of initial parameters' calculation that can be equally applied to both SHCA and HSCA is outlined as follows. The design may start from a selection of the number of stages n which should be kept small. For most typical applications with low to moderate noise requirement, n is lower than five stages [11]. From the total gain and noise factor specifications,  $G_{\rm tot}$  and F, the resistor ratio  $\rho$  is determined at the selected n using (12) and this yields the interstage resistance  $R = \rho R_o$ . Next, the interstage gain  $G_i$  can be decomposed from  $G_{\rm tot}$  at

$$G_i = \sqrt[n]{2\frac{R}{R_o}G_{\text{tot}}} = \sqrt[n]{2\rho G_{\text{tot}}}$$

(13)

and the required transconductance  $g_m$  for the transistor at each stage is at  $g_m = G_i/R$ . For the CA to exhibit gain advantage over the DA, it requires that  $G_i > n^{(1/n-1)}[8]$ . If this is not the case, n should be reduced until the condition is satisfied. From the total bandwidth specification  $\mathrm{BW}_{\mathrm{tot}}$ , since both SH and HS peaking are fourth-order networks, the interstage bandwidth  $\mathrm{BW}_i$  may be calculated by [12]

$$BW_i = \frac{BW_{\text{tot}}}{\left(\sqrt[k]{2^{1/n} - 1}\right)}$$

(14)

where k is equal to 8. By combining (13)–(14) and the BWER definition, the total gate capacitance at each of the transistor amplifiers is determined at

$$C_g = \frac{\mathrm{BWER'}}{(1+\alpha)} \cdot \frac{g_m}{G_i 2\pi \mathrm{BW}_i}.$$

(15)

The equation requires estimation of the parameters  $\alpha = C_d/C_g$  and BWER' which can be obtained from the plot similar to Fig. 14(a) and (b) where the effect of the parasitic resistances is included via the estimated parameters  $Q_{Ls}$ and  $Q_{Cq}$ . With another estimation on the parasitic capacitances that contribute to  $C_g$  and  $C_d$ , the intrinsic gate-source capacitances  $C_{gs}$  and hence the amplifier transistor's width W at the minimum feature length  $L_{\min}$  can be computed. Continuing the design, by using the short-channel MOS transistor model equations (see [13] for an example), the transistor gate-overdrive  $V_{od} (= V_{gs} - V_t)$  and the drain current consumption  $I_d$ are obtained. Subsequently, the inductances  $\mathcal{L}_H$  and  $\mathcal{L}_S$  are determined using (4) and (6) where  $C_1 = C_q$  and  $C_2 = C_d$ for SHCA and vice versa for HSCA. For optimum bandwidth in HSCA, an additional capacitance may be required to make the ratio  $C_d/C_g = 1.0$  as indicated by the theoretical plot in Fig. 13(b). At this stage, the estimation of the parasitic capacitances and resistances in the amplifier transistors and

Fig. 14. Calculated plots of BWER versus quality factors  $Q_{Ls}$  and  $Q_{Cg}$  for (a) SH peaking and (b) HS peaking networks with parasitic resistances.

Fig. 15. Simulated frequency responses based on distributed RC model (dark dotted curves) and single RC equivalent model (dark solid curves) at  $Q_{Ls} = Q_{Cg} = 8.0$  for (a) HS peaking at  $C_d/C_g = 1.0$  and (b) SH peaking network at  $C_d/C_g = 0.6$ .

inductors can be made more accurate with the help of simulation using practical electrical RF models and layouts. This also enables selection of the dimensions of the inductors  $L_H$  and  $L_S$  for the desired Qs via the plot similar to Fig. 12 so that the passband-edge peaking of the CA can be controlled. By putting back the simulated parasitics into (15), the parameters W,  $V_{od}$  and  $I_d$  can be re-calculated with improved precision. Finally, given the simulated total capacitances  $C_g$  and  $C_d$ , the input and output matching inductances of the CA can be obtained based on the traditional T-network design.

### B. Simulation Results

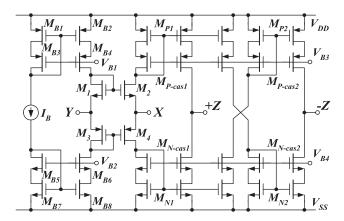

To demonstrate the integrity of the analysis and design, the SHCA has been designed, laid out and simulated using a 0.18- $\mu m$  1.8 V 6-Metal RF CMOS process. The amplifier's total gain was specified at  $G_{\rm tot} \geq 15$  dB and the bandwidth at BW  $_{\rm tot} \geq 12.5$  GHz. The specified noise factor is at  $F \leq 10$  (or  $\leq 10$  dB). The input source and output load impedances are selected at  $R_o = 50~\Omega$ . For implementation of the amplifier stages, the cascoded transistor configuration was employed.

For realistic simulation, practical RFMOS device and passive component models provided by the process design kit were employed. The interconnect parasitics were characterized via electromagnetic (EM) simulation and these were subsequently included in SpectreRF circuit simulation. Following the outlined

TABLE I SUMMARY OF DESIGN PARAMETERS FOR THE SHCA

| Specifications                        |                                                  |                                                 |  |  |  |  |

|---------------------------------------|--------------------------------------------------|-------------------------------------------------|--|--|--|--|

| $G_{tot} \ge 15 \mathrm{dB}$          |                                                  |                                                 |  |  |  |  |

|                                       | $BW_{tot} \ge 12.5GHz$                           |                                                 |  |  |  |  |

|                                       | $F \leq 10$                                      |                                                 |  |  |  |  |

|                                       | Amplifier parameter                              | s                                               |  |  |  |  |

|                                       | n = 4                                            |                                                 |  |  |  |  |

|                                       | $G_i = 2.027$                                    |                                                 |  |  |  |  |

|                                       | $g_m = 27.03 \text{mS}$                          |                                                 |  |  |  |  |

|                                       | $R = 75\Omega$                                   |                                                 |  |  |  |  |

|                                       | $BW_i = 15.4GHz$                                 |                                                 |  |  |  |  |

| Component parameters                  |                                                  |                                                 |  |  |  |  |

| Parameters                            | Initial values Final values                      |                                                 |  |  |  |  |

| $C_{g}$                               | 300fF                                            | 255fF                                           |  |  |  |  |

| $C_{pg}^{ m Tr}$                      | 180fF                                            | 170fF                                           |  |  |  |  |

| $C_p^{\mathrm{I}} + C_p^{\mathrm{L}}$ | $0.4C_g$                                         | (0.137+0.196) C <sub>g</sub>                    |  |  |  |  |

| W                                     | 90μm                                             | 85µm                                            |  |  |  |  |

| $V_{od}$                              | 0.248V                                           | 0.32V                                           |  |  |  |  |

| $I_d$                                 | 4.67mA                                           | 6.155mA                                         |  |  |  |  |

| $L_H$                                 | 0.85nH                                           | 1.16nH                                          |  |  |  |  |

| $L_{\mathcal{S}}$                     | 1.3nH                                            | 1.67nH                                          |  |  |  |  |

| $\alpha = C_d/C_g$                    | 0.6                                              | 0.63                                            |  |  |  |  |

| $Q_{Ls}$ / $Q_{Cg}$                   | 8/8                                              | 7.7 / 6.7                                       |  |  |  |  |

| $[@\omega_2]$                         | $[@2\pi \cdot 13.16 \cdot 10^9 \text{ rad/sec}]$ | $[@2\pi \cdot 12.4 \cdot 10^9 \text{ rad/sec}]$ |  |  |  |  |

| $R_S / r_g$                           | 13.43 / 5                                        | NA                                              |  |  |  |  |

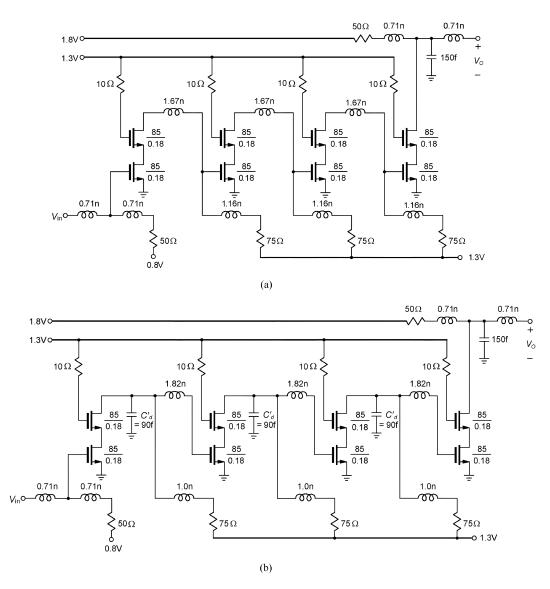

Fig. 16. Schematics of the designed SHCA and HSCA with four stages.

TABLE II SUMMARY OF DESIGN PARAMETERS FOR THE HSCA

| Parameters                            | Initial values                                     | Final values                                     |

|---------------------------------------|----------------------------------------------------|--------------------------------------------------|

| $C_g$                                 | 300fF                                              | 215fF                                            |

| $C_{pg}^{ m Tr}$                      | 180fF                                              | 170fF                                            |

| $C_p^{\mathrm{I}} + C_p^{\mathrm{L}}$ | $0.4C_g$                                           | $(0.095+0.116) C_g$                              |

| $L_H$                                 | 0.85nH                                             | 1.0nH                                            |

| $L_S$                                 | 1.64nH                                             | 1.82nH                                           |

| $C'_d$                                | 72fF                                               | 90fF                                             |

| $Q_{Ls}/Q_{Cg}$                       | 8/8                                                | 7.7 / 8.3                                        |

| $[@\omega_2]$                         | [@ $2\pi \cdot 10.15 \cdot 10^9 \text{ rad/sec}$ ] | $[@2\pi \cdot 11.38 \cdot 10^9 \text{ rad/sec}]$ |

| $R_S / r_g$                           | 13 / 6.5                                           | NA                                               |

parameters' design at four stages, i.e., n=4, the initial component values can be computed. Subsequently, these were adjusted manually via simulation for the final values. Table I summarizes the initial and final design parameters of the SHCA where close matching between the two parameters implies the efficiency of the design flow. In the table, the numbers in italic were estimated

Fig. 17. Simulated interstage responses of the four-stage SHCA and HSCA without interconnection parasitics (gray lines) and with parasitics (dark lines).

values for calculation of the initial parameters. Also, the final inductances are larger than the initial design and this is mainly to account for the parasitic resistance effect.

| Condition ( | Performance<br>°C) | BW <sub>i</sub> <sup>SH</sup> (GHz) | BW <sub>i</sub> <sup>HS</sup> (GHz) | BW <sub>i</sub> Ratio |

|-------------|--------------------|-------------------------------------|-------------------------------------|-----------------------|

|             | -40                | 15.14                               | 11.51                               | 1.31                  |

| Slow        | 27                 | 14.39                               | 11.2                                | 1.28                  |

|             | 100                | 13.48                               | 10.85                               | 1.24                  |

|             | -40                | 15.52                               | 11.81                               | 1.31                  |

| Typical     | 27                 | 14.9                                | 11.6                                | 1.28                  |

|             | 100                | 14.07                               | 11.25                               | 1.25                  |

|             | -40                | 15.24                               | 11.72                               | 1.30                  |

| Fast        | 27                 | 14.13                               | 11.39                               | 1.24                  |

|             | 100                | 13.02                               | 11.03                               | 1.18                  |

TABLE III

INTER-STAGE BANDWIDTH PERFORMANCE UNDER EXTREME PROCESS AND

TEMPERATURE CONDITIONS

Fig. 16(a) shows the schematic of the designed SHCA. A resistor (10  $\Omega$ ) is inserted at the gate of each of the cascode transistors for good stability [4]. In the amplifier layout (not shown), the circular spiral using metal 6 was adopted for all the inductors. For comparison, the four-stage HSCA was also designed using the same transistor stage with  $W/L_{\min}$  ,  $I_d$  and R identical to the final parameter assignment in Table I. This essentially yields the same gain and power consumption as those of the SHCA but the bandwidth is different. The amplifier schematic is shown in Fig. 16(b) with the additional  $C'_d$ , implemented by a MIM capacitor, included for optimum bandwidth. The final inductance and capacitance design values are listed in Table II for the optimum HSCA. From Tables I and II, since the resulting overall capacitance ratio at each of the SHCA transistor gain stages is  $C_d/C_q = 0.63$ , it is anticipated from the BWER plots in Fig. 14(a) and (b) under their corresponding final Q parameters that the SHCA should exhibit a bandwidth advantage over the HSCA, with  $C'_d$  added to yield  $C_d/C_g = 1.0$ , by about a factor of 1.3.

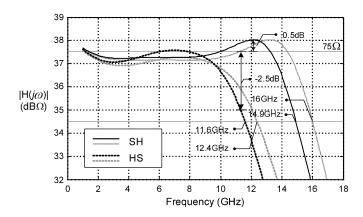

The simulated interstage frequency responses of the designed SHCA and HSCA with and without interconnect parasitic capacitances are shown in Fig. 17. It is seen that, for both of the CAs, a bandwidth reduction by about 7% results from the parasitics. For the SHCA, the interstage peaking near the passband edge frequency at  $\omega_2 = 2\pi 12.4 \cdot 10^9$  rad/s is 0.5 dB. For the HSCA, there is -2.5 dB attenuation at its  $\omega_2 = 2\pi 11.38 \cdot 10^9$  rad/s. The interstage bandwidth of the HSCA is at 11.6 GHz and that of the SHCA is larger by a factor of 1.28, i.e., at 14.9 GHz, close to the theoretical prediction. It should be noted that, as indicated by simulation under extreme process and temperature conditions, the relative bandwidth figures between the interstage responses of the SHCA and HSCA are only varied slightly, as summarized in Table III.

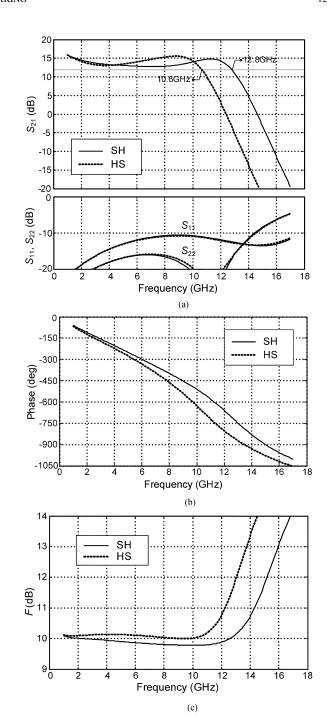

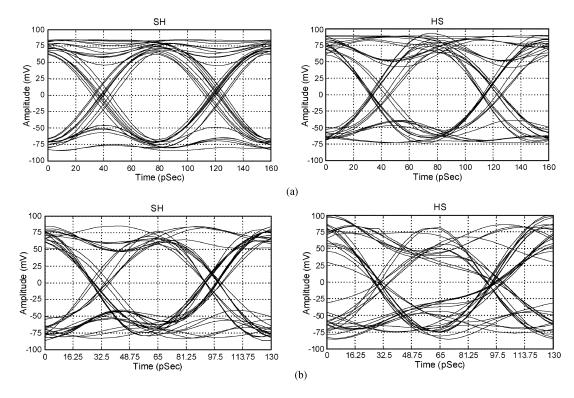

Fig. 18(a) shows the simulated overall frequency characteristics of the four-stage CAs. The responses indicate the SHCA bandwidth at 12.8 GHz and this is about 1.2 times more than the bandwidth of the optimum HSCA at 10.6 GHz. From the responses in Fig. 18(a), both the CAs exhibit a low-frequency gain at 15.7 dB and the return loss characteristics at the input and output ports are all kept below -10 dB within their corresponding bandwidth. Fig. 18(b) shows the simulated phase responses of the amplifiers. The simulated noise factor F (in decibles) of the amplifiers is almost identical at 10 dB [Fig. 18(c)] for frequencies up to their passband edges. Note that simulation also indicates a less than 4% contribution from gate noise. Finally, simulated output eye diagrams for a set of 12.5- and

Fig. 18. Simulated CA performances (a) overall magnitude responses (b) phase responses (c) noise figure.

15-Gb/s input random data are given in Fig. 19(a) and (b) confirming the speed advantage in the SHCA.

### VI. CONCLUSION

The triple-resonance bandwidth enhancement techniques based on SH and HS peaking for interstage networks of wide-band CAs have been investigated. From the qualitative time-domain operation, although both networks enable serial charging of the drain and gate capacitances, it has been shown that SH peaking inherently offers superior bandwidth enhancement due to less diversion of the gate charging current. By using the triple-resonance concept, the frequency-domain

Fig. 19. Simulated eye diagrams at (a) 12.5 Gb/s and (b) 15 Gb/s.

characteristics of the networks were studied. Based upon this frequency-domain insight and also the reciprocal property between the SH and HS networks, analytical design equations that are equally applicable to both networks have been developed. Subsequently, the equations were employed for a quantitative bandwidth comparison. The frequency characteristics of both peaking networks against the capacitor ratio  $C_d/C_q$  were discussed through the relative locations of their three resonant frequencies. Specifically, it has been shown that SH peaking maintains a high BWER over a wide range of  $C_d/C_q$  ratios and, as the ratio converges to zero, its BWER approaches the theoretical limit of a bandwidth enhancement two-port network. On the other hand, HS peaking exhibits a considerably inferior BWER. Moreover, its BWER is degraded as the ratio  $C_d/C_q$ decreases and a certain  $C_d/C_g$  ratio is required to achieve optimum HS bandwidth. Peaking suppression and bandwidth reduction in the SH and HS networks as a result of the nonideal effects due to transistor's gate resistance and inductors' losses were analyzed in detail. The noise expression of a CA was given and calculation of the initial parameters was described. Verification of the analysis equations was provided via practical simulations where close agreement between the theoretical indications and simulation results was observed. Following the extensive theoretical analysis and verification, SH peaking has manifested itself as a superior technique for implementation of integrated wide-band CMOS CAs.

### REFERENCES

- [1] E. L. Ginzton, W. R. Hewlett, J. H. Jasberg, and J. D. Noe, "Distributed amplification," *Proc. IRE*, vol. 36, pp. 956–969, Aug. 1948.

- [2] S. Kimura and Y. Imai, "0–40-GHz GaAs MESFET distributed baseband amplifier ICs for high-speed optical transmission," *IEEE Trans. Microw. Theory Tech.*, vol. 44, no. 11, pp. 2076–2082, Nov. 1996.

- [3] B. M. Ballweber, R. Gupta, and D. J. Allstot, "A fully integrated 0.5–5.5-GHz CMOS distributed amplifier," *IEEE J. Solid-State Circuits*, vol. 35, no. 2, pp. 231–239, Feb. 2000.

- [4] R. C. Liu, C. S. K. Lin, L. Deng, and H. Wang, "Design and analysis of DC-to-14-GHz and 22-GHz CMOS cascode distributed amplifiers," *IEEE J. Solid-State Circuits*, vol. 39, no. 8, pp. 1370–1374, Aug. 2004.

- [5] S. S. Mohan, M. M. Hershenson, S. P. Boyd, and T. H. Lee, "Bandwidth extension in CMOS with optimized on-chip inductors," *IEEE J. Solid-State Circuits*, vol. 35, no. 3, pp. 346–355, Mar. 2000.

- [6] C. H. Wu, C. H. Lee, W. S. Chen, and S. I. Lui, "CMOS wide-band amplifiers using multiple inductive-series peaking technique," *IEEE J. Solid-State Circuits*, vol. 40, no. 2, pp. 548–552, Feb. 2005.

- [7] B. Analui and A. Hajamiri, "Bandwidth enhancement for transimpedance amplifiers," *IEEE J. Solid-State Circuits*, vol. 39, no. 8, pp. 1263–1270, Aug. 2004.

- [8] J. Y. Liang and C. S. Aitchison, "Gain performance of cascade of single stage distributed amplifiers," *Electron. Lett.*, vol. 31, no. 15, pp. 1260–1261, Jul. 1995.

- [9] A. Worapishet, S. Srisathit, and M. Chongcheawchamnan, "Broadband amplification in CMOS technology using cascaded single-stage distributed amplifier," *Electron. Lett.*, vol. 38, no. 14, pp. 675–676, Jul. 2002.

- [10] M. D. Tsai, K. L. Deng, H. Wang, C. H. Chen, C. S. Chang, and J. G. J. Chern, "A miniature 25-GHz 9-dB CMOS cascaded single-stage distributed amplifier," *IEEE Microw. Wireless Compon. Lett.*, vol. 14, no. 12, pp. 554–556, Dec. 2004.

- [11] S. Galal and B. Razavi, "40-Gb/s amplifier and ESD protection circuit in 0.18-\(mu\)m CMOS technology," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2389–2396, Dec. 2004.

- [12] R. P. Jindal, "Gigahertz-Band high-gain low-noise AGC amplifiers in fine-line NMOS," *IEEE J. Solid-State Circuits*, vol. SC-22, no. 4, pp. 512–521, Aug. 1987.

- [13] T. H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits. New York: Cambridge University Press, 1998.

- [14] C. A. Desoer and E. S. Kuh, *Basic Circuit Theory*, . Berkeley: University of California, 1969.

- [15] B. Razavi, R. H. Yan, and K. F. Lee, "Impact of distributed gate resistance on the performance of MOS devices," *IEEE Trans. Circuits Syst. I., Fundam Theory Appl.*, vol. 41, no. 11, pp. 750–754, Nov. 1994.

Apisak Worapishet (M'00) received the B.Eng. degree from King Mongkut's Institute of Technology, Ladkrabang, Thailand, in 1990, the M.Eng.Sc. degree from the University of New South Wales, Sydney, Australia in 1995 both in electrical engineering, and the Ph.D. degree in electrical engineering from Imperial College of Science, Technology and Medicine, London, U.K., in 2001.

Since 1990, he has been with Mahanakorn University of Technology, Nong-Chok, Thailand, where he currently serves as the director of Mahanakorn

Microelectronics Research Center (MMRC) and an Associate Professor at Telecommunication Department. His current research interest includes mixed-signal CMOS analog integrated circuits and RF CMOS circuits and systems. Dr. Apisak is also a member of the IEICE and the Analogue Signal Processing Technical Committee (ASPTC) of the IEEE Circuit and System Society (CAS).

Ittipat Roopkom was born in Bangkok, Thailand. He received the B.E. and M.E. degrees in telecommunication engineering from Mahanakorn University of Technology, Nong-Chok, Thailand, in 2002 and 2005, respectively. he is currently working toward the Ph.D. degree at King Mongkut's Institute of Technology, Ladkrabang, Thailand.

Since 2006, he has been with the Faculty of Engineering and Research Center for Communications and Information Technology (ReCCIT), King Mongkut's Institute of Technology, His research

focuses on broadband circuit for communication system.

Wanlop Surakampontorn (M'79–SM'04) was born in Bangkok, Thailand. He received the B.Eng. and M.Eng. degrees in electrical engineering from the King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, Thailand, in 1976 and 1978, respectively, and the Ph.D. degree in electronics from the University of Kent, Canterbury, Kent, U.K., in 1983.

Since 1978, he has been a Member of the Department of Electronics, Faculty of Engineering, KMITL, where he is currently a Senior Professor of Electronic

Engineering. His research interests are in the areas of analog and digital integrated circuit designs, real-time application of PC computers and microprocessors, digital signal processing, electronic instrumentation, and VLSI signal processing.

Dr. Surakampontorn received the Outstanding Scientist of Thailand Award in 1996 and The National Award for Distinguished Researcher, Thailand, in 1998. He is a member of the IEICE.

International Journal of Electronics and Communications

Int. J. Electron. Commun. (AEÜ) 62 (2008) 11-23

www.elsevier.de/aeue

# Efficient implementation of tunable ladder filters using multi-output current controlled conveyors

Amorn Jiraseree-amornkun\*, Wanlop Surakampontorn

Faculty of Engineering and Research Center for Communications and Information Technology, King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand

Received 16 May 2006; accepted 22 January 2007

#### **Abstract**

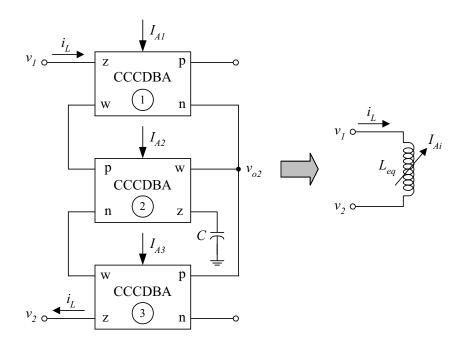

A methodology to realize continuous-time current-mode tunable ladder filters of any order has been presented. This proposed technique individually simulates signal flow graph (SFG) of each branch element from passive filter prototype using only multi-output second generation current controlled conveyors (MCCCIIs) and grounded capacitors. This leads to simple structure, ease of design and suitability for IC fabrication. A third-order Butterworth low-pass filter, a third-order elliptic low-pass filter and a sixth-order Chebyshev band-pass filter are employed to demonstrate the proposed realization scheme. These simulated filters retain minimum requirement of passive and active elements and provide the filter corner frequency tunability. Moreover, the method allows an implementation of the elliptic filters by simply adding floating capacitors to all-pole filter structures.

© 2007 Elsevier GmbH. All rights reserved.

Keywords: Tunable ladder filter; Current-mode; Multi-output current controlled conveyors

### 1. Introduction

Although information processing is migrating continuously to digital domain, analog filters have still been found in wide range of applications as a medium connecting digital processors and analog signals often found in nature. This paper concentrates on functional emulation of high-order passive RLC ladder filters, which are well known for their low pass-band sensitivity to component variations and component spreads. There have been numerous developed methods to enjoy these benefits using Op-amp-RC and OTA-C circuits [1]. Among these methods, the signal flow graph (SFG) simulation has gained better popularity than the synthetic elements replacement as it shares the low sensitivity and low component spreads of the precedent RLC filters. Traditionally,

E-mail address: amorn@ieee.org (A. Jiraseree-amornkun).

the SFG simulation is based on a modeling of the circuit characteristic using voltage signals. However, interests in current-mode signal processing are substantially expanding since it possesses a large number of good properties such as low internal nodes impedance, which gives a potential to achieve a large bandwidth. As signals are represented by current, a much lower voltage is required as compared with the voltage-mode signal processing. This makes the currentmode circuits suitable for low voltage designs. Furthermore, summation and subtraction of signal currents can be directly performed at circuit nodes, resulting in a simple structure. Consequently, many suggestions of the current-mode active ladder filters employing multiple output OTAs and CCIIs have been published [2-4]. However, most of them showed the realizations of the simulated transfer function in rather complicated ways and do not possess the optimal or efficient employment of active and passive elements. Furthermore, the realization may not have a direct connection to the prototype RLC filters. Thus, the sensitivity may not be

<sup>\*</sup> Corresponding author.

necessarily low. Recently, the linear transformation has been adopted to realize the active ladder filters with some good results [5,6]. But, complex synthesis equations as well as some external resistors are required. Moreover, the utilized frequency is fixed by their determined passive elements.

Rather than converting the whole network to a large SFG equivalent diagram, this paper shows an intuitive idea to divide the original ladder network into subsections, and then realize SFG of each subsection one by one. Hence the low sensitivity basis is guaranteed while reducing the complexity of a large SFG diagram. This proposed scheme possesses many advantages. First, the structure is very simple and easy to design including realization of the finite transmission zero. All capacitors are grounded and no external resistors are required, thereby saving chip area in IC implementation. In addition, each individual subsection SFG is simulated using the multi-output second generation current controlled convevor (MCCCII), the tunable internal impedance of which can be utilized to electronically adjust the frequency characteristics of the filters. This will be useful to reconfigure the system or to compensate for component deviations using automatic tuning system in IC integration [7].

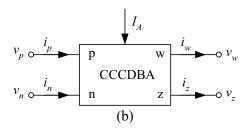

The next section briefly describes the current-mode ladder structure and the idea of individual component synthesis. An introduction to the multi-output current controlled conveyor and how to use it to implement each component of current-mode active filters using the proposed structure are discussed in Section 3. The circuit design of MCCCII is shown in Section 4. Section 5 explains some filter examples and their simulation results and Section 6 contains our conclusions.

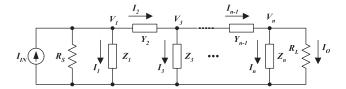

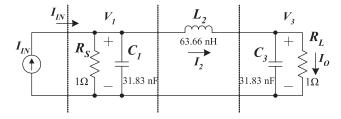

# 2. Current-domain ladder component partitioning

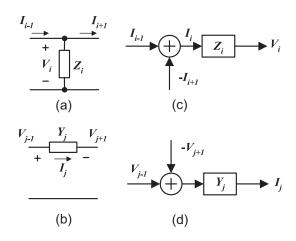

The traditional SFG simulation technique emulates voltage-current relationships of all elements in the prototype ladder filters. For a large network, however, this appears to be a roundabout and impractical way [1]. In this paper, a new viewpoint has been proposed. The idea is based on a partitioning of a large network into individual basic sections. Consider a general doubly terminated lossless passive ladder network in Fig. 1. Such a network can be partitioned into two basic sections: shunt and series (as depicted in Figs. 2(a) and (b), respectively), the corresponding SFG equivalent block diagrams of which are shown in Figs. 2(c) and (d). The block diagram in Fig. 2(c) (and Fig. 2(d)) represents the output voltage (current) as a result of the product of the impedance (admittance) and the subtraction between corresponding current (voltage) of the previous and next stages. Therefore, the overall equivalent structure can be constructed by a proper cascading of these two equivalent branches. With these two basic operations, the branch relationships for the entire structure can be

Fig. 1. General doubly terminated ladder network.

**Fig. 2.** Fundamental operations: (a) shunt branch, (b) equivalent shunt branch, (c) series branch, and (d) equivalent series branch.

rewritten in form of

$$V_{1} = Z_{1} \left( I_{IN} - I_{2} - \frac{V_{1}}{R_{S}} \right),$$

$$I_{2} = Y_{2}(V_{1} - V_{3}),$$

$$V_{3} = Z_{3}(I_{2} - I_{4}),$$

$$\vdots$$

$$V_{n} = Z_{n}(I_{n-1} - I_{o}),$$

$$I_{o} = \frac{V_{n}}{R_{I}}.$$

$$(1)$$

Since the summation or subtraction of current signals can be implemented at circuit nodes, converting all variables into current forms will lead to design simplicity. The conversion is simply performed by either normalizing or scaling the equations with resistance  $R_p$ . All relations in Eq. (1) are then transformed into their corresponding current transfer functions as

$$\frac{V_{1}}{R_{p}} = \frac{Z_{1}}{R_{p}} \left( I_{IN} - I_{2} - \frac{V_{1}}{R_{S}} \right),

I_{2} = Y_{2}R_{p} \left( \frac{V_{1}}{R_{p}} - \frac{V_{3}}{R_{p}} \right),

\frac{V_{3}}{R_{p}} = \frac{Z_{3}}{R_{p}} (I_{2} - I_{4}),

\vdots

\frac{V_{n}}{R_{p}} = \frac{Z_{n}}{R_{p}} (I_{n-1} - I_{o}),

I_{o} = \frac{R_{p}}{R_{L}} \frac{V_{n}}{R_{p}}.$$

(2)

### 3. Synthesis of branch elements using MCCCII

After the separated shunt and series portions have been created for the prototype ladder network, they will be subsequently implemented using the MCCCIIs. Each block of them has two outputs: a positive output for the forward path and a negative output for the feedback path. Finally, cascading every portion of branches back together with proper connections of the feed forward and feedback paths will result in the complete equivalent circuit. This method is as easy as the synthetic element replacement, yet maintaining the benefit of low sensitivity of the ladder structure.

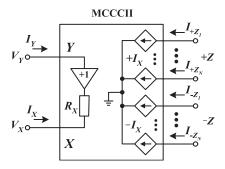

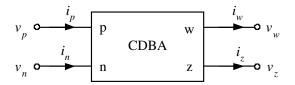

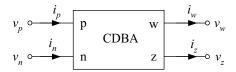

### 3.1. Characteristic of MCCCII

Typically, current conveyor has only one output current terminal, whose signal is available only once for each feedback path. Therefore, in multi-loop feedback topologies, which require several duplicated signals, multi-output configuration will gain more advantages. The equivalent circuit of MCCCII is shown in Fig. 3 and its port relations can be described by the following matrix equation:

$$\begin{bmatrix} I_Y \\ V_X \\ I_{+Z} \\ I_{-Z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 1 & R_X & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & -1 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_Y \\ I_X \\ V_{+Z} \\ V_{-Z} \end{bmatrix}, \tag{3}$$

where  $R_X$  is an intrinsic resistance of the current input port X and it is possible to be controlled by varying the external bias current [8]. The equivalent MCCCII-based components for simulating the two fundamental operations in Fig. 2 and the use of  $R_X$  as a tunable parameter fall into 3 categories namely (1) single passive element, (2) single passive element with source or load resistor, and (3) double passive elements, details of which will be described in the following sections.

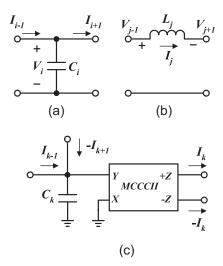

### 3.2. Simulation of single passive element

The first two basic single passive element frames: a shunt capacitor branch and a series inductor branch, are shown in Figs. 4(a) and (b), respectively. With all voltage signals transformed into their current counterparts by a scaling resistance  $R_p$  as mentioned in Section 2, their voltage and current relations in form of current transfer functions can be shown as

$$\frac{V_i}{R_p} = \frac{1}{sC_iR_p}(I_{i-1} - I_{i+1}),\tag{4a}$$

$$I_{j} = \frac{R_{p}}{sL_{j}} \left( \frac{V_{j-1}}{R_{p}} - \frac{V_{j+1}}{R_{p}} \right). \tag{4b}$$

Obviously, both equations represent an integrating function. Hence, they can be simulated by an equivalent MCCCII

Fig. 3. Equivalent circuit of MCCCII.

**Fig. 4.** Single element: (a) shunt C, (b) series L, (c) equivalent MCCCII structure.

integrator in Fig. 4(c), which has the current transfer function of

$$I_k = \frac{1}{sC_k R_X} (I_{k-1} - I_{k+1}). \tag{5}$$

Mapping the equivalent circuit to the shunt capacitor by letting  $I_k = V_i/R_p$ ,  $I_{k-1} = I_{i-1}$  and  $I_{k+1} = I_{i+1}$  results in the design parameter  $C_k = (C_i R_p)/R_X$ . Similarly, the design parameter for the series inductor branch is  $C_k = L_j/(R_p R_X)$ , which is deduced from mapping the circuit variables  $I_k = I_j$ ,  $I_{k-1} = V_{j-1}/R_p$  and  $I_{k+1} = V_{j+1}/R_p$ . Since after the transformation, all variables are related to  $R_X$ , the adjustment of  $R_X$  will tune the corner frequency of the filters.

The shunt inductor and the series capacitor can be treated in the same way. For ease of reference, all single passive element syntheses are summarized and listed in Table 1.

## 3.3. Simulation of single passive element with source or load resistor

By using the same concept as in Section 3.2, all single passive element syntheses with a source resistor are summarized in Table 2. Notice that similar current transfer

Table 1. Single passive element syntheses

| Passive elements                                                                                      | Voltage-current relations                                                         | MCCCII-based circuits                                                                                                                                |                                    |

|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| $I_{i:l} \xrightarrow{I_{i+l}} C_i$                                                                   | $\frac{V_i}{R_p} = \frac{1}{sC_i R_p} (I_{i-1} - I_{i+1})$                        | $\begin{array}{c c} I_{k-I} & \downarrow -I_{k+I} & I_k \\ \hline \\ C_k & \downarrow \\ \hline \\ & X & -Z & \rightarrow \\ & & & -I_k \end{array}$ | $C_k = (C_i R_p)/R_X$ for shunt C  |

| $V_{j-1} \longrightarrow V_{j+1} \longrightarrow V_{j+1}$                                             | $I_j = \frac{R_p}{sL_j} \left( \frac{V_{j-1}}{R_p} - \frac{V_{j+1}}{R_p} \right)$ | $I_k = \frac{1}{sC_k R_X} (I_{k-1} - I_{k+1})$                                                                                                       | $C_k = L_j/(R_p R_X)$ for series L |

| $I_{i-1} \longrightarrow I_{i+1}$ $V_i \longrightarrow L_i$                                           | $\frac{V_i}{R_p} = \frac{sL_i}{R_p} (I_{i-1} - I_{i+1})$                          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                | $C_k = L_i/(R_p R_X)$ for shunt L  |

| $ \begin{array}{c ccc} V_{j-l} & C_j & V_{j+l} \\  & & & \\  & & & \\ \hline I_j & & \\ \end{array} $ | $I_{j} = sC_{j}R_{p}\left(\frac{V_{j-1}}{R_{p}} - \frac{V_{j+1}}{R_{p}}\right)$   | $= sC_k R_X (I_{k-1} - I_{k+1})$                                                                                                                     | $C_k = (C_j R_p)/R_X$ for series C |

Table 2. Single passive element syntheses with source or load resistor

| Passive elements                                                                                           | Voltage-current relations                                                                   | MCCCII-based circuits                                                                                                                                 |                                    |

|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| $R_{s} \xrightarrow{I_{i+1}} C_{i}$                                                                        | $\frac{V_i}{R_S} = \frac{1}{sC_i R_S + 1} (I_{IN} - I_{i+1})$                               | $\begin{array}{c c} I_{k-1} & & & I_k \\ \hline C_k & & & X \\ \hline & & & & & & \\ & & & & & & \\ \hline & & & & & & \\ & & & & & & \\ & & & & & &$ | $C_k = (C_i R_S)/R_X$ for shunt C  |

| $\begin{array}{c c} I_{IN} & L_j & V_{j+1} \\ \hline \\ R_S & I_j & \\ \end{array}$                        | $I_{j} = \frac{1}{s \frac{L_{j}}{R_{S}} + 1} \left( I_{IN} - \frac{V_{j+1}}{R_{S}} \right)$ | _                                                                                                                                                     | $C_k = L_j/(R_S R_X)$ for series L |

| $I_{IN}$ $I_{i+1}$ $R_S$ $V_i$ $L_i$                                                                       | $\frac{V_i}{R_S} = \frac{s \frac{L_i}{R_S}}{s \frac{L_i}{R_S} + 1} (I_{IN} - I_{i+1})$      | $I_{k-I}$ $X$ $X$ $X$ $Y$ $+Z$ $Y$ $X$ $Y$ $+Z$ $Y$ $X$ $X$ $Y$ $Y$   | $C_k = L_i/(R_S R_X)$ for shunt L  |

| $\begin{array}{c c} I_{IN} & C_j & V_{j+1} \\ \hline \downarrow & & \downarrow \\ R_S & & I_j \end{array}$ | $I_j = \frac{sC_jR_S}{sC_jR_S + 1} \left( I_{IN} - \frac{V_{j+1}}{R_S} \right)$             | $I_{k} = \frac{sC_{k}R_{X}}{sC_{k}R_{X} + 1}(I_{k-1} - I_{k+1})$                                                                                      | $C_k = (C_j R_S)/R_X$ for series C |

equations as in the single passive element can be obtained when choosing  $R_S = R_p$ . Again, mapping  $I_k$ ,  $I_{k-1}$  and  $I_{k+1}$  of the MCCCII equivalent circuits to the passive branch elements result in the same design parameters  $C_k = (C_i R_S)/R_X$  for the shunt capacitor and  $C_k = L_j/(R_S R_X)$  for the series inductor. Note that it is also possible to realize these functions using an additional MCCCII connected as a resistor together with the circuits in Section 3.2 [9,10], but this will unnecessarily require some extra MCCCIIs. Comparing the circuits in Tables 1 and 2, the single passive elements with and without *source* resistor have nearly identical equivalent MCCCII circuits, except for a few different port arrangements of MCCCIIs. This is because we directly use  $R_X$  to simulate the *source* resistor and employ the potential of the multi-output structure.

Furthermore, it can be shown that single passive elements with a *load* resistor also share the same structures. However, we have to consider the input signals coming into the right-hand side of the passive RC/RL instead and the current  $I_{IN}$  is absent since load devices are considered. The equivalent MCCCII circuit remains unchanged, so does the design parameter  $C_k$ . This is also true for the rest of passive elements with either *source* or *load* resistor. Filter designs in Section 5 will clearly illustrate their usages in actual applications.

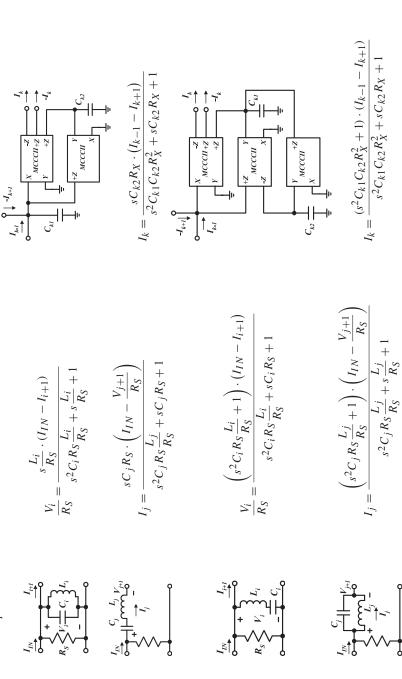

### 3.4. Simulation of double passive elements

Double LC passive elements, both with and without *source/load* resistor(s), can also be considered in a similar way as in the case of the single passive elements. Their results are shown in Table 3.

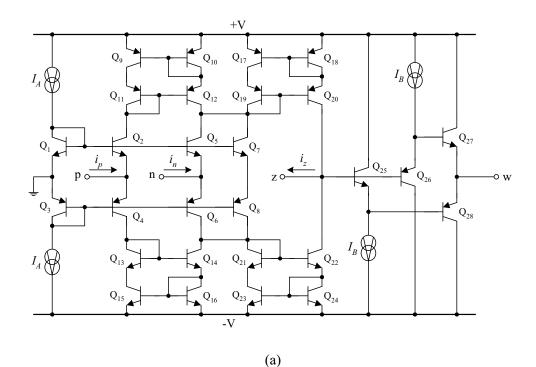

### 4. MCCCII implementation

### 4.1. Circuit description

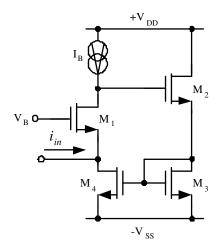

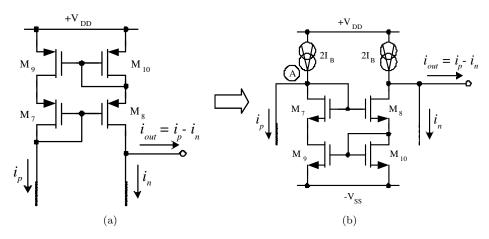

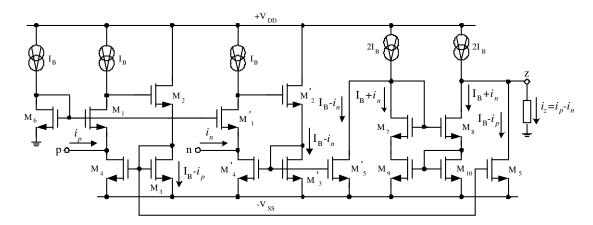

The implementation of a current conveyor based on a complementary push–pull class-AB has gained popularity in many applications since its structure is as simple as a basic OTA but consumes less power [8]. Although the bipolar technologies provide higher gain, greater linearity and wider frequency bandwidth, CMOS technologies have been in wide spread use in almost all areas of applications when low power consumption, low cost and suitability for mixed analog/digital implementations, are of major concerns. A circuit schematic of a CMOS push–pull MCCCII is shown in Fig. 5. All transistors are biased to operate in saturation region. The multi-output topology can be easily implemented by appending additional output transistors to the current mirrors at port +Z and -Z as required.

### 4.2. Nonlinearity consideration

From the proposed MCCCII-based filter topology, there are two major circuit functions: voltage-to-current con-

verter and current buffer. Nevertheless, both the Y-terminal-voltage-induced current and the input current that directly flows into the X-terminal have been nonlinearly divided into two paths flowing through the output NMOS and PMOS current mirrors, before they are duplicated and summed up again at the +Z and -Z outputs. Their transfer linearities can be shown in term of  $R_X$ . First, consider an input voltage applying to Y-terminal. This voltage will induce a current at the X-terminal, which in turn flow into the upper and lower transistors,  $M_2$  and  $M_4$ , respectively. Assuming  $K_1 = K_2 = K_N$ ,  $K_3 = K_4 = K_P$ ,  $V_{T1} = V_{T2} = V_{TN}$  and  $V_{T3} = V_{T4} = V_{TP}$ , we can write the following current relations:

$$i_{D2} = \begin{cases} I_B + 2v_Y \sqrt{K_N I_B} + K_N v_Y^2 & \text{for } v_Y > -\sqrt{\frac{I_B}{K_N}}, \\ 0 & \text{for } v_Y < -\sqrt{\frac{I_B}{K_N}}, \end{cases}$$

(6a)

$$i_{D4} = \begin{cases} I_B - 2v_Y \sqrt{K_P I_B} + K_P v_Y^2 & \text{for } v_Y < +\sqrt{\frac{I_B}{K_P}}, \\ 0 & \text{for } v_Y > +\sqrt{\frac{I_B}{K_P}}, \end{cases}$$

(6b)

where  $I_B$  is the bias current and MOSFET parameter  $K_{N(P)} = \mu_{N(P)} C_{OX}(W/L)/2$ . Combining these two branch currents in Eqs. (6a) and (6b) results in the total current flowing out of the X-terminal as

$$i_X = i_{D2} - i_{D4}$$

=  $2\sqrt{I_B}(\sqrt{K_N} + \sqrt{K_P})v_Y + (K_N - K_P)v_Y^2$ . (7)

Note that the short transition to weak inversion before the complete transistor turn-off is neglected, as this current does not normally contribute to a large error in the total current in the X-terminal if the bias current  $I_B$  is sufficiently large. Then the X-terminal current could be a linear function of the Y-input voltage and we can consider  $R_X$  as a linear resistor of  $1/4\sqrt{KI_B}$   $\Omega$ , as long as  $K_N = K_P = K$  and  $|i_X| < 4I_B$ are assumed [11]. This also implies that all transistors in the push-pull current conveyor will remain in saturation region until X-current signal is almost four times larger than the bias current  $I_B$ . Thus, its class-A operation range is nearly four times greater than a typical class-A current conveyor. This is also true for the input current directly flowing into the X-terminal in the current buffering operation. Eq. (7) is still valid with  $v_X$  replacing  $v_Y$  and the last parenthesis becomes  $(K_P - K_N)$ . The wide swing cascode current mirror has been chosen in order to minimize the current transfer error and raise the output impedance. The cascode transistor  $M_{P-\text{cas}}$  and  $M_{N-\text{cas}}$  help control the drain-source voltage,

| evnthese |  |

|----------|--|

| Plement  |  |

| naccive  |  |

| Domble   |  |

| ahle 3   |  |

| Ì        |  |

| Table 3. Double passive element syntheses           Passive elements         Voltage-current | ement syntheses  Voltage-current relations                                                                                               | MCCCII-based circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Double passive elements $V_{i} = C_{i} $ $V_{i} = C_{i} $ $V_{i} = C_{i} $                   | $\frac{V_i}{R_p} = \frac{s \frac{L_i}{R_p}}{s^2 C_i R_p \frac{L_i}{R_p} + 1} (I_{i-1} - I_{i+1})$                                        | $C_{kl} = \begin{bmatrix} I_{k+1} & I_k \\ I_{k+1} & I_k \\ I_{k+1} & I_k \end{bmatrix}$ $C_{kl} = \begin{bmatrix} I_k & I_k \\ I_k & I_k \\ I_k & I_k \end{bmatrix}$ $C_{kl} = \begin{bmatrix} I_k & I_k \\ I_k & I_k \end{bmatrix}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $C_{k1} = (C_i R_p)/R_X$<br>$C_{k2} = L_i/(R_p R_X)$ for shunt parallel LC       |

|                                                                                              | $I_{j} = \frac{sC_{j}R_{p}}{s^{2}C_{j}R_{p}\frac{L_{j}}{R_{p}} + 1} \left(\frac{V_{j-1}}{R_{p}} - \frac{V_{j+1}}{R_{p}}\right)$          | $=\frac{sC_{k2}R_{x}}{s^{2}C_{k1}C_{k2}R_{z}^{2}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $C_{k1} = L_j/(R_p R_X)$<br>$C_{k2} = (C_j R_p)/R_X$ for series LC               |

|                                                                                              | $\frac{V_i}{R_p} = \frac{s^2 C_i R_p \frac{L_i}{R_p} + 1}{s C_i R_p} (I_{i-1} - I_{i+1})$                                                | NCCCII Z  NCCCII | $C_{k1} = L_i/(R_p R_X)$ $C_{k2} = (C_i R_p)/R_X$ for shunt series LC            |

|                                                                                              | $I_{j} = \frac{s^{2}C_{j}R_{p}\frac{L_{j}}{R_{p}} + 1}{s\frac{L_{j}}{R_{p}}} \left(\frac{V_{j-1}}{R_{p}} - \frac{V_{j+1}}{R_{p}}\right)$ | $I_k = \frac{s^2 C_{k1} C_{k2} R_X^2}{s C_{k2} R_X} (I_{k-1} - I_{k+1})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $C_{k1} = (C_j R_p)/R_X$ $C_{k2} = L_j/(R_p R_X) \text{ for series parallel LC}$ |

$C_{k2} = (C_i R_S)/R_X$  for shunt series LC

$C_{k1} = L_i/(R_S R_X)$

$C_{k2} = L_j/(R_S R_X)$  for series parallel LC

$C_{k1} = (C_j R_S)/R_X$

Double passive elements with source or load resistor

$C_{k2} = L_i/(R_S R_X)$  for shunt parallel LC

$C_{k1} = (C_i R_S)/R_X$

$C_{k2} = (C_j R_S)/R_X$  for series LC

$C_{k1} = L_j/(R_S R_X)$

Fig. 5. Circuit schematic of a CMOS MCCCII.

Fig. 6. Small-signal equivalent circuit of the upper half of MCCCII.

$v_{\rm DS}$ , between transistors within the current mirrors  $M_P$  and  $M_N$ . The difference of drain-source voltages between the mirror transistors is in the order of a few millivolts for a proper design, hence the distortion from the channel length modulation effect is insignificant.

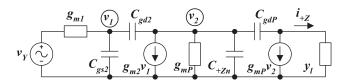

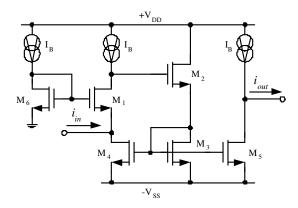

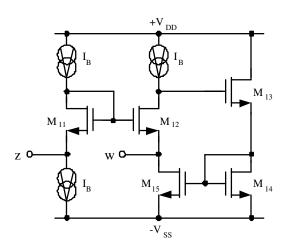

### 4.3. Frequency limitation

The small-signal equivalent circuit of the upper half from Y-terminal to +Z-terminal of the MCCCII is presented in Fig. 6, assuming that the transistor output conductance  $g_{ds}$ is much smaller than the transconductance  $g_m$  and the conductance  $g_1$  in the load admittance  $y_1 = g_1 + sC_1$ . For simplicity, all current mirrors are considered as simple MOS current mirrors since the cascode transistors barely contribute to the overall frequency response limitation. The capacitance  $C_{+\mathrm{Z}n}$  consists of the gate-source capacitances  $C_{\mathrm{gs}P}$  of the mirror transistors  $M_P$  and all other parasitic capacitances at node  $v_2$ , excluding the gate-drain capacitances  $C_{gd2}$  and  $C_{gdP}$ . Typically, the current mirror transistors usually have relatively large gate areas in order to minimize the current transfer error. Therefore, the gate-source capacitances are dominant and consequently the approximated  $C_{+Zn}$  can be determined as

$$C_{+Zn} \approx (n+2)C_{gsP} = (n+2)\frac{2}{3}C_{ox}W_PL_P,$$

(8)

where n is the number of output +Z ports and all mirror transistors have the same size. Note that the number n+2 in the parenthesis will become n+1 if there is no -Z-terminal.

Suppose that the gate-drain capacitances  $C_{\rm gd}$  are far smaller than the capacitances  $C_{+{\rm Z}n}$  and  $C_{\rm l}$ , therefore the upper half  $v_Y$ -to- $i_{+{\rm Z}}$  transconductance function can be determined as

$$\frac{i_{+Z}}{v_Y}\bigg|_{\text{upper half}} = g_{m2} \frac{\left(s \frac{C_{\text{gd2}}}{g_{m2}} - 1\right) \left(s \frac{C_{\text{gd}P}}{g_{mP}} - 1\right)}{\left(s \frac{C_{\text{gs2}}}{g_{m1}} + 1\right) \left(s \frac{C_{+Zn}}{g_{mP}} + 1\right)}.$$

(9)

The transfer function has two poles and two right half-plane (RHP) zeros. The first pole is the product of NMOS parameters that usually results in a much higher frequency than the second pole, which is originated from PMOS current mirror  $M_{P1}$  especially for the multi-output circuits. The RHP zeros do not contribute a great deal to the amplitude response near the corner frequency. Furthermore, the relatively insignificant Miller effect of  $C_{\rm gd}$  can be reduced even further by incorporating the cascode transistors into the current-mirrors. Accordingly, we can assume the second pole as the dominant pole that limits the frequency response of the upper half circuit. Therefore, the corner frequency can be expressed as a function of device dimensions, number of +Z ports and bias current in form of

$$\omega_0 = \frac{3}{n+2} \sqrt{\frac{\mu_P I_B}{2C_{ox} W_P L_P^3}}.$$

(10)

The above equation shows a trade-off between bandwidth and number of ports. Therefore, the port numbers must be minimized in order to use in higher frequency applications. As the corner frequency strongly depends on the channel length, there is also a strong trade-off between bandwidth and gain accuracy as well as bandwidth and distortion.

The lower half circuit of +Z-terminal can be similarly derived. This will show a dominant pole at the current mirror  $M_{N1}$ . However, such a pole frequency is almost three times larger due to the greater mobility of NMOS over PMOS. The frequency response of the -Z-terminal will have the additional poles and RHP zeros due to the current mirrors  $M_{P2}$  and  $M_{N2}$ . Therefore, the number of -Z ports must be reduced as much as possible in order to prevent further limitation on the operating frequency.

### 5. Filter designs and simulation results

The performance of filters designed by using the proposed methodology has been examined through HSPICE circuit simulator using AMIS 0.5- $\mu$ m level 49 CMOS model. For the MCCCII circuit in Fig. 5, the aspect ratio of all transistors are listed in Table 4. The bias current  $I_B$  is set to 50  $\mu$ A under the voltage supply of  $V_{\rm sup}=\pm 2.0\,{\rm V}$ . The simulated openloop transconductance gain  $(g_m)$  and 3-dB cutoff bandwidth are 0.53 mA/V and 183 MHz, respectively, when using the dual output MCCCII as a transconductance cell.

Table 4. W/L area of MOS in MCCCII circuit

| Transistors           | W/L   | Transistors          | W/L      |

|-----------------------|-------|----------------------|----------|

| $\overline{M_1, M_2}$ | 5/0.5 | $M_3, M_4$           | 18.5/0.5 |

| $M_{B1}$ , $M_{B2}$   | 90/2  | $M_{B3}, M_{B4}$     | 90/0.5   |

| $M_{B5}, M_{B6}$      | 30/2  | $M_{B7}, M_{B8}$     | 30/0.5   |

| $M_P$                 | 60/1  | $M_{P-\mathrm{cas}}$ | 100/1    |

| $M_N$                 | 60/1  | $M_{N-\mathrm{cas}}$ | 50/1     |

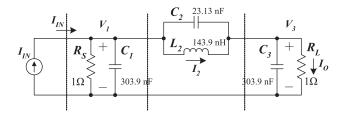

**Fig. 7.** Prototype current-mode 3rd-order Butterworth low-pass RLC ladder filter.

**Fig. 8.** MCCCIIs-based current-mode 3rd-order Butterworth low-pass filter.

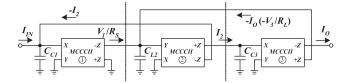

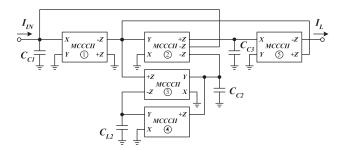

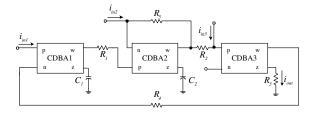

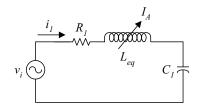

A current-mode third-order Butterworth low-pass ladder filter in Fig. 7 is adopted as the first design example. From the prototype passive filter, we can easily divide it into three sections of branch elements, comprising with the first shunt capacitor with the source resistor, the second series inductor and the third shunt capacitor with the load resistor. Refer to Table 2 for implementing the shunt capacitor with source and load resistors and Table 1 for the series inductor. The final equivalent MCCCII-based circuit is shown in Fig. 8. Obviously, only three MCCCIIs and three grounded capacitors are needed for realizing the third-order filter. It can be concluded that merely n MCCCIIs and n capacitors are required for the nth-order all-pole low-pass filters implementation with no requirement of external resistors. Therefore, this structure delivers a truly minimum requirement of active and passive components.

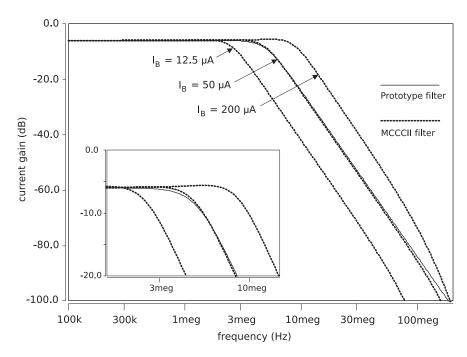

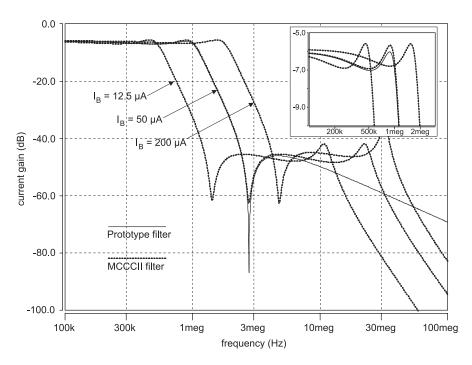

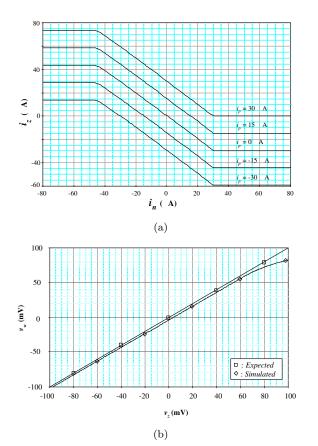

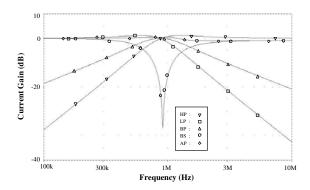

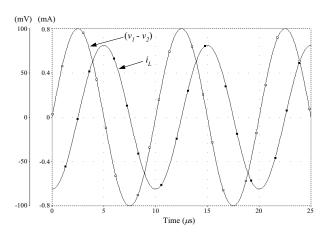

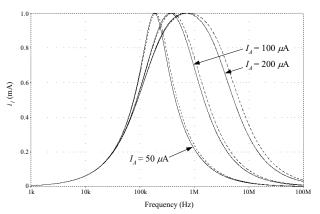

To picture out the feasibility of the proposed technique, the filter has been designed with the cutoff frequency  $f_{-3 \text{ dB}}$ of 5 MHz. Refer to Tables 1 and 2 for the design parameters  $C_k$ . Let  $R_p = R_S = 1 \Omega$  for simplicity and MCCCII  $R_X(1/g_m)$  of 1887  $\Omega$ , the capacitor values become  $C_{C1}$  $C_{C3} = 17.506 \,\mathrm{pF}$  and  $C_{L2} = 35.013 \,\mathrm{pF}$ . The simulated frequency responses of the designed circuit and the prototype RLC filter are shown together in Fig. 9. The tuning ability is performed by varying bias current to 12.5 and 200 μA. The corner frequencies are 2.65, 5.09 and 9.34 MHz relating to the calculated frequencies of 2.5, 5 and 10 MHz, respectively. The frequency accuracy is within about 6%. The proposed structure shows almost identical characteristic with the passive prototype filter before the signals begin to deviate at frequency beyond 100 MHz due to the frequency limitation of the MCCCIIs.

Fig. 9. Simulated frequency response of the 3rd-order Butterworth low-pass filter.

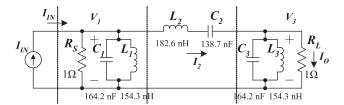

Filters including transmission zeroes like a third-order elliptic low-pass filter in Fig. 10 is also possible to be separated into three sections. By using the circuits in Table 3 for implementing the middle parallel LC elements while the first and the last blocks are, again, adopted from Table 2, the complete equivalent filter using only MCCCIIs and grounded capacitors is shown in Fig. 11. The prototype

Fig. 10. Prototype current-mode 3rd-order elliptic low-pass RLC ladder filter.

**Fig. 11.** MCCCIIs and only grounded capacitor current-mode 3rd-order elliptic low-pass filter.

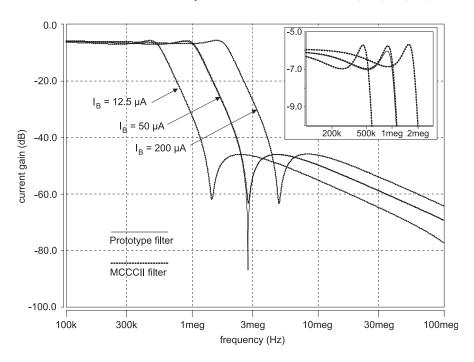

corner frequency has been selected to be 1 MHz with 1 dB pass band ripple and 40 dB stop band attenuation. The simulated frequency responses are depicted in Fig. 12. The large variation of MCCCIIs-filter in high frequencies is noticed. This comes from the frequency restriction of the multi-output current controlled conveyor especially the second current conveyor with three output ports, as predicted in Section 4.3. Note that the notch position is not as deep as in the prototype filter due to the limitation of quality factor of simulated LC components.

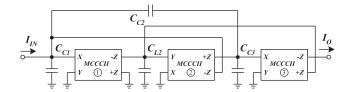

Because this proposed technique derives each element with one-by-one replacement concept, it is possible to separate the floating capacitor  $C_2$  from the passive filter in Fig. 10 and then realize the canonical MCCCII-based all-pole low-pass ladder filter first. After that, adding the scaled capacitor  $C_2$  to the synthesized circuit at the corresponding node will result in a circuit shown in Fig. 13. Simulated frequency responses of the floating capacitor MCCCIIs-based filter is shown in Fig. 14. It is clearly seen that a better performance than the previous circuit using only grounded

**Fig. 13.** MCCCIIs and floating capacitor current-mode 3rd-order elliptic low-pass filter.

Fig. 12. Simulated frequency response of the grounded capacitor elliptic low-pass filter.

Fig. 14. Simulated frequency response of the floating capacitor elliptic low-pass filter.

**Fig. 15.** Prototype current-mode 6th-order Chebyshev band-pass RLC ladder filter.

Fig. 16. MCCCIIs and only grounded capacitor current-mode 6th-order Chebyshev band-pass filter.

capacitors is achieved. It is worth noting that the peaking magnitude at the corner frequency due to phase lag is also smaller by 0.2 dB comparing to Fig. 12. This is because the use of low frequency three output ports MCCCII is avoided. Furthermore, this structure has the filter capacitances presented at all nodes and is suitable for high frequency operation. Therefore, this solution is preferable for realizing the elliptic filters when the floating capacitor is permitted.

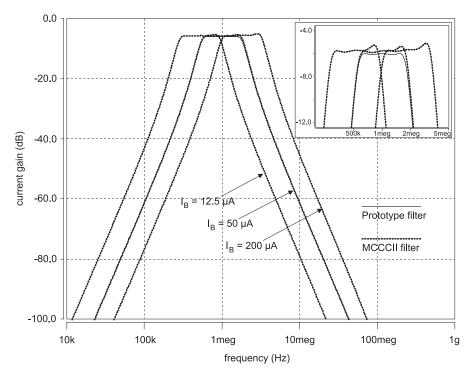

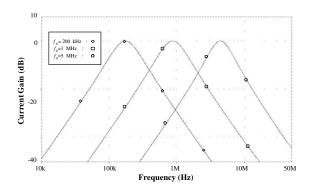

The last example is a sixth-order Chebyshev band-pass filter shown in Fig. 15 with 1 MHz center frequency and 1 MHz bandwidth. Its three branch sections are all listed in Table 3. The complete MCCCII-based band-pass filter appearing in Fig. 16 has the frequency response as shown in Fig. 17. There is a noticeable peaking due to the *Q*-enhancement effect. Since every separated section can be tuned electronically, incorporating a suitable *Q*-control circuit will help adjust the filter to the desired center frequency [7].

### 6. Conclusions

The current-mode ladder filter synthesis using multioutput current controlled conveyors has been proposed. The design method is very simple and covers all types of precedent passive LC ladder filters. This technique requires the minimum number for both passive and active components. There are only n MCCCIIs needed for realizing the nth-order all-pole filter and elliptic low-pass filter with an absence of the external resistor provided that floating capacitors are permitted. However, 2n - 1 and 2n - 2 MCCCIIs are required to achieve odd and even *n*thorder elliptic filters, respectively, when implementing with only grounded capacitors. The characteristic frequency can be tuned electronically by controlling the bias current of MCCCIIs. Third-order Butterworth and elliptic low-pass filter and sixth Chebyshev band-pass filter were chosen as design examples. HSPICE simulation results yield good agreement with the theoretical expectation.

Fig. 17. Simulated frequency response of the Chebyshev band-pass filter.

### Acknowledgement

This work was funded by the Thailand Research Fund (TRF) through the Royal Golden Jubilee Ph.D. Program (Grant No. PHD/0039/2545) to Mr. Amorn Jiraseree-amornkun and Prof. Dr. Wanlop Surakampontorn and financial support from the Thailand Research Fund under the Senior Research Scholar Program, Grant No. RTA4680003, is also acknowledged. The authors would like to thank Assoc. Prof. Dr. Apisak Worapishet for his valuable comments and discussions.

#### References

- [1] Schaumann R, Van Valkenberg M. Design of analog filters. New York: Oxford University Press; 2001.

- [2] Ramírez-Angulo J, Sánchez-Sinencio E. High frequency compensated current-mode ladder filters using multiple output otas. IEEE Trans Circ Syst II 1994;41:581–6.

- [3] Wu J, El-Masry E. Design of current-mode ladder filters using coupled-biquads. IEEE Trans Circ Syst II 1998;45:1445–54.

- [4] Wu J, El-Masry E. Current-mode ladder filters using multiple output current conveyors. IEE Proc G Circ Dev Syst 1996;143:218–22.

- [5] Hwang Y, Hung P, Chen W, Liu S. Ccii-based linear transformation elliptic filters. Int J Electron 2002;89:123–33.

- [6] Hwang Y, Hung P, Chen W, Liu S. Systematic generation of current-mode linear transformation filters based on multiple output cciis. Analog Integrated Circuit Sig Process 2002;32:123–34.

- [7] Gopinathan V, Tsividis Y, Tan K, Hester R. Design considerations for high-frequency continuous-time filters and

- implementation of an antialiasing filter for digital video. IEEE J Solid State Circ 1990:25:1368–78.

- [8] Fabre A, Saaid O, Wiest F, Boucheron C. High-frequency high-q bicmos current-mode bandpass filters and mobile communication application. IEEE J Solid State Circ 1998;33:614–25.

- [9] Jiraseree-amornkun A, Fujii N, Surakampontorn W. Realization of electronically tunable ladder filters using multiouput current controlled conveyor. Proceedings of the IEEE international symposium of circuits and systems, Bangkok, 2003. p. I-541–4.